KR102215664B1 - Multifunctional circuit board detection module and detection method - Google Patents

Multifunctional circuit board detection module and detection method Download PDFInfo

- Publication number

- KR102215664B1 KR102215664B1 KR1020197010197A KR20197010197A KR102215664B1 KR 102215664 B1 KR102215664 B1 KR 102215664B1 KR 1020197010197 A KR1020197010197 A KR 1020197010197A KR 20197010197 A KR20197010197 A KR 20197010197A KR 102215664 B1 KR102215664 B1 KR 102215664B1

- Authority

- KR

- South Korea

- Prior art keywords

- copper

- hole

- test

- connection

- holes

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0296—Conductive pattern lay-out details not covered by sub groups H05K1/02 - H05K1/0295

- H05K1/0298—Multilayer circuits

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0266—Marks, test patterns or identification means

- H05K1/0268—Marks, test patterns or identification means for electrical inspection or testing

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/16—Inspection; Monitoring; Aligning

- H05K2203/166—Alignment or registration; Control of registration

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

Abstract

다기능 회로판 검출 모듈의 검출 방법은 각 하나의 테스트 블록을 각각 테스트하고, 각 하나의 테스트 블록에서 제2 내지 제N-1 구리 스트립이 도통하는 지의 여부를 순차적으로 테스트하며, 구체적으로는 제1 연결홀과 기타 연결홀 사이에 도통하는 지의 여부를 검출하고, 도통하지 않으면, 내층 공정을 진행할 시 과도하게 에칭한 것으로 판정하고, 상이한 테스트 블록의 테스트 결과 및 각 테스트 블록에서 구리 스트립이 가장 좁은 곳의 폭을 결합하여 과도한 에칭량을 판정하는 단계; 각 하나의 테스트 블록을 각각 테스트하고, 각 하나의 테스트 블록에서 제2 내지 제N-1 구리층 사이에 도통하는 지의 여부를 순차적으로 테스트하며, 구체적으로는 제2 내지 제N-1 연결홀 사이에 도통하는 지의 여부를 검출하고, 도통하면, 라미네이션을 진행할 시 층 편이가 발생한 것으로 판정하고; 모든 구리층이 모두 도통하면, 드릴링 시 홀 편이가 발생한 것으로 판정하며, 상이한 테스트 블록의 테스트 결과 및 각 테스트 블록에서 고리형 구리 프리 영역의 폭을 결합하여 홀 편이의 편이량을 판정하는 단계를 포함한다. 내층, 라미네이션, 드릴링 공정의 제어 요구에 한하여 테스트 블록을 설계하고, 내층 공정 중의 에칭량, 라미네이션 공정 중의 층 편이, 드릴링 공정 중의 홀 편이에 대해 판단할 수 있으며, 이로써 회로판 제품이 정식으로 제작되기 전에 신빈성 있는 참조를 제공할 수 있고, 엔지니어링 자료 및 공정 실시의 조절을 진행하여, 제조 공정 능력 및 제품 품질을 향상시킨다.The detection method of the multifunctional circuit board detection module is to test each test block, and sequentially test whether the second to N-1th copper strips are conducting in each test block, specifically, the first connection It detects whether there is conduction between the hole and the other connection hole, and if it does not conduct, it is determined that the inner layer process is over-etched, and the test results of different test blocks and the narrowest copper strip in each test block. Combining the widths to determine an excessive amount of etching; Each test block is individually tested, and each test block sequentially tests whether or not conduction between the second to N-1th copper layers is conducted, and specifically, between the second to N-1th connection holes. Detects whether or not conduction is conducted, and if the conduction is conducted, it is determined that a layer shift has occurred when performing lamination; If all of the copper layers are conductive, it is determined that hole shift has occurred during drilling, and includes the step of determining the amount of hole shift by combining the test results of different test blocks and the width of the annular copper free region in each test block. do. Test blocks are designed only for the control requirements of the inner layer, lamination, and drilling process, and the amount of etching during the inner layer process, the layer shift during the lamination process, and the hole shift during the drilling process can be judged. Can provide reliable reference, control engineering data and process implementation, improve manufacturing process capability and product quality.

Description

본 발명은 회로판 공정 분야에 관한 것으로, 특히는 다기능 회로판 검출 모듈 및 검출 방법에 관한 것이다.The present invention relates to the field of circuit board processing, and more particularly, to a multifunctional circuit board detection module and detection method.

PCB 생산 과정에서, 각각의 공정의 실제 작업 능력(제조 공정 능력)의 높고 낮음은 이미 PCB 기업의 핵심 경쟁력으로 자리 잡았고, 제조 공정 능력의 향상 역시 기업 발전의 수요로서, 제조 과정 중 각각의 공정의 제조 공정 능력을 어떻게 효과적으로 모니터링하여, 제조 공정 능력의 향상에 참조적인 근거를 제공할 것인지는 PCB 기업이 중점적으로 해결해야 할 과제로 남았는 바, 특히는 다층판(6층 이상) 내층 수축 및 팽창, 내층 에칭 능력, 라미네이션 수축 및 팽창, 라미네이션 층 편이, 드릴링 수축 및 팽창, 드릴링 홀 편이 등 문제이며, 불량이 발생하면 제품의 기능에 직접적인 영향을 일으킬 수 있다.In the PCB production process, the high and low of the actual work capability (manufacturing process capability) of each process has already established itself as the core competitiveness of PCB companies, and the improvement of the manufacturing process capability is also a demand for corporate development. How to effectively monitor the manufacturing process capability and provide a reference basis for the improvement of the manufacturing process capability remains a major challenge for PCB companies. In particular, the shrinkage and expansion of the inner layer of multilayer boards (more than 6 layers), and the inner layer. There are problems such as etching ability, lamination contraction and expansion, lamination layer shift, drilling contraction and expansion, drilling hole shift, etc. If a defect occurs, it can directly affect the function of the product.

상기 문제에 한하여, 본 발명은 다기능 회로판 검출 모듈을 제공하는 데 그 목적이 있다.In light of the above problem, an object of the present invention is to provide a multifunctional circuit board detection module.

본 발명은 PCB 테스트 보드를 포함하고, 상기 PCB 테스트 보드는 다층 회로판이며, 상측으로부터 하측으로 순차적으로 설치되는 제1 내지 제N 구리층을 포함하고, 총 N층 구리층이며, N은 6보다 큰 짝수이고; The present invention includes a PCB test board, wherein the PCB test board is a multilayer circuit board, and includes first to Nth copper layers sequentially installed from top to bottom, and is a total N-layer copper layer, where N is greater than 6 Is even number;

PCB 테스트 보드에 한 개 또는 다수 개의 테스트 블록이 설치되어 있으며, 상기 테스트 블록은 제1 관통홀 그룹 및 제2 관통홀 그룹을 포함하고, 상기 제1 관통홀 그룹은 3라인으로 배열된 6 내지 12개의 테스트 홀을 포함하며, 상기 테스트 홀은 홀 직경이 동일한 관통홀이고; 제2 관통홀 그룹은 제1 연결홀 내지 제N-1 연결홀을 포함하며, 총 N-1개 연결홀이고, 상기 연결홀은 홀 직경이 동일한 관통홀이며; 상기 테스트 홀과 연결홀에 모두 홀 구리가 설치되어 있고; One or more test blocks are installed on the PCB test board, the test block includes a first through-hole group and a second through-hole group, and the first through-hole group is 6 to 12 arranged in three lines. It includes three test holes, the test holes are through holes having the same hole diameter; The second through-hole group includes a first connection hole to an N-1th connection hole, a total of N-1 connection holes, and the connection holes are through holes having the same hole diameter; Hole copper is installed in both the test hole and the connection hole;

제1 구리층에 제1 관통홀 그룹과 대응되는 제1 팩 구리 블록이 설치되어 있으며; 제N 구리층에 제1 관통홀 그룹과 대응되는 제N 팩 구리 블록이 설치되어 있고; 상기 제1 및 제N 팩 구리 블록은 모든 테스트 홀의 홀 구리와 연결되며; A first pack copper block corresponding to the first through-hole group is provided in the first copper layer; An Nth pack copper block corresponding to the first through-hole group is provided in the Nth copper layer; The first and Nth pack copper blocks are connected to hole copper in all test holes;

상기 제2 내지 제N-1 구리층에 제1 관통홀 그룹과 대응되는 제2 내지 제N-1 구리 스트립이 각각 순차적으로 설치되어 있고, 총 N-2개 구리 스트립이며, 제2 구리층에 제1 관통홀 그룹과 대응되는 제2 구리 스트립이 설치되어 있고, 제3 구리층에 제1 관통홀 그룹과 대응되는 제3 구리 스트립이 설치되어 있으며, 순차적으로 유추하고; 동일한 테스트 블록 내부의 구리 스트립이 가장 좁은 곳의 폭은 동일하며; 상기 제2 내지 제N-1 구리 스트립은 모두 제1 관통홀 그룹 내부의 각 라인의 테스트 홀의 상하측을 따라 휘어지게 둘러싸고, 각각 제2 내지 제N-1 구리층에서 각 하나의 테스트 홀에 대응되게 고리형 구리 프리 영역이 형성되며; 동일한 테스트 블록의 고리형 구리 프리 영역의 폭은 동일하고; 상기 제2 내지 제N-1 구리 스트립의 일단은 모두 제1 연결홀과 연결되며, 타단은 각각 순차적으로 제2 내지 제N-1 연결홀과 연결되고, 제2 구리 스트립의 타단은 제2 연결홀과 연결되며, 제3 구리 스트립의 타단은 제3 연결홀과 연결되고, 순차적으로 유추한다. The second to N-1th copper strips corresponding to the first through-hole group are sequentially installed in the second to N-1th copper layers, respectively, a total of N-2 copper strips, and in the second copper layer A second copper strip corresponding to the first through-hole group is provided, and a third copper strip corresponding to the first through-hole group is provided in the third copper layer, sequentially inferred; The width of the narrowest copper strip inside the same test block is the same; The second to N-1th copper strips are all bent along the upper and lower sides of the test holes of each line in the first through-hole group, and correspond to each test hole in the second to N-1th copper layers, respectively. A cyclic copper free region is formed; The width of the annular copper free regions of the same test block is the same; One end of the 2nd to N-1th copper strips are all connected to the first connection hole, the other ends are sequentially connected to the 2nd to N-1th connection holes, and the other end of the second copper strip is connected to the second It is connected to the hole, and the other end of the third copper strip is connected to the third connection hole, and is sequentially inferred.

바람직하게, 제1 및 제N 구리층에 제2 관통홀 그룹의 모든 연결홀에 대응되게 구리 홀 링이 설치되어 있고; 상기 제2 내지 제N-1 구리층에 모두 제1 연결홀에 대응되게 구리 홀 링이 설치되어 있으며; 제2 내지 제N-1 구리층에 제2 내지 제N-1 연결홀에 각각 순차적으로 대응되게 구리 홀 링이 설치되어 있고, 제2 구리층에 제2 연결홀에 대응되게 구리 홀 링이 설치되어 있으며, 제3 구리층에 제3 연결홀에 대응되게 구리 홀 링이 설치되어 있고, 순차적으로 유추하며; 상기 구리 홀 링은 상응한 연결홀의 홀 구리와 연결되고; 상기 제2 내지 제N-1 구리 스트립의 양단은 구리층에 대응되게 설치되는 두 개의 구리 홀 링과 각각 연결된다. Preferably, copper hole rings are provided in the first and Nth copper layers to correspond to all connection holes of the second through-hole group; Copper hole rings are provided in all of the second to N-1th copper layers to correspond to the first connection holes; Copper hole rings are installed in the 2nd to N-1th copper layers to correspond sequentially to the 2nd to N-1th connection holes, respectively, and the copper hole rings are installed in the second copper layer to correspond to the second connection holes A copper hole ring is provided in the third copper layer to correspond to the third connection hole, and is sequentially inferred; The copper hole ring is connected to the hole copper of the corresponding connection hole; Both ends of the second to N-1th copper strips are respectively connected to two copper hole rings provided to correspond to the copper layer.

바람직하게, 상기 제2 내지 제N-1 구리 스트립에서 제1 관통홀 그룹 내부의 각 라인의 테스트 홀 사이에 위치하는 부분에 구리 브릿지가 각각 형성되고; 동일한 구리 스트립에서 서로 인접한 구리 브릿지 사이의 최소 거리는 0.1mm보다 크거나 같다. Preferably, copper bridges are formed in portions of the second to N-1th copper strips positioned between test holes of each line in the first through-hole group; The minimum distance between adjacent copper bridges in the same copper strip is greater than or equal to 0.1mm.

또한, 제 1항 내지 제 3항 중 어느 한 항에 있어서, 서로 인접한 연결홀의 홀 간격은 1.0 내지 1.1mm이고; 테스트 홀과 연결홀의 홀 직경은 모두 0.2mm이며; 테스트 홀과 연결홀 사이의 거리는 1mm보다 크다. Further, according to any one of claims 1 to 3, the hole spacing of the connecting holes adjacent to each other is 1.0 to 1.1 mm; Both the test hole and the connection hole have a hole diameter of 0.2 mm; The distance between the test hole and the connection hole is greater than 1mm.

또한, 상기 제1 관통홀 그룹은 3라인으로 배열된 9개의 테스트 홀을 포함한다. In addition, the first through-hole group includes nine test holes arranged in three lines.

또한, PCB 테스트 보드에 6개의 테스트 블록이 설치되어 있다. In addition, six test blocks are installed on the PCB test board.

또한, 상기 6개의 테스트 블록에서 고리형 구리 프리 영역의 폭은 각각 0.075mm, 0.1mm, 0.127mm, 0.15mm, 0.178mm, 0.2mm이다.In addition, the widths of the annular copper-free regions in the six test blocks are 0.075mm, 0.1mm, 0.127mm, 0.15mm, 0.178mm, and 0.2mm, respectively.

또한, 상기 6개의 테스트 블록에서 구리 스트립이 가장 좁은 곳의 폭은 각각 0.075mm, 0.1mm, 0.127mm, 0.15mm, 0.178mm, 0.2mm이다. In addition, the widths of the narrowest copper strips in the six test blocks are 0.075mm, 0.1mm, 0.127mm, 0.15mm, 0.178mm, and 0.2mm, respectively.

본 발명은 다기능 회로판 검출 모듈을 사용하는 검출 방법을 더 제공하며, 내층, 라미네이션, 드릴링 공정을 완료한 후의 제조된 다기능 회로판 검출 모듈에 대해, 하기의 테스트 항목을 진행하는 바, The present invention further provides a detection method using a multifunctional circuit board detection module, and the following test items are performed for the manufactured multifunctional circuit board detection module after completing the inner layer, lamination, and drilling process,

각 하나의 테스트 블록을 각각 테스트하고, 각 하나의 테스트 블록에서 제2 내지 제N-1 구리 스트립이 도통하는 지의 여부를 순차적으로 테스트하며, 구체적으로는 제1 연결홀과 기타 연결홀 사이에 도통하는 지의 여부를 검출하고, 도통하지 않으면, 내층 공정을 진행할 시 과도하게 에칭한 것으로 판정하고, 상이한 테스트 블록의 테스트 결과 및 각 테스트 블록에서 구리 스트립이 가장 좁은 곳의 폭을 결합하여 과도한 에칭량을 판정하는 단계; Each test block is tested, and in each test block, it is sequentially tested whether or not the second to N-1th copper strips are conducting. Specifically, conduction is conducted between the first connection hole and other connection holes. If it does not conduct, it is judged that the inner layer process is over-etched, and the test results of different test blocks and the width of the narrowest copper strip in each test block are combined to reduce the excessive etching amount. Determining;

각 하나의 테스트 블록을 각각 테스트하고, 각 하나의 테스트 블록에서 제2 내지 제N-1 구리층 사이에 도통하는 지의 여부를 순차적으로 테스트하며, 구체적으로는 제2 내지 제N-1 연결홀 사이에 도통하는 지의 여부를 검출하고, 도통하면, 라미네이션을 진행할 시 층 편이가 발생한 것으로 판정하고; 모든 구리층이 모두 도통하면, 드릴링할 시 홀 편이가 발생한 것으로 판정하며, 상이한 테스트 블록의 테스트 결과 및 각 테스트 블록의 고리형 구리 프리 영역의 폭을 결합하여 홀 편이의 편이량을 판정하는 단계를 포함한다. Each test block is individually tested, and each test block sequentially tests whether or not conduction between the second to N-1th copper layers is conducted, and specifically, between the second to N-1th connection holes. Detects whether or not conduction is conducted, and if the conduction is conducted, it is determined that a layer shift has occurred when performing lamination; If all of the copper layers are conductive, it is determined that a hole shift has occurred during drilling, and the step of determining the amount of hole shift by combining the test results of different test blocks and the width of the annular copper free region of each test block is performed. Include.

바람직하게, 각 하나의 테스트 블록에서 제2 내지 제N-1 구리층 사이에 도통하는 지의 여부를 순차적으로 테스트할 시, 제2 내지 제N-1 구리층에서 임의의 두 개의 구리층이 도통하면, 층 편이가 상기 두 개의 구리층 사이에서 발생하는 것으로 판정할 수 있고, 상이한 테스트 블록의 테스트 결과 및 각 테스트 블록에서 고리형 구리 프리 영역의 폭을 결합하여 층 편이의 편이량을 판정하며; Preferably, when sequentially testing whether or not conduction between the second to N-1th copper layers is conducted in each one test block, if any two copper layers are conductive in the second to N-1th copper layers , It can be determined that the layer shift occurs between the two copper layers, and the test results of different test blocks and the width of the annular copper free region in each test block are combined to determine the amount of shift of the layer;

제2 내지 제N-1 구리층에서 임의의 다수의 구리층이 도통하면, 모든 구리층에서 모두 층 편이가 발생하는 것으로 판정할 수 있고, 상이한 테스트 블록의 테스트 결과 및 각 테스트 블록에서 고리형 구리 프리 영역의 폭을 결합하여 각 구리층의 층 편이의 편이량을 판정한다.If a plurality of copper layers are conductive in the second to N-1th copper layers, it can be determined that layer shift occurs in all copper layers, and the test results of different test blocks and annular copper in each test block. The width of the free region is combined to determine the amount of shift in the layer shift of each copper layer.

본 발명은 내층, 라미네이션, 드릴링 공정의 제어 요구에 한하여 테스트 블록을 설계하고, 내층 공정 중의 에칭량, 라미네이션 공정 중의 층 편이, 드릴링 공정 중의 홀 편이를 간편하고 신속하게 판단할 수 있으며, 이로써 회로판 제품이 정식으로 제작되기 전에 신빈성 있는 참조를 제공할 수 있고, 엔지니어링 자료 및 공정 실시의 조절을 진행하여, 제조 공정 능력을 향상시키며, 제품의 품질을 향상시킨다.In the present invention, the test block is designed only for the control requirements of the inner layer, lamination, and drilling process, and the etching amount during the inner layer process, the layer shift during the lamination process, and the hole shift during the drilling process can be determined easily and quickly. Before it is formally manufactured, it can provide reliable reference, control engineering data and process implementation, improve manufacturing process capability, and improve product quality.

도 1은 다기능 회로판 검출 모듈의 실시예의 구조도이다.

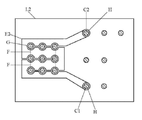

도 2는 다기능 회로판 검출 모듈의 실시예의 제1 구리층 중 테스트 블록 모식도이다.

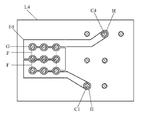

도 3은 다기능 회로판 검출 모듈의 실시예의 제2 구리층 중 테스트 블록 모식도이다.

도 4는 다기능 회로판 검출 모듈의 실시예의 제3 구리층 중 테스트 블록 모식도이다.

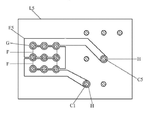

도 5는 다기능 회로판 검출 모듈의 실시예의 제4 구리층 중 테스트 블록 모식도이다.

도 6은 다기능 회로판 검출 모듈의 실시예의 제5 구리층 중 테스트 블록 모식도이다.

도 7은 다기능 회로판 검출 모듈의 실시예의 제6 구리층 중 테스트 블록 모식도이다.

도 8은 다기능 회로판 검출 모듈의 실시예의 제7 구리층 중 테스트 블록 모식도이다.

도 9는 다기능 회로판 검출 모듈의 실시예의 제8 구리층 중 테스트 블록 모식도이다.1 is a structural diagram of an embodiment of a multifunctional circuit board detection module.

2 is a schematic diagram of a test block in a first copper layer of an embodiment of a multifunctional circuit board detection module.

3 is a schematic diagram of a test block in a second copper layer of an embodiment of a multifunctional circuit board detection module.

4 is a schematic diagram of a test block in a third copper layer of an embodiment of a multifunctional circuit board detection module.

5 is a schematic diagram of a test block in a fourth copper layer of an embodiment of a multifunctional circuit board detection module.

6 is a schematic diagram of a test block in a fifth copper layer of an embodiment of a multifunctional circuit board detection module.

7 is a schematic diagram of a test block in a sixth copper layer of an embodiment of a multifunctional circuit board detection module.

8 is a schematic diagram of a test block in a seventh copper layer of an embodiment of a multifunctional circuit board detection module.

9 is a schematic diagram of a test block in an eighth copper layer of an embodiment of a multifunctional circuit board detection module.

본 기술분야의 통상의 기술자가 본 발명의 기술내용을 간편하게 이해하도록 하기 위해, 이하 도면 및 실시예를 결부하여 본 발명을 더욱 상세하게 설명한다.In order for those skilled in the art to easily understand the technical content of the present invention, the present invention will be described in more detail with reference to the drawings and examples below.

도 1에 도시된 다기능 회로판 검출 모듈은, PCB 테스트 보드(1)를 포함하고, 상기 PCB 테스트 보드는 다층 회로판이며, 상측으로부터 하측으로 순차적으로 설치되는 제1 구리층(L1), 제2 구리층 L2…제8 구리층(L8)을 포함하고, 총 8층 구리층이다. The multifunctional circuit board detection module shown in FIG. 1 includes a PCB test board 1, and the PCB test board is a multilayer circuit board, a first copper layer L1 and a second copper layer sequentially installed from top to bottom. L2... It includes an eighth copper layer (L8), and is a total of 8 copper layers.

PCB 테스트 보드(1)에 6개의 테스트 블록(2)이 설치되어 있고, 그중의 하나의 테스트 블록은 도 2 내지 도 9에 도시된 바와 같으며, 각 하나의 테스트 블록은 제1 관통홀 그룹(A1) 및 제2 관통홀 그룹(A2)을 포함하고, 제1 관통홀 그룹(A1)은 3라인으로 배열된 9개의 테스트 홀(B)을 포함하며; 제2 관통홀 그룹(A2)은 제1 연결홀(C1), 제2 연결홀(C2)…제7 연결홀(C7)을 포함하고, 총 7개의 연결홀이며, 테스트 홀과 연결홀은 모두 홀 직경이 동일한 관통홀이고, 홀 내부에 모두 홀 구리가 설치되어 있다. 서로 인접한 연결홀의 홀 간격은 1.1mm이고; 테스트 홀과 연결홀의 홀 직경은 모두 0.2mm이며; 테스트 홀과 연결홀 사이의 거리는 1mm보다 크다. Six

제1 구리층(L1)에 제1 관통홀 그룹(A1)과 대응되는 제1 팩 구리 블록(D1)이 설치되어 있고; 제8 구리층(L8)에 제1 관통홀 그룹(A1)과 대응되는 제8 팩 구리 블록(D8)이 설치되어 있으며; 제1 및 제8 팩 구리 블록은 모든 테스트 홀 내부의 홀 구리와 연결되고; 제2 내지 제7 구리층에 제1 관통홀 그룹과 대응되는 제2 구리 스트립(E2), 제3 구리 스트립(E3)…제7 구리 스트립(E7)이 각각 순차적으로 설치되어 있으며, 6개의 테스트 블록에서 구리 스트립이 가장 좁은 곳의 폭은 각각 0.075mm, 0.1mm, 0.127mm, 0.15mm, 0.178mm, 0.2mm로 설치된다. 내층이 상이한 구리 두께에 따라, 상이한 구리 스트립 폭을 설계할 수 있고, 구리 스트립의 폭이 내층 에칭 능력을 검증하기 위한 것이기에, 내층 구리 두께가 상이하고, 에칭량이 같지 않다. A first pack copper block D1 corresponding to the first through-hole group A1 is provided in the first copper layer L1; An eighth pack copper block D8 corresponding to the first through-hole group A1 is provided in the eighth copper layer L8; The first and eighth pack copper blocks are connected with the hole copper inside all the test holes; The second copper strip E2, the third copper strip E3 corresponding to the first through-hole group in the second to seventh copper layers. Each of the seventh copper strips (E7) is sequentially installed, and the widths of the narrowest copper strips in the six test blocks are respectively 0.075mm, 0.1mm, 0.127mm, 0.15mm, 0.178mm, and 0.2mm. . According to the copper thickness of the inner layer different, different copper strip widths can be designed, and since the width of the copper strip is for verifying the inner layer etching ability, the inner layer copper thickness is different, and the etching amount is not the same.

제2 내지 제7 구리 스트립에서 제1 관통홀 그룹 내부의 각 라인의 테스트 홀 사이에 위치하는 부분에 구리 브릿지(F)가 각각 형성되고; 동일한 구리 스트립에서 서로 인접한 구리 브릿지(F) 사이의 최소 거리는 0.1mm이다. Copper bridges (F) are formed in portions between the test holes of each line in the first through-hole group in the second to seventh copper strips, respectively; The minimum distance between adjacent copper bridges (F) in the same copper strip is 0.1 mm.

제2 내지 제7 구리 스트립은 모두 제1 관통홀 그룹 내부의 각 라인의 테스트 홀의 상하측을 따라 휘어지게 둘러싸고, 제2 내지 제7 구리층에서 각 하나의 테스트 홀에 대응되게 고리형 구리 프리 영역(G)을 각각 형성하며; 6개의 테스트 블록에서 고리형 구리 프리 영역의 폭은 각각 0.075mm, 0.1mm, 0.127mm, 0.15mm, 0.178mm, 0.2mm로 설치된다. All the 2nd to 7th copper strips are bent along the upper and lower sides of the test holes of each line in the first through-hole group, and annular copper free regions corresponding to each one test hole in the second through seventh copper layers Each forming (G); In the six test blocks, the width of the annular copper free area is set to 0.075mm, 0.1mm, 0.127mm, 0.15mm, 0.178mm and 0.2mm respectively.

제2 내지 제7 구리 스트립의 일단은 모두 제1 연결홀과 연결되고, 타단은 제2 내지 제7 연결홀과 각각 순차적으로 연결되며, 제2 구리 스트립의 타단은 제2 연결홀과 연결되고, 제3 구리 스트립의 타단은 제3 연결홀과 연결되며, 순차적으로 유추한다. One end of the second to seventh copper strips are all connected to the first connection hole, the other end is sequentially connected to the second to seventh connection holes, and the other end of the second copper strip is connected to the second connection hole, The other end of the third copper strip is connected to the third connection hole, and is sequentially inferred.

구리 스트립 및 상응한 연결홀의 간편한 연결과 데스트할 시의 간편 신속을 위해, 제1 및 제8 구리층에서 제2 관통홀 그룹의 모든 연결홀에 대응되게 구리 홀 링(H)이 설치되어 있고; 제2 내지 제7 구리층에 모두 제1 연결홀에 대응되게 구리 홀 링(H)이 설치되어 있으며; 제2 내지 제7 구리층에서 제2 내지 제7 연결홀에 각각 순차적으로 대응되게 구리 홀 링(H)이 설치되어 있고, 제2 구리층에 제2 연결홀에 대응되게 구리 홀 링이 설치되어 있으며, 제3 구리층에 제3 연결홀에 대응되게 구리 홀 링이 설치되어 있고, 순차적으로 유추하며; 구리 홀 링은 상응한 연결홀의 홀 구리와 연결되고; 제2 내지 제7 구리 스트립의 양단은 각각 구리층에 대응되게 설치되는 두 개의 구리 홀 링(H)과 연결된다. For simple connection of the copper strip and the corresponding connection hole and for simple and quick testing during testing, a copper hole ring H is provided to correspond to all connection holes of the second through hole group in the first and eighth copper layers; Copper hole rings (H) are provided in all of the second to seventh copper layers to correspond to the first connection holes; In the second to seventh copper layers, copper hole rings (H) are installed to correspond sequentially to the second to seventh connection holes, and copper hole rings are installed to correspond to the second connection holes in the second copper layer. And a copper hole ring is provided in the third copper layer to correspond to the third connection hole, and is sequentially inferred; The copper hole ring is connected with the hole copper of the corresponding connection hole; Both ends of the second to seventh copper strips are connected to two copper hole rings H installed to correspond to the copper layers, respectively.

상기 실시예에 언급되는 다기능 회로판 검출 모듈을 이용하여 검출을 진행할 시, 내층, 라미네이션, 드릴링 공정을 완료한 후의 제조된 다기능 회로판 검출 모듈에 대해, 하기의 테스트 항목을 진행하는 바, When the detection is performed using the multifunctional circuit board detection module mentioned in the above embodiment, the following test items are performed for the manufactured multifunctional circuit board detection module after completing the inner layer, lamination, and drilling process,

각 하나의 테스트 블록을 각각 테스트하고, 각 하나의 테스트 블록에서 제2 내지 제7 구리 스트립이 도통하는 지의 여부를 순차적으로 테스트하며, 구체적으로는 제1 연결홀과 기타 연결홀 사이에 도통하는 지의 여부를 검출하고, 도통하지 않으면, 내층 공정을 진행할 시 과도하게 에칭한 것으로 판정하고, 상이한 테스트 블록의 테스트 결과 및 각 테스트 블록에서 구리 스트립이 가장 좁은 곳의 폭을 결합하여 과도한 에칭량을 판정한다. Each test block is individually tested, and in each test block, it is sequentially tested whether or not the second to seventh copper strips are conducting, and specifically, whether or not the first connection hole and the other connection holes are conducting. If it does not conduct, it is determined that the inner layer process is over-etched, and the test result of different test blocks and the width of the narrowest copper strip in each test block are combined to determine the excessive etching amount. .

각 하나의 테스트 블록을 각각 테스트하고, 각 하나의 테스트 블록에서 제2 내지 제7 구리층 사이에 도통하는 지의 여부를 순차적으로 테스트하며, 구체적으로는 제2 내지 제7 연결홀 사이에 도통하는 지의 여부를 검출하고, 도통하면, 라미네이션을 진행할 시 층 편이가 발생한 것으로 판정하고; 제2 내지 제7 구리층에서 임의의 두 개의 구리층이 도통하면, 층 편이가 상기 두 개의 구리층 사이에서 발생하는 것으로 판정할 수 있고, 상이한 테스트 블록의 테스트 결과 및 각 테스트 블록에서 고리형 구리 프리 영역의 폭을 결합하여 층 편이의 편이량을 판정하며; 제2 내지 제7 구리층의 임의의 다수의 구리층이 도통하면, 모든 구리층에서 모두 층 편이가 발생하는 것으로 판정할 수 있고, 상이한 테스트 블록의 테스트 결과 및 각 테스트 블록에서 고리형 구리 프리 영역의 폭을 결합하여 각 층의 층 편이의 편이량을 판정한다. Each test block is tested, and in each test block, whether or not conduction is conducted between the second to seventh copper layers is sequentially tested, and specifically, whether conduction is conducted between the second to seventh connection holes. Whether or not it is detected, and if it conducts, it is determined that a layer shift has occurred when performing lamination; If any two copper layers in the 2nd to 7th copper layers conduct, it can be determined that a layer shift occurs between the two copper layers, and the test results of different test blocks and the annular copper in each test block Combining the widths of the free regions to determine the amount of shift in the layer; If any plurality of copper layers of the 2nd to 7th copper layers conduct, it can be determined that layer shifts occur in all of the copper layers, and the test results of different test blocks and the annular copper free area in each test block The widths of are combined to determine the amount of shift in each layer.

모든 구리층이 모두 도통하면, 드릴링할 시 홀 편이가 발생한 것으로 판정하며, 상이한 테스트 블록의 테스트 결과 및 각 테스트 블록의 고리형 구리 프리 영역의 폭을 결합하여 홀 편이의 편이량을 판정한다. If all of the copper layers are conductive, it is determined that a hole shift has occurred during drilling, and the amount of hole shift is determined by combining the test results of different test blocks and the width of the annular copper free region of each test block.

상기 내용은 본 발명의 구체적인 실시예로서, 그 묘사는 비교적 구체적이고 상세하지만, 이로써 본 발명의 특허범위를 한정한다고 할 수 없다. 반드시 지적해야 하는 바, 본 기술분야의 통상의 기술자에게 있어서, 본 발명의 구상을 벗어나지 않는 전제하에서, 약간의 변형과 개선을 진행할 수 있는 바, 이러한 자명한 교체 형식은 본 발명의 보호범위에 속한다.The above is a specific embodiment of the present invention, and the description is relatively specific and detailed, but it cannot be said to limit the scope of the present invention. It should be pointed out that, for those skilled in the art, some modifications and improvements can be made without departing from the concept of the present invention, and such an obvious replacement format falls within the protection scope of the present invention. .

Claims (10)

이는 PCB 테스트 보드를 포함하고, 상기 PCB 테스트 보드는 다층 회로판이며, 상측으로부터 하측으로 순차적으로 설치되는 제1 내지 제N 구리층을 포함하고, 총 N층 구리층이며, N은 6보다 큰 짝수이고; PCB 테스트 보드에 한 개 또는 다수 개의 테스트 블록이 설치되어 있으며, 상기 테스트 블록은 제1 관통홀 그룹 및 제2 관통홀 그룹을 포함하고, 상기 제1 관통홀 그룹은 3라인으로 배열된 6 내지 12개의 테스트 홀을 포함하며, 상기 테스트 홀은 홀 직경이 동일한 관통홀이고; 제2 관통홀 그룹은 제1 연결홀 내지 제N-1 연결홀을 포함하며, 총 N-1개 연결홀이고, 상기 연결홀은 홀 직경이 동일한 관통홀이며; 상기 테스트 홀과 연결홀에 홀 구리가 설치되어 있고;

제1 구리층에 제1 관통홀 그룹과 대응되는 제1 팩 구리 블록이 설치되어 있으며; 제N 구리층에 제1 관통홀 그룹과 대응되는 제N 팩 구리 블록이 설치되어 있고; 상기 제1 및 제N 팩 구리 블록은 모든 테스트 홀의 홀 구리와 연결되며;

상기 제2 내지 제N-1 구리층에 제1 관통홀 그룹과 대응되는 제2 내지 제N-1 구리 스트립이 각각 순차적으로 설치되어 있고, 총 N-2개 구리 스트립이며, 제2 구리층에 제1 관통홀 그룹과 대응되는 제2 구리 스트립이 설치되어 있고, 제3 구리층에 제1 관통홀 그룹과 대응되는 제3 구리 스트립이 설치되어 있으며, 순차적으로 유추하고; 동일한 테스트 블록 내부의 구리 스트립이 가장 좁은 곳의 폭은 동일하며; 상기 제2 내지 제N-1 구리 스트립은 제1 관통홀 그룹 내부의 각 라인의 테스트 홀의 상하측을 따라 휘어지게 둘러싸고, 각각 제2 내지 제N-1 구리층에서 각 하나의 테스트 홀에 대응되게 고리형 구리 프리 영역이 형성되며; 동일한 테스트 블록의 고리형 구리 프리 영역의 폭은 동일하고; 상기 제2 내지 제N-1 구리 스트립의 일단은 제1 연결홀과 연결되며, 타단은 각각 순차적으로 제2 내지 제N-1 연결홀과 연결되고, 제2 구리 스트립의 타단은 제2 연결홀과 연결되며, 제3 구리 스트립의 타단은 제3 연결홀과 연결되고, 순차적으로 유추하는 것을 특징으로 하는 다기능 회로판 검출 모듈.

In the multifunctional circuit board detection module,

This includes a PCB test board, wherein the PCB test board is a multilayer circuit board, and includes first to Nth copper layers sequentially installed from top to bottom, a total of N-layer copper layers, and N is an even number greater than 6 ; One or more test blocks are installed on the PCB test board, the test block includes a first through-hole group and a second through-hole group, and the first through-hole group is 6 to 12 arranged in three lines. Including test holes, the test holes are through holes having the same hole diameter; The second through-hole group includes a first connection hole to an N-1th connection hole, a total of N-1 connection holes, and the connection holes are through holes having the same hole diameter; Hole copper is installed in the test hole and the connection hole;

A first pack copper block corresponding to the first through-hole group is provided in the first copper layer; An Nth pack copper block corresponding to the first through-hole group is provided in the Nth copper layer; The first and Nth pack copper blocks are connected to hole copper in all test holes;

The second to N-1th copper strips corresponding to the first through-hole group are sequentially installed in the second to N-1th copper layers, respectively, a total of N-2 copper strips, and in the second copper layer A second copper strip corresponding to the first through-hole group is provided, and a third copper strip corresponding to the first through-hole group is provided in the third copper layer, and inferred sequentially; The width of the narrowest copper strip inside the same test block is the same; The second to N-1th copper strips are curved along the upper and lower sides of the test holes of each line in the first through-hole group, and correspond to each test hole in the second to N-1th copper layers, respectively. A cyclic copper free region is formed; The width of the annular copper free regions of the same test block is the same; One end of the second to N-1th copper strip is connected to a first connection hole, the other end is sequentially connected to the second to N-1th connection hole, and the other end of the second copper strip is a second connection hole And the other end of the third copper strip is connected to the third connection hole, and is sequentially inferred.

제1 및 제N 구리층에 제2 관통홀 그룹의 모든 연결홀에 대응되게 구리 홀 링이 설치되어 있고; 상기 제2 내지 제N-1 구리층에 제1 연결홀에 대응되게 구리 홀 링이 설치되어 있으며; 제2 내지 제N-1 구리층에 제2 내지 제N-1 연결홀에 각각 순차적으로 대응되게 구리 홀 링이 설치되어 있고, 제2 구리층에 제2 연결홀에 대응되게 구리 홀 링이 설치되어 있으며, 제3 구리층에 제3 연결홀에 대응되게 구리 홀 링이 설치되어 있고, 순차적으로 유추하며; 상기 구리 홀 링은 상응한 연결홀의 홀 구리와 연결되고; 상기 제2 내지 제N-1 구리 스트립의 양단은 구리층에 대응되게 설치되는 두 개의 구리 홀 링과 각각 연결되는 것을 특징으로 하는 다기능 회로판 검출 모듈.

The method of claim 1,

Copper hole rings are provided in the first and Nth copper layers to correspond to all connection holes of the second through-hole group; A copper hole ring is provided in the second to N-1th copper layers to correspond to the first connection holes; Copper hole rings are installed in the 2nd to N-1th copper layers to correspond sequentially to the 2nd to N-1th connection holes, respectively, and the copper hole rings are installed in the second copper layer to correspond to the second connection holes A copper hole ring is provided in the third copper layer to correspond to the third connection hole, and is sequentially inferred; The copper hole ring is connected to the hole copper of the corresponding connection hole; Both ends of the second to N-1th copper strips are respectively connected to two copper hole rings installed to correspond to the copper layer.

상기 제2 내지 제N-1 구리 스트립에서 제1 관통홀 그룹 내부의 각 라인의 테스트 홀 사이에 위치하는 부분에 구리 브릿지가 각각 형성되고; 동일한 구리 스트립에서 서로 인접한 구리 브릿지 사이의 최소 거리는 0.1mm보다 크거나 같은 것을 특징으로 하는 다기능 회로판 검출 모듈.

The method of claim 1,

Copper bridges are formed in portions of the second to N-1th copper strips positioned between test holes of each line in the first through-hole group; Multifunctional circuit board detection module, characterized in that the minimum distance between adjacent copper bridges in the same copper strip is greater than or equal to 0.1mm.

서로 인접한 연결홀의 홀 간격은 1.0 내지 1.1mm이고; 테스트 홀과 연결홀의 홀 직경은 0.2mm이며; 테스트 홀과 연결홀 사이의 거리는 1mm보다 큰 것을 특징으로 하는 다기능 회로판 검출 모듈.

The method according to any one of claims 1 to 3,

The hole spacing of the connecting holes adjacent to each other is 1.0 to 1.1 mm; The hole diameter of the test hole and the connection hole is 0.2mm; Multifunctional circuit board detection module, characterized in that the distance between the test hole and the connection hole is greater than 1mm.

상기 제1 관통홀 그룹은 3라인으로 배열된 9개의 테스트 홀을 포함하는 것을 특징으로 하는 다기능 회로판 검출 모듈.

The method according to any one of claims 1 to 3,

The first through-hole group is a multifunctional circuit board detection module, characterized in that it comprises nine test holes arranged in three lines.

PCB 테스트 보드에 6개의 테스트 블록이 설치되어 있는 것을 특징으로 하는 다기능 회로판 검출 모듈.

The method according to any one of claims 1 to 3,

A multifunctional circuit board detection module, characterized in that 6 test blocks are installed on the PCB test board.

상기 6개의 테스트 블록에서 고리형 구리 프리 영역의 폭은 각각 0.075mm, 0.1mm, 0.127mm, 0.15mm, 0.178mm, 0.2mm인 것을 특징으로 하는 다기능 회로판 검출 모듈.

The method of claim 6,

The width of the ring-shaped copper free region in the six test blocks is 0.075mm, 0.1mm, 0.127mm, 0.15mm, 0.178mm, 0.2mm, respectively.

상기 6개의 테스트 블록에서 구리 스트립이 가장 좁은 곳의 폭은 각각 0.075mm, 0.1mm, 0.127mm, 0.15mm, 0.178mm, 0.2mm인 것을 특징으로 하는 다기능 회로판 검출 모듈.

The method of claim 6,

In the six test blocks, the width of the narrowest part of the copper strip is 0.075mm, 0.1mm, 0.127mm, 0.15mm, 0.178mm, and 0.2mm, respectively.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201710630682.8A CN107509302A (en) | 2017-07-28 | 2017-07-28 | A kind of multi-functional wiring board detection module and detection method |

| CN201710630682.8 | 2017-07-28 | ||

| PCT/CN2017/103329 WO2019019339A1 (en) | 2017-07-28 | 2017-09-26 | Multi-functional circuit board detection module and detection method |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20190049826A KR20190049826A (en) | 2019-05-09 |

| KR102215664B1 true KR102215664B1 (en) | 2021-02-10 |

Family

ID=60690340

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020197010197A KR102215664B1 (en) | 2017-07-28 | 2017-09-26 | Multifunctional circuit board detection module and detection method |

Country Status (3)

| Country | Link |

|---|---|

| KR (1) | KR102215664B1 (en) |

| CN (1) | CN107509302A (en) |

| WO (1) | WO2019019339A1 (en) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN108008288B (en) * | 2017-12-29 | 2020-05-12 | 大连崇达电路有限公司 | Copper thickness self-recognition and glue-shortage risk early warning system for copper-free area of multilayer circuit board |

| CN108430165B (en) * | 2018-02-08 | 2019-12-20 | 广州兴森快捷电路科技有限公司 | PCB etching detection method |

| CN108901128B (en) * | 2018-08-26 | 2021-12-28 | 深圳华秋电子有限公司 | Double-sided flexible PCB |

| CN109287082B (en) * | 2018-11-28 | 2022-02-18 | 郑州云海信息技术有限公司 | Testing method and device for circuit board easy to short circuit |

| CN114205991B (en) * | 2020-09-18 | 2024-05-03 | 重庆方正高密电子有限公司 | PCB (printed circuit board) |

| CN112188726B (en) * | 2020-10-20 | 2021-11-12 | 深圳市强达电路股份有限公司 | Multilayer board for performing V _ CUT depth detection through electrical test |

| CN113435156B (en) * | 2021-07-08 | 2022-07-22 | 苏州悦谱半导体有限公司 | Method for adjusting copper surface data interval of printed circuit board and intelligently judging copper bridge supplement |

| CN113660773B (en) * | 2021-07-14 | 2022-10-21 | 深圳市景旺电子股份有限公司 | Reliability test board and manufacturing method thereof |

| CN113613394B (en) * | 2021-08-04 | 2023-06-09 | 吉安满坤科技股份有限公司 | Manufacturing process of chip IC packaging printed circuit board |

| CN113740713B (en) * | 2021-09-09 | 2024-02-13 | 博敏电子股份有限公司 | Test board for detecting whether PCB is incomplete in glue removal and test method thereof |

| CN114531775A (en) * | 2022-03-04 | 2022-05-24 | 生益电子股份有限公司 | Printed circuit board |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104582331A (en) | 2014-12-31 | 2015-04-29 | 广州兴森快捷电路科技有限公司 | Inner-layer deviation detecting method for multi-layer circuit board |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4894606A (en) * | 1988-07-07 | 1990-01-16 | Paur Tom R | System for measuring misregistration of printed circuit board layers |

| JPH0661652A (en) * | 1992-05-27 | 1994-03-04 | Nec Corp | Inspection method for multilayer printed wiring board |

| JPH10270860A (en) * | 1997-03-26 | 1998-10-09 | Meidensha Corp | Multilayered printed wiring board |

| JPH11112152A (en) * | 1997-10-03 | 1999-04-23 | Matsushita Electric Ind Co Ltd | Multilayered printed board for mounting flip chip |

| JP2008218925A (en) * | 2007-03-07 | 2008-09-18 | Fujitsu Ltd | Wiring board, manufacturing method of wiring board and inspection method thereof |

| CN104378909A (en) * | 2013-08-12 | 2015-02-25 | 英业达科技有限公司 | Printed circuit board |

| CN106455293B (en) * | 2016-09-27 | 2019-05-17 | 惠州市金百泽电路科技有限公司 | A kind of production method having a size of 500mm*800mm or more multilayer large scale High speed rear panel |

-

2017

- 2017-07-28 CN CN201710630682.8A patent/CN107509302A/en active Pending

- 2017-09-26 KR KR1020197010197A patent/KR102215664B1/en active IP Right Grant

- 2017-09-26 WO PCT/CN2017/103329 patent/WO2019019339A1/en active Application Filing

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104582331A (en) | 2014-12-31 | 2015-04-29 | 广州兴森快捷电路科技有限公司 | Inner-layer deviation detecting method for multi-layer circuit board |

Also Published As

| Publication number | Publication date |

|---|---|

| CN107509302A (en) | 2017-12-22 |

| KR20190049826A (en) | 2019-05-09 |

| WO2019019339A1 (en) | 2019-01-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102215664B1 (en) | Multifunctional circuit board detection module and detection method | |

| CN101882591B (en) | Detection method of wafer | |

| CN103687315B (en) | Designing method of punching alignment target | |

| KR101380478B1 (en) | Area classifying device, substrate detecting device and method for classifying area | |

| CN107092757B (en) | Method for checking through hole pressure dividing line in PCB design | |

| CN103796417B (en) | Circuit board and preparation method thereof | |

| CN106197250A (en) | The method of testing of pcb board internal layer off normal | |

| CN104918423A (en) | Manufacturing method for circuit board capable of detecting inner-layer pore ring | |

| US11246212B2 (en) | Printed circuit board deformable in both length and width | |

| KR101572089B1 (en) | Method of defect inspection for printed circuit board | |

| CN103415165B (en) | A kind of method of testing HDI wiring board blind hole quality | |

| US20140144691A1 (en) | Method for shortening via stub and printed circuit board designed based on the method | |

| CN108333496B (en) | Rapid test method for precision capability of flying probe machine capacitance method | |

| KR100797690B1 (en) | Printed circuit board | |

| CN104619114A (en) | PCB (printed circuit board) with embedded resistors and embedded resistor test method | |

| CN204408747U (en) | A kind of have the pcb board burying resistance | |

| CN116546750A (en) | Automatic copper drawing method for PCB | |

| CN206517662U (en) | Edges of boards wad cutter error-proof structure | |

| CN109714896B (en) | Method for improving local deformation of inner sleeve plate of large spliced board of multilayer printed circuit | |

| DE602005006745D1 (en) | METHOD FOR MAGNIFYING A ROUTING DENSITY FOR A PCB AND SUCH A PCB | |

| JP6272682B2 (en) | Printed circuit board continuity testing method | |

| US20070248800A1 (en) | Multilayer board having layer configuration indicator portion | |

| CN203774318U (en) | Stress migration test structure | |

| US7185427B2 (en) | Method for making electrical connections to an element on printed circuit board | |

| CN104465621B (en) | Dual graphing electrical testing structure and monitoring method |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant |