KR102215664B1 - 다기능 회로판 검출 모듈 및 검출 방법 - Google Patents

다기능 회로판 검출 모듈 및 검출 방법 Download PDFInfo

- Publication number

- KR102215664B1 KR102215664B1 KR1020197010197A KR20197010197A KR102215664B1 KR 102215664 B1 KR102215664 B1 KR 102215664B1 KR 1020197010197 A KR1020197010197 A KR 1020197010197A KR 20197010197 A KR20197010197 A KR 20197010197A KR 102215664 B1 KR102215664 B1 KR 102215664B1

- Authority

- KR

- South Korea

- Prior art keywords

- copper

- hole

- test

- connection

- holes

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0296—Conductive pattern lay-out details not covered by sub groups H05K1/02 - H05K1/0295

- H05K1/0298—Multilayer circuits

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0266—Marks, test patterns or identification means

- H05K1/0268—Marks, test patterns or identification means for electrical inspection or testing

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/16—Inspection; Monitoring; Aligning

- H05K2203/166—Alignment or registration; Control of registration

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

Abstract

다기능 회로판 검출 모듈의 검출 방법은 각 하나의 테스트 블록을 각각 테스트하고, 각 하나의 테스트 블록에서 제2 내지 제N-1 구리 스트립이 도통하는 지의 여부를 순차적으로 테스트하며, 구체적으로는 제1 연결홀과 기타 연결홀 사이에 도통하는 지의 여부를 검출하고, 도통하지 않으면, 내층 공정을 진행할 시 과도하게 에칭한 것으로 판정하고, 상이한 테스트 블록의 테스트 결과 및 각 테스트 블록에서 구리 스트립이 가장 좁은 곳의 폭을 결합하여 과도한 에칭량을 판정하는 단계; 각 하나의 테스트 블록을 각각 테스트하고, 각 하나의 테스트 블록에서 제2 내지 제N-1 구리층 사이에 도통하는 지의 여부를 순차적으로 테스트하며, 구체적으로는 제2 내지 제N-1 연결홀 사이에 도통하는 지의 여부를 검출하고, 도통하면, 라미네이션을 진행할 시 층 편이가 발생한 것으로 판정하고; 모든 구리층이 모두 도통하면, 드릴링 시 홀 편이가 발생한 것으로 판정하며, 상이한 테스트 블록의 테스트 결과 및 각 테스트 블록에서 고리형 구리 프리 영역의 폭을 결합하여 홀 편이의 편이량을 판정하는 단계를 포함한다. 내층, 라미네이션, 드릴링 공정의 제어 요구에 한하여 테스트 블록을 설계하고, 내층 공정 중의 에칭량, 라미네이션 공정 중의 층 편이, 드릴링 공정 중의 홀 편이에 대해 판단할 수 있으며, 이로써 회로판 제품이 정식으로 제작되기 전에 신빈성 있는 참조를 제공할 수 있고, 엔지니어링 자료 및 공정 실시의 조절을 진행하여, 제조 공정 능력 및 제품 품질을 향상시킨다.

Description

본 발명은 회로판 공정 분야에 관한 것으로, 특히는 다기능 회로판 검출 모듈 및 검출 방법에 관한 것이다.

PCB 생산 과정에서, 각각의 공정의 실제 작업 능력(제조 공정 능력)의 높고 낮음은 이미 PCB 기업의 핵심 경쟁력으로 자리 잡았고, 제조 공정 능력의 향상 역시 기업 발전의 수요로서, 제조 과정 중 각각의 공정의 제조 공정 능력을 어떻게 효과적으로 모니터링하여, 제조 공정 능력의 향상에 참조적인 근거를 제공할 것인지는 PCB 기업이 중점적으로 해결해야 할 과제로 남았는 바, 특히는 다층판(6층 이상) 내층 수축 및 팽창, 내층 에칭 능력, 라미네이션 수축 및 팽창, 라미네이션 층 편이, 드릴링 수축 및 팽창, 드릴링 홀 편이 등 문제이며, 불량이 발생하면 제품의 기능에 직접적인 영향을 일으킬 수 있다.

상기 문제에 한하여, 본 발명은 다기능 회로판 검출 모듈을 제공하는 데 그 목적이 있다.

본 발명은 PCB 테스트 보드를 포함하고, 상기 PCB 테스트 보드는 다층 회로판이며, 상측으로부터 하측으로 순차적으로 설치되는 제1 내지 제N 구리층을 포함하고, 총 N층 구리층이며, N은 6보다 큰 짝수이고;

PCB 테스트 보드에 한 개 또는 다수 개의 테스트 블록이 설치되어 있으며, 상기 테스트 블록은 제1 관통홀 그룹 및 제2 관통홀 그룹을 포함하고, 상기 제1 관통홀 그룹은 3라인으로 배열된 6 내지 12개의 테스트 홀을 포함하며, 상기 테스트 홀은 홀 직경이 동일한 관통홀이고; 제2 관통홀 그룹은 제1 연결홀 내지 제N-1 연결홀을 포함하며, 총 N-1개 연결홀이고, 상기 연결홀은 홀 직경이 동일한 관통홀이며; 상기 테스트 홀과 연결홀에 모두 홀 구리가 설치되어 있고;

제1 구리층에 제1 관통홀 그룹과 대응되는 제1 팩 구리 블록이 설치되어 있으며; 제N 구리층에 제1 관통홀 그룹과 대응되는 제N 팩 구리 블록이 설치되어 있고; 상기 제1 및 제N 팩 구리 블록은 모든 테스트 홀의 홀 구리와 연결되며;

상기 제2 내지 제N-1 구리층에 제1 관통홀 그룹과 대응되는 제2 내지 제N-1 구리 스트립이 각각 순차적으로 설치되어 있고, 총 N-2개 구리 스트립이며, 제2 구리층에 제1 관통홀 그룹과 대응되는 제2 구리 스트립이 설치되어 있고, 제3 구리층에 제1 관통홀 그룹과 대응되는 제3 구리 스트립이 설치되어 있으며, 순차적으로 유추하고; 동일한 테스트 블록 내부의 구리 스트립이 가장 좁은 곳의 폭은 동일하며; 상기 제2 내지 제N-1 구리 스트립은 모두 제1 관통홀 그룹 내부의 각 라인의 테스트 홀의 상하측을 따라 휘어지게 둘러싸고, 각각 제2 내지 제N-1 구리층에서 각 하나의 테스트 홀에 대응되게 고리형 구리 프리 영역이 형성되며; 동일한 테스트 블록의 고리형 구리 프리 영역의 폭은 동일하고; 상기 제2 내지 제N-1 구리 스트립의 일단은 모두 제1 연결홀과 연결되며, 타단은 각각 순차적으로 제2 내지 제N-1 연결홀과 연결되고, 제2 구리 스트립의 타단은 제2 연결홀과 연결되며, 제3 구리 스트립의 타단은 제3 연결홀과 연결되고, 순차적으로 유추한다.

바람직하게, 제1 및 제N 구리층에 제2 관통홀 그룹의 모든 연결홀에 대응되게 구리 홀 링이 설치되어 있고; 상기 제2 내지 제N-1 구리층에 모두 제1 연결홀에 대응되게 구리 홀 링이 설치되어 있으며; 제2 내지 제N-1 구리층에 제2 내지 제N-1 연결홀에 각각 순차적으로 대응되게 구리 홀 링이 설치되어 있고, 제2 구리층에 제2 연결홀에 대응되게 구리 홀 링이 설치되어 있으며, 제3 구리층에 제3 연결홀에 대응되게 구리 홀 링이 설치되어 있고, 순차적으로 유추하며; 상기 구리 홀 링은 상응한 연결홀의 홀 구리와 연결되고; 상기 제2 내지 제N-1 구리 스트립의 양단은 구리층에 대응되게 설치되는 두 개의 구리 홀 링과 각각 연결된다.

바람직하게, 상기 제2 내지 제N-1 구리 스트립에서 제1 관통홀 그룹 내부의 각 라인의 테스트 홀 사이에 위치하는 부분에 구리 브릿지가 각각 형성되고; 동일한 구리 스트립에서 서로 인접한 구리 브릿지 사이의 최소 거리는 0.1mm보다 크거나 같다.

또한, 제 1항 내지 제 3항 중 어느 한 항에 있어서, 서로 인접한 연결홀의 홀 간격은 1.0 내지 1.1mm이고; 테스트 홀과 연결홀의 홀 직경은 모두 0.2mm이며; 테스트 홀과 연결홀 사이의 거리는 1mm보다 크다.

또한, 상기 제1 관통홀 그룹은 3라인으로 배열된 9개의 테스트 홀을 포함한다.

또한, PCB 테스트 보드에 6개의 테스트 블록이 설치되어 있다.

또한, 상기 6개의 테스트 블록에서 고리형 구리 프리 영역의 폭은 각각 0.075mm, 0.1mm, 0.127mm, 0.15mm, 0.178mm, 0.2mm이다.

또한, 상기 6개의 테스트 블록에서 구리 스트립이 가장 좁은 곳의 폭은 각각 0.075mm, 0.1mm, 0.127mm, 0.15mm, 0.178mm, 0.2mm이다.

본 발명은 다기능 회로판 검출 모듈을 사용하는 검출 방법을 더 제공하며, 내층, 라미네이션, 드릴링 공정을 완료한 후의 제조된 다기능 회로판 검출 모듈에 대해, 하기의 테스트 항목을 진행하는 바,

각 하나의 테스트 블록을 각각 테스트하고, 각 하나의 테스트 블록에서 제2 내지 제N-1 구리 스트립이 도통하는 지의 여부를 순차적으로 테스트하며, 구체적으로는 제1 연결홀과 기타 연결홀 사이에 도통하는 지의 여부를 검출하고, 도통하지 않으면, 내층 공정을 진행할 시 과도하게 에칭한 것으로 판정하고, 상이한 테스트 블록의 테스트 결과 및 각 테스트 블록에서 구리 스트립이 가장 좁은 곳의 폭을 결합하여 과도한 에칭량을 판정하는 단계;

각 하나의 테스트 블록을 각각 테스트하고, 각 하나의 테스트 블록에서 제2 내지 제N-1 구리층 사이에 도통하는 지의 여부를 순차적으로 테스트하며, 구체적으로는 제2 내지 제N-1 연결홀 사이에 도통하는 지의 여부를 검출하고, 도통하면, 라미네이션을 진행할 시 층 편이가 발생한 것으로 판정하고; 모든 구리층이 모두 도통하면, 드릴링할 시 홀 편이가 발생한 것으로 판정하며, 상이한 테스트 블록의 테스트 결과 및 각 테스트 블록의 고리형 구리 프리 영역의 폭을 결합하여 홀 편이의 편이량을 판정하는 단계를 포함한다.

바람직하게, 각 하나의 테스트 블록에서 제2 내지 제N-1 구리층 사이에 도통하는 지의 여부를 순차적으로 테스트할 시, 제2 내지 제N-1 구리층에서 임의의 두 개의 구리층이 도통하면, 층 편이가 상기 두 개의 구리층 사이에서 발생하는 것으로 판정할 수 있고, 상이한 테스트 블록의 테스트 결과 및 각 테스트 블록에서 고리형 구리 프리 영역의 폭을 결합하여 층 편이의 편이량을 판정하며;

제2 내지 제N-1 구리층에서 임의의 다수의 구리층이 도통하면, 모든 구리층에서 모두 층 편이가 발생하는 것으로 판정할 수 있고, 상이한 테스트 블록의 테스트 결과 및 각 테스트 블록에서 고리형 구리 프리 영역의 폭을 결합하여 각 구리층의 층 편이의 편이량을 판정한다.

본 발명은 내층, 라미네이션, 드릴링 공정의 제어 요구에 한하여 테스트 블록을 설계하고, 내층 공정 중의 에칭량, 라미네이션 공정 중의 층 편이, 드릴링 공정 중의 홀 편이를 간편하고 신속하게 판단할 수 있으며, 이로써 회로판 제품이 정식으로 제작되기 전에 신빈성 있는 참조를 제공할 수 있고, 엔지니어링 자료 및 공정 실시의 조절을 진행하여, 제조 공정 능력을 향상시키며, 제품의 품질을 향상시킨다.

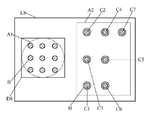

도 1은 다기능 회로판 검출 모듈의 실시예의 구조도이다.

도 2는 다기능 회로판 검출 모듈의 실시예의 제1 구리층 중 테스트 블록 모식도이다.

도 3은 다기능 회로판 검출 모듈의 실시예의 제2 구리층 중 테스트 블록 모식도이다.

도 4는 다기능 회로판 검출 모듈의 실시예의 제3 구리층 중 테스트 블록 모식도이다.

도 5는 다기능 회로판 검출 모듈의 실시예의 제4 구리층 중 테스트 블록 모식도이다.

도 6은 다기능 회로판 검출 모듈의 실시예의 제5 구리층 중 테스트 블록 모식도이다.

도 7은 다기능 회로판 검출 모듈의 실시예의 제6 구리층 중 테스트 블록 모식도이다.

도 8은 다기능 회로판 검출 모듈의 실시예의 제7 구리층 중 테스트 블록 모식도이다.

도 9는 다기능 회로판 검출 모듈의 실시예의 제8 구리층 중 테스트 블록 모식도이다.

도 2는 다기능 회로판 검출 모듈의 실시예의 제1 구리층 중 테스트 블록 모식도이다.

도 3은 다기능 회로판 검출 모듈의 실시예의 제2 구리층 중 테스트 블록 모식도이다.

도 4는 다기능 회로판 검출 모듈의 실시예의 제3 구리층 중 테스트 블록 모식도이다.

도 5는 다기능 회로판 검출 모듈의 실시예의 제4 구리층 중 테스트 블록 모식도이다.

도 6은 다기능 회로판 검출 모듈의 실시예의 제5 구리층 중 테스트 블록 모식도이다.

도 7은 다기능 회로판 검출 모듈의 실시예의 제6 구리층 중 테스트 블록 모식도이다.

도 8은 다기능 회로판 검출 모듈의 실시예의 제7 구리층 중 테스트 블록 모식도이다.

도 9는 다기능 회로판 검출 모듈의 실시예의 제8 구리층 중 테스트 블록 모식도이다.

본 기술분야의 통상의 기술자가 본 발명의 기술내용을 간편하게 이해하도록 하기 위해, 이하 도면 및 실시예를 결부하여 본 발명을 더욱 상세하게 설명한다.

도 1에 도시된 다기능 회로판 검출 모듈은, PCB 테스트 보드(1)를 포함하고, 상기 PCB 테스트 보드는 다층 회로판이며, 상측으로부터 하측으로 순차적으로 설치되는 제1 구리층(L1), 제2 구리층 L2…제8 구리층(L8)을 포함하고, 총 8층 구리층이다.

PCB 테스트 보드(1)에 6개의 테스트 블록(2)이 설치되어 있고, 그중의 하나의 테스트 블록은 도 2 내지 도 9에 도시된 바와 같으며, 각 하나의 테스트 블록은 제1 관통홀 그룹(A1) 및 제2 관통홀 그룹(A2)을 포함하고, 제1 관통홀 그룹(A1)은 3라인으로 배열된 9개의 테스트 홀(B)을 포함하며; 제2 관통홀 그룹(A2)은 제1 연결홀(C1), 제2 연결홀(C2)…제7 연결홀(C7)을 포함하고, 총 7개의 연결홀이며, 테스트 홀과 연결홀은 모두 홀 직경이 동일한 관통홀이고, 홀 내부에 모두 홀 구리가 설치되어 있다. 서로 인접한 연결홀의 홀 간격은 1.1mm이고; 테스트 홀과 연결홀의 홀 직경은 모두 0.2mm이며; 테스트 홀과 연결홀 사이의 거리는 1mm보다 크다.

제1 구리층(L1)에 제1 관통홀 그룹(A1)과 대응되는 제1 팩 구리 블록(D1)이 설치되어 있고; 제8 구리층(L8)에 제1 관통홀 그룹(A1)과 대응되는 제8 팩 구리 블록(D8)이 설치되어 있으며; 제1 및 제8 팩 구리 블록은 모든 테스트 홀 내부의 홀 구리와 연결되고; 제2 내지 제7 구리층에 제1 관통홀 그룹과 대응되는 제2 구리 스트립(E2), 제3 구리 스트립(E3)…제7 구리 스트립(E7)이 각각 순차적으로 설치되어 있으며, 6개의 테스트 블록에서 구리 스트립이 가장 좁은 곳의 폭은 각각 0.075mm, 0.1mm, 0.127mm, 0.15mm, 0.178mm, 0.2mm로 설치된다. 내층이 상이한 구리 두께에 따라, 상이한 구리 스트립 폭을 설계할 수 있고, 구리 스트립의 폭이 내층 에칭 능력을 검증하기 위한 것이기에, 내층 구리 두께가 상이하고, 에칭량이 같지 않다.

제2 내지 제7 구리 스트립에서 제1 관통홀 그룹 내부의 각 라인의 테스트 홀 사이에 위치하는 부분에 구리 브릿지(F)가 각각 형성되고; 동일한 구리 스트립에서 서로 인접한 구리 브릿지(F) 사이의 최소 거리는 0.1mm이다.

제2 내지 제7 구리 스트립은 모두 제1 관통홀 그룹 내부의 각 라인의 테스트 홀의 상하측을 따라 휘어지게 둘러싸고, 제2 내지 제7 구리층에서 각 하나의 테스트 홀에 대응되게 고리형 구리 프리 영역(G)을 각각 형성하며; 6개의 테스트 블록에서 고리형 구리 프리 영역의 폭은 각각 0.075mm, 0.1mm, 0.127mm, 0.15mm, 0.178mm, 0.2mm로 설치된다.

제2 내지 제7 구리 스트립의 일단은 모두 제1 연결홀과 연결되고, 타단은 제2 내지 제7 연결홀과 각각 순차적으로 연결되며, 제2 구리 스트립의 타단은 제2 연결홀과 연결되고, 제3 구리 스트립의 타단은 제3 연결홀과 연결되며, 순차적으로 유추한다.

구리 스트립 및 상응한 연결홀의 간편한 연결과 데스트할 시의 간편 신속을 위해, 제1 및 제8 구리층에서 제2 관통홀 그룹의 모든 연결홀에 대응되게 구리 홀 링(H)이 설치되어 있고; 제2 내지 제7 구리층에 모두 제1 연결홀에 대응되게 구리 홀 링(H)이 설치되어 있으며; 제2 내지 제7 구리층에서 제2 내지 제7 연결홀에 각각 순차적으로 대응되게 구리 홀 링(H)이 설치되어 있고, 제2 구리층에 제2 연결홀에 대응되게 구리 홀 링이 설치되어 있으며, 제3 구리층에 제3 연결홀에 대응되게 구리 홀 링이 설치되어 있고, 순차적으로 유추하며; 구리 홀 링은 상응한 연결홀의 홀 구리와 연결되고; 제2 내지 제7 구리 스트립의 양단은 각각 구리층에 대응되게 설치되는 두 개의 구리 홀 링(H)과 연결된다.

상기 실시예에 언급되는 다기능 회로판 검출 모듈을 이용하여 검출을 진행할 시, 내층, 라미네이션, 드릴링 공정을 완료한 후의 제조된 다기능 회로판 검출 모듈에 대해, 하기의 테스트 항목을 진행하는 바,

각 하나의 테스트 블록을 각각 테스트하고, 각 하나의 테스트 블록에서 제2 내지 제7 구리 스트립이 도통하는 지의 여부를 순차적으로 테스트하며, 구체적으로는 제1 연결홀과 기타 연결홀 사이에 도통하는 지의 여부를 검출하고, 도통하지 않으면, 내층 공정을 진행할 시 과도하게 에칭한 것으로 판정하고, 상이한 테스트 블록의 테스트 결과 및 각 테스트 블록에서 구리 스트립이 가장 좁은 곳의 폭을 결합하여 과도한 에칭량을 판정한다.

각 하나의 테스트 블록을 각각 테스트하고, 각 하나의 테스트 블록에서 제2 내지 제7 구리층 사이에 도통하는 지의 여부를 순차적으로 테스트하며, 구체적으로는 제2 내지 제7 연결홀 사이에 도통하는 지의 여부를 검출하고, 도통하면, 라미네이션을 진행할 시 층 편이가 발생한 것으로 판정하고; 제2 내지 제7 구리층에서 임의의 두 개의 구리층이 도통하면, 층 편이가 상기 두 개의 구리층 사이에서 발생하는 것으로 판정할 수 있고, 상이한 테스트 블록의 테스트 결과 및 각 테스트 블록에서 고리형 구리 프리 영역의 폭을 결합하여 층 편이의 편이량을 판정하며; 제2 내지 제7 구리층의 임의의 다수의 구리층이 도통하면, 모든 구리층에서 모두 층 편이가 발생하는 것으로 판정할 수 있고, 상이한 테스트 블록의 테스트 결과 및 각 테스트 블록에서 고리형 구리 프리 영역의 폭을 결합하여 각 층의 층 편이의 편이량을 판정한다.

모든 구리층이 모두 도통하면, 드릴링할 시 홀 편이가 발생한 것으로 판정하며, 상이한 테스트 블록의 테스트 결과 및 각 테스트 블록의 고리형 구리 프리 영역의 폭을 결합하여 홀 편이의 편이량을 판정한다.

상기 내용은 본 발명의 구체적인 실시예로서, 그 묘사는 비교적 구체적이고 상세하지만, 이로써 본 발명의 특허범위를 한정한다고 할 수 없다. 반드시 지적해야 하는 바, 본 기술분야의 통상의 기술자에게 있어서, 본 발명의 구상을 벗어나지 않는 전제하에서, 약간의 변형과 개선을 진행할 수 있는 바, 이러한 자명한 교체 형식은 본 발명의 보호범위에 속한다.

Claims (10)

- 다기능 회로판 검출 모듈에 있어서,

이는 PCB 테스트 보드를 포함하고, 상기 PCB 테스트 보드는 다층 회로판이며, 상측으로부터 하측으로 순차적으로 설치되는 제1 내지 제N 구리층을 포함하고, 총 N층 구리층이며, N은 6보다 큰 짝수이고; PCB 테스트 보드에 한 개 또는 다수 개의 테스트 블록이 설치되어 있으며, 상기 테스트 블록은 제1 관통홀 그룹 및 제2 관통홀 그룹을 포함하고, 상기 제1 관통홀 그룹은 3라인으로 배열된 6 내지 12개의 테스트 홀을 포함하며, 상기 테스트 홀은 홀 직경이 동일한 관통홀이고; 제2 관통홀 그룹은 제1 연결홀 내지 제N-1 연결홀을 포함하며, 총 N-1개 연결홀이고, 상기 연결홀은 홀 직경이 동일한 관통홀이며; 상기 테스트 홀과 연결홀에 홀 구리가 설치되어 있고;

제1 구리층에 제1 관통홀 그룹과 대응되는 제1 팩 구리 블록이 설치되어 있으며; 제N 구리층에 제1 관통홀 그룹과 대응되는 제N 팩 구리 블록이 설치되어 있고; 상기 제1 및 제N 팩 구리 블록은 모든 테스트 홀의 홀 구리와 연결되며;

상기 제2 내지 제N-1 구리층에 제1 관통홀 그룹과 대응되는 제2 내지 제N-1 구리 스트립이 각각 순차적으로 설치되어 있고, 총 N-2개 구리 스트립이며, 제2 구리층에 제1 관통홀 그룹과 대응되는 제2 구리 스트립이 설치되어 있고, 제3 구리층에 제1 관통홀 그룹과 대응되는 제3 구리 스트립이 설치되어 있으며, 순차적으로 유추하고; 동일한 테스트 블록 내부의 구리 스트립이 가장 좁은 곳의 폭은 동일하며; 상기 제2 내지 제N-1 구리 스트립은 제1 관통홀 그룹 내부의 각 라인의 테스트 홀의 상하측을 따라 휘어지게 둘러싸고, 각각 제2 내지 제N-1 구리층에서 각 하나의 테스트 홀에 대응되게 고리형 구리 프리 영역이 형성되며; 동일한 테스트 블록의 고리형 구리 프리 영역의 폭은 동일하고; 상기 제2 내지 제N-1 구리 스트립의 일단은 제1 연결홀과 연결되며, 타단은 각각 순차적으로 제2 내지 제N-1 연결홀과 연결되고, 제2 구리 스트립의 타단은 제2 연결홀과 연결되며, 제3 구리 스트립의 타단은 제3 연결홀과 연결되고, 순차적으로 유추하는 것을 특징으로 하는 다기능 회로판 검출 모듈.

- 제 1항에 있어서,

제1 및 제N 구리층에 제2 관통홀 그룹의 모든 연결홀에 대응되게 구리 홀 링이 설치되어 있고; 상기 제2 내지 제N-1 구리층에 제1 연결홀에 대응되게 구리 홀 링이 설치되어 있으며; 제2 내지 제N-1 구리층에 제2 내지 제N-1 연결홀에 각각 순차적으로 대응되게 구리 홀 링이 설치되어 있고, 제2 구리층에 제2 연결홀에 대응되게 구리 홀 링이 설치되어 있으며, 제3 구리층에 제3 연결홀에 대응되게 구리 홀 링이 설치되어 있고, 순차적으로 유추하며; 상기 구리 홀 링은 상응한 연결홀의 홀 구리와 연결되고; 상기 제2 내지 제N-1 구리 스트립의 양단은 구리층에 대응되게 설치되는 두 개의 구리 홀 링과 각각 연결되는 것을 특징으로 하는 다기능 회로판 검출 모듈.

- 제 1항에 있어서,

상기 제2 내지 제N-1 구리 스트립에서 제1 관통홀 그룹 내부의 각 라인의 테스트 홀 사이에 위치하는 부분에 구리 브릿지가 각각 형성되고; 동일한 구리 스트립에서 서로 인접한 구리 브릿지 사이의 최소 거리는 0.1mm보다 크거나 같은 것을 특징으로 하는 다기능 회로판 검출 모듈.

- 제 1항 내지 제 3항 중 어느 한 항에 있어서,

서로 인접한 연결홀의 홀 간격은 1.0 내지 1.1mm이고; 테스트 홀과 연결홀의 홀 직경은 0.2mm이며; 테스트 홀과 연결홀 사이의 거리는 1mm보다 큰 것을 특징으로 하는 다기능 회로판 검출 모듈.

- 제 1항 내지 제 3항 중 어느 한 항에 있어서,

상기 제1 관통홀 그룹은 3라인으로 배열된 9개의 테스트 홀을 포함하는 것을 특징으로 하는 다기능 회로판 검출 모듈.

- 제 1항 내지 제 3항 중 어느 한 항에 있어서,

PCB 테스트 보드에 6개의 테스트 블록이 설치되어 있는 것을 특징으로 하는 다기능 회로판 검출 모듈.

- 제 6항에 있어서,

상기 6개의 테스트 블록에서 고리형 구리 프리 영역의 폭은 각각 0.075mm, 0.1mm, 0.127mm, 0.15mm, 0.178mm, 0.2mm인 것을 특징으로 하는 다기능 회로판 검출 모듈.

- 제 6항에 있어서,

상기 6개의 테스트 블록에서 구리 스트립이 가장 좁은 곳의 폭은 각각 0.075mm, 0.1mm, 0.127mm, 0.15mm, 0.178mm, 0.2mm인 것을 특징으로 하는 다기능 회로판 검출 모듈.

- 삭제

- 삭제

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201710630682.8A CN107509302A (zh) | 2017-07-28 | 2017-07-28 | 一种多功能线路板检测模块及检测方法 |

| CN201710630682.8 | 2017-07-28 | ||

| PCT/CN2017/103329 WO2019019339A1 (zh) | 2017-07-28 | 2017-09-26 | 一种多功能线路板检测模块及检测方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20190049826A KR20190049826A (ko) | 2019-05-09 |

| KR102215664B1 true KR102215664B1 (ko) | 2021-02-10 |

Family

ID=60690340

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020197010197A KR102215664B1 (ko) | 2017-07-28 | 2017-09-26 | 다기능 회로판 검출 모듈 및 검출 방법 |

Country Status (3)

| Country | Link |

|---|---|

| KR (1) | KR102215664B1 (ko) |

| CN (1) | CN107509302A (ko) |

| WO (1) | WO2019019339A1 (ko) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN108008288B (zh) * | 2017-12-29 | 2020-05-12 | 大连崇达电路有限公司 | 多层线路板无铜区铜厚自识别及缺胶风险预警系统 |

| CN108430165B (zh) * | 2018-02-08 | 2019-12-20 | 广州兴森快捷电路科技有限公司 | Pcb板蚀刻检测方法 |

| CN108901128B (zh) * | 2018-08-26 | 2021-12-28 | 深圳华秋电子有限公司 | 双面柔性pcb板 |

| CN109287082B (zh) * | 2018-11-28 | 2022-02-18 | 郑州云海信息技术有限公司 | 一种易短路线路板的测试方法及装置 |

| CN114205991B (zh) * | 2020-09-18 | 2024-05-03 | 重庆方正高密电子有限公司 | Pcb板 |

| CN112188726B (zh) * | 2020-10-20 | 2021-11-12 | 深圳市强达电路股份有限公司 | 一种通过电测试进行v_cut深度检测的多层板 |

| CN113435156B (zh) * | 2021-07-08 | 2022-07-22 | 苏州悦谱半导体有限公司 | 印刷电路板铜面数据间距调整和智能判断补铜桥的方法 |

| CN113660773B (zh) * | 2021-07-14 | 2022-10-21 | 深圳市景旺电子股份有限公司 | 可靠性测试板及可靠性测试板的制作方法 |

| CN113613394B (zh) * | 2021-08-04 | 2023-06-09 | 吉安满坤科技股份有限公司 | 一种芯片ic封装印制电路板制造工艺 |

| CN113740713B (zh) * | 2021-09-09 | 2024-02-13 | 博敏电子股份有限公司 | 一种检测pcb是否除胶不尽的测试板及其测试方法 |

| CN114531775A (zh) * | 2022-03-04 | 2022-05-24 | 生益电子股份有限公司 | 一种印制电路板 |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104582331A (zh) | 2014-12-31 | 2015-04-29 | 广州兴森快捷电路科技有限公司 | 多层线路板的内层偏位检测方法 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4894606A (en) * | 1988-07-07 | 1990-01-16 | Paur Tom R | System for measuring misregistration of printed circuit board layers |

| JPH0661652A (ja) * | 1992-05-27 | 1994-03-04 | Nec Corp | 多層印刷配線板の検査方法 |

| JPH10270860A (ja) * | 1997-03-26 | 1998-10-09 | Meidensha Corp | 多層プリント配線板 |

| JPH11112152A (ja) * | 1997-10-03 | 1999-04-23 | Matsushita Electric Ind Co Ltd | フリップチップ実装の多層プリント基板 |

| JP2008218925A (ja) * | 2007-03-07 | 2008-09-18 | Fujitsu Ltd | 配線板、配線板の製造方法及び検査方法 |

| CN104378909A (zh) * | 2013-08-12 | 2015-02-25 | 英业达科技有限公司 | 印刷电路板 |

| CN106455293B (zh) * | 2016-09-27 | 2019-05-17 | 惠州市金百泽电路科技有限公司 | 一种尺寸为500mm*800mm以上多层大尺寸高速背板的制作方法 |

-

2017

- 2017-07-28 CN CN201710630682.8A patent/CN107509302A/zh active Pending

- 2017-09-26 KR KR1020197010197A patent/KR102215664B1/ko active IP Right Grant

- 2017-09-26 WO PCT/CN2017/103329 patent/WO2019019339A1/zh active Application Filing

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104582331A (zh) | 2014-12-31 | 2015-04-29 | 广州兴森快捷电路科技有限公司 | 多层线路板的内层偏位检测方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| WO2019019339A1 (zh) | 2019-01-31 |

| CN107509302A (zh) | 2017-12-22 |

| KR20190049826A (ko) | 2019-05-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102215664B1 (ko) | 다기능 회로판 검출 모듈 및 검출 방법 | |

| CN101882591B (zh) | 晶片的检测方法 | |

| CN103687315B (zh) | 冲孔对位靶标的设计方法 | |

| JP5865734B2 (ja) | 領域分類装置、そのプログラム、基板検査装置、および領域分類方法 | |

| CN107092757B (zh) | 一种pcb设计中过孔压分割线的检查方法 | |

| CN103796417B (zh) | 电路板及其制作方法 | |

| CN106197250A (zh) | Pcb板内层偏位的测试方法 | |

| CN104918423A (zh) | 一种可检测内层孔环的线路板制作方法 | |

| US11246212B2 (en) | Printed circuit board deformable in both length and width | |

| KR101572089B1 (ko) | 인쇄회로기판 검사방법 | |

| CN103415165B (zh) | 一种测试hdi线路板盲孔品质的方法 | |

| US20140144691A1 (en) | Method for shortening via stub and printed circuit board designed based on the method | |

| CN108333496B (zh) | 飞针机电容法精度能力的快速测试方法 | |

| KR100797690B1 (ko) | 인쇄회로기판 | |

| CN104619114A (zh) | 一种具有埋阻的pcb板以及埋阻的测试方法 | |

| CN204408747U (zh) | 一种具有埋阻的pcb板 | |

| CN116546750A (zh) | 一种pcb板自动掏铜的方法 | |

| CN206517662U (zh) | 板边靶孔防呆结构 | |

| CN109714896B (zh) | 一种改善多层印制电路大拼板内套板局部形变的方法 | |

| DE602005006745D1 (de) | Verfahren zur vergrösserung einer routing-dichte für eine leiterplatte und eine solche leiterplatte | |

| JP6272682B2 (ja) | プリント配線板の導通検査方法 | |

| US20070248800A1 (en) | Multilayer board having layer configuration indicator portion | |

| CN203774318U (zh) | 应力迁移测试结构 | |

| US7185427B2 (en) | Method for making electrical connections to an element on printed circuit board | |

| CN104465621B (zh) | 双重图形化电学测试结构及监控方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant |