JP4635173B2 - メモリシステムおよびその制御方法 - Google Patents

メモリシステムおよびその制御方法 Download PDFInfo

- Publication number

- JP4635173B2 JP4635173B2 JP2008114863A JP2008114863A JP4635173B2 JP 4635173 B2 JP4635173 B2 JP 4635173B2 JP 2008114863 A JP2008114863 A JP 2008114863A JP 2008114863 A JP2008114863 A JP 2008114863A JP 4635173 B2 JP4635173 B2 JP 4635173B2

- Authority

- JP

- Japan

- Prior art keywords

- memory

- data

- verification

- data amount

- buffer memory

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000015654 memory Effects 0.000 title claims description 374

- 238000000034 method Methods 0.000 title claims description 19

- 238000012795 verification Methods 0.000 claims description 72

- 238000012546 transfer Methods 0.000 claims description 20

- 230000006870 function Effects 0.000 description 17

- 238000010586 diagram Methods 0.000 description 14

- 230000008569 process Effects 0.000 description 6

- 238000003491 array Methods 0.000 description 5

- 230000004044 response Effects 0.000 description 5

- 230000009977 dual effect Effects 0.000 description 4

- 238000006243 chemical reaction Methods 0.000 description 3

- 238000004891 communication Methods 0.000 description 3

- 238000003199 nucleic acid amplification method Methods 0.000 description 3

- 230000003321 amplification Effects 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 238000007726 management method Methods 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 230000000630 rising effect Effects 0.000 description 2

- 101710190962 50S ribosomal protein L9 Proteins 0.000 description 1

- 101000682328 Bacillus subtilis (strain 168) 50S ribosomal protein L18 Proteins 0.000 description 1

- 230000003213 activating effect Effects 0.000 description 1

- 238000013524 data verification Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000010200 validation analysis Methods 0.000 description 1

Images

Landscapes

- Read Only Memory (AREA)

- Memory System (AREA)

Description

2つのSRAM41は、排他的に動作する。例えば、一方のSRAM41がインターナルバスIBを介してバックエンドである不揮発性メモリセルアレイNVARYまたは検証メモリ部5と通信中に、他方のSRAM41がフロントエンドであるI/Oインターフェース部3(外部端子2)と通信する。具体的には、一方のSRAM41がインターナルバスIBと通信する場合、X−Decoder101とY−Decoder101は、S2信号またはS5信号に対応してバックエンドアドレスをスクランブルテーブルSTのスクランブル情報をスクランブルしたデコーディング信号によって複数のSRAMセルを選択する。他方のSRAM41がI/Oインターフェース部3と通信する場合、X−Decoder101とY−Decoder102は、S6信号に対応してフロントエンドアドレスのデコーディング信号によって複数のSRAMセルを選択する。ここで、Y−Decoder101と第1バスコネクタ41A間には、不図示のセレクターが配置され、一方のバッファメモリ41が第1バスコネクタ41Aを介してインターナルバスIBと通信する場合、Y−Decoder101の出力が一方のバッファメモリ41内の第1バスコネクタ41Aへのみ入力される。また、Y−Decoder102とI/Oターミナルコネクタ41B間には、不図示のセレクターが配置され、他方のバッファメモリ41がI/Oターミナルコネクタ41Bを介してI/Oインターフェース部3と通信する場合、Y−Decoder102の出力が他方のバッファメモリ41内のI/Oターミナルコネクタ41Bへのみ入力される。前記インターリーブ通信の場合、一方の第1デコーダD1(X−Decoder101)は、S2信号またはS5信号に対応してバックエンドアドレスをスクランブルテーブルSTのスクランブル情報をスクランブルしたデコーディング信号によって一方のSRAM41内のワード線WLを制御する。他方の第1デコーダD1(X−Decoder101)は、S6信号に対応してフロントエンドアドレスのデコーディング信号によって一方のSRAM41内のワード線WLを制御する。

SRAMアレイSARY2では、WL17〜WL32/BL1〜BL256が活性化される。SRAMアレイSARY3では、WL1〜WL16/BL257〜BL512が活性化される。SRAMアレイSARY4では、WL17〜WL32/BL257〜BL512が活性化される。

例えば、本実施形態では、不揮発性メモリセルアレイNVARYの1ページのデータを1/4分割し、セクタごとにロードする場合を例示したが、本発明はこれに限定されるものではない。さらに大きな記憶容量に対するロード動作、逆に更に分割された小さな記憶容量をごとのロード動作に対しても同様に適用することができる。この場合、検証メモリ部5の記憶容量をロードされる単位に合わせればよい。

また、検証メモリ部5においてリセットされる記憶容量は、例示された場合に限定されることはない。適宜にマルチプレクスしてやれば、ロードされる記憶容量に合わせることができる。

また、検証メモリ部5は、書込みアンプ7または読出しアンプ8と兼用することができる。

また、検証メモリセルアレイ52は、SRAM構成のメモリセルであってもよい。

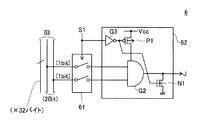

また、検証メモリ部5からバッファメモリ部4へのリセットデータ(“1”)の転送は、インターナルバスIB(x32バイト)を経由することもできる。この場合、バッファメモリ部4内のビット線とインターナルバスIBを選択的に接続する第1バスコネクタ41Aは、S2信号、S5信号、スクランブルテーブルSTとバックエンドアドレスとにより制御される第1スイッチ系統Sw.1のみで構成される。

1A 第2バスコネクタ

1B 第3バスコネクタ

2 外部端子

3 I/Oインターフェース部

4 バッファメモリ部

5 検証メモリ部

6 ブランク判定部

7 書込みアンプ

8 読出しアンプ

9 制御部

9A コマンドデコーダ

9B バックエンドコントローラ

9C フロントエンドコントローラ

41 SRAM

41A 第1バスコネクタ

41B I/Oターミナルコネクタ

51 第4バスコネクタ

52、52A、52B 検証メモリセルアレイ

53 マルチプレクサ

61 第5バスコネクタ

62 ブランク判定回路

CB コアバス

D1 第1デコーダ

D2 第2デコーダ

D3 第3デコーダ

IB インターナルバス

NVARY 不揮発性メモリセルアレイ

SARY SRAMアレイ

ST スクランブルテーブル

Claims (11)

- 不揮発性メモリと、

前記不揮発性メモリと外部端子との間に介在して、外部との1回の読出しまたは/および書込み動作で転送される第1データ量の記憶容量を備えるバッファメモリと、

前記第1データ量より小さな第2データ量の記憶容量を備え、前記バッファメモリから前記不揮発性メモリへのプログラム動作の際、期待値を格納する検証メモリとを備え、

前記不揮発性メモリから前記バッファメモリへのデータのロード動作の際、前記不揮発性メモリにおける前記第2データ量またはその整数倍であって前記第1データ量より小さな所定記憶容量が消去状態の場合、前記検証メモリをリセットし、該検証メモリの内容を前記バッファメモリの前記ロード対象に該当する記憶容量場所に転送することを特徴とするメモリシステム。 - 前記不揮発性メモリは、前記所定記憶容量ごとに消去状態であるか否かを記憶する情報記憶部を備え、

前記ロード動作に応じて、前記不揮発性メモリからのデータの読み出しに先立ち前記情報記憶部を読み出し、前記所定記憶容量が消去状態であるか否かを判定する消去状態判定部とを備えることを特徴とする請求項1に記載のメモリシステム。 - 前記検証メモリは、前記バッファメモリへの転送ビット幅と同数またはその整数倍の検証メモリセルをリセットすることを特徴とする請求項1または2に記載のメモリシステム。

- 前記検証メモリは、マルチプレクサを備え、

前記バッファメモリへの転送ビット幅より少数の検証メモリセルをリセットし、リセットされた前記検証メモリセルの内容は前記マルチプレクサを経て前記転送ビット幅に拡張されることを特徴とする請求項1または2に記載のメモリシステム。 - 前記検証メモリと前記バッファメモリ間にはそれらを接続する複数のインターナルバスと、前記所定記憶容量が消去状態でない場合に活性化される第1スイッチ素子と、前記所定記憶容量が消去状態の場合に活性化される第2スイッチ素子とを備え、

前記バッファメモリは、前記第1スイッチ素子を経由して前記不揮発性メモリからデータが転送され、前記第2スイッチ素子を経由して前記検証メモリからデータが転送されることを特徴とする請求項1または2に記載のメモリシステム。 - 前記不揮発性メモリは、前記所定記憶容量を構成するメモリセルと、前記情報記憶部を構成するメモリセルとが、同一のワード線に接続されることを特徴とする請求項1乃至5の少なくとも何れか1項に記載のメモリシステム。

- 前記第1データ量はページを構成するデータ量であり、前記第2データ量はセクタを構成するデータ量であることを特徴とする請求項1乃至6の少なくとも何れか1項に記載のメモリシステム。

- 不揮発性メモリと、前記不揮発性メモリと外部端子との間に介在するバッファメモリと、前記バッファメモリから前記不揮発性メモリへのプログラム動作の際、前記第1データ量より小さな第2データ量の期待値を格納する検証メモリとを備え、外部との1回の読出しまたは/および書込み動作として前記バッファメモリを介して第1データ量のアクセスを行うメモリシステムの制御方法であって、

読出し動作の際、

前記不揮発性メモリから前記バッファメモリへのデータのロード動作に先立ち、前記不揮発性メモリにおける前記第2データ量またはその整数倍であって前記第1データ量より小さな所定記憶容量が消去状態であるか否かを記憶する情報記憶部を読み出すステップと、

前記所定記憶容量が消去状態であると判断された場合に、前記検証メモリをリセットするステップと、

リセットされた前記検証メモリの内容を前記バッファメモリに転送するステップとを有することを特徴とするメモリシステムの制御方法。 - 前記転送ステップは、前記所定記憶容量に対応して前記バッファメモリ内のワード線選択または/およびコラム線選択をそれぞれ同時に活性する、ことを特徴とする請求項8に記載のメモリシステムの制御方法。

- 前記転送ステップは、前記検証メモリと前記バッファメモリ間を接続する複数のインターナルバスの一部のみを使用する、ことを特徴とする請求項8または9に記載のメモリシステムの制御方法。

- 前記情報記憶部を読み出すステップの後、前記所定記憶容量が消去状態でないと判断された場合に前記第1データ量を読み出すステップと、

前記第1データ量を読み出すステップは、前記情報記憶部を読み出すステップで読み出された情報記憶部のメモリセルデータが流す電流を元に、前記第1データ量のメモリセルデータを判定する、ことを特徴とする請求項8に記載のメモリシステムの制御方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008114863A JP4635173B2 (ja) | 2008-04-25 | 2008-04-25 | メモリシステムおよびその制御方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008114863A JP4635173B2 (ja) | 2008-04-25 | 2008-04-25 | メモリシステムおよびその制御方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009266305A JP2009266305A (ja) | 2009-11-12 |

| JP4635173B2 true JP4635173B2 (ja) | 2011-02-16 |

Family

ID=41391960

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008114863A Expired - Fee Related JP4635173B2 (ja) | 2008-04-25 | 2008-04-25 | メモリシステムおよびその制御方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4635173B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8924626B2 (en) | 2010-04-29 | 2014-12-30 | Sandisk Technologies Inc. | Phased NAND power-on reset |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05342891A (ja) * | 1992-06-10 | 1993-12-24 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP2001357684A (ja) * | 2000-06-12 | 2001-12-26 | Sharp Corp | 半導体記憶装置 |

| JP2008097736A (ja) * | 2006-10-13 | 2008-04-24 | Spansion Llc | 半導体装置およびその制御方法 |

-

2008

- 2008-04-25 JP JP2008114863A patent/JP4635173B2/ja not_active Expired - Fee Related

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05342891A (ja) * | 1992-06-10 | 1993-12-24 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP2001357684A (ja) * | 2000-06-12 | 2001-12-26 | Sharp Corp | 半導体記憶装置 |

| JP2008097736A (ja) * | 2006-10-13 | 2008-04-24 | Spansion Llc | 半導体装置およびその制御方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009266305A (ja) | 2009-11-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7415568B2 (en) | Method and apparatus for initialization control in a non-volatile memory device | |

| US7952958B2 (en) | Non-volatile semiconductor storage system | |

| JP5016841B2 (ja) | 不揮発性半導体記憶装置 | |

| KR20070117606A (ko) | 데이터용과 에러 정정 코드용으로 전환가능한 부분을 갖는메모리 | |

| JP2006252624A (ja) | 半導体記憶装置 | |

| US7898866B2 (en) | Nonvolatile memory device and method of operating the same | |

| KR20030071644A (ko) | 뱅크/블록 계층 구성을 갖는 eeprom형 반도체 기억장치 | |

| EP2359369B1 (en) | Semiconductor device with main memory unit and auxiliary memory unit requiring preset operation | |

| US9251918B2 (en) | Semiconductor memory device | |

| US20120159044A1 (en) | Non-volatile memory system with block protection function and block status control method | |

| US6570809B1 (en) | Real-time multitasking flash memory with quick data duplication | |

| JP4582551B2 (ja) | 半導体装置およびデータ書き込み方法 | |

| JP4635173B2 (ja) | メモリシステムおよびその制御方法 | |

| JP4467371B2 (ja) | 不揮発性半導体記憶装置及び不揮発性半導体記憶装置の置換情報の設定方法 | |

| US7430150B2 (en) | Method and system for providing sensing circuitry in a multi-bank memory device | |

| EP1632950B1 (en) | Non-volatile memory device with improved initialization readout speed | |

| KR100598907B1 (ko) | 연속적 읽기/쓰기가 가능한 플래쉬 메모리 | |

| US7760556B2 (en) | Data path circuit in a flash memory device | |

| US6882554B2 (en) | Integrated memory, and a method of operating an integrated memory | |

| US7652905B2 (en) | Flash memory array architecture | |

| JP4660316B2 (ja) | 不揮発性メモリ装置 | |

| KR100609540B1 (ko) | 불량 셀 처리 회로를 포함하는 불휘발성 강유전체 메모리장치 및 제어 방법 | |

| JP4413674B2 (ja) | 半導体メモリ装置 | |

| JP2009176375A (ja) | 不揮発性半導体記憶装置 | |

| KR20070062922A (ko) | 초기 동작 및 기능을 설정하기 위한 설정 정보를 기억하는기억부를 구비한 반도체 기억 장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20101020 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101026 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101026 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4635173 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |