CN103545342A - 半导体装置 - Google Patents

半导体装置 Download PDFInfo

- Publication number

- CN103545342A CN103545342A CN201310468513.0A CN201310468513A CN103545342A CN 103545342 A CN103545342 A CN 103545342A CN 201310468513 A CN201310468513 A CN 201310468513A CN 103545342 A CN103545342 A CN 103545342A

- Authority

- CN

- China

- Prior art keywords

- conductive layer

- layer

- thin

- film transistor

- insulating barrier

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 243

- 230000015572 biosynthetic process Effects 0.000 claims abstract description 42

- 230000004888 barrier function Effects 0.000 claims description 85

- 238000005530 etching Methods 0.000 claims description 52

- 239000010410 layer Substances 0.000 abstract description 426

- 239000010409 thin film Substances 0.000 abstract description 212

- 239000000758 substrate Substances 0.000 abstract description 157

- 229910052760 oxygen Inorganic materials 0.000 abstract description 71

- 239000001301 oxygen Substances 0.000 abstract description 68

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 abstract description 59

- 239000000463 material Substances 0.000 abstract description 56

- 239000011241 protective layer Substances 0.000 abstract description 28

- 239000011159 matrix material Substances 0.000 abstract description 6

- 239000010408 film Substances 0.000 description 187

- 239000004973 liquid crystal related substance Substances 0.000 description 65

- 238000000034 method Methods 0.000 description 65

- 238000004519 manufacturing process Methods 0.000 description 56

- 239000012212 insulator Substances 0.000 description 48

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 47

- 239000002245 particle Substances 0.000 description 43

- 239000008393 encapsulating agent Substances 0.000 description 37

- 238000004544 sputter deposition Methods 0.000 description 37

- 229910052786 argon Inorganic materials 0.000 description 26

- 210000004027 cell Anatomy 0.000 description 24

- 239000007789 gas Substances 0.000 description 24

- 238000000151 deposition Methods 0.000 description 23

- 238000003466 welding Methods 0.000 description 22

- 239000000123 paper Substances 0.000 description 21

- 230000008569 process Effects 0.000 description 21

- 238000009832 plasma treatment Methods 0.000 description 19

- 239000012298 atmosphere Substances 0.000 description 16

- 230000008021 deposition Effects 0.000 description 16

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 15

- 238000000576 coating method Methods 0.000 description 15

- 239000013078 crystal Substances 0.000 description 15

- 239000000203 mixture Substances 0.000 description 15

- -1 oxygen radical Chemical class 0.000 description 15

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 14

- 229910052782 aluminium Inorganic materials 0.000 description 13

- 239000004020 conductor Substances 0.000 description 13

- 230000006870 function Effects 0.000 description 13

- 239000011521 glass Substances 0.000 description 13

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 12

- 239000011248 coating agent Substances 0.000 description 12

- 229920005989 resin Polymers 0.000 description 12

- 239000011347 resin Substances 0.000 description 12

- 239000010936 titanium Substances 0.000 description 12

- 229910052581 Si3N4 Inorganic materials 0.000 description 11

- 239000004411 aluminium Substances 0.000 description 11

- 238000010438 heat treatment Methods 0.000 description 11

- 229910052738 indium Inorganic materials 0.000 description 11

- 239000003094 microcapsule Substances 0.000 description 11

- 229910052733 gallium Inorganic materials 0.000 description 10

- 229910052725 zinc Inorganic materials 0.000 description 10

- 239000011701 zinc Substances 0.000 description 10

- 210000002858 crystal cell Anatomy 0.000 description 9

- 230000004048 modification Effects 0.000 description 9

- 238000012986 modification Methods 0.000 description 9

- 238000007639 printing Methods 0.000 description 9

- 229910045601 alloy Inorganic materials 0.000 description 8

- 239000000956 alloy Substances 0.000 description 8

- 239000007788 liquid Substances 0.000 description 8

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 8

- 229910052814 silicon oxide Inorganic materials 0.000 description 8

- 239000011787 zinc oxide Substances 0.000 description 8

- 230000007547 defect Effects 0.000 description 7

- 230000005684 electric field Effects 0.000 description 7

- 238000003780 insertion Methods 0.000 description 7

- 230000037431 insertion Effects 0.000 description 7

- 230000003287 optical effect Effects 0.000 description 7

- 238000012545 processing Methods 0.000 description 7

- 229910052719 titanium Inorganic materials 0.000 description 7

- 238000001039 wet etching Methods 0.000 description 7

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 6

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 6

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 6

- 230000008859 change Effects 0.000 description 6

- 238000010586 diagram Methods 0.000 description 6

- MRNHPUHPBOKKQT-UHFFFAOYSA-N indium;tin;hydrate Chemical compound O.[In].[Sn] MRNHPUHPBOKKQT-UHFFFAOYSA-N 0.000 description 6

- 239000012528 membrane Substances 0.000 description 6

- 229910052751 metal Inorganic materials 0.000 description 6

- 239000002184 metal Substances 0.000 description 6

- 238000012856 packing Methods 0.000 description 6

- 230000003071 parasitic effect Effects 0.000 description 6

- 239000000126 substance Substances 0.000 description 6

- 238000000137 annealing Methods 0.000 description 5

- 239000003990 capacitor Substances 0.000 description 5

- 239000011651 chromium Substances 0.000 description 5

- 238000004891 communication Methods 0.000 description 5

- 239000002322 conducting polymer Substances 0.000 description 5

- 229920001940 conductive polymer Polymers 0.000 description 5

- 238000010276 construction Methods 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 239000001257 hydrogen Substances 0.000 description 5

- 229910052739 hydrogen Inorganic materials 0.000 description 5

- 229910003437 indium oxide Inorganic materials 0.000 description 5

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 5

- 239000011229 interlayer Substances 0.000 description 5

- 238000005192 partition Methods 0.000 description 5

- 229920003023 plastic Polymers 0.000 description 5

- 239000004033 plastic Substances 0.000 description 5

- 230000009467 reduction Effects 0.000 description 5

- 229910052710 silicon Inorganic materials 0.000 description 5

- 239000010703 silicon Substances 0.000 description 5

- 238000003860 storage Methods 0.000 description 5

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 4

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 4

- 239000000872 buffer Substances 0.000 description 4

- 238000006243 chemical reaction Methods 0.000 description 4

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 4

- 239000005262 ferroelectric liquid crystals (FLCs) Substances 0.000 description 4

- 229910052750 molybdenum Inorganic materials 0.000 description 4

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 4

- 150000002894 organic compounds Chemical class 0.000 description 4

- 150000003254 radicals Chemical class 0.000 description 4

- 238000004062 sedimentation Methods 0.000 description 4

- 238000000926 separation method Methods 0.000 description 4

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 4

- 229910052721 tungsten Inorganic materials 0.000 description 4

- 229910001930 tungsten oxide Inorganic materials 0.000 description 4

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 4

- NIXOWILDQLNWCW-UHFFFAOYSA-N 2-Propenoic acid Natural products OC(=O)C=C NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 3

- QTBSBXVTEAMEQO-UHFFFAOYSA-N Acetic acid Chemical compound CC(O)=O QTBSBXVTEAMEQO-UHFFFAOYSA-N 0.000 description 3

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 3

- 229910052779 Neodymium Inorganic materials 0.000 description 3

- 239000004642 Polyimide Substances 0.000 description 3

- OBNDGIHQAIXEAO-UHFFFAOYSA-N [O].[Si] Chemical compound [O].[Si] OBNDGIHQAIXEAO-UHFFFAOYSA-N 0.000 description 3

- 230000009471 action Effects 0.000 description 3

- 235000011114 ammonium hydroxide Nutrition 0.000 description 3

- 229910021417 amorphous silicon Inorganic materials 0.000 description 3

- 238000013459 approach Methods 0.000 description 3

- 229910052804 chromium Inorganic materials 0.000 description 3

- 238000005401 electroluminescence Methods 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 3

- 230000005669 field effect Effects 0.000 description 3

- 230000007246 mechanism Effects 0.000 description 3

- 239000011733 molybdenum Substances 0.000 description 3

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 3

- 229910052757 nitrogen Inorganic materials 0.000 description 3

- 239000000049 pigment Substances 0.000 description 3

- 229920006267 polyester film Polymers 0.000 description 3

- 229920001721 polyimide Polymers 0.000 description 3

- 229920002620 polyvinyl fluoride Polymers 0.000 description 3

- 230000004044 response Effects 0.000 description 3

- 239000000377 silicon dioxide Substances 0.000 description 3

- 239000002356 single layer Substances 0.000 description 3

- 239000000243 solution Substances 0.000 description 3

- 229910052715 tantalum Inorganic materials 0.000 description 3

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 3

- 239000010937 tungsten Substances 0.000 description 3

- SMZOUWXMTYCWNB-UHFFFAOYSA-N 2-(2-methoxy-5-methylphenyl)ethanamine Chemical compound COC1=CC=C(C)C=C1CCN SMZOUWXMTYCWNB-UHFFFAOYSA-N 0.000 description 2

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 2

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 2

- 229920002430 Fibre-reinforced plastic Polymers 0.000 description 2

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 2

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 2

- 241001062009 Indigofera Species 0.000 description 2

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 2

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- 230000001133 acceleration Effects 0.000 description 2

- 125000000217 alkyl group Chemical group 0.000 description 2

- 125000004429 atom Chemical group 0.000 description 2

- SWXQKHHHCFXQJF-UHFFFAOYSA-N azane;hydrogen peroxide Chemical compound [NH4+].[O-]O SWXQKHHHCFXQJF-UHFFFAOYSA-N 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 2

- 230000000903 blocking effect Effects 0.000 description 2

- 239000005388 borosilicate glass Substances 0.000 description 2

- DQXBYHZEEUGOBF-UHFFFAOYSA-N but-3-enoic acid;ethene Chemical compound C=C.OC(=O)CC=C DQXBYHZEEUGOBF-UHFFFAOYSA-N 0.000 description 2

- 238000001354 calcination Methods 0.000 description 2

- 229910052799 carbon Inorganic materials 0.000 description 2

- 230000015556 catabolic process Effects 0.000 description 2

- 239000002800 charge carrier Substances 0.000 description 2

- 239000012069 chiral reagent Substances 0.000 description 2

- 239000010949 copper Substances 0.000 description 2

- 230000007797 corrosion Effects 0.000 description 2

- 238000005260 corrosion Methods 0.000 description 2

- 230000008878 coupling Effects 0.000 description 2

- 238000010168 coupling process Methods 0.000 description 2

- 238000005859 coupling reaction Methods 0.000 description 2

- 238000006731 degradation reaction Methods 0.000 description 2

- 238000005137 deposition process Methods 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 238000004720 dielectrophoresis Methods 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- 239000003822 epoxy resin Substances 0.000 description 2

- 239000005038 ethylene vinyl acetate Substances 0.000 description 2

- 230000005284 excitation Effects 0.000 description 2

- 239000011151 fibre-reinforced plastic Substances 0.000 description 2

- 239000011737 fluorine Substances 0.000 description 2

- 229910052731 fluorine Inorganic materials 0.000 description 2

- 239000012535 impurity Substances 0.000 description 2

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 2

- 229910010272 inorganic material Inorganic materials 0.000 description 2

- 238000009434 installation Methods 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- 238000010030 laminating Methods 0.000 description 2

- 238000003475 lamination Methods 0.000 description 2

- 238000004020 luminiscence type Methods 0.000 description 2

- 238000001755 magnetron sputter deposition Methods 0.000 description 2

- 239000002159 nanocrystal Substances 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- 239000011368 organic material Substances 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 2

- 229920001200 poly(ethylene-vinyl acetate) Polymers 0.000 description 2

- 229920002037 poly(vinyl butyral) polymer Polymers 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920000647 polyepoxide Polymers 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- 229920001296 polysiloxane Polymers 0.000 description 2

- 229920000915 polyvinyl chloride Polymers 0.000 description 2

- 239000004800 polyvinyl chloride Substances 0.000 description 2

- 238000001552 radio frequency sputter deposition Methods 0.000 description 2

- 238000005546 reactive sputtering Methods 0.000 description 2

- 229910052706 scandium Inorganic materials 0.000 description 2

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 2

- 239000002904 solvent Substances 0.000 description 2

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 2

- 229910001936 tantalum oxide Inorganic materials 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- 229960001296 zinc oxide Drugs 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 229910000838 Al alloy Inorganic materials 0.000 description 1

- 229910017073 AlLi Inorganic materials 0.000 description 1

- 229910017083 AlN Inorganic materials 0.000 description 1

- PIGFYZPCRLYGLF-UHFFFAOYSA-N Aluminum nitride Chemical compound [Al]#N PIGFYZPCRLYGLF-UHFFFAOYSA-N 0.000 description 1

- 239000004986 Cholesteric liquid crystals (ChLC) Substances 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- 229920000426 Microplastic Polymers 0.000 description 1

- GRYLNZFGIOXLOG-UHFFFAOYSA-N Nitric acid Chemical compound O[N+]([O-])=O GRYLNZFGIOXLOG-UHFFFAOYSA-N 0.000 description 1

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 1

- 239000004952 Polyamide Substances 0.000 description 1

- 229910002808 Si–O–Si Inorganic materials 0.000 description 1

- 229910006404 SnO 2 Inorganic materials 0.000 description 1

- FKNQFGJONOIPTF-UHFFFAOYSA-N Sodium cation Chemical compound [Na+] FKNQFGJONOIPTF-UHFFFAOYSA-N 0.000 description 1

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 1

- 229910007541 Zn O Inorganic materials 0.000 description 1

- AZWHFTKIBIQKCA-UHFFFAOYSA-N [Sn+2]=O.[O-2].[In+3] Chemical compound [Sn+2]=O.[O-2].[In+3] AZWHFTKIBIQKCA-UHFFFAOYSA-N 0.000 description 1

- 239000002253 acid Substances 0.000 description 1

- 230000004913 activation Effects 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 239000005030 aluminium foil Substances 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- 230000003321 amplification Effects 0.000 description 1

- 230000003667 anti-reflective effect Effects 0.000 description 1

- 150000004945 aromatic hydrocarbons Chemical class 0.000 description 1

- 125000003118 aryl group Chemical group 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 1

- 239000001569 carbon dioxide Substances 0.000 description 1

- 229910002092 carbon dioxide Inorganic materials 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 230000003098 cholesteric effect Effects 0.000 description 1

- 238000005253 cladding Methods 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 229920001577 copolymer Polymers 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000013039 cover film Substances 0.000 description 1

- 238000002425 crystallisation Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 230000004069 differentiation Effects 0.000 description 1

- 238000007598 dipping method Methods 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 239000006185 dispersion Substances 0.000 description 1

- 238000006073 displacement reaction Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 210000005069 ears Anatomy 0.000 description 1

- 235000013399 edible fruits Nutrition 0.000 description 1

- 238000001962 electrophoresis Methods 0.000 description 1

- 238000005538 encapsulation Methods 0.000 description 1

- 238000005265 energy consumption Methods 0.000 description 1

- 239000004744 fabric Substances 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 230000005283 ground state Effects 0.000 description 1

- 230000009931 harmful effect Effects 0.000 description 1

- 239000001307 helium Substances 0.000 description 1

- 229910052734 helium Inorganic materials 0.000 description 1

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 1

- 150000002431 hydrogen Chemical class 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 230000005764 inhibitory process Effects 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 150000002484 inorganic compounds Chemical class 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 238000005224 laser annealing Methods 0.000 description 1

- 230000004807 localization Effects 0.000 description 1

- 239000000696 magnetic material Substances 0.000 description 1

- 238000000838 magnetophoresis Methods 0.000 description 1

- 230000013011 mating Effects 0.000 description 1

- 229910021645 metal ion Inorganic materials 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 239000003595 mist Substances 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 229910017604 nitric acid Inorganic materials 0.000 description 1

- 238000003199 nucleic acid amplification method Methods 0.000 description 1

- 238000005457 optimization Methods 0.000 description 1

- AHLBNYSZXLDEJQ-FWEHEUNISA-N orlistat Chemical compound CCCCCCCCCCC[C@H](OC(=O)[C@H](CC(C)C)NC=O)C[C@@H]1OC(=O)[C@H]1CCCCCC AHLBNYSZXLDEJQ-FWEHEUNISA-N 0.000 description 1

- 125000004430 oxygen atom Chemical group O* 0.000 description 1

- 238000001259 photo etching Methods 0.000 description 1

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 1

- 239000002985 plastic film Substances 0.000 description 1

- 229920006255 plastic film Polymers 0.000 description 1

- 229920006122 polyamide resin Polymers 0.000 description 1

- 229920000767 polyaniline Polymers 0.000 description 1

- 229920000128 polypyrrole Polymers 0.000 description 1

- 229920000123 polythiophene Polymers 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 239000000376 reactant Substances 0.000 description 1

- 238000002310 reflectometry Methods 0.000 description 1

- 230000027756 respiratory electron transport chain Effects 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- 238000005204 segregation Methods 0.000 description 1

- 229920002050 silicone resin Polymers 0.000 description 1

- 229910001415 sodium ion Inorganic materials 0.000 description 1

- 125000006850 spacer group Chemical group 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 238000005507 spraying Methods 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 230000003746 surface roughness Effects 0.000 description 1

- 239000013077 target material Substances 0.000 description 1

- OFIYHXOOOISSDN-UHFFFAOYSA-N tellanylidenegallium Chemical compound [Te]=[Ga] OFIYHXOOOISSDN-UHFFFAOYSA-N 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- 238000000108 ultra-filtration Methods 0.000 description 1

- 210000003462 vein Anatomy 0.000 description 1

- 238000012795 verification Methods 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/1368—Active matrix addressed cells in which the switching element is a three-electrode device

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/13624—Active matrix addressed cells having more than one switching element per pixel

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136286—Wiring, e.g. gate line, drain line

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

- H01L27/1225—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer with semiconductor materials not belonging to the group IV of the periodic table, e.g. InGaZnO

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/124—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/121—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements

- H10K59/1213—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements the pixel elements being TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/131—Interconnections, e.g. wiring lines or terminals

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

- H10K50/80—Constructional details

- H10K50/805—Electrodes

- H10K50/82—Cathodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/80—Constructional details

- H10K59/805—Electrodes

- H10K59/8052—Cathodes

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Computer Hardware Design (AREA)

- Nonlinear Science (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Mathematical Physics (AREA)

- Optics & Photonics (AREA)

- Geometry (AREA)

- Ceramic Engineering (AREA)

- Thin Film Transistor (AREA)

- Liquid Crystal (AREA)

- Electroluminescent Light Sources (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Electrodes Of Semiconductors (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Electrochromic Elements, Electrophoresis, Or Variable Reflection Or Absorption Elements (AREA)

- Physical Deposition Of Substances That Are Components Of Semiconductor Devices (AREA)

Abstract

本公开涉及半导体装置。一种显示装置包括其中像素以矩阵状排列的像素部,该像素包括:具有含氧量不同的至少两种氧化物半导体层的组合并在与栅电极层重叠的成为沟道形成区的半导体层上具有沟道保护层的反交错型薄膜晶体管;以及与该反交错型薄膜晶体管电连接的像素电极层。在该显示装置中的该像素部的周边,设置有包括由与所述像素电极层相同材料而形成的导电层的焊盘部。并且,所述导电层电连接到形成在对置衬底上的共同电极层。

Description

技术领域

本发明涉及一种使用氧化物半导体的显示装置及其制造方法。

背景技术

在液晶显示装置中典型看到的形成在玻璃衬底等的平板上的薄膜晶体管使用非晶硅或多晶硅制造。使用非晶硅的薄膜晶体管具有低的场效应迁移率,但是可以在大玻璃衬底上形成。另一方面,使用结晶硅的薄膜晶体管具有高的场效应迁移率,但是由于需要进行激光退火等的晶化工序,因此其并不总是能在大玻璃衬底上形成。

根据前述,使用氧化物半导体制造薄膜晶体管并将其应用于电子装置或光学装置的技术受到注目。专利文献1及专利文献2公开这些技术的例子,其中使用氧化锌、或In-Ga-Zn-O类氧化物半导体用于氧化物半导体膜来制造薄膜晶体管,并将其用于图像显示装置的开关元件等。

[专利文献1]日本专利申请公开2007-123861号公报

[专利文献2]日本专利申请公开2007-96055号公报

在沟道形成区中使用氧化物半导体的薄膜晶体管可以实现比使用非晶硅的薄膜晶体管更高的场效应迁移率。作为氧化物半导体膜,可以利用溅射法等在300℃或以下的温度下形成,其制造工序比使用多晶硅的薄膜晶体管简单。

期待使用上述氧化物半导体在玻璃衬底、塑料衬底等上形成薄膜晶体管,并可以期待将其应用于液晶显示器、电致发光显示器或电子纸等。

氧化物半导体薄膜晶体管工作特性优良且可以在低温下制造。然而不为了有效利用这些特征,需要对元件的结构和制造条件进行最优化,还需要顾虑到信号的输入和输出所必要的布线结构和布线的连接结构。虽然氧化物半导体膜可以在低温下形成,但是当形成布线或电极的金属等的薄膜、例如层间绝缘膜等的绝缘膜出现分离现象时,则造成产品缺陷。另外,还存在当设置在显示面板的元件衬底侧的共同连接部的电极的连接电阻高时,显示屏幕出现斑点且亮度降低的问题。

发明内容

本发明的一个实施方式的目的之一在于提供一种适用于设置在显示面板中的共同连接部的结构。

本发明的一个实施方式的另一目的在于:在使用氧化物半导体、绝缘膜及导电膜的叠层而制造的各种显示装置中,防止薄膜的分离所引起的缺陷。

本发明的一个实施方式的显示装置,包括像素部,其中扫描线与信号线交叉且像素电极层以矩阵形状排列,对应于该像素电极层设置具有含氧量不同的至少两种氧化物半导体层的组合和沟道保护层的反交错型薄膜晶体管。在该显示装置中的像素部的外侧区域中,设置焊盘部,其使用与扫描线、信号线相同的材料制成的导电层电连接到相对于像素电极层的共同电极层。

本发明的一个示例方式的显示装置,包括像素部,其具有连接到像素电极的薄膜晶体管,和与相对于像素电极的共同电极电连接的焊盘部,并且显示装置包括以下结构。在像素部中,扫描线和信号线交叉,像素电极层以矩阵形状排列。对应于像素电极层设置薄膜晶体管,其包括:与扫描线连接的栅电极层,覆盖栅电极层的栅极绝缘层,成为沟道形成区的第一氧化物半导体层,覆盖与栅电极层重叠的第一氧化物半导体层的沟道保护层,第一氧化物半导体层和沟道保护层上的成为源区和漏区的第二氧化物半导体层,第一氧化物半导体层、沟道保护层以及第二氧化物半导体层上的源电极层和漏电极层。

焊盘部设置在像素部的外侧区域,焊盘部包括使用与栅极绝缘层相同的层形成的绝缘层、绝缘层上使用与源电极层和漏电极层相同的层形成的导电层,和在导电层上的层间绝缘层。焊盘部通过层间绝缘层中的开口部电连接到相对于像素电极层的共同电极层。

根据本发明的一个示例方式,设置在像素部的外侧区域的焊盘部可具有另一结构:由与栅电极层相同的层形成的第一导电层、由与栅极绝缘层相同的层形成的绝缘层、由与源电极层和漏电极层相同的层形成的第二导电层按此顺序堆叠。该焊盘部可以通过设置在第二导电层上的层间绝缘层的开口部电连接到相对于像素电极层的共同电极层。

在上述结构中,焊盘部可以具有其中在由与栅极绝缘层相同的层形成的绝缘层和第二导电层之间设置由与第二氧化物半导体层相同的层形成的氧化物半导体层的一种结构。

用作半导体层的沟道形成区的氧化物半导体层(第一氧化物半导体层)比用作源区和漏区的氧化物半导体层(第二氧化物半导体层)氧浓度高。可以认为第一氧化物半导体层为氧过剩氧化物半导体层,

而第二氧化物半导体层为氧缺欠氧化物半导体层。

第二氧化物半导体层为n型导电型,并且比第一氧化物半导体层电导率高。所以,使用第二氧化物半导体层的源区和漏区比使用第一氧化物半导体层的半导体层电阻低。

在一些情况下,第一氧化物半导体层具有非晶结构,第二氧化物半导体层在非晶结构中包含晶粒(纳米晶体)。注意该第二氧化物半导体层中的晶粒(纳米晶体)的直径为1nm至10nm,典型的为大约2nm至4nm。

注意,为了方便起见在说明书中使用“第一”、“第二”等序数词,但其并不表示工序顺序或层叠顺序,也不表示用来指定发明的特定名词。

作为成为沟道形成区的第一氧化物半导体层及/或成为源区和漏区的第二氧化物半导体层,可以使用包含In、Ga及Zn的氧化物半导体膜。可以使用钨、钼、钛、镍或铝来取代In、Ga及Zn中的任意一个。

在本说明书中,将使用包含In、Ga及Zn的氧化物半导体膜形成的半导体层也记作“IGZO半导体层”。IGZO半导体层是指非单晶半导体层并且至少包含非晶成分。

将表面上形成有像素电极层及与该像素电极层电连接的薄膜晶体管的衬底使用称为密封材料的粘结材料固定到对置衬底。

在液晶显示装置中,使用密封材料在两个衬底之间密封液晶材料。

向密封材料混入多个导电粒子(镀金的塑料粒子等),以使设置在对置衬底上的对置电极(也称为第一共同电极)与设置在另一方的衬底上的第二共同电极或共同电位线电连接。

可以在与薄膜晶体管的制造工序相同的制造工序中在同一衬底上形成共同电位线。

另外,可将共同电位线与密封材料的导电粒子重叠的部分称为共同连接部,也可以认为共同电位线与导电粒子重叠的部分为共同电极。

与薄膜晶体管在同一衬底上形成的共同电位线可以认为是当对液晶交流驱动时供给成为基准的电压的线。

除了与对置电极连接的共同电位线之外,与存储电容的一方的电极连接的电容布线也称为共同电位线的一种变型,同样地也可以形成在与薄膜晶体管相同的衬底上。

使用电泳显示元件的也被称为电子纸的显示装置具有以下结构,其中在一对衬底之间容纳白色粒子、带有与白色粒子相反的极性的黑色粒子以及使它们分散的分散介质(气体或液体)。设置在一对衬底中的一个衬底上的电极是共同电极。在另一个衬底上与该共同电极相对地设置有像素电极,并且在该衬底上设置有多个与像素电极电连接的薄膜晶体管。例如,在使用该电泳显示元件的显示装置的操作中,对于用于将白色显示变成黑色显示的像素电极,对其施加相对于施加到共同电极的基准电位的正的电压,而对用于将黑色显示变成白色显示的像素电极,对其施加相对于施加到共同电极的基准电位的负的电压,至于不使显示发生变化的像素电极,将其设定为与共同电位相同的电位。

与薄膜晶体管在相同衬底上形成的共同电位线也可以认为是当操作电泳显示元件时供给成为基准的电压的线。

注意使用电泳显示元件的显示装置包括由一对衬底及在该对衬底之间设置的分隔壁形成的具有一致尺寸的多个独立空间,一个独立空间用作单位像素而进行部分图像显示。独立空间包含多个白色粒子、具有与白色粒子相反的极性的黑色粒子以及使它们分散的分散介质(气体或液体)。

而且,在使用电泳显示元件的显示装置中,带有不同极性的多个有色粒子以及使它们分散的分散介质被密封材料密封在两个衬底之间。另外,在使用电泳显示元件的显示装置中,设置在一个衬底上的共同电极与形成在另一个衬底上的共同电位线通过共同连接部中的导电粒子电连接。

在液晶显示装置或使用电泳显示元件的显示装置中,根据制造过程的温度,作为使用的一对衬底的材料,可以使用塑料膜。

可以使用溅射(溅射法)来形成栅极绝缘层、成为沟道形成区的第一氧化物半导体层、成为源区和漏区的第二氧化物半导体层,以及源电极层和漏电极层。

溅射法示例包括如下方法:作为溅射电源使用高频电源的RF溅射法、DC溅射法以及以脉冲方式施加偏压的脉冲DC溅射法。RF溅射法主要用于形成绝缘膜,而DC溅射法主要用于形成金属膜的例子。

另外,也有可以设置材料不同的多个靶的多源溅射装置。多源溅射装置既可以在同一反应室中层叠地沉积不同的材料膜,又可以在同一反应室中同时进行放电来沉积多种材料。

另外,也有使用磁控管溅射法的溅射装置和使用ECR溅射法的溅射装置:在使用磁控管溅射法的溅射装置中,在反应室内部具备磁铁系统;而在使用ECR溅射法的溅射装置中,不使用辉光放电而利用使用微波产生的等离子体。

另外,作为使用溅射法的沉积方法,还有反应溅射法、偏压溅射法:在反应溅射法中,当进行沉积时使靶物质和溅射气体成分起化学反应而形成它们的化合物薄膜;而在偏压溅射法中,当进行沉积时对衬底还施加电压。

使用任意上述各种溅射法形成栅极绝缘层、半导体层、源区和漏区以及源电极层和漏电极层。

当使用IGZO半导体层作为第一氧化物半导体层(氧过剩氧化物半导体层)和第二氧化物半导体层(氧缺乏氧化物半导体层)时,在不同的沉积条件下形成第一氧化物半导体层和第二氧化物半导体层。成为源区和漏区的第二氧化物半导体层通过以下条件沉积:刚沉积后含有直径为1nm以上且10nm以下的晶粒。例如,如果使用In2O3:Ga2O3:ZnO=1:1:1的靶,并利用DC溅射法以氩气体流量:氧流量为2:1的比例引入,或者只引入氩气体来沉积第二氧化物半导体层时,在刚沉积后一些情况下获得含有直径为1nm以上且10nm以下的晶粒的膜。注意意图性地设计In2O3:Ga2O3:ZnO=1:1:1的靶为该比例是为了获得非晶状的氧化物半导体膜,所以可以对靶的组成比进行变更以便形成结晶性更高的源区和漏区。优选使用相同的靶并仅通过变更引入的气体来分别形成成为沟道形成区的第一氧化物半导体层和成为源区和漏区的第二氧化物半导体层,以便实现工序简化和低成本化。

源电极层和漏电极层优选使用钛膜。

至于溅射法,因为对靶施加Ar离子的强能量,所以可以认为:在沉积的氧化物半导体层(典型的IGZO半导体层)中存在着强应变能。优选进行200℃至600℃,典型地为300℃至500℃的温度下的热处理,以释放该应变能。通过进行该热处理,进行原子能级的重新排列。由于通过进行该热处理而释放阻碍载流子迁移的应变能,所以沉积和热处理(包括光退火)是重要的。

注意,在本说明书中的半导体装置是指通过利用半导体特性而能够工作的所有装置,因此电光装置、半导体电路以及电子设备都是半导体装置。

根据本发明的一个实施方式,可以提供适用于设置在显示面板上的焊盘部的结构。

根据本发明的一个实施方式,在设置在像素部的外侧区域的焊盘部中,层叠氧化物半导体层和导电层,由此可以防止由于薄膜的分离造成的缺陷。另外,通过采用层叠氧化物半导体层和导电层的结构,焊盘部厚度增加,其电阻降低,而可以具有强度增加的结构。

另外,根据本发明的一个实施方式,可以制造光电流少、寄生电容小、导通截止比高、具有良好的动态特性的薄膜晶体管。

由此,根据本发明的一个实施方式,可以提供电特性高且可靠性好的显示装置。

附图说明

在附图中:

图1A和1B是说明半导体装置的图;

图2A和2B是说明半导体装置的图;

图3A和3B是说明半导体装置的图;

图4A至4C是说明半导体装置的制造方法的图;

图5A至5C是说明半导体装置的制造方法的图;

图6是说明半导体装置的制造方法的图;

图7是说明半导体装置的制造方法的图;

图8是说明半导体装置的制造方法的图;

图9是说明半导体装置的图;

图10A至10D是说明半导体装置的图;

图11是说明半导体装置的图;

图12是说明半导体装置的图;

图13A和13B是半导体装置的框图;

图14是说明信号线驱动电路的配置的图;

图15是说明信号线驱动电路的工作的时序图;

图16是说明信号线驱动电路的工作的时序图;

图17是说明移位寄存器的配置的图;

图18是说明图17所示的触发器的连接结构的图;

图19是半导体装置的像素的等效电路的图;

图20A至20C是说明半导体装置的图;

图21A至21C是说明半导体装置的图;

图22是说明半导体装置的图;

图23A和23B是说明半导体装置的图;

图24A和24B是说明电子纸的应用的图;

图25是示出电子书阅读器的一例的外观图;

图26A和26B是分别示出电视装置及数码相框的外观图;

图27A和27B是示出游戏机的例子的外观图;

图28是示出蜂窝电话的外观图;

图29A和29B是说明半导体装置的图;

图30A和30B是说明半导体装置的图;

图31A和31B是说明半导体装置的图;

图32是说明半导体装置的图。

具体实施方式

下面,参照附图对本发明的实施方式进行详细说明。但是,本发明不局限于以下的说明,所属技术领域的普通技术人员可以很容易地理解一个事实就是,其方式及详细内容在不脱离本发明的宗旨及其范围的情况下可以被变换为各种各样的形式。因此,本发明不应该被解释为仅限定在以下所示的实施方式所记载的内容中。在以下说明的本发明的结构中,使用相同的附图标记来标明具有类似功能的相同部分,而省略对其的说明。

实施方式1

本实施方式示出液晶显示装置的例子,其中在第一衬底和第二衬底之间封入有液晶层,将用于与设置在第二衬底上的对置电极电连接的共同连接部(焊盘部)形成在第一衬底上。注意,在第一衬底上形成有用作开关元件的薄膜晶体管,并且共同连接部在与像素部的开关元件相同的制造工序中制造,从而可以不使工序复杂而获得。

共同连接部设置在与用于贴合第一衬底和第二衬底的密封材料重叠的位置,并通过密封材料所含有的导电粒子与对置电极电连接。或者,在不与密封材料重叠的位置(除了像素部)设置共同连接部,将含有导电粒子的膏剂与密封材料另行设置以与共同连接部重叠,由此共同连接部可以通过膏剂中的导电粒子与对置电极电连接。

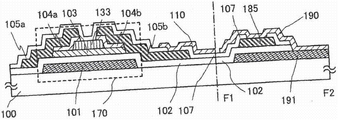

图1A是在同一衬底上形成薄膜晶体管和共同连接部的半导体装置的截面结构图。注意图1A所示的薄膜晶体管为具有沟道保护层的反交错型薄膜晶体管,在半导体层103的沟道形成区上设置沟道保护层133,并在半导体层103和沟道保护层133上隔着源区和漏区104a、104b设置有源电极层和漏电极层105a、105b。

在本实施方式中,具有沟道形成区的半导体层103是包含In、Ga、Zn以及O的非单晶半导体层(第一氧化物半导体层),其至少包含非晶成分。源区和漏区104a、104b是包含In、Ga、Zn以及O的氧化物半导体层(第二氧化物半导体层),并且其在与半导体层103不同条件下形成,比半导体层103含有的氧浓度低,比半导体层103的电阻低。源区和漏区104a、104b具有n型导电型,其活化能(ΔE)为0.01eV以上0.1eV以下,也称为n+区。注意源区和漏区104a、104b是包含In、Ga、Zn以及O的非单晶半导体层,其至少包含非晶成分。所以,用于半导体层103的氧化物半导体层为氧过剩氧化物半导体层,用作源区和漏区的氧化物半导体层为氧缺欠半导体层。

当将氧缺欠氧化物半导体层作为源区和漏区104a、104b来设置,使为金属层的源电极层和漏电极层105a、105b和半导体层103(氧过剩氧化物半导体层)之间具有良好的结,且与肖特基结相比具有更高热稳定性。另外,为了供给沟道载流子(源极侧)、稳定地吸收来自沟道的载流子(漏极侧)或者防止在与源电极层(或漏电极层)的界面产生电阻,积极地设置源区和漏区是有效的。通过低电阻化,即使在高漏极电压下也可以保持良好的迁移率。

由于在半导体层103的沟道形成区上设置沟道保护层133,所以可以防止半导体层103的沟道形成区在工序中损伤(可以防止蚀刻时产生的等离子体或蚀刻剂造成的厚度降低、氧化等)。由此可以提高薄膜晶体管170的可靠性。

图1B示出共同连接部的俯视图的一个例子,图1B中的虚线G1-G2相当于图1A的共同连接部的截面。注意,在图1B中与图1A类似的部分使用相同的附图标记来标明。

共同电位线185设置在栅极绝缘层102上,并由与源电极层和漏电极层105a、105b相同的材料及在相同的工序中制造。

共同电位线185由保护绝缘层107覆盖,保护绝缘层107在与共同电位线185重叠的位置具有多个开口部。该开口部通过与连接源电极层或漏电极层105a、105b和像素电极层110的接触孔相同的工序而制造。

注意,由于其尺寸差异很大,所以将其区分称为像素部中的接触孔和共同连接部中的开口部。在图1A中,像素部和共同连接部不是使用相同的缩尺来图示的,例如共同连接部的虚线G1-G2的长度为500μm左右,而薄膜晶体管的宽度小于50μm,因此,共同连接部面积是薄膜晶体管的10倍或以上,但是为了进行简化,在图1A中改变了像素部和共同连接部的缩尺。

共同电极层190设置在保护绝缘层107上,并由与像素部的像素电极层110相同的材料和在相同的工序中制造。

如此,在与像素部的开关元件的相同的制造工序中制造共同连接部。

然后,使用密封材料将设置有像素部和共同连接部的第一衬底100固定到具有对置电极的第二衬底。

当密封材料包含导电粒子时,对一对的衬底(第一衬底以及第二衬底)进行对准以使密封材料和共同连接部重叠。例如,在小型的液晶面板中,在像素部的对角等处与密封材料重叠地配置两个共同连接部。在大型的液晶面板中,与密封材料重叠地配置四个或以上的共同连接部。

注意共同电极层190是与包含在密封材料中的导电粒子接触的电极,并与第二衬底的对置电极电连接。

当使用液晶注入法时,在使用密封材料固定一对衬底之后,将液晶注入到一对衬底之间。当使用液晶滴落法时,在第二衬底或第一衬底上涂画密封材料,在使液晶滴落在其上后,在减压下将一对衬底贴合。

在本实施方式中,虽然示出与对置电极电连接的共同连接部的例子,但是本发明不特别局限于此例子,还可以用于与其他的布线连接的连接部或与外部连接端子等连接的连接部。

例如,当制造发光显示装置时,其与液晶显示装置不同而没有用于与对置电极连接的连接部分,但是发光显示装置具有将发光元件的阴极(负电极)连接到共同布线的部分,该部分可具有与图1A所示的相同的连接结构。对于每个像素,发光元件的阴极可以具有连接部,或者在像素部和驱动电路部之间设置连接部。

实施方式2

在本实施方式中,图2A和2B示出其中使用由与栅极布线相同的材料以及在相同的工序中形成的布线用作共同电位线的制造共同连接部(焊盘部)的例子。

图2B示出共同连接部的俯视图的一个例子,图2B中的虚线E1-E2相当于图2A的共同连接部的截面。

注意如图2A所示,像素部中的薄膜晶体管的结构与实施方式1相同,所以与图1A类似的部分使用相同的附图标记,而在这里省略其详细说明。

共同电位线181设置在第一衬底100上,并由与栅电极层101相同的材料以及在相同的工序中制造。

另外,共同电位线181由栅极绝缘层102和保护绝缘层107覆盖,栅极绝缘层102和保护绝缘层107在与共同电位线181重叠的位置具有多个开口部。该开口部与实施方式1不同,具有相当于两层绝缘层厚度的大的深度。注意,在通过与连接源电极层105a或漏电极层105b和像素电极层110的接触孔相同的工序中的蚀刻、然后进一步对栅极绝缘层102进行选择性的蚀刻而制造该开口部。

共同电极层190设置在保护绝缘层107上,并由与像素部中的像素电极层110相同的材料以及在相同的工序中制造。

如此,由与像素部的开关元件相同的制造工序制造共同连接部。

然后,使用密封材料将设置有像素部和共同连接部的第一衬底100固定至具有对置电极的第二衬底。

当密封材料中包含导电粒子时,对一对的衬底进行对准以使密封材料和共同连接部重叠。

注意共同电极层190是与包含在密封材料中的导电粒子接触的电极,并与第二衬底的对置电极电连接。

当使用液晶注入法时,在使用密封材料固定一对衬底之后,将液晶注入到一对衬底之间。当使用液晶滴落法时,在第二衬底或第一衬底上涂画密封材料,在使液晶滴落在其上后,在减压下将一对衬底进行贴合。

在本实施方式中,虽然示出与对置电极电连接的共同连接部的例子,但是本发明不特别局限于此例子,还可以用于与其他的布线连接的连接部或与外部连接端子等连接的连接部。

实施方式3

在该实施方式中,图3A和图3B示出制造共同连接部(焊盘部)的例子,在共同连接部(焊盘部)中形成由与栅极布线相同的材料以及在相同的工序中形成的电极,以及作为电极上的共同电位线,提供由与源电极层相同的材料以及在相同的工序中形成的布线。

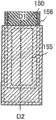

图3B是示出共同连接部的俯视图的一个例子的图,图3B中的虚线F1-F2相当于图3A的共同连接部的截面。

注意,如图3A所示像素部的薄膜晶体管的结构与实施方式1相同,所以与图1A相似的部分使用相同的附图标记,而在这里省略其详细说明。

连接电极层191设置在第一衬底100上,并由与栅电极层101相同的材料以及在相同的工序中制造。

另外,连接电极层191由栅极绝缘层102和保护绝缘层107覆盖,栅极绝缘层102和保护绝缘层107在与共同电极层190重叠的位置具有开口部。该开口部与实施方式1不同,具有相当于两层绝缘层厚度的大的深度。注意,在通过与连接源电极层105a或漏电极层105b和像素电极层110的接触孔相同的工序中的蚀刻、之后进一步对栅极绝缘层102进行选择性的蚀刻而制造该开口部。

共同电位线185设置在栅极绝缘层102上,并由与源电极层和漏电极层105a、105b相同的材料以及在相同的工序中制造。

共同电位线185由保护绝缘层107覆盖,保护绝缘层107在与共同电位线185重叠的位置具有多个开口部。该开口部通过与连接源电极层105a或漏电极层105b和像素电极层110的接触孔相同的工序而制造。

共同电极层190设置在保护绝缘层107上,并由与像素部的像素电极层110相同的材料以及在相同的工序中制造。

如此,由与像素部的开关元件的制造工序制造共同连接部。

然后使用密封材料将设置有像素部和共同连接部的第一衬底100固定至具有对置电极的第二衬底。

注意,在本实施方式中,在栅极绝缘层102的开口部选择性地设置多个导电粒子。即,在共同电极层190与连接电极层191接触的区域中设置多个导电粒子。与连接电极层191和共同电位线185的双方都连接的共同电极层190通过导电粒子与第二衬底的对置电极电连接。

当使用液晶注入法时,在使用密封材料固定一对衬底之后,将液晶注入到一对衬底之间。当使用液晶滴落法时,在第二衬底或第一衬底上涂画密封材料,在使液晶滴落在其上后,在减压下将一对衬底进行贴合。

在本实施方式中,虽然示出与对置电极电连接的共同连接部的例子,但是本发明不特别局限于此例子,还可以用于与其他的布线连接的连接部或与外部连接端子等连接的连接部。

实施方式4

在此实施方式中,图29A和29B示出实施方式1中示出显示装置的另一个例子,其中源电极层和漏电极层及源区和漏区使用相同的掩模进行蚀刻而形成。

图29A是其中将薄膜晶体管和共同连接部(焊盘部)制造在同一衬底上的半导体装置的截面结构图。图29A所示的薄膜晶体管172是具有沟道保护层的反交错型薄膜晶体管,在半导体层103的沟道形成区上设置沟道保护层133,并在半导体层103和沟道保护层133上隔着源区和漏区104a、104b设置有源电极层和漏电极层105a、105b。在薄膜晶体管172中,使用相同的掩模来蚀刻形成源区和漏区104a、104b的氧化物半导体层和形成源电极层和漏电极层105a、105b的导电层。

由此,在薄膜晶体管172中,源电极层和漏电极层105a、105b和源区和漏区104a、104b具有相同的形状,源区和漏区104a、104b在源电极层和漏电极层105a、105b的下方。

所以,在共同连接部中,在栅极绝缘层102和共同电位线185之间形成有由与源区和漏区104a、104b相同的材料以及在相同的工序中制造的氧化物半导体层186。

注意图29B示出共同连接部的俯视图的一个例子,图29B中的虚线G1-G2相当于图29A的共同连接部的截面。

注意如图29B所示,共同连接部的俯视图具有与实施方式1相同的结构,所以与图1B相似的部分使用相同的附图标记,而在这里省略其详细说明。

根据本实施方式,在设置在像素部的外侧区域的共同连接部(焊盘部)中,层叠氧化物半导体层和导电层,由此可以防止由于薄膜的分离造成的缺陷。另外,通过采用层叠氧化物半导体层和导电层的结构,焊盘部厚度增加,其电阻降低,而可以具有强度增加的结构。

实施方式5

在本实施方式中,图30A和30B示出实施方式3中示出的显示装置的另一个例子,其中源电极层和漏电极层及源区和漏区使用相同的掩模进行蚀刻而形成。

图30A是其中薄膜晶体管和共同连接部(焊盘部)制造在同一衬底上的半导体装置的截面结构图。

注意,如图30A所示像素部的薄膜晶体管的结构与实施方式4相同,所以与图29A相似的部分使用相同的附图标记,而在这里省略其详细说明。

在薄膜晶体管172中,使用相同的掩模蚀刻形成源区和漏区104a、104b的氧化物半导体层,和形成源电极层和漏电极层105a、105b的导电层。由此,在薄膜晶体管172中,源电极层和漏电极层105a、105b和源区和漏区104a、104b具有相同的形状,源区和漏区104a、104b在源电极层和漏电极层105a、105b的下方。

在共同连接部中,在栅极绝缘层102和共同电位线185之间形成有由与源区和漏区104a、104b相同的材料以及在相同的工序中制造的氧化物半导体层186。

图30B示出共同连接部的俯视图的一个例子,图30B中的虚线F1-F2相当于图30A的共同连接部的截面。

注意如图30B所示,共同连接部的俯视图的结构与实施方式3相同,所以与图3B相似的部分使用相同的附图标记,而在这里省略其详细说明。

根据该实施方式,在设置在像素部的外侧区域的共同连接部(焊盘部)中,层叠氧化物半导体层和导电层,由此可以防止由于薄膜的分离造成的缺陷。另外,通过采用层叠氧化物半导体层和导电层的结构,焊盘部厚度增加,其电阻降低,而可以具有强度增加的结构。

实施方式6

在本实施方式中,参照图4A至4C、图5A至5C、图6-图9、图10A和10B以及图11对包括本发明的一个实施方式的薄膜晶体管的显示装置的制造工序进行说明。本发明显示装置所包括的薄膜晶体管为具有沟道保护层的反交错型薄膜晶体管。

在图4A中,作为具有透光性的第一衬底100,可以使用以康宁公司制造的#7059玻璃、或#1737玻璃等为代表的钡硼硅酸盐玻璃或铝硼硅酸盐玻璃等的玻璃衬底。

在将导电层形成在第一衬底100的整个表面上之后,进行第一光刻工序形成抗蚀剂掩模,然后通过蚀刻去除不需要的部分来形成布线及电极(包括栅电极层101的栅极布线、电容布线108以及第一端子121)。在此,进行蚀刻,使得将至少栅电极层101的端部(edge)形成为锥形。图4A示出该阶段的截面图。注意图6是该阶段的俯视图。

包括栅电极层101的栅极布线、电容布线108、以及端子部的第一端子121优选使用铝(Al)或铜(Cu)等的低电阻导电材料形成,然而,单独Al有耐热性低及容易腐蚀等缺点,所以其与耐热性导电材料组合来使用。耐热性导电材料可以使用选自钛(Ti)、钽(Ta)、钨(W)、钼(Mo)、铬(Cr)、钕(Nd)、钪(Sc)中的元素、以任意上述元素为成分的合金、任意上述元素的组合的合金或者以任意上述元素为成分的氮化物。

接着,在栅电极层101的整个表面上形成栅极绝缘层102。栅极绝缘层102利用溅射法等并以50nm至250nm的厚度形成。

例如,通过溅射法并以100nm的厚度形成氧化硅膜作为栅极绝缘层102。当然,栅极绝缘层102不局限于这种氧化硅膜,也可以使用例如氧氮化硅膜、氮化硅膜、氧化铝膜、或氧化钽膜等的其他绝缘膜以构成单层结构或多层结构。

可以在形成成为沟道形成区的氧化物半导体层(IGZO半导体层)之前,利用等离子体处理对栅极绝缘层的表面进行清洗。进行去除存在于栅极绝缘层的表面的有机物等的碎屑的等离子体处理是有效的。另外,有效的是:栅极绝缘层表面经等离子体处理而成为用作氧的供给源的氧过剩区域,其在热处理(200℃至600℃)中对栅极绝缘层和IGZO半导体层之间的界面改性以在后面的工序中提高可靠性。

优选在等离子体处理之后不暴露于大气地利用溅射法沉积氧化物半导体层。如果在沉积氧化物半导体层之前,沉积靶衬底接触到大气,则沉积靶衬底可能会附着有水分等,而可能对界面状态有不良影响,从而导致阈值的不均匀、电特性的劣化或变成常开(nonnally on)TFT等。等离子体处理使用氧气体或氩气体来进行。还可以使用其它的稀有气体替代氩气体。

为了在等离子体处理之后不暴露于大气地利用溅射法沉积成为沟道形成区的氧化物半导体层,优选进行称为反溅射处理的等离子体处理的一种,该反溅射处理可以在与形成氧化物半导体层的同一个反应室中进行。反溅射处理是指不向靶侧施加电压,而在氧气氛或氧以及氩气氛下对衬底侧施加电压而产生等离子体来对衬底上的薄膜表面进行改性的方法。

当在使用氧气体填充的反应室中进行等离子体处理时,通过对栅极绝缘层的表面照射氧自由基,从而将栅极绝缘层的表面改性成氧过剩区域,从而提高与后面沉积的成为沟道形成区的氧化物半导体层的界面的氧浓度。也就是说,如果对栅极绝缘层进行氧自由基处理,其上层叠氧化物半导体层,之后进行加热处理,则也可以使成为沟道形成区的氧化物半导体层的在栅极绝缘层侧的氧浓度增加。因此,在栅极绝缘层与成为沟道形成区的氧化物半导体层的界面处具有氧浓度的峰值,并且栅极绝缘层的氧浓度具有浓度梯度,该梯度朝着接近栅极绝缘层与成为沟道形成区的氧化物半导俺层的界面而增加。包括氧过剩区域的栅极绝缘层与成为氧过剩氧化物半导体层的沟道形成区的氧化物半导体层的亲和性高,使得栅极绝缘层与氧过剩氧化物半导体层之间可以得到良好的界面特性。

既可利用包含氧的气体通过等离子体产生装置产生氧自由基,又可通过臭氧产生装置产生氧自由基。通过将所产生的氧自由基或氧照射到薄膜,能够对膜进行表面改性。

等离子体处理也可以使用氩和氧的自由基来进行,而不局限于使用氧自由基的等离子体处理。使用氩和氧的自由基的处理是指通过引入氩气体和氧气体而产生等离子体以对薄膜进行表面改性的处理。

在施加电场而产生放电等离子体的反应空间中的Ar原子(Ar)被放电等离子体中的电子(e)激发或电离,而成为氩自由基(Ar*)、氩离子(Ar+)或电子(e)。氩自由基(Ar*)处于能量高的准稳定状态,其与周围的同种或异种原子起反应而回到稳定状态(通过使该原子激发或电离),由此发生如雪崩现象那样的反应。此时,若周围存在有氧,则氧原子(O)被激发或电离而成为氧自由基(O*)、氧离子(O+)或氧(O)。该氧自由基(O*)与被处理的薄膜表面的材料起反应而对表面进行改性,并且氧自由基还与表面上的有机物起反应而去除有机物,由此进行等离子体处理。注意,与反应性气体(氧气体)的自由基相比,氩气体的自由基具有更长时间地维持准稳定状态的特性,因此通常使用氩气体以产生等离子体。

接下来,在栅极绝缘层102上形成第一氧化物半导体膜(在本实施方式中第一IGZO膜)。在等离子体处理后,不暴露于大气地沉积第一IGZO膜,这在不使栅极绝缘层与半导体膜之间的界面处附着尘屑或水分这点上是有利的。这里,使用直径为8英寸的包含In、Ga及Zn的氧化物半导体靶(In2O3:Ga2O3:ZnO=1:1:1),衬底与靶之间的距离设定为170mm、压力0.4Pa、直流(DC)电源0.5kW、在氩或氧气氛下进行沉积。注意,优选使用脉冲直流(DC)电源可以减少尘屑且使膜的厚度分布均匀。将第一IGZO膜的厚度设定为5nm至200nm。在本实施方式中,将第一IGZO膜的厚度设定为100nm。

通过利用溅射法并适当地改变引入反应室内的气体或反应室中设置的靶,可以使栅极绝缘层和第一IGZO膜不暴露于大气地连续地沉积。当不使暴露于大气并连续沉积这些膜,可以防止杂质进入膜中。在不使暴露于大气并连续沉积这些膜的情况下,优选使用多室型制造装置。

接着,在与第一IGZO膜的沟道形成区重叠地形成沟道保护层133。也可以以不暴露于大气的方式在栅极绝缘层102、第一IGZO膜之后连续地沉积沟道保护层133。当以不暴露于大气的方式连续沉积层叠的层时可以提高生产率。

作为沟道保护层133,可以使用无机材料(氧化硅、氮化硅、氧氮化硅、氮氧化硅等)通过例如等离子体CVD法或热CVD法等的气相沉积法或溅射法来制成。沟道保护层133通过处理沉积膜的形状来获得。这里,通过溅射法形成氧化硅膜,然后使用通过光刻形成的掩模进行蚀刻而获得沟道保护层133。

接下来,利用溅射法在第一IGZO膜和沟道保护层133上沉积第二氧化物半导体膜(本实施方式的第二IGZO膜)。这里,使用In2O3:Ga2O3:ZnO=1:1:1的靶,并在如下条件下进行溅射沉积:压力0.4Pa;功率500W;温度为室温;氩气体流量为40sccm。虽然意图性地使用In2O3:Ga2O3:ZnO=1:1:1的靶,但在一些情况下在刚沉积后形成有包含直径为1nm至10nm的晶粒的IGZO膜。可以说通过适当地调整靶材的成分比、沉积压力(0.1Pa至2.0Pa)、功率(250W至3000W:8英寸φ)、或温度(室温至100℃)等反应性溅射的沉积条件,可以控制晶粒的有无、晶粒的密度以及直径。将晶粒直径控制为1nm至10nm的范围内。第二IGZO膜的厚度为5nm至20nm。当然,如果在膜中包括晶粒,晶粒的直径不超过膜的厚度。在本实施方式中,第二IGZO膜的厚度为5nm。

使第一IGZO膜的沉积条件与第二IGZO膜的沉积条件相异,使得第一IGZO膜中比第二IGZO膜中的氧浓度更高。例如,与第二IGZO膜的沉积条件中的氧气与氩气流量比相比,第一IGZO膜的沉积条件中的氧气与氩气流量比更高。具体地,第二IGZO膜在稀有气体(氩或氦等)气氛下(或含氧10%或以下、含氩气体90%或以上的气氛)沉积,第一IGZO膜在氧气氛下(或氧气体的流量与氩气体的流量相等或大于氩气体的流量)沉积。当更多的氧包含在第一IGZO膜中,可以使得第一IGZO膜的电导率低于第二IGZO膜电导率。另外,当更多的氧包含在第一IGZO膜中可以实现第一IGZO膜截止电流的降低,所以可以得到导通截止比高的薄膜晶体管。

第二IGZO膜可以使用与之前反溅射处理所使用的反应室同一反应室沉积,或者只要可以在不暴露于大气地进行沉积的情况下,也可以在与之前进行反溅射处理所使用的反应室不同的反应室中沉积。

接下来,优选以200℃至600℃,典型的是300℃至500℃进行热处理。在此在炉中,在氮气氛下以350℃进行1小时的热处理。该热处理使得IGZO膜的原子能级的重新排列。在此步骤的热处理(包括光退火)因为可以释放阻碍载流子迁移的应变能而所以是重要的。注意,进行热处理的时序没有特别的限制,该热处理可以在沉积第二IGZO膜之后任意时间进行,例如可以在形成像素电极之后进行。

接着,进行第二光刻工序形成抗蚀剂掩模,并且对第一IGZO膜及第二IGZO膜进行蚀刻。在此,通过使用ITO07N(日本关东化学株式会社制造)的湿蚀刻去除不需要的部分,来形成氧过剩型第一IGZO膜的半导体层103及氧缺欠型第二IGZO膜的IGZO膜111。注意,此蚀刻步骤不局限于湿蚀刻,也可以进行干蚀刻。图4B示出该阶段中的截面图。另外,图7是该阶段的俯视图。

接下来,利用溅射法或真空蒸镀法在半导体层103以及IGZO膜111上形成由金属材料制成的导电膜132。图4C示出该阶段中的俯视图。

作为导电膜132的材料,可以举出选自Al、Cr、Ta、Ti、Mo、W中的元素或以任意上述元素为成分的合金、包含任意上述元素的组合的合金等。如果进行200℃至600℃的热处理,优选使导电膜具有承受该热处理的耐热性。由于单独铝具有耐热性很低且容易腐蚀等缺点,所以与耐热导电材料组合来使用。作为与Al组合的耐热导电材料,可以使用选自钛(Ti)、钽(Ta)、钨(W)、钼(Mo)、铬(Cr)、钕(Nd)、Sc(钪)中的元素、以任意上述元素为成分的合金、包含任意上述元素的组合的合金或者以任意上述元素为成分的氮化物。

在此,作为导电膜132使用钛膜的单层结构。导电膜132还可以采用其中在铝膜上层叠钛膜的双层结构。或者,导电膜132还可以采用如下三层结构:按顺序堆叠的Ti膜、包含钕的铝膜(Al-Nd膜)以及Ti膜。另外或者是,导电膜132还可以采用包含硅的铝膜的单层结构。

接着,进行第三光刻工序形成抗蚀剂掩模131,并通过蚀刻去除不必要的部分来形成源电极层和漏电极层105a、105b以及源区和漏区104a、104b。该蚀刻步骤使用湿蚀刻或干蚀刻来进行。例如,在作为导电膜132使用铝膜或铝合金膜情况下,可以进行使用了将磷酸、醋酸以及硝酸混合的溶液的湿蚀刻。这里,通过使用了过氧化氢氨水混合物(过氧化氢:氨水:水=5:2:2),对Ti制成的导电膜132进行湿蚀刻来形成源电极层和漏电极层105a、105b,并对IGZO膜111进行湿蚀刻来形成源区和漏区104a、104b。在该蚀刻工序中,由于沟道保护层133用作半导体层103的蚀刻停止层,所以半导体层103不被蚀刻。在图5A中,由于利用过氧化氢氨水混合物对源电极层和漏电极层105a、105b以及源区和漏区104a、104b同时蚀刻,所以源电极层和漏电极层105a、105b的端部与源区和漏区104a、104b的端部对准,从而具有连续的结构。此外,由于使用湿蚀刻允许这些层被各向同性地蚀刻,所以源电极层和漏电极层105a、105b的端部比抗蚀剂掩模131更缩退。通过上述工序可以制造包括IGZO半导体层103用作沟道形成区,并在沟道形成区上具有沟道保护层133的薄膜晶体管170。图5A示出该阶段中的截面图。注意图8相当于该阶段的俯视图。

由于在半导体层103的沟道形成区上设置沟道保护层133,所以可以防止在工序中损伤(可以防止蚀刻时产生的等离子体或蚀刻剂造成的厚度降低、氧化等)半导体层103的沟道形成区。由此可以提高薄膜晶体管170的可靠性。

在该第三光刻工序中,在端子部中留有由与源电极层和漏电极层105a、105b相同材料制成的第二端子122。注意,第二端子122与源极布线(包括源电极层和漏电极层105a、105b的源极布线)电连接。

如果使用利用多级灰度掩模而形成的具有不同厚度(典型的是两种厚度)的多个区域的抗蚀剂掩模,可以减少抗蚀剂掩模的数目,所以可以谋求工序的简化以及低成本化。

接下来,去除抗蚀剂掩模131,形成覆盖薄膜晶体管170的保护绝缘层107。保护绝缘层107可以使用利用溅射法等获得的氮化硅膜、氧化硅膜、氧氮化硅膜、氧化铝膜或氧化钽膜等来形成。

接着,进行第四光刻工序,形成抗蚀剂掩模,通过保护绝缘层107的蚀刻以形成到达源电极层105a或漏电极层105b的接触孔125。另外,通过该同一蚀刻工序还形成到达第二端子122的接触孔127。为了减少掩模数,优选使用同一掩模对栅极绝缘层进行蚀刻,使得使用同一抗蚀剂掩模形成到达栅电极的接触孔126。图5B示出该阶段中的截面图。

接下来,去除抗蚀剂掩模,然后形成透明导电膜。作为透明导电膜,利用溅射法或真空蒸镀法等使用氧化铟(In2O3)、氧化铟-氧化锡合金(缩写为ITO的In2O3-SnO2)来形成。使用盐酸类的溶液进行上述材料的蚀刻。但是,因为ITO的蚀刻尤其容易产生残渣,所以也可以使用氧化铟-氧化锌合金(In2O3-ZnO),以改善蚀刻加工性。

接着,进行第五光刻工序,形成抗蚀剂掩模,通过蚀刻去除不需要的部分,而形成像素电极层110。

在该第五光刻工序中,以在电容部中的栅极绝缘层102及保护绝缘层107为电介质,在电容布线108和像素电极层110之间形成存储电容。

另外,在该第五光刻工序中,使用抗蚀剂掩模覆盖第一端子和第二端子使得在端子部中留有透明导电膜128、129。透明导电膜128、129成为与FPC连接的电极或布线。形成在第二端子122上的透明导电膜129是用作源极布线的输入端子的连接用端子电极。

接着,去除抗蚀剂掩模,图5C示出该阶段中的截面图。另外,图9是该阶段的俯视图。

图10A和10B分别是该阶段的栅极布线端子部的俯视图和截面图。图10A是沿着图10B中的C1-C2线的截面图。在图10A中,形成在保护绝缘膜154上的透明导电膜155是用作输入端子的连接用端子电极。另外,在图10A中,在端子部中,由与栅极布线相同材料形成的第一端子151与由与源极布线相同材料形成的连接电极层153隔着栅极绝缘层152重叠,并通过透明导电膜155电连接。注意,图5C的透明导电膜128与第一端子121所接触的部分对应于图10A的透明导电膜155与第一端子151所接触的部分。

图10C和10D分别是与图5C所示的源极布线端子部不同的源极布线端子部的截面图和俯视图。图10C是沿着图10D中的D1-D2线的截面图。在图10C中,形成在保护绝缘膜154上的透明导电膜155是用作输入端子的连接用端子电极。另外,在图10C中,在端子部中,

由与栅极布线相同材料形成的电极层156,在与源极布线电连接的第二端子150的下方形成且隔着栅极绝缘层152与第二端子150重叠。电极层156不与第二端子150电连接,如果将电极层156电位设定为与第二端子150不同的电位,例如浮置、GND、0V等,可以形成防止杂波的电容或防止静电的电容。第二端子150隔着保护绝缘膜154与透明导电膜155电连接。

根据像素密度设置多个栅极布线、源极布线以及电容布线。另外,在端子部中,排列多个与栅极布线同电位的第一端子、多个与源极布线同电位的第二端子、多个与电容布线同电位的第三端子等。各端子的数目没有特别限制,实施者可以适当地决定端子数目。

通过这五次的光刻工序,使用五个光掩模,可以完成具有底栅型的n沟道型薄膜晶体管的薄膜晶体管170的像素薄膜晶体管部以及存储电容。当这些像素薄膜晶体管部和存储电容对应于相应像素以矩阵状排列时,形成像素部,并且可以获得用来制造有源矩阵型的显示装置的一个衬底。在本说明书中,为了方便将该衬底称为有源矩阵衬底。

在制造有源矩阵型的液晶显示装置情况下,在有源矩阵衬底与设置有对置电极的对置衬底之间设置液晶层,将有源矩阵衬底与对置衬底贴合。注意,将与设置在对置衬底上的对置电极电连接的共同电极设置在有源矩阵衬底上,并将与共同电极电连接的第四端子设置在端子部。该第四端子是用来将共同电极固定在预定电位,例如GND、或0V等。

本发明的一个实施方式不局限于图9的像素结构,图11示出与图9不同的俯视图的例子。图11示出其中不设置电容布线,像素电极层与相邻的像素的栅极布线隔着保护绝缘膜以及栅极绝缘层而重叠以形成存储电容的例子。在此情况下,可以省略电容布线以及与电容布线连接的第三端子。注意在图11中,与图9类似的部分使用相同的附图标记标明。

在有源矩阵型的液晶显示装置中,驱动排列为矩阵状的像素电极,以在屏幕上形成显示图案。具体地,对选择的像素电极和对应于该像素电极的对置电极之间施加电压,使得对设置在像素电极与对置电极之间的液晶层进行光学调制,该光学调制由观察者认出是显示图案。

当液晶显示装置显示运动图像时,由于液晶分子本身长的响应时间,所以液晶显示装置存在出现余像或出现运动图像模糊的问题。为了改善液晶显示装置的运动图像特性,采用被称为黑插入的驱动方法,其中每隔一个帧期进行整个屏幕的黑显示。

或者,可采用被称为倍帧速率驱动的驱动方法,其中将垂直周期设定为通常的1.5倍或2倍长来改善运动图像特性。

另外或者是,为了改善液晶显示装置的运动图像特性,可采用一种驱动方法,其中作为背光灯,使用多个LED(发光二极管)或多个EL光源构成面光源,将面光源的各个光源独立地在一个帧期内进行脉冲方式驱动。作为面光源,可以使用三种或以上的LED或白色发光LED。由于可以独立地控制多个LED,所以可以使LED的发光时序与液晶层的光学调制的时序同步进行。根据该驱动方法,可以将LED部分地关断,所以尤其是在显示大部分是黑显示的图像情况下,可以实现低耗电量的效果。

通过组合上述驱动方法,可以相比现有液晶显示装置改善液晶显示装置的运动图像特性等的显示特性。

通过本实施方式得到的n沟道型晶体管在沟道形成区中包含IGZO半导体层,并具有良好的动态特性,所以对该实施例的n沟道晶体管可以组合地应用这些驱动方法。

在制造发光显示装置情况下,将有机发光元件的一个电极(也称为阴极)设定为低电源电位,例如GND、0V等,所以在端子部设置有用来将阴极设定为低电源电位、例如GND、0V等的第四端子。另外,在制造发光显示装置情况下,除源极布线和栅极布线之外还设置电源供给线。所以,在端子部中设置有与电源供给线电连接的第五端子。

如果不设置源区和漏区(包含In、Ga及Zn的氧缺欠氧化物半导体层)而堆叠栅电极层、栅极绝缘层、半导体层(含有In、Ga以及Zn的氧过剩氧化物半导体层)、源电极层和漏电极层,栅电极层与源和漏电极层之间的距离被降低,从而导致在其之间产生的寄生电容增加。此外,该寄生电容进一步因半导体层的厚度降低而增加。在本实施方式中,薄膜晶体管采用栅电极层、栅极绝缘层、半导体层、源区和漏区、源电极层和漏电极层的叠层结构,即使半导体层的厚度小也可以抑制寄生电容。

根据本实施方式可以制造光电流少、寄生电容小、导通截止比高、具有良好的动态特性的薄膜晶体管。因此,可以提供具有电特性高并可靠性高的薄膜晶体管的半导体装置。

实施方式7

在该实施方式中,图31A和31B示出在实施方式3中的显示装置的另一例子,其包括其中源电极层和漏电极层与半导体层接触的薄膜晶体管。

图31A是在同一衬底上制造薄膜晶体管和共同连接部(焊盘部)的半导体装置的截面结构图。图31A所示的薄膜晶体管171为具有沟道保护层的反交错型薄膜晶体管。在半导体层103的沟道形成区上设置沟道保护层133,并在半导体层103和沟道保护层133上接触于半导体层103地设置源电极层和漏电极层105a、105b。

在薄膜晶体管171中,优选利用等离子体处理来对半导体层103与源电极层和漏电极层105a、105b之间的接触区域进行改性。在本实施方式中,在形成用作源电极层和漏电极层的导电膜之前,对氧化物半导体层(本实施方式中的IGZO半导体层)进行等离子体处理。

作为等离子体处理,使用氩气体、氢气体或氩和氢的混合气体。可以在上述气体中加入氧气体。可以使用其它稀有气体代替氩气体a

如图32所示,在半导体层103上形成绝缘层135以及绝缘层136作为层间绝缘层。源电极层和漏电极层105a、105b,通过形成在绝缘层135以及绝缘层136中的接触孔,与半导体层103接触并电连接。

注意在图32中,分别利用溅射法形成氧化硅层作为栅极绝缘层102以及沟道保护层133,形成IGZO氧过剩半导体层作为半导体层103,并形成氮化硅层作为绝缘层135。

在图32中也优选在形成源电极层和漏电极层105a、105b之前对半导体层103进行等离子体处理。也可以在半导体层103上形成沟道保护层133之后进行等离子体处理。或者,可以在绝缘层135以及绝缘层136中形成接触孔之后,对在每个接触孔底面露出的半导体层103上进行等离子体处理。

接触通过等离子体处理而改性的半导体层103地形成导电层,由此形成源电极层和漏电极层105a、105b,因此可以降低半导体层103与源电极层和漏电极层105a、105b之间的接触电阻。

通过上述工序,可以制造作为半导体装置可靠性高的显示装置。

本实施方式可以与其他的实施方式所记载的结构适当地组合而实施。

实施方式8

在本实施方式中,将说明作为本发明的半导体装置的一个例子的显示装置的例子。在该显示装置中,在一个衬底上至少形成驱动电路的一部分以及设置在像素部的薄膜晶体管。

根据实施方式6或实施方式7形成设置在像素部中的薄膜晶体管。此外,实施方式6或实施方式7所示的薄膜晶体管是n沟道型TFT,因此将驱动电路中可以包括n沟道型TFT的驱动电路的一部分形成在与像素部中的薄膜晶体管相同的衬底上。

图13A示出作为本发明的半导体装置例子的有源矩阵型液晶显示装置的框图的例子。图13A所示的显示装置在衬底5300上包括:具有多个各自具备显示元件的像素的像素部5301;选择像素的扫描线驱动电路5302;以及控制至所选像素的视频信号输入的信号线驱动电路5303。

像素部5301通过从信号线驱动电路5303在列方向上延伸的多个信号线S1-Sm(未图示)与信号线驱动电路5303连接,并且通过从扫描线驱动电路5302在行方向上延伸的多个扫描线G1-Gn(未图示)与扫描线驱动电路5302连接。像素部5301具有配置为矩阵以对应于信号线S1-Sm以及扫描线G1-Gn的多个像素(未图示)。各个像素与信号线Sj(信号线S1-Sm中之一)和扫描线Gi(扫描线G1-Gn中之一)连接。

实施方式6或7中所示的薄膜晶体管是n沟道型TFT,并且参照图14说明包含n沟道型TFT的信号线驱动电路。

图14所示的信号线驱动电路包括:驱动器IC5601;开关群5602_1至5602_M;第一布线5611;第二布线5612;第三布线5613;以及布线5621_1至5621_M。开关群5602_1至5602_M中的每个包括第一薄膜晶体管5603a、第二薄膜晶体管5603b以及第三薄膜晶体管5603c。

驱动器IC5601连接到第一布线5611、第二布线5612、第三布线5613及布线5621_1至5621_M。开关群5602_1至5602_M中的每个连接到第一布线5611、第二布线5612和第三布线5613,并且开关群5602_1至5602_M分别连接到布线5621_1至5621_M。布线5621_1至5621_M中的每个通过第一薄膜晶体管5603a、第二薄膜晶体管5603b及第三薄膜晶体管5603c连接到三个信号线。例如,第J列的布线5621_J(布线5621_1至布线5621_M中之一)通过开关群5602_J中包含的第一薄膜晶体管5603a、第二薄膜晶体管5603b及第三薄膜晶体管5603c连接到信号线sj-1、信号线sj、信号线sj+1。

对第一布线5611、第二布线5612与第三布线5613中的每个输入信号。

注意,驱动器IC5601优选形成在单晶衬底上。再者,开关群5602_1至5602_M优选形成在与像素部相同的衬底上。因此,驱动器IC5601优选通过FPC等连接到开关群56021至5602M。

接着,参照图15的时序图说明图14所示的信号线驱动电路的工作。图15的时序图示出选择第i行扫描线Gi的情况。第i行扫描线Gi的选择期被分为第一子选择期T1、第二子选择期T2及第三子选择期T3。此外,图14的信号线驱动电路即使在选择其他行的扫描线时也按与图15相似的方式工作。

注意,图15的时序图示出第J列布线5621J通过第一薄膜晶体管5603a、第二薄膜晶体管5603b及第三薄膜晶体管5603c连接到信号线Sj-1、信号线Sj与信号线sj+1的情况。

图15的时序图示出第i行扫描线Gi被选择的时序、第一薄膜晶体管5603a导通/截止的时序5703a、第二薄膜晶体管5603b导通/截止的时序5703b、第三薄膜晶体管5603c导通/截止的时序5703c及输入到第J列布线5621_J的信号5721_J。

在第一子选择期T1、第二子选择期T2及第三子选择期T3中,对布线5621_1至布线5621_M输入不同的视频信号。例如,在第一子选择期T1中输入到布线5621_J的视频信号被输入到信号线sj-1,在第二子选择期T2中输入到布线5621_J的视频信号被输入到信号线Sj,在第三子选择期T3中输入到布线5621_J的视频信号被输入到信号线Sj+1。在第一子选择期T1、第二子选择期T2及第三子选择期T3中输入到布线5621J的视频信号分别表示为Dara_j-1、Dara_j、Data_3+1。

如图15所示,在第一子选择期T1中,第一薄膜晶体管5603a导通,而第二薄膜晶体管5603b及第三薄膜晶体管5603c截止。此时,输入到布线5621_J的Dara_j-1通过第一薄膜晶体管5603a输入到信号线Sj-1。在第二子选择期T2中,第二薄膜晶体管5603b导通,而第一薄膜晶体管5603a及第三薄膜晶体管5603c截止。此时,输入到布线5621_J的Data_j通过第二薄膜晶体管5603b输入到信号线Sj。在第三子选择期T3中,第三薄膜晶体管5603c导通,而第一薄膜晶体管5603a及第二薄膜晶体管5603b截止。此时,输入到布线5621_J的Data_j+1通过第三薄膜晶体管5603c输入到信号线Sj+1。

如上所述,在图14的信号线驱动电路中,通过将一个栅极选择期分为三个,可以在一个栅极选择期中将视频信号从一个布线5621输入到三个信号线。因此,在图14的信号线驱动电路中,可以将设置有驱动器IC5601的衬底和设置有像素部的衬底之间的连接数减少到信号线数的大约1/3。在将连接数减少到信号线数的大约1/3时,可以提高图14的信号线驱动电路的可靠性、成品率等。

注意,只要如图14所示将一个栅极选择期分为多个子选择期并在相应子选择期中将视频信号从一个布线输入到多个信号线,就不存在对薄膜晶体管的配置、数量、驱动方法等的特别限制。

例如,当在三个或更多子选择期中将视频信号从一个布线输入到三个或更多信号线时,只需要追加薄膜晶体管及用于控制薄膜晶体管的布线。注意,当将一个栅极选择期分为四个或更多子选择期时,一个子选择期变得较短。因此,优选将一个栅极选择期分为两个或三个子选择期。

作为另一个例子,如图16的时序图所示,可以将一个选择期分为预充电期Tp、第一子选择期T1、第二子选择期T2和第三子选择期T3。图16的时序图示出选择第i行扫描线Gi的时序、第一薄膜晶体管5603a导通/截止的时序5803a、第二薄膜晶体管5603b导通/截止的时序5803b、第三薄膜晶体管5603c导通/截止的时序5803c以及输入到第J列布线5621_J的信号5821_J。如图16所示,在预充电期Tp中,第一薄膜晶体管5603a、第二薄膜晶体管5603b及第三薄膜晶体管5603c导通。此时,输入到布线5621_J的预充电电压Vp通过第一薄膜晶体管5603a、第二薄膜晶体管5603b及第三薄膜晶体管5603c输入到信号线sj-1、信号线sj与信号线Sj+1中的每个。在第一子选择期T1中,第一薄膜晶体管5603a导通,第二薄膜晶体管5603b及第三薄膜晶体管5603c截止。此时,输入到布线5621_J的Data_j-1通过第一薄膜晶体管5603a输入到信号线sj-1。在第二子选择期T2中,第二薄膜晶体管5603b导通,而第一薄膜晶体管5603a及第三薄膜晶体管5603c截止。此时,输入到布线5621_J的Data_j通过第二薄膜晶体管5603b输入到信号线Sj。在第三子选择期T3中,第三薄膜晶体管5603c导通,而第一薄膜晶体管5603a及第二薄膜晶体管5603b截止。此时,输入到布线5621_J的Data_j+1通过第三薄膜晶体管5603c输入到信号线Sj+1。

如上所述,在应用图16中时序图的图14的信号线驱动电路中,可以将视频信号高速写入到像素,因为可以通过在子选择期之前提供预充电选择期对信号线进行预充电。注意,在图16中,用相同的附图标记来表示与图15相似的部分,并且省略对类似部分或具有相似功能的部分的详细说明。

此外,说明扫描线驱动电路的结构。扫描线驱动电路包括移位寄存器和缓冲器。此外,在一些情况中,扫描线驱动电路可以包括电平转移器(level shifter)。在扫描线驱动电路中,在对移位寄存器输入时钟信号(CLK)及起始脉冲信号(SP)时,生成选择信号。所生成的选择信号通过缓冲器缓冲和放大,并将所得信号供给到对应的扫描线。一条线的像素中的晶体管的栅电极连接到扫描线。由于一条线的像素中的晶体管必须一齐导通,因此使用可提供大电流的缓冲器。

参照图17和图18说明用于扫描线驱动电路的一部分的移位寄存器的一个方式。

图17示出移位寄存器的电路配置。图17所示的移位寄存器包括多个触发器(触发器5701_1至5701_n)。移位寄存器通过输入第一时钟信号、第二时钟信号、起始脉冲信号与复位信号而工作。

说明图17中移位寄存器的连接关系。在图17的移位寄存器的第i级触发器5701_i(触发器5701_1至5701_n中之一)中,图18所示的第一布线5501连接到第七布线5717_i-1,图18所示的第二布线5502连接到第七布线5717_i+1,图18所示的第三布线5503连接到第七布线5717_i,并且图18所示的第六布线5506连接到第五布线5715。

此外,图18所示的第四布线5504在奇数编号级触发器中连接到第二布线5712,而在偶数编号级触发器中连接到第三布线5713。图18所示的第五布线5505连接到第四布线5714。

注意,图18所示的第一级触发器57011中第一布线5501连接到第一布线5711。此外,图18所示的第n级触发器5701n中第二布线5502连接到第六布线5716。

注意,第一布线5711、第二布线5712、第三布线5713和第六布线5716可以分别称为第一信号线、第二信号线、第三信号线和第四信号线。第四布线5714和第五布线5715可以分别称为第一电源线和第二电源线。

接着,图18示出图17所示的触发器的详细结构。图18所示的触发器包括第一薄膜晶体管5571、第二薄膜晶体管5572、第三薄膜晶体管5573、第四薄膜晶体管5574、第五薄膜晶体管5575、第六薄膜晶体管5576、第七薄膜晶体管5577以及第八薄膜晶体管5578。第一薄膜晶体管5571、第二薄膜晶体管5572、第三薄膜晶体管5573、第四薄膜晶体管5574、第五薄膜晶体管5575、第六薄膜晶体管5576、第七薄膜晶体管5577以及第八薄膜晶体管5578中的每个是n沟道型晶体管,并且在栅极-源极电压(Vgs)超过阈值电压(Vth)时导通。

接着,下面示出图18所示的触发器的连接结构。

第一薄膜晶体管5571的第一电极(源电极与漏电极中之一)连接到第四布线5504。第一薄膜晶体管5571的第二电极(源电极与漏电极中的另一个)连接到第三布线5503。

第二薄膜晶体管5572的第一电极连接到第六布线5506。第二薄膜晶体管5572的第二电极连接到第三布线5503。

第三薄膜晶体管5573的第一电极连接到第五布线5505,并且第三薄膜晶体管的第二电极连接到第二薄膜晶体管5572的栅电极。第三薄膜晶体管5573的栅电极连接到第五布线5505。

第四薄膜晶体管5574的第一电极连接到第六布线5506。第四薄膜晶体管5574的第二电极连接到第二薄膜晶体管5572的栅电极。第四薄膜晶体管5574的栅电极连接到第一薄膜晶体管5571的栅电极。

第五薄膜晶体管5575的第一电极连接到第五布线5505。第五薄膜晶体管5575的第二电极连接到第一薄膜晶体管5571的栅电极。第五薄膜晶体管5575的栅电极连接到第一布线5501。

第六薄膜晶体管5576的第一电极连接到第六布线5506。第六薄膜晶体管5576的第二电极连接到第一薄膜晶体管5571的栅电极。第六薄膜晶体管5576的栅电极连接到第二薄膜晶体管5572的栅电极。

第七薄膜晶体管5577的第一电极连接到第六布线5506。第七薄膜晶体管5577的第二电极连接到第一薄膜晶体管5571的栅电极。第七薄膜晶体管5577的栅电极连接到第二布线5502。第八薄膜晶体管5578的第一电极连接到第六布线5506。第八薄膜晶体管5578的第二电极连接到第二薄膜晶体管5572的栅电极。第八薄膜晶体管5578的栅电极连接到第一布线5501。

注意,第一薄膜晶体管5571的栅电极、第四薄膜晶体管5574、的栅电极、第五薄膜晶体管5575的第二电极、第六薄膜晶体管5576的第二电极以及第七薄膜晶体管5577的第二电极相连接的点分别称为节点5543。第二薄膜晶体管5572的栅电极、第三薄膜晶体管5573的第二电极、第四薄膜晶体管5574的第二电极、第六薄膜晶体管5576的栅电极及第八薄膜晶体管5578的第二电极相连接的点分别称为节点5544。

注意,第一布线5501、第二布线5502、第三布线5503以及第四布线5504可以分别称为第一信号线、第二信号线、第三信号线和第四信号线。第五布线5505和第六布线5506可以分别称为第一电源线和第二电源线。

此外,可以仅使用实施方式6所述的n沟道型TFT形成信号线驱动电路及扫描线驱动电路。因为实施方式6所述的n沟道型TFT的高迁移率,所以可以提高驱动电路的驱动频率。另外,在实施方式6所述的n沟道型TFT中,由于通过作为包含铟、镓以及锌的氧欠缺氧化物半导体层的源区或漏区而减少寄生电容,因此可获得高频率特性(称为F特性)。例如,使用实施方式6所述的n沟道型TFT的扫描线驱动电路可以高速工作,因此可以提高帧频率并且实现黑屏图像插入等。

再者,在增大扫描线驱动电路中晶体管的沟道宽度或提供多个扫描线驱动电路时,可以实现更高的帧频率。在提供多个扫描线驱动电路时,将用于驱动偶数编号扫描线的扫描线驱动电路提供在一侧,并将用于驱动奇数编号扫描线的扫描线驱动电路提供在相反一侧,因此可以实现帧频率的提高。

此外,在制造作为本发明的半导体装置的例子的有源矩阵型发光显示装置时,在至少一个像素中配置多个薄膜晶体管,因此优选配置多个扫描线驱动电路。图13B是有源矩阵型发光显示装置的框图的例子。

图13B所示的发光显示装置在衬底5400上包括:具有多个各自具备显示元件的像素的像素部5401;选择像素的第一扫描线驱动电路5402及第二扫描线驱动电路5404;以及控制至所选像素的视频信号输入的信号线驱动电路5403。

在输入到图13B所示发光显示装置的像素的视频信号为数字方式时,通过切换晶体管导通/截止,像素发光或不发光。因此,可以采用面积灰度级法或时间灰度级法进行灰度级显示。面积灰度级法指的是其中将一个像素分为多个子像素并根据视频信号分别驱动相应子像素使得进行灰度级显示的一种驱动法。此外,时间灰度级法指的是其中控制像素发光的时段使得进行灰度级显示的一种驱动法。

因为发光元件的响应时间比液晶元件等的高,所以与液晶元件相比发光元件更适合于时间灰度级法。具体而言,在采用时间灰度级法进行显示的情况下,将一个帧期分为多个子帧期。然后,根据视频信号,在各子帧期中使像素的发光元件处于发光状态或非发光状态。通过将一个帧期分割为多个子帧期,在一个帧期中像素实际发光的总时间长度可受视频信号控制,使得可以显示灰度级。

在图13B所示的发光显示装置中,在其中在一个像素中配置开关TFT和电流控制TFT的两个TFT的情况下,第一扫描线驱动电路5402生成输入到第一扫描线的信号,第一扫描线用作开关TFT的栅极布线,而第二扫描线驱动电路5404生成输入到第二扫描线的信号,第二扫描线用作电流控制TFT的栅极布线;但是,一个扫描线驱动电路可以生成输入到第一扫描线的信号和输入到第二扫描线的信号二者。此外,例如,根据开关元件中包含的晶体管的数量,存在在各像素中设置用来控制开关元件的工作的多个第一扫描线的可能性。在此情况下,一个扫描线驱动电路可生成输入到多个第一扫描线的所有信号,或者多个扫描线驱动电路可生成输入到多个第一扫描线的信号。

同样,在发光显示装置中,可以将驱动电路中可包括n沟道型TFT的驱动电路的一部分形成在与像素部中薄膜晶体管相同的衬底上。备选地,也可以仅使用实施方式6或7所述的n沟道型TFT形成信号线驱动电路及扫描线驱动电路。

此外,上述驱动电路可以用于利用与开关元件电连接的元件来驱动电子墨水的电子纸,而不限于对液晶显示装置或者发光显示装置的应用。电子纸也称为电泳显示装置(电泳显示器),并其优点在于:它具有与普通纸相同的易读性水平,它与其他的显示装置相比具有更低功耗,并且它可形成得薄且轻。

电泳显示器可具有各种方式。电泳显示器含有分散在溶剂或溶质中的多个微囊,每个微囊含有带正电的第一粒子和带负电的第二粒子。通过对微囊施加电场,微囊中的粒子互相沿相反方向移动,并且仅显示集合在一侧的粒子的颜色。注意,第一粒子和第二粒子各自包含色素,且在没有电场时不移动。此外,第一粒子和第二粒子具有不同颜色(可为无色)。

因此,电泳显示器是利用所谓的介电电泳效应的显示器,通过介电电泳效应,具有高介电常数的物质移动到高电场区。电泳显示装置不需要液晶显示装置中所需的偏振片或对置衬底,并且电泳显示装置的厚度和重量厚度可以减少到液晶显示装置一半。

将在溶剂中分散有上述微囊的溶液称作电子墨水,该电子墨水可以印刷到玻璃、塑料、布、纸等的表面上。另外,通过使用彩色滤光片或具有色素的粒子,还可以获得彩色显示。

此外,如果在有源矩阵衬底上适当地设置多个上述微囊以使其夹在两个电极之间,则完成有源矩阵型显示装置,并且通过对微囊施加电场可以执行显示。例如,可以使用实施方式6或7所述的薄膜晶体管而获得的有源矩阵衬底。

注意,微囊中的第一粒子及第二粒子可以各自由选自导电材料、绝缘材料、半导体材料、磁性材料、液晶材料、铁电性材料、电致发光材料、电致变色材料与磁泳材料中的单个材料制成,或者由这些材料中任意材料的复合材料制成。

通过上述过程,可以制造作为半导体装置的高可靠性显示装置。

本实施方式可以与其他的实施方式所记载的结构适当地组合而实施。

实施方式9

在本发明的一个实施方式的薄膜晶体管被制造并用于像素部以及进一步用于驱动电路时,可制造具有显示功能的半导体装置(也称为显示装置)。此外,在将使用本发明的一个实施方式的薄膜晶体管的驱动电路的部分或全部形成在与像素部相同的衬底上时,可获得板上系统(system-on-panel)。

显示装置包括显示元件。作为显示元件,可以使用液晶元件(也称为液晶显示元件)或发光元件(也称为发光显示元件)。发光元件在其类别中包括其亮度受电流或电压控制的元件,具体而言,包括无机电致发光(EL)元件、有机EL元件等。此外,也可以使用通过电作用而改变其对比度的显示介质,例如电子墨水。

此外,显示装置包括其中密封显示元件的面板和其中在面板上安装包括控制器的IC等的模块。本发明的一个实施方式还涉及相当于在显示装置的制造过程中在显示元件完成之前的一个方式的元件衬底,并且该元件衬底设置有用于将电流供给到在多个像素的每个中的显示元件的单元。具体而言,元件衬底可以处于只形成显示元件的像素电极之后的状态、形成成为像素电极的导电膜之后且蚀刻导电膜以形成像素电极之前的状态或其他状态中的任何状态。

注意,本说明书中的显示装置是指图像显示器件、显示器件或光源(包括照明装置)。另外,显示装置在其类别中还包括以下模块:附连有诸如柔性印刷电路(FPC)、载带自动键合(TAB)带或载带封装TCP(TCP)的连接器的模块;具有其端部设置印刷线路板的TAB带或TCP的模块;以及通过玻璃上芯片(COG)将集成电路(IC)直接安装在显示元件上的模块。

在本实施方式中,参照图21A至21C说明作为本发明的半导体装置的一个实施方式的液晶显示面板的外观及截面。图21A和21B是一种面板的俯视图,其中利用密封材料4005将薄膜晶体管4010、4011及液晶元件4013密封在第一衬底4001与第二衬底4006之间。图21C是沿着图21A和21B的线M-N的截面图。

密封材料4005设置成围绕设置在第一衬底4001上的像素部4002和扫描线驱动电路4004。在像素部4002和扫描线驱动电路4004上设置第二衬底4006。因此,像素部4002和扫描线驱动电路4004通过第一衬底4001、密封材料4005和第二衬底4006与液晶层4008密封在一起。在第一衬底4001上的与由密封材料4005围绕的区域不同的区域中安装信号线驱动电路4003,该信号线驱动电路4003使用单晶半导体膜或多晶半导体膜形成在另外准备的衬底上。

注意对于另外形成的驱动电路的连接方法没有特别的限制,而可以采用COG、引线键合或TAB等。图21A图示通过COG安装信号线驱动电路4003的例子,而图21B图示通过TAB安装信号线驱动电路4003的例子。

设置在第一衬底4001上的像素部4002和扫描线驱动电路4004各包括多个薄膜晶体管。图21C图示像素部4002所包括的薄膜晶体管4010和扫描线驱动电路4004所包括的薄膜晶体管4011。薄膜晶体管4010、4011上设置有绝缘层4020、4021。

作为薄膜晶体管4010、4011,可以使用包含作为沟道形成区的氧过剩氧化物半导体层以及作为源区和漏区的氧缺欠氧化物半导体层的可靠性高的实施方式6所示的薄膜晶体管。备选地,可以使用实施方式7所示的薄膜晶体管作为薄膜晶体管4010、4011。在本实施方式中,薄膜晶体管4010、4011是n沟道型薄膜晶体管。

液晶元件4013所具有的像素电极层4030与薄膜晶体管4010电连接。液晶元件4013的对置电极层4031形成在第二衬底4006上。像素电极层4030、对置电极层4031和液晶层4008重叠的部分相当于液晶元件4013。注意,像素电极层4030、对置电极层4031分别设置有各用作取向膜的绝缘层4032和绝缘层4033。隔着绝缘层4032、4033将液晶层4008夹在像素电极层4030和对置电极层4031。

注意,第一衬底4001、第二衬底4006可以使用玻璃、金属(典型的是不锈钢)、陶瓷、或塑料制成。作为塑料,可以使用纤维增强塑料(FRP)板、聚氟乙烯(PVF)膜、聚酯膜或丙烯酸树脂膜。备选地,可以使用具有将铝箔夹在PVF膜或聚酯膜之间的结构的薄片。

附图标记4035表示通过对绝缘膜选择性地进行蚀刻而获得的柱状间隔物,并且它是为控制像素电极层4030和对置电极层4031之间的距离(单元间隙)而设置的。备选地,可以使用球状间隔物。对置电极层4031与与薄膜晶体管4010设置在同一衬底上的共同电位线电连接。使用实施方式1至实施方式3中所示的任一共同连接部,通过配置在一对衬底间的导电粒子,对置电极层4031与共同电位线电连接。注意,导电粒子包含在密封材料4005中。

备选地,可以使用不需要取向膜的显示为蓝相的液晶。蓝相是液晶相的一种,是指当使胆甾相液晶的温度上升时即将从胆甾相转变到均质相之前出现的相。由于蓝相只出现在较窄的温度范围内,所以为了改善温度范围而将含有5重量%或以上的手性试剂的液晶组成物用于液晶层4008。包含显示为蓝相的液晶和手性试剂的液晶组成物的响应时间短,即为10μs至100μs,并且由于其具有光学各向同性而不需要取向处理且视角依赖性小。

虽然本实施方式示出透射型液晶显示装置的例子,但是本发明的实施方式可以用于反射型液晶显示装置,或可以用于半透射型液晶显示装置。

在本实施方式中,示出其中在衬底的外表面(在观察者侧)上设置偏振片并在衬底的内表面上依次设置着色层和用于显示元件的电极层的液晶显示装置例子;但是,可以在衬底的内表面上设置偏振片。偏振片和着色层的叠层结构不局限于本实施方式所示的结构,并且根据偏振片和着色层的材料或制造工序条件适当地设定。另外,还可以设置用作黑矩阵的遮光膜。

在本实施方式中,使用用作保护膜或平坦化绝缘膜的绝缘层(绝缘层4020与绝缘层4021)覆盖通过实施方式6得到的薄膜晶体管,以降低薄膜晶体管的表面粗糙度并提高薄膜晶体管的可靠性。注意,保护膜设置成防止悬浮在大气中的例如有机物质、金属物质或者水蒸气的杂质的侵入,并且优选为致密膜。通过溅射法将保护膜形成为氧化硅膜、氮化硅膜、氧氮化硅膜、氮氧化硅膜、氧化铝膜、氮化铝膜、氧氮化铝膜/和或氮氧化铝膜的单层膜或多层膜。虽然本实施方式示出通过溅射法形成保护膜的例子,但是本发明并不局限于该方法,而可以使用各种方法。

在本实施方式中,形成具有多层结构的绝缘层作为保护膜。作为绝缘层4020的第一层,通过溅射法形成氧化硅膜。将氧化硅膜用作保护膜具有防止用作源电极层和漏电极层的铝膜的小丘的效果。

还形成绝缘层作为保护膜的第二层。在本实施方式中,作为绝缘层4020的第二层,通过溅射法形成氮化硅膜。将氮化硅膜用作保护膜可以抑制例如钠离子的可动离子侵入到半导体区中,从而抑制TFT的电特性变化。

在形成保护膜之后,可以将IGZO半导体层退火(在300℃至400℃)。

形成绝缘层4021作为平坦化绝缘膜。对于绝缘层4021,可以使用具有耐热性的有机材料,例如聚酰亚胺、丙烯酸、聚酰亚胺、苯并环丁烯、聚酰胺或环氧树脂。除了上述有机材料之外,还可以使用低介电常数材料(低k材料)、硅氧烷基树脂、PSG(磷硅玻璃)、BPSG(硼磷硅玻璃)或者诸如此类。硅氧烷基树脂可以包括氟、烷基和芳基中的至少一种作为取代基,还包括氢。注意,可以通过层叠多个由这些材料形成的绝缘膜来形成绝缘层4021。

注意,硅氧烷基树脂是由作为起始材料的硅氧烷材料形成的并且包含Si-O-Si键的树脂。硅氧烷基树脂可以包括氟、烷基和芳香烃中的至少一种作为取代基,还包括氢。

对形成绝缘层4021的方法没有特别限制,绝缘层4021可以根据材料通过溅射法、SOG、旋涂、浸渍、喷涂、液滴喷射法(例如喷墨法、丝网印刷、或胶版印刷)、刮刀、辊涂机、帘涂机、刮刀涂布机或者诸如此类来形成。在使用材料液形成绝缘层4021的情况下,可以在焙烧工序的同时将IGZO半导体层的退火(在300℃至400℃)。绝缘层4021的焙烧工序还用作IGZO半导体层的退火工序,从而可以高效地制造半导体装置。

像素电极层4030和对置电极层4031可以由诸如包含氧化钨的氧化铟、包含氧化钨的氧化铟锌、包含氧化钛的氧化铟、包含氧化钛的氧化铟锡、氧化铟锡(下面表示为ITO)、氧化铟锌或者添加有氧化硅的氧化铟锡的透光导电材料制成。

可以将包含导电高分子(也称为导电聚合物)的导电组成物用于像素电极层4030和对置电极层4031。由导电组成物制成的像素电极优选具有10000Ω/□或更小的薄层电阻以及在波长550nm的70%或更高的透光率。另外,导电组成物所包含的导电高分子的电阻率优选为0.1Ω·cm或更小。

作为导电高分子,可以使用所谓的π电子共轭类导电高分子。例如,可以使用聚苯胺或其衍生物、聚吡咯或其衍生物、聚噻吩或其衍生物或者上述材料中两种或更多种的共聚物。

另外,将各种信号及电位从FPC4018供给到另外形成的信号线驱动电路4003以及扫描线驱动电路4004或像素部4002。

在本实施方式中,连接端子电极4015使用与液晶元件4013所包含的像素电极层4030相同的导电膜形成,并且端子电极4016使用与薄膜晶体管4010、4011的源电极层和漏电极层相同的导电膜形成。

连接端子电极4015通过各向异性导电膜4019电连接到FPC4018所包含的端子。

注意,图21A至21C示出其中另外形成信号线驱动电路4003并将其安装在第一衬底4001的例子;但是本实施方式不局限于该结构。可以另外形成并安装扫描线驱动电路,或者可以另外仅形成并安装信号线驱动电路的一部分或扫描线驱动电路的一部分。

图22示出通过使用通过本发明制造的TFT衬底2600来制成为半导体装置的液晶显示模块的例子。

图22是液晶显示模块的例子,其中利用密封材料2602贴合TFT衬底2600和对置衬底2601,并在这些衬底之间设置包括TFT或诸如此类的像素部2603、包括液晶层的显示元件2604以及着色层2605以形成显示区。执行彩色显示需要着色层2605。在RGB系统的情况下,对于相应像素设置对应于红色、绿色与蓝色的相应着色层。在TFT衬底2600和对置衬底2601外配置偏振片2606与2607以及漫射片2613。光源包括冷阴极管2610和反射板2611。电路板2612通过柔性布线板2609与TFT衬底2600的布线电路部2608连接,且包含例如控制电路或电源电路的外部电路。偏振片和液晶层可以层叠有置于其间的延迟板。

对于液晶显示模块,可以采用TN(扭曲向列;Twisted Nematic)模式、IPS(平面内转换;In-Plane-Switching)模式、FFS(边缘场转换;Fringe Field Switching)模式、MVA(多畴垂直取向;Multi-domainVertical Alignment)模式、PVA(垂直取向构型;Patterned VerticalAlignment)模式、ASM(轴对称排列微单元;Axially Symmetric alignedMicro-cell)模式、0CB(光学补偿双折射;Optical CompensatedBirefringence)模式、FLC(铁电性液晶;Ferroelectric Liquid Crystal)模式、AFLC(反铁电性液晶;Anti Ferroelectric Liquid Crystal)模式或者诸如此类。

通过上述过程,可以制造作为半导体装置的高可靠性液晶显示面板。

本实施方式可以与其他实施方式所描述的结构适当地组合而实施。

实施方式10

在本实施方式中,将电子纸的例子描述为本发明的一个实施方式的半导体装置。

图12将有源矩阵型电子纸示出为应用本发明的半导体装置的例子。可以按与实施方式6中所示薄膜晶体管类似的方式制造用于半导体装置的薄膜晶体管581,并且该薄膜晶体管581是包括作为沟道形成区的氧过剩氧化物半导体层以及作为源区和漏区的氧缺欠氧化物半导体层的高可靠性薄膜晶体管。实施方式7所示的薄膜晶体管也可以用作本实施方式的薄膜晶体管581。

图12的电子纸是采用扭转球显示系统的显示装置的例子。扭转球显示系统是指如下的方法:其中,将各自以黑色与白色着色的球形粒子配置在作为用于显示元件的电极层的第一电极层与第二电极层之间,并且在第一电极层与第二电极层之间产生电位差以控制球形粒子的方向,使得执行显示。

介于衬底580与衬底596之间的薄膜晶体管581是底栅薄膜晶体管,并且源电极层或漏电极层通过形成在绝缘层585中的开口与第一电极层587接触,从而将薄膜晶体管581电连接到第一电极层587。在第一电极层587和第二电极层588之间设置球形粒子589,球形粒子589各自具有黑色区590a、白色区590b以及在这些区周围的填充有液体的空洞594。球形粒子589周围的空间用例如树脂的填充材料595填充(参见图12)。在本实施方式中,第一电极层587相当于像素电极,而第二电极层588相当于共同电极。第二电极层588电连接到与薄膜晶体管581设置在同一衬底上的共同电位线。通过使用实施方式1至3中任一个所示的共同连接部,第二电极层588通过配置在一对衬底间的导电粒子与共同电位线电连接。

还可以使用电泳元件来代替扭转球。使用直径为10μm至200μm左右的微囊,在微囊中封入有透明液体、带正电的白色微粒以及带负电的黑色微粒。在设置在第一电极层和第二电极层之间的微囊中,在第一电极层和第二电极层之间施加电场时,白色微粒和黑色微粒相互移动到相反侧,使得可以显示白色或黑色。使用这种原理的显示元件是电泳显示元件,并且一般被称为电子纸。电泳显示元件具有比液晶显示元件高的反射率,因而不需要辅助灯,功耗低,并且在昏暗的地方能够辨别显示部。另外,甚至在不给显示部供应电源时,也能够保持显示过一次的图像。因此,即使具有显示功能的半导体装置(其可简单地称为显示装置或设置有显示装置的半导体装置)远离电波源,也能够储存显示过的图像。

通过上述工序,可以制造作为半导体装置的高可靠性电子纸。

本实施方式可以与实施方式1至5中任一个所记载的共同连接部的结构适当地组合而实施。

实施方式11

在本实施方式中,将发光显示装置的例子描述为本发明的一个实施方式的半导体装置。作为显示装置所包含的显示元件,这里描述利用电致发光的发光元件。利用电致发光的发光元件根据发光材料是有机化合物还是无机化合物进行分类。一般来说,前者被称为有机EL元件,而后者被称为无机EL元件。

在有机EL元件中,通过对发光元件施加电压,电子和空穴从一对置电极分别注入到包含发光有机化合物的层,并且电流流过。然后,这些载流子(电子和空穴)重新结合,使得发光有机化合物被激发。发光有机化合物从激发态返回到基态,从而发光。由于这种机理,该发光元件被称为电流激发型发光元件。

无机EL元件根据其元件结构分类为分散型无机EL元件和薄膜无机EL元件。分散型无机EL元件具有其中在粘合剂中分散有发光材料粒子的发光层,且其发光机理是利用供体能级和受体能级的供体-受体重新结合型发光。薄膜型无机EL元件具有其中发光层夹在电介质层之间、它们进而夹在电极之间的结构,且其发光机理是利用金属离子的内壳电子跃迁的定域型发光。注意,在此使用有机EL元件作为发光元件进行说明。,

图19示出作为本发明的半导体装置例子的可以通过数字时间灰度级方法驱动的像素结构的例子。

对可以通过数字时间灰度级方法驱动的像素的结构以及工作进行说明。这里示出其中一个像素包含两个n沟道型的晶体管(其在沟道形成区中使用氧化物半导体层(IGZO半导体层))的例子。

像素6400包括开关晶体管6401、驱动晶体管6402、发光元件6404以及电容元件6403。开关晶体管6401的栅极与扫描线6406连接,开关晶体管6401的第一电极(源电极以及漏电极中之一)与信号线6405连接,并且开关晶体管6401的第二电极(源电极以及漏电极中的另一个)与驱动晶体管6402的栅极连接。驱动晶体管6402的栅极通过电容器6403与电源线6407连接,驱动晶体管6402的第一电极与电源线6407连接,并且驱动晶体管6402的第二电极与发光元件6404的第一电极(像素电极)连接。发光元件6404的第二电极相当于共同电极6408。共同电极6408与设置在同一衬底上的共同电位线电连接,并且可以将连接部分用作共同连接部而获得图1A、图2A或图3A所示的结构。

注意,将发光元件6404的第二电极(共同电极6408)设定为低电源电位。低电源电位低于供应给电源线6407的高电源电位。例如,可以将低电源电位设定为GND或0V。将高电源电位与低电源电位之差施加到发光元件6404,以使电流在发光元件6404中流过,由此发光元件6404发光。因此,设定每个电位,使得高电源电位与低电源电位之差等于或高于正向阈值电压。

在驱动晶体管6402的栅极电容用作电容器6403的替代时,可省略电容器6403。驱动晶体管6402的栅极电容可以形成在沟道区与栅电极之间。

在采用电压输入电压驱动方法的情况下,对驱动晶体管6402的栅极输入使驱动晶体管6402完全导通或截止的视频信号。即,驱动晶体管6402工作在线性区域,并且因此将比电源线6407的电压高的电压施加到驱动晶体管6402的栅极。注意,对信号线6405施加高于或等于(电源线电压+驱动晶体管6402的Vth)的电压。

在使用模拟灰度级方法代替数字时间灰度级方法的情况下,通过以不同方式输入信号可以使用与图19相同的像素结构。

在使用模拟灰度级方法的情况下,对驱动晶体管6402的栅极施加高于或等于(发光元件6404的正向电压+驱动晶体管6402的Vth)的电压。发光元件6404的正向电压是指获得所希望亮度的电压,并且至少包含正向阈值电压。通过输入允许驱动晶体管6402工作在饱和区的视频信号,电流可以在发光元件6404中流过。为了允许驱动晶体管6402工作在饱和区,电源线6407的电位高于驱动晶体管6402的栅极电位。因为视频信号为模拟信号,所以根据视频信号的电流在发光元件6404中流过并且可以执行模拟灰度级方法。

注意,像素结构不局限于图19中所示。例如,图26中的像素还可以包括开关、电阻器、电容器、晶体管、逻辑电路或诸如此类。

接着,参照图20A至20C说明发光元件的结构。通过把n沟道驱动TFT作为例子来说明像素的截面结构。用于图20A至20C所示的半导体装置的驱动TFT7001、7011和7021可以按与实施方式6中所述的薄膜晶体管类似的方式进行制造,并且是各自包括作为沟道形成区的氧过剩氧化物半导体层以及作为源区和漏区的氧缺欠氧化物半导体层的高可靠性薄膜晶体管。备选地,可以将实施方式7中所述的薄膜晶体管用作驱动TFT7001、7011、7021。

为了取出从发光元件发出的光,要求阳极与阴极中至少之一透射光。在衬底上形成薄膜晶体管及发光元件。发光元件可具有其中通过与衬底相反的表面取出光的顶部发射结构、其中通过衬底侧上的表面取出光的底部发射结构,或通过与衬底相反的表面和衬底侧上的表面取出光的双发射结构。本发明实施方式的像素结构可以应用于具有任何这些发射结构的发光元件。

参照图20A说明具有顶部发射结构的发光元件。

图20A是在驱动TFT7001为n型且光从发光元件7002发射到阳极7005侧的情况下像素的截面图。在图20A中,发光元件7002的阴极7003与驱动TFT7001电连接,并且在阴极7003上按顺序层叠发光层7004和阳极7005。阴极7003可以由各种导电材料制成,只要它们具有低功函数且反射光即可。例如,优选采用Ca、A1、CaF、MgAg、AlLi或者诸如此类。发光层7004可以使用单层或层叠的多层构成。在发光层7004使用多层构成时,通过在阴极7003上按顺序层叠电子注入层、电子传输层、发光层、空穴传输层与空穴注入层来构成发光层7004。不需要设置所有这些层。阳极7005由例如包含氧化钨的氧化铟、包含氧化钨的氧化铟锌、包含氧化钛的氧化铟、包含氧化钛的氧化铟锡、氧化铟锡(下面表示为ITO)、氧化铟锌、或添加有氧化硅的氧化铟锡的透光导电材料形成。

发光元件7002相当于阴极7003与阳极7005将发光层7004夹在中间的区域。在图20A所示像素的情况下,光从发光元件7002发射到阳极7005侧,如箭头所示。