CN100507695C - 液晶显示器件的制造方法 - Google Patents

液晶显示器件的制造方法 Download PDFInfo

- Publication number

- CN100507695C CN100507695C CNB2007101260097A CN200710126009A CN100507695C CN 100507695 C CN100507695 C CN 100507695C CN B2007101260097 A CNB2007101260097 A CN B2007101260097A CN 200710126009 A CN200710126009 A CN 200710126009A CN 100507695 C CN100507695 C CN 100507695C

- Authority

- CN

- China

- Prior art keywords

- layer

- conductive layer

- substrate

- mask

- photoresist film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000000034 method Methods 0.000 title claims abstract description 75

- 239000004973 liquid crystal related substance Substances 0.000 title claims abstract description 47

- 239000000758 substrate Substances 0.000 claims abstract description 63

- 238000004380 ashing Methods 0.000 claims abstract description 32

- 239000004065 semiconductor Substances 0.000 claims abstract description 28

- 238000002161 passivation Methods 0.000 claims abstract description 17

- 229920002120 photoresistant polymer Polymers 0.000 claims description 93

- 239000000203 mixture Substances 0.000 claims description 37

- 238000004519 manufacturing process Methods 0.000 claims description 20

- 238000009413 insulation Methods 0.000 claims description 16

- 239000011651 chromium Substances 0.000 claims description 12

- 238000005530 etching Methods 0.000 claims description 12

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 claims description 8

- 229910052804 chromium Inorganic materials 0.000 claims description 8

- 239000010949 copper Substances 0.000 claims description 8

- 229910021344 molybdenum silicide Inorganic materials 0.000 claims description 7

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 claims description 6

- YXTPWUNVHCYOSP-UHFFFAOYSA-N bis($l^{2}-silanylidene)molybdenum Chemical compound [Si]=[Mo]=[Si] YXTPWUNVHCYOSP-UHFFFAOYSA-N 0.000 claims description 6

- 229910052750 molybdenum Inorganic materials 0.000 claims description 5

- 239000011733 molybdenum Substances 0.000 claims description 5

- 229910000838 Al alloy Inorganic materials 0.000 claims description 4

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 claims description 4

- 239000004411 aluminium Substances 0.000 claims description 4

- 229910052782 aluminium Inorganic materials 0.000 claims description 4

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 claims description 4

- 229910052802 copper Inorganic materials 0.000 claims description 4

- MRNHPUHPBOKKQT-UHFFFAOYSA-N indium;tin;hydrate Chemical compound O.[In].[Sn] MRNHPUHPBOKKQT-UHFFFAOYSA-N 0.000 claims description 4

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 claims description 4

- 229910052721 tungsten Inorganic materials 0.000 claims description 4

- 239000010937 tungsten Substances 0.000 claims description 4

- 229910045601 alloy Inorganic materials 0.000 claims description 3

- 239000000956 alloy Substances 0.000 claims description 3

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 claims description 3

- 230000008569 process Effects 0.000 abstract description 23

- 238000000059 patterning Methods 0.000 abstract description 4

- 238000010030 laminating Methods 0.000 abstract 1

- 239000010408 film Substances 0.000 description 58

- 239000010409 thin film Substances 0.000 description 23

- 239000004020 conductor Substances 0.000 description 22

- 230000015572 biosynthetic process Effects 0.000 description 20

- 230000005540 biological transmission Effects 0.000 description 16

- 229910021417 amorphous silicon Inorganic materials 0.000 description 13

- 230000003760 hair shine Effects 0.000 description 8

- 239000012528 membrane Substances 0.000 description 8

- 206010019133 Hangover Diseases 0.000 description 7

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 6

- 230000000717 retained effect Effects 0.000 description 6

- 229910052710 silicon Inorganic materials 0.000 description 6

- 239000010703 silicon Substances 0.000 description 6

- 230000002950 deficient Effects 0.000 description 5

- 230000014509 gene expression Effects 0.000 description 5

- 239000011159 matrix material Substances 0.000 description 5

- 239000000463 material Substances 0.000 description 4

- 230000008901 benefit Effects 0.000 description 3

- 239000011248 coating agent Substances 0.000 description 3

- 238000000576 coating method Methods 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- 238000002834 transmittance Methods 0.000 description 3

- 239000000969 carrier Substances 0.000 description 2

- 238000011049 filling Methods 0.000 description 2

- 238000001914 filtration Methods 0.000 description 2

- 239000007769 metal material Substances 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 239000012780 transparent material Substances 0.000 description 2

- 229910000967 As alloy Inorganic materials 0.000 description 1

- 101150064138 MAP1 gene Proteins 0.000 description 1

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- 229910004205 SiNX Inorganic materials 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- 230000003213 activating effect Effects 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 239000007772 electrode material Substances 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 210000004276 hyalin Anatomy 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 238000001259 photo etching Methods 0.000 description 1

- 238000011112 process operation Methods 0.000 description 1

- 238000007790 scraping Methods 0.000 description 1

- 238000012216 screening Methods 0.000 description 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/1288—Multistep manufacturing methods employing particular masking sequences or specially adapted masks, e.g. half-tone mask

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1345—Conductors connecting electrodes to cell terminals

- G02F1/13458—Terminal pads

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/1368—Active matrix addressed cells in which the switching element is a three-electrode device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136231—Active matrix addressed cells for reducing the number of lithographic steps

- G02F1/136236—Active matrix addressed cells for reducing the number of lithographic steps using a grey or half tone lithographic process

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Nonlinear Science (AREA)

- General Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Optics & Photonics (AREA)

- Crystallography & Structural Chemistry (AREA)

- Chemical & Material Sciences (AREA)

- Mathematical Physics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Liquid Crystal (AREA)

- Thin Film Transistor (AREA)

- Electrodes Of Semiconductors (AREA)

Abstract

本发明公开了一种液晶显示器件的制造方法,包括:提供具有像素部的第一基板;在其中形成有栅极的第一基板上顺序层叠栅绝缘层、半导体层和第一导电层;用半色调掩模在第一导电层上形成第一PR图案,该第一PR图案在将要形成晶体管的沟道区域上构图为相对较薄;用第一PR图案对第一导电层进行构图;通过在第一PR图案上进行第一灰化工序来形成与第一导电层外围对齐的第二PR图案;使用第二PR图案对半导体层进行构图;使用第二PR图案形成源极/漏极;在第一基板上形成钝化层和像素电极;将第一基板粘附到第二基板;在第一基板和第二基板之间形成液晶层。

Description

技术领域

本发明涉及一种制造液晶显示(LCD)器件的方法,尤其涉及一种在光刻工序中半色调掩模代替狭缝掩模获得均匀沟道的液晶显示器件的制造方法,并且根据由此获得的均匀性,通过当形成源极/漏极时进行预灰化工序可减小有源拖尾(active tail)和波动噪声现象。

背景技术

在显示器件中,尤其是在包括液晶显示器件的平板显示器中,显示器件由每个显示像素中的有源器件,如薄膜晶体管驱动。

这种驱动显示器件的方法一般称作“有源矩阵驱动方法”。

在有源矩阵驱动方法中,有源器件设置在排列成矩阵形状的每个像素中,从而驱动相应的像素。

鉴于该点,现在将参照图1解释相关技术的液晶显示器件。

图1是显示执行有源矩阵像素驱动方法的液晶显示器件像素的视图。

如图1所示,相关技术的液晶显示器件是薄膜晶体管液晶显示器件,其使用薄膜晶体管10作为有源像素驱动器件。

参照图1,薄膜晶体管液晶显示器件(其中垂直和水平设置有N×M个像素)中的每个像素都包括薄膜晶体管10,薄膜晶体管10形成在从外部驱动电路供给扫描信号的栅线13与供给图像信号的数据线19c彼此交叉的区域。

这里,薄膜晶体管10包括与栅线13连接的栅极13a、形成在栅极13a上且当给栅极13a供给扫描信号时激活的有源图案17a、和分别形成在有源图案17a上的源极19a和漏极19b。

像素的显示区域设置有与源极/漏极19a和19b连接并当有源图案17a被激活时通过源极/漏极19a和19b接收像素信号以操作液晶材料层(没有示出)的像素电极25。

现在将参照图2给出相关技术的液晶显示器件结构的详细描述,图2是图1中沿线II-II的横截面图,显示了相关技术的液晶显示器件的横截面。

参照图2,薄膜晶体管设置在由透明材料(如玻璃)形成并形成为阵列基板的第一基板11上。

这里,薄膜晶体管包括形成在第一基板11上的栅极13a、层叠在具有栅极13a的整个第一基板11上的栅绝缘层5、形成栅绝缘层5上的有源图案17a、形成在有源图案17a上的源极19a和漏极19b、和形成在整个第一基板11上的钝化层23。

此外,在钝化层23上形成像素电极25,像素电极25通过形成在钝化层23中的接触孔(没有示出)与薄膜晶体管的漏极19b连接。

同时,面对阵列基板11的滤色片基板包括由透明材料(如玻璃)形成的第二基板31、形成在第二基板31上并形成在图像非显示区域(如具有薄膜晶体管的区域或像素之间的区域)上以阻止光透过图像非显示区域的黑色矩阵33、和由红色、绿色和蓝色滤色片形成来实现真彩色的滤色片层35。

在该情形中,当滤色片基板和阵列基板彼此粘接时,在它们之间填充液晶层41,从而完成液晶显示器件。

同时,在滤色片层35上进一步设置有公共电极37,用于与像素电极25一起向液晶层41施加电场。

这种液晶显示器件一般通过比较复杂的工序制造,例如由使用掩模的光刻来制造。

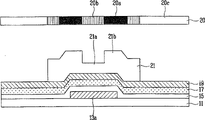

参照图3A到3G,现在将详细描述通过使用狭缝掩模的相关技术的4轮掩模工序制造液晶显示器件的方法。

图3A到3G是顺序显示通过使用狭缝掩模进行4轮掩模工序来制造液晶显示器件的方法步骤的横截面图。

首先,参照图3A,在第一基板11的整个表面上形成用于形成栅极的金属层,然后在上面涂敷光刻胶。通过光刻工序,形成栅线(没有示出)和与栅线连接的栅极13a。

参照图3B,在具有栅极13a的第一基板11的整个表面上顺序形成栅绝缘层15、半导体层17、欧姆接触层(一般使用n+非晶硅薄膜,没有示出)、和导电层19。

这里,导电层19是将要通过下面的工序被构图成源极和漏极的层。

在导电层19上涂敷光刻胶(没有示出),然后将光通过具有遮光部20a、半透射部20b、和透射部20c的狭缝掩模20照射到光刻胶薄膜(没有示出)上。然后,在曝光和显影工序之后在导电层19上形成光刻胶薄膜图案21。

这里,因为光刻胶薄膜图案21通过使用狭缝掩模20形成的,所以与形成在其他区域上的光刻胶薄膜图案21b相比,形成在沟道区域上方的光刻胶薄膜图案21a比较薄。

然后,参照图3C,使用光刻胶薄膜图案21作为蚀刻掩模,从而顺序蚀刻导电层19、欧姆接触层(没有示出)、和半导体层17,由此形成有源图案17a。

接下来,参照图3D,在光刻胶薄膜图案21上进行灰化工序。这里,因为在灰化工序过程中移除了沟道区域上的光刻胶薄膜图案部分21a(就是说,光刻胶薄膜图案相对薄的区域),所以暴露出导电层19。

灰化工序是下述一种工序,即为了移除而氧化作为有机物质的光刻胶薄膜。通过氧化移除了光刻胶薄膜图案21的一些部分21a,由此减小了整体体积。这里,也移除了沟道区域和有源图案边缘的光刻胶薄膜图案21。

参照图3E,利用灰化后的光刻胶薄膜图案21作为蚀刻掩模,从而去除沟道区域上的导电层和欧姆接触层,由此形成源极19a和漏极19b。

接下来,参照图3F,在去除了灰化后的光刻胶薄膜图案21之后,在具有源极和漏极19a和19b的基板上形成钝化层23。

参照图3G,通过光刻工序在钝化层23中形成暴露漏极19b的接触孔(没有示出)。

然后,形成像素电极25,像素电极25与漏极19b连接并由透明电极材料形成。

依照上述工序形成的相关技术的薄膜晶体管由4轮掩模工序制造,其中第一个掩模用于形成栅极,第二个掩模用于形成有源图案和源极/漏极,第三个掩模用于形成暴露漏极的接触孔,第四个掩模用于形成像素电极。

依照通过上述工序制造液晶显示器件的相关技术的方法,如图3E中所示,因为灰化后的光刻胶薄膜图案21还暴露了有源图案17a的边缘,所以形成在有源图案17a边缘上的欧姆接触层(没有示出)和导电层19被去除。因而,有源图案17a比有源/漏极更加突出,由此导致“有源拖尾缺陷”。

将参照图4A和4B详细描述有源拖尾缺陷,图4A和4B是当从数据线一侧观看时,显示使用狭缝掩模在相关技术的工序中形成源极/漏极制造工序的横截面图。

如图4A中所示,在基板11上形成有半导体层17、欧姆接触层18、图案化的形成源极/漏极的导电材料19、和图案化的光刻胶薄膜图案21。下面将对比图3C进行详细说明。

当从数据线一侧观看时,图4A显示了图3C中所示的形成源极/漏极的导电材料19被构图后的状态。就是说,其是通过使用光刻胶薄膜图案21进行湿刻而构图形成源极/漏极的导电材料19(如包含钼的金属材料)的状态。

在图4A中,所以没有示出栅极和栅绝缘层。此外,因为具有与图3C不同的截面,也没有示出具有相对薄的沟道区域的光刻胶薄膜。

参照图4A,构图后的形成源极/漏极的导电材料19比光刻胶薄膜图案21更加向内蚀刻了距离d1,即底切。

不希望的是,这导致了有源拖尾缺陷,现在将参照下面的工序进行描述。

在图4A中,将形成源极/漏极的导电材料19构图,然后通过使用光刻胶薄膜图案21作为蚀刻掩模来进行干刻工序,用于构图欧姆接触层18和半导体层17,由此形成有源图案。

这里,如图4A中所示,由于用作蚀刻掩模的光刻胶薄膜图案21的形状,被蚀刻的有源图案17a的外围和构图后的形成源极/漏极的导电材料19的外围没有彼此对齐。

就是说,参照图4B,有源图案17a的边缘没有被完全蚀刻,留下一部分残留,导致不希望的拖尾形状。

这称作“有源拖尾现象”,如图4B中所示,其具有几乎1.7μm的突出。有源拖尾现象导致像素电极区域减小,且作为区域减小的结果,导致孔径比减小大约2%。

此外,作为具有非常薄厚度的非晶硅薄膜,欧姆接触层18被完全蚀刻,从而与在上述干刻工序中的构图后的形成源极/漏极的导电材料19的外围对齐。

图4B是当从数据线一侧观看时,显示形成钝化层23和像素电极25的状态的横截面图。

因为导电层通常存在于形成源极/漏极的导电材料下方,所以从数据线一侧投射的来自背光的光穿过栅绝缘层,直接入射到半导体层上。

穿过栅绝缘层并入射到半导体层的背光激活半导体层,导致缺陷,如波动噪声。

在形成源极/漏极时,当比源极/漏极更加凸出的有源图案衍射背光或者沟道信号被背光打乱时,在所显示的图像中产生波动噪声。

发明内容

因此,为了克服上述问题,本发明的一个目的是提供一种制造液晶显示器件的方法,其能在不需要额外掩模工序的情况下减小有源拖尾和波动噪声缺陷。

为了实现这些目的和其它的优点并根据本发明的目的,如这里具体化和广泛描述的,提供了一种液晶显示器件的制造方法,包括:提供具有像素部的第一基板;在其中构图有栅极的第一基板上顺序层叠栅绝缘层、半导体层、导电层和光刻胶薄膜;通过使用半色调掩模对光刻胶薄膜进行构图来形成光刻胶薄膜图案;使用光刻胶薄膜图案作为掩模对导电层和半导体层进行构图;通过第一灰化工序部分地去除光刻胶薄膜图案;通过使用剩余的光刻胶薄膜图案作为掩模对导电层进行构图以形成源极/漏极;在第一基板上形成钝化层和像素电极;将第一基板粘附到第二基板;以及在第一基板和第二基板之间形成液晶层。

依照本发明的另一个实施方案,提供了一种液晶显示器件的制造方法,包括:提供具有像素部的第一基板;使用第一掩模在第一基板上形成栅极;在其中形成有栅极的第一基板上顺序层叠栅绝缘层、半导体层和第一导电层;使用半色调掩模在第一导电层上形成光刻胶(PR)图案,该光刻胶图案在晶体管的沟道区域构图为相对较薄;使用PR图案对第一导电层和半导体层进行构图;通过在PR图案上进行第一灰化工序部分地去除PR图案;通过使用剩余的PR图案对第一导体层进行构图以形成源极/漏极;在具有源极/漏极的第一基板上形成钝化层;通过使用第二掩模对第一基板上的钝化层进行构图以部分地暴露漏极;在第一基板上形成第二导电层;通过使用第三掩模对第一基板上的第二导电层进行构图以形成像素电极;将第一基板粘附到第二基板;和在第一基板和第二基板之间形成液晶层。

本发明的上述和其他的目的、特征、特点和优点通过下面结合附图的详细说明变得显而易见。

附图说明

本申请所包括的附图用于提供对本发明的进一步理解,并且包括在该申请中并且作为本申请的一部分,示出了本发明的实施方式并且连同说明书一起用于解释本发明的原理。

附图中:

图1是显示相关技术的液晶显示器件中的单位像素结构的平面图;

图2是显示图1中单位像素的横截面图;

图3A到3G是显示通过使用狭缝掩模进行4轮掩模工序制造液晶显示器件的方法的横截面图;

图4A和4B是当从数据线一侧看时,部分地显示通过使用狭缝掩模进行4轮掩模工序来制造液晶显示器件的工序的横截面图;

图5是显示当使用狭缝掩模时沟道区域的非均匀性的视图;

图6是显示当使用半色调掩模时沟道区域的均匀性的视图;

图7A至7C是当从数据线一侧看时,部分地显示通过使用半色调掩模进行预灰化工序来制造液晶显示器件的工序的横截面图;以及

图8A至8E是显示依照本发明示例性实施方式的制造液晶显示器件方法的工序次序的横截面图。

具体实施方式

现在将详细描述依照本发明的制造液晶显示器件的方法,在附图中示出了其实施例。

图5是显示在使用狭缝掩模的光刻工序过程中照射到薄膜晶体管沟道区域的光的强度的视图。在图5中,标号121表示透明基板,标号123表示形成在狭缝掩模中遮光区域上的遮光材料(例如铬)。

参照图5,狭缝掩模120包括光100%透射的透射区域、光透射超过0%小于100%的狭缝区域、和光透射被阻止的遮光区域。

狭缝区域具有狭缝结构,通过狭缝结构照射的光的强度小于通过其中光完全透射的透射区域照射的光的强度。因此,涂敷光刻胶薄膜113之后,如果使用部分地具有设置在光刻胶薄膜113上的狭缝区域和透射区域的狭缝掩模120来曝光,则留在狭缝区域下方的光刻胶薄膜113a的厚度和保留在透射区域下方的光刻胶薄膜113b的厚度形成为不同。

就是说,对于正型光刻胶薄膜的情形,通过狭缝区域被照射的光刻胶薄膜113a的厚度形成为比透射区域下方的厚。然而,对于负型光刻胶薄膜的情形,保留在透射区域下方的光刻胶薄膜的厚度形成为比狭缝区域下方的厚。

参照图5,当使用狭缝掩模120时,在曝光工序过程中照射到沟道区域上的光强度是不均匀的。因此,由此形成的沟道区域的最终表面是不均匀且不平坦的,由此减小了其均匀性。

由于这些问题,当使用狭缝掩模时,很难在有源图案被构图之前进行预灰化工序。

图6是显示在依照本发明实施方案的制造液晶显示器件过程中,在光刻工序工序中使用半色调掩模代替狭缝掩模,照射到薄膜晶体管沟道区域上的光的强度的视图。

与使用狭缝掩模类似,本发明中使用的半色调掩模220包括透射区域、半色调区域(即半透射区域)、和遮光区域。

半色调区域由根据厚度来控制光透射量的金属材料(例如硅化钼,MoSi)形成。通过半色调区域照射的光的强度小于通过其中光完全透射的透射区域的光的强度。因此,在涂敷光刻胶薄膜213之后,如果使用光刻胶薄膜213上方的半色调掩模220曝光,则保留在半色调区域下方的光刻胶薄膜213a的厚度和保留在透射区域下方的光刻胶薄膜213b的厚度形成为不同。

就是说,对于正型光刻胶薄膜的情形,通过半色调区域被照射的光刻胶薄膜的厚度形成为比透射区域下方的厚。然而,对于负型光刻胶薄膜的情形,保留在透射区域下方的光刻胶薄膜的厚度形成为比半色调区域下方的厚。

在图6中,标号221表示透明基板,标号223表示遮光的铬层,标号225表示形成在半色调区域上的硅化钼(MoSi)层。这里,如果调整硅化钼(MoSi)层225的厚度,则可控制照射到光刻胶薄膜213上的透射光的量。

参照图6,因为在曝光工序过程中照射到沟道区域上的光的强度是均匀的,所以沟道区域表面形成的比较平滑,由此提高了均匀性。

因此,当使用半色调掩模220时,可在有源图案被构图之前进行预灰化工序。

现在将参照图7A至7C详细描述依照本发明的制造液晶显示器件的方法。

图7A至7C是依照本发明一个实施方案当从数据线一侧看时,示出在有源图案被构图之前利用半色调掩模进行预灰化工序的制造工序的顺序横截面图。

图7A示出了通过湿刻工序将形成源极/漏极的导电材料307构图的状态。

参照图7A,提供有基板300、在基板300上形成且要通过下面的工序构图为有源图案的半导体层303、在半导体层303上形成的且用于与之后形成的源极/漏极欧姆接触n+硅薄膜305、在具有n+硅薄膜且已经被湿刻的半导体层上形成的形成源极/漏极的导电材料307,在形成源极/漏极的导电材料307上形成并且使用半色调掩模(没有示出)进行构图后的光刻胶薄膜309。

图7A没有示出与图4A的太多差别。就是说,如图7A中所示,形成源极/漏极的导电材料307比光刻胶薄膜309被更向内蚀刻了距离d2。

图7B示出了在通过构图半导体层303而形成有源图案之前进行预灰化工序的状态。

在预灰化工序之后保留的光刻胶薄膜309a具有减小的横向宽度。此外,光刻胶薄膜309a的外围和形成源极/漏极的导电材料307的外围彼此对齐,由此显著减小了在下面的工序中产生有源拖尾现象的可能性。

在图7B中所示的预灰化工序之后,进行相关技术的液晶显示器件的制造步骤。就是说,预灰化工序之后留下的光刻胶薄膜309a用作构图n+硅薄膜305和半导体层303以形成有源图案的蚀刻掩模,然后对薄膜晶体管的沟道区域进行灰化工序。

图3D显示了在沟道区域上进行灰化工序的结果。部分保留在沟道区域上的经过半色调曝光后的光刻胶薄膜被全部移除,由此暴露出形成源极/漏极的导电材料(图3D中的标号19)。

接下来,进行干刻工序,以去除沟道区域上的形成源极/漏极的导电材料(19,图7B中的标号307)。

然后,进行干刻工序,以去除沟道区域(图3D中没有示出,图7B中的标号305)上的n+硅薄膜。

优选地,在一个室中整体地进行上述预灰化工序和去除沟道区域上n+硅薄膜(图3D中没有示出,图7B中的标号305)的干刻工序。

之后,进行PR剥离工序,用于去除残留的光刻胶薄膜,从而完成源极/漏极(没有示出)的形成。

最后,顺序进行包括钝化层形成、像素电极形成、液晶层形成等的工序,从而制造液晶显示器件。

图7C是示出从数据线一侧看时形成像素电极的状态的横截面图。

在图7C中,提供有基板300、在基板300上形成的半导体层303、n+硅薄膜305、形成源极/漏极的导电材料307、钝化层311和像素电极313。

参照图7C,在依照本发明一个实施方式的液晶显示器件中有源拖尾的形成范围仅在0.3-0.5μm,与相关技术产生的有源拖尾现象相比,有了显著提高。

如上所述,依照本发明一个实施方式,通过使用半色调掩模代替在相关技术使用的狭缝掩模获得了薄膜晶体管的沟道区域中的均匀性。此外,基于沟道区域中获得的均匀性,可在有源图案被构图之前进行预灰化工序,由此阻止或减小有源拖尾现象的发生。

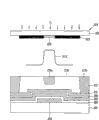

之后,将参照图8A到8E详细描述依照本发明另一个实施方案的制造液晶显示器件的方法,图8A到8E是显示依照本发明另一个示例性实方式制造液晶显示器件的方法的顺序横截面图。

在图8A中,进行了最初的清洗工序之后,在透明基板300(例如玻璃)上形成用于栅极的第一导电层(没有示出)。然后,使用第一掩模(没有示出)进行构图工序(例如湿刻),从而形成栅极301a、栅线301、和电容器下电极301b。

这里,第一掩模(没有示出)使用一般掩模,不必是昂贵的狭缝掩模或昂贵的半色调掩模。

此外,第一导电层(没有示出)形成为具有低电阻的不透明导电材料,如铝(Al)、铝合金、钨(W)、铜(Cu)、铬(Cr)、钼(Mu)以及它们的合金等的薄膜。

第一导电层(没有示出)可以形成为由两个或多个低电阻导电材料层叠的多层结构。

接下来,图8B和8C示出了形成源极/漏极307a和307b。在该工序中,使用半色调掩模并进行预灰化工序。

现在将参照图8B和8C详细描述进行的预灰化工序。

参照图8B,在其上已经构图出栅极301的基板300上形成栅绝缘层302。这里,栅绝缘层302由氮化硅(SiNx)层、氧化硅层或其他无机绝缘材料形成。

在栅绝缘层302上顺序层叠氢化非晶硅层303、n+非晶硅薄膜(没有示出)、和形成源极/漏极的第二导电层307。

这里,氢化非晶硅层303用作薄膜晶体管的有源区域,且其是将要构图产生有源图案的层,晶体管沟道通过下面的工序形成。

此外,氢化非晶硅层303用作形成有源图案的半导体层,其允许进行低温工序并使用便宜的绝缘基板。

n+非晶硅薄膜(没有示出)是欧姆接触层。源极和漏极通过由n+非晶硅薄膜形成的欧姆接触层与有源图案的特定区域进行欧姆接触。

这里,形成源极/漏极的第二导电层307由具有低电阻的不透明导电材料,如铝(Al)、铝合金、钨(W)、铜(Cu)、铬(Cr)、钼(Mo)以及它们的合金等形成。

如图8C中所示,在基板300上顺序层叠栅绝缘层302、氢化非晶硅层303、n+非晶硅薄膜(没有示出)、形成源极/漏极的第二导电层307和光刻胶薄膜(没有示出)。然后,通过使用半色调掩模320形成源极/漏极307a和307b。

首先,通过使用半色调掩模320将光刻胶薄膜(没有示出)构图,然后通过使用构图后的光刻胶薄膜309作为掩模来湿刻第二导电层307,从而形成源极/漏极307a和307b。

在该情形中,源极/漏极307a和307b形成为“U形”,从而随着沟道变宽提高开关速度。

如图8B中所示,沟道区域上的光刻胶薄膜具有小于其他区域上的厚度,但是其在沟道区域上具有均匀性。

在形成源极/漏极的第二导电层307上的构图工序之后,依照本发明一个实施方案进行预灰化工序。

如上所述,通过预灰化工序也可防止有源拖尾现象的发生。

接下来,如图8C中所示,将氢化非晶硅层303干刻并构图,之后进行灰化工序,从而去除留在沟道区域上的所有光刻胶薄膜309。

然后,通过干刻去除形成在沟道区域上的用于形成源极/漏极的第二导电层307。去除形成在沟道区域上的n+非晶硅薄膜(没有示出),由此暴露出在沟道区域上的氢化非晶硅层303。

此外,当为了去除剩余的光刻胶薄膜309而进行PR剥离工序时,形成了源极/漏极307a和307b。

参照图8D,在整个最终的结构上形成钝化层311,以保护器件免受湿气和刮擦的影响。

然后,使用第三个掩模(没有示出)进行光刻工序,从而形成贯穿钝化层311特定区域而暴露源极307的接触孔312。

如图8E中所示,在基板整个表面上沉积透明导电材料(没有示出)并通过使用第四个掩模进行光刻工序对其进行构图之后,形成像素电极313,像素电极313通过接触孔312与源极307b电连接。

这里,形成像素电极的材料是具有出色光透射率的导电材料的透明膜,如氧化铟锡(ITO)或氧化铟锌(IZO)。

之后,进行一般的工序,如在液晶显示器件中填充液晶材料的工序等,从而完成液晶显示器件的制造。

到目前为止所述,依照本发明的制造液晶显示器件的方法获得了沟道区域的均匀性,而不需要额外的掩模工序,基于通过当形成源极/漏极时额外进行预灰化步骤而获得的均匀性,减小了有源拖尾现象的发生,并与常规技术相比改善了波动噪声的发生。

上述的实施例和优点仅仅作为示例性的,并不能被解释为对本发明的限制。本发明可以容易地用于其它类型的装置中。这些描述仅仅作为示例性的,并不限制所附权利要求的范围。许多替代方式、修改和变形对本领域的技术人员是显而易见的。这里描述的示例性实施例的特征、结构、方法和其它特性可以以各种方式进行组合以获得额外的和/或可替换的示例性实施例。

由于在不脱离本发明特征的情况下,可以用多种方式实现本发明,所以很显然,上述实施例并不受上述任何细节的限制,除非另有说明,否则应在所属权利要求确定的范围内作广义解释,因此,所有落入权利要求范围内的改进和变更或这些范围的等同物都被视为包含在所附权利要求的范围内。

Claims (16)

1.一种液晶显示器件的制造方法,包括:

提供具有像素部的第一基板;

在其中构图有栅极的第一基板上顺序层叠栅绝缘层、半导体层、导电层和光刻胶薄膜;

通过使用半色调掩模将光刻胶薄膜构图来形成光刻胶薄膜图案;

使用所述光刻胶薄膜图案作为掩模湿刻所述导电层;

通过预灰化工序刻蚀所述光刻胶薄膜图案,以使构图后的光刻胶薄膜的外围与所述导电层的外围彼此对齐;

使用光刻胶薄膜图案作为掩模将半导体层构图;

通过一灰化工序去除留在所述导电层上方的、对应于沟道区域的光刻胶薄膜图案;

通过使用剩余的光刻胶薄膜图案作为掩模将导电层构图以形成源极/漏极;

去除剩余的光刻胶薄膜图案;

在第一基板上形成钝化层和像素电极;

将第一基板粘附到第二基板;以及

在第一基板和第二基板之间形成液晶层。

2.根据权利要求1所述的方法,其特征在于,所述在其中构图有栅极的第一基板上顺序层叠栅绝缘层、半导体层和导电层的步骤中,进一步包括:

在半导体层和导电层之间形成欧姆接触层。

3.根据权利要求2所述的方法,其特征在于,所述通过使用光刻胶薄膜图案作为掩模以形成源极/漏极的步骤进一步包括:

通过在光刻胶薄膜图案上进行所述灰化工序暴露出沟道区域上的导电层;

去除沟道区域上的导电层;

去除沟道区域上的欧姆接触层;以及

去除剩余的光刻胶薄膜图案。

4.根据权利要求1所述的方法,其特征在于,导电层由铝Al、铝合金、钨W、铜Cu、铬Cr、钼Mo或它们的合金中的至少一个形成。

5.根据权利要求1所述的方法,其特征在于,像素电极由氧化铟锡ITO或氧化铟锌IZO中的至少一个形成。

6.根据权利要求1所述的方法,其特征在于,半色调掩模包括透明基板、遮光层和半透射层。

7.根据权利要求6所述的方法,其特征在于,铬用于遮光层,硅化钼用于半透射层。

8.根据权利要求6所述的方法,其特征在于,遮光层设置在与导电层的源极/漏极形成区域相对应的位置处,半透射层对应于沟道区域设置在导电层的上方。

9.一种液晶显示器件的制造方法,包括:

提供具有像素部的第一基板;

使用第一掩模在第一基板上形成栅极;

在形成有栅极的第一基板上顺序层叠栅绝缘层、半导体层和第一导电层;

使用半色调掩模在第一导电层上形成光刻胶图案;

使用所述光刻胶图案作为掩模将所述第一导电层构图;

使用所述光刻胶图案作为掩模湿刻所述第一导电层;

通过预灰化工序刻蚀所述光刻胶图案,以使光刻胶图案的外围与所述第一导电层的外围彼此对齐;

使用光刻胶图案作为掩模将半导体层构图;

去除留在所述第一导电层上方的、对应于沟道区域的所述光刻胶图案;

通过使用剩余的光刻胶图案作为掩模对第一导电层进行构图以形成源极/漏极;

去除剩余的光刻胶图案;

在具有源极/漏极的第一基板上形成钝化层;

通过使用第二掩模对第一基板上的钝化层进行构图以部分地暴露漏极;

在第一基板上形成第二导电层;

通过使用第三掩模对第一基板上的第二导电层进行构图以形成像素电极;

将第一基板粘附到第二基板;以及

在第一基板和第二基板之间形成液晶层。

10.根据权利要求9所述的方法,其特征在于,所述在形成有栅极的第一基板上顺序层叠栅绝缘层、半导体层和第一导电层的步骤中,进一步包括:

在半导体层和所述第一导电层之间形成欧姆接触层。

11.根据权利要求10所述的方法,其特征在于,所述通过使用剩余的光刻胶图案作为掩模以形成源极/漏极的步骤进一步包括:

通过在光刻胶图案上进行第一灰化工序以暴露沟道区域处的所述第一导电层;

去除沟道区域处的第一导电层;

去除沟道区域处的欧姆接触层;以及

去除剩余的光刻胶图案。

12.根据权利要求9所述的方法,其特征在于,第一导电层由铝Al、铝合金、钨W、铜Cu、铬Cr、钼Mo或它们的合金中的至少一个形成。

13.根据权利要求9所述的方法,其特征在于,第二导电层由氧化铟锡ITO或氧化铟锌IZO中的至少一个形成。

14.根据权利要求9所述的方法,其特征在于,半色调掩模包括透明基板、遮光层和半透射层。

15.根据权利要求14所述的方法,其特征在于,铬用于遮光层,硅化钼用于半透射层。

16.根据权利要求14所述的方法,其特征在于,遮光层设置在所述第一导电层的与源极/漏极相对应的位置处,半透射层对应于沟道区域设置在所述第一导电层的上方。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020060061475A KR101266273B1 (ko) | 2006-06-30 | 2006-06-30 | 액정표시소자의 제조방법 |

| KR1020060061475 | 2006-06-30 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN101097381A CN101097381A (zh) | 2008-01-02 |

| CN100507695C true CN100507695C (zh) | 2009-07-01 |

Family

ID=38877064

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2007101260097A Active CN100507695C (zh) | 2006-06-30 | 2007-06-29 | 液晶显示器件的制造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7989147B2 (zh) |

| JP (1) | JP4949142B2 (zh) |

| KR (1) | KR101266273B1 (zh) |

| CN (1) | CN100507695C (zh) |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20090090915A1 (en) * | 2007-10-05 | 2009-04-09 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor, display device having thin film transistor, and method for manufacturing the same |

| JP5217558B2 (ja) * | 2008-03-27 | 2013-06-19 | 三菱電機株式会社 | 薄膜トランジスタ基板 |

| CN101661907B (zh) * | 2008-08-27 | 2011-12-28 | 北京京东方光电科技有限公司 | 液晶显示装置的阵列基板制造方法 |

| KR101593443B1 (ko) * | 2009-02-19 | 2016-02-12 | 엘지디스플레이 주식회사 | 어레이 기판의 제조방법 |

| TWI444758B (zh) * | 2009-06-19 | 2014-07-11 | Au Optronics Corp | 薄膜電晶體元件與用於定義薄膜電晶體元件之光罩及薄膜電晶體元件之製作方法 |

| CN102654698B (zh) * | 2011-06-15 | 2015-03-25 | 京东方科技集团股份有限公司 | 液晶显示器阵列基板及其制造方法、液晶显示器 |

| CN102830535A (zh) * | 2012-08-24 | 2012-12-19 | 京东方科技集团股份有限公司 | 一种显示装置、彩膜基板及其制备方法 |

| KR101881857B1 (ko) | 2012-08-27 | 2018-08-24 | 삼성전자주식회사 | 계단형 패턴 형성 방법 |

| CN102983103B (zh) * | 2012-12-10 | 2015-09-16 | 京东方科技集团股份有限公司 | 制作薄膜晶体管阵列基板的方法、阵列基板和显示装置 |

| CN103383946B (zh) * | 2013-07-12 | 2016-05-25 | 京东方科技集团股份有限公司 | 一种阵列基板、显示装置及阵列基板的制备方法 |

| CN105140131A (zh) | 2015-07-15 | 2015-12-09 | 京东方科技集团股份有限公司 | 氧化物薄膜晶体管的制备方法 |

| CN105070687A (zh) * | 2015-09-18 | 2015-11-18 | 京东方科技集团股份有限公司 | 薄膜晶体管、阵列基板及其制作方法、显示装置 |

| KR102095935B1 (ko) | 2016-08-31 | 2020-04-01 | 코닝 인코포레이티드 | 향상된 평면도를 갖는 글라스 라미네이트 및 그 형성방법 |

| CN106409844A (zh) * | 2016-11-29 | 2017-02-15 | 深圳市华星光电技术有限公司 | 底栅型多晶硅tft基板及其制作方法 |

| JP2020098867A (ja) * | 2018-12-18 | 2020-06-25 | 株式会社ブイ・テクノロジー | レーザアニール方法および薄膜トランジスタの製造方法 |

| CN112309970B (zh) * | 2020-10-30 | 2022-11-08 | 成都中电熊猫显示科技有限公司 | 阵列基板的制作方法以及阵列基板 |

| CN113241323B (zh) * | 2021-03-09 | 2024-05-03 | 滁州惠科光电科技有限公司 | 一种阵列基板的制造方法和显示面板 |

| CN113917751B (zh) * | 2021-10-25 | 2023-05-02 | 深圳市华星光电半导体显示技术有限公司 | 阵列基板及液晶显示面板 |

| CN114137771B (zh) * | 2021-12-08 | 2023-08-01 | Tcl华星光电技术有限公司 | 阵列基板及其制作方法 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4357689B2 (ja) | 2000-03-28 | 2009-11-04 | シャープ株式会社 | 液晶表示パネル及びその製造方法 |

| JP3696127B2 (ja) | 2001-05-21 | 2005-09-14 | シャープ株式会社 | 液晶用マトリクス基板の製造方法 |

| JP2002350899A (ja) * | 2001-05-24 | 2002-12-04 | Matsushita Electric Ind Co Ltd | 液晶ディスプレイ装置の製造方法 |

| KR100519372B1 (ko) * | 2002-12-31 | 2005-10-07 | 엘지.필립스 엘시디 주식회사 | 액정표시장치 및 그 제조방법 |

-

2006

- 2006-06-30 KR KR1020060061475A patent/KR101266273B1/ko active IP Right Grant

-

2007

- 2007-06-29 US US11/819,938 patent/US7989147B2/en active Active

- 2007-06-29 CN CNB2007101260097A patent/CN100507695C/zh active Active

- 2007-06-29 JP JP2007171878A patent/JP4949142B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2008015523A (ja) | 2008-01-24 |

| JP4949142B2 (ja) | 2012-06-06 |

| KR20080002582A (ko) | 2008-01-04 |

| US7989147B2 (en) | 2011-08-02 |

| CN101097381A (zh) | 2008-01-02 |

| KR101266273B1 (ko) | 2013-05-22 |

| US20080003526A1 (en) | 2008-01-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100507695C (zh) | 液晶显示器件的制造方法 | |

| CN100399193C (zh) | 掩模 | |

| US8735888B2 (en) | TFT-LCD array substrate and manufacturing method thereof | |

| US7115913B2 (en) | Array substrate used for a display device and a method of making the same | |

| CN100523971C (zh) | 用于液晶显示器件的阵列基板及其制造方法 | |

| CN102269900B (zh) | Tft阵列基板及其制造方法 | |

| CN101211863B (zh) | 液晶显示器件及其制造方法 | |

| KR101255307B1 (ko) | 액정표시장치 및 이의 제조방법 | |

| CN100562989C (zh) | 液晶显示器件及其制造方法 | |

| CN102087449A (zh) | 液晶显示设备的阵列基板和制造该阵列基板的方法 | |

| KR100983716B1 (ko) | 액정표시장치 및 그 제조방법 | |

| KR20170124624A (ko) | Tft-lcd 디스플레이 기판의 제조방법, 액정 패널 및 액정 디스플레이 장치 | |

| US7489379B2 (en) | Liquid crystal display device and fabricating method thereof | |

| CN101206325B (zh) | 具有光敏元件的液晶显示器件及其制造方法 | |

| KR20070001758A (ko) | 액정표시장치 및 그 제조방법 | |

| KR101331812B1 (ko) | 액정표시장치 및 그 제조방법 | |

| KR20090053612A (ko) | 액정표시소자 및 그 제조방법 | |

| CN102543866B (zh) | 穿透式液晶显示器的阵列基板制造方法 | |

| KR100769185B1 (ko) | 액정표시소자 및 그 제조방법 | |

| KR101856209B1 (ko) | 액정표시장치의 박막트랜지스터 및 그 제조방법 | |

| KR101036708B1 (ko) | 액정표시소자의 제조방법 | |

| JPH10170950A (ja) | アクティブマトリクス型液晶表示装置及びその製造方法 | |

| KR20080057035A (ko) | 액정표시장치 및 그 제조방법 | |

| KR20080048323A (ko) | 박막트랜지스터 액정표시장치 및 그 제조방법 | |

| KR20070072204A (ko) | 액정표시소자 및 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant |