KR101881857B1 - 계단형 패턴 형성 방법 - Google Patents

계단형 패턴 형성 방법 Download PDFInfo

- Publication number

- KR101881857B1 KR101881857B1 KR1020120093498A KR20120093498A KR101881857B1 KR 101881857 B1 KR101881857 B1 KR 101881857B1 KR 1020120093498 A KR1020120093498 A KR 1020120093498A KR 20120093498 A KR20120093498 A KR 20120093498A KR 101881857 B1 KR101881857 B1 KR 101881857B1

- Authority

- KR

- South Korea

- Prior art keywords

- pattern

- forming

- photoresist pattern

- interlayer insulating

- preliminary step

- Prior art date

Links

- 238000000034 method Methods 0.000 title claims abstract description 154

- 229920002120 photoresistant polymer Polymers 0.000 claims abstract description 160

- 239000010410 layer Substances 0.000 claims abstract description 140

- 230000001681 protective effect Effects 0.000 claims abstract description 95

- 239000011229 interlayer Substances 0.000 claims abstract description 89

- 238000005530 etching Methods 0.000 claims abstract description 55

- 239000000758 substrate Substances 0.000 claims abstract description 27

- 229910010272 inorganic material Inorganic materials 0.000 claims abstract description 6

- 239000011147 inorganic material Substances 0.000 claims abstract description 6

- 230000008569 process Effects 0.000 claims description 122

- 238000002161 passivation Methods 0.000 claims description 13

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 8

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 8

- 238000011065 in-situ storage Methods 0.000 claims description 6

- 239000007769 metal material Substances 0.000 claims description 5

- 238000010030 laminating Methods 0.000 claims description 4

- 239000011241 protective layer Substances 0.000 claims description 4

- 230000007261 regionalization Effects 0.000 claims description 2

- 229910003910 SiCl4 Inorganic materials 0.000 claims 1

- FDNAPBUWERUEDA-UHFFFAOYSA-N silicon tetrachloride Chemical compound Cl[Si](Cl)(Cl)Cl FDNAPBUWERUEDA-UHFFFAOYSA-N 0.000 claims 1

- 239000010408 film Substances 0.000 description 196

- 238000009966 trimming Methods 0.000 description 49

- 239000004065 semiconductor Substances 0.000 description 25

- 238000000206 photolithography Methods 0.000 description 20

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 10

- 229920005591 polysilicon Polymers 0.000 description 10

- 239000000463 material Substances 0.000 description 8

- 238000000151 deposition Methods 0.000 description 7

- 239000007789 gas Substances 0.000 description 6

- 238000004519 manufacturing process Methods 0.000 description 6

- 239000002184 metal Substances 0.000 description 6

- 229910052581 Si3N4 Inorganic materials 0.000 description 4

- 230000015572 biosynthetic process Effects 0.000 description 4

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 4

- 238000003860 storage Methods 0.000 description 4

- 230000004888 barrier function Effects 0.000 description 3

- 239000011368 organic material Substances 0.000 description 3

- 238000000059 patterning Methods 0.000 description 3

- 229910003902 SiCl 4 Inorganic materials 0.000 description 2

- 230000000903 blocking effect Effects 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 239000000945 filler Substances 0.000 description 2

- 230000014509 gene expression Effects 0.000 description 2

- 239000012535 impurity Substances 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- 230000000149 penetrating effect Effects 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/308—Chemical or electrical treatment, e.g. electrolytic etching using masks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31144—Etching the insulating layers by chemical or physical means using masks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76885—By forming conductive members before deposition of protective insulating material, e.g. pillars, studs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/20—EEPROM devices comprising charge-trapping gate insulators characterised by three-dimensional arrangements, e.g. with cells on different height levels

- H10B43/23—EEPROM devices comprising charge-trapping gate insulators characterised by three-dimensional arrangements, e.g. with cells on different height levels with source and drain on different levels, e.g. with sloping channels

- H10B43/27—EEPROM devices comprising charge-trapping gate insulators characterised by three-dimensional arrangements, e.g. with cells on different height levels with source and drain on different levels, e.g. with sloping channels the channels comprising vertical portions, e.g. U-shaped channels

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/50—EEPROM devices comprising charge-trapping gate insulators characterised by the boundary region between the core and peripheral circuit regions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/027—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34

- H01L21/0271—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising organic layers

- H01L21/0273—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising organic layers characterised by the treatment of photoresist layers

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Semiconductor Memories (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

계단형 패턴 형성 방법으로, 기판 상에 층간 절연막 및 희생막을 반복 적층하여 적층 구조물을 형성한다. 상기 적층 구조물 상에 형성된 제1 포토레지스트 패턴을 식각 마스크로 사용하여 최상부 1층의 층간 절연막 및 희생막을 식각하여 제n 예비 계단 패턴을 형성한다. 상기 제1 포토레지스트 패턴의 상부면을 덮는 무기물의 제1 보호막 패턴을 형성한다. 상기 제1 포토레지스트 패턴의 측벽 부위를 일부 제거하여 제2 포토레지스트 패턴을 형성한다. 상기 제2 포토레지스트 패턴을 식각 마스크로 사용하여 최상부 1층의 층간 절연막 및 희생막과, 상기 제n 예비 계단 패턴에서 노출된 상부면 아래의 1층의 층간 절연막 및 희생막을 각각 식각하여 제n+1 예비 계단 패턴을 형성한다. 또한, 상기 제n+1 예비 계단 패턴에 대해, 상기 제1 보호막 패턴을 형성하는 공정에서부터 상기 제n+1 예비 계단 패턴을 형성하는 공정까지를 반복하여 수행함으로써, 목표한 층수의 계단 패턴을 형성한다.

Description

본 발명은 계단형 패턴 형성 방법에 관한 것이다. 보다 상세하게는, 수직형 메모리 소자에 사용될 수 있는 계단형 패턴 형성 방법에 관한 것이다.

최근에는 반도체 소자의 고집적화를 위하여 기판 표면에 대해 수직한 방향으로 셀들을 적층시키는 기술이 개발되고 있다. 상기 수직형 반도체 소자의 경우, 셀들 뿐 아니라 이들과 연결되는 배선들도 수직 적층된 구조로 형성된다. 상기 수직 방향으로 적층되는 각 배선들에 독립적으로 전기적 신호를 인가하기 위하여, 상기 각 배선들의 가장자리에는 콘택 연결을 위한 패드로써 계단형 패턴이 포함되어야 한다. 상기 계단형 패턴을 형성하기 위하여, 수 회의 사진 및 식각 공정이 요구된다. 이와같이, 수 회의 사진 및 식각 공정을 수행하는데 따른 공정 비용이 증가된다.

본 발명의 목적은 사진 공정 횟수를 감소시키면서 계단형 패턴을 형성하는 방법을 제공하는데 있다.

상기한 목적을 달성하기 위한 본 발명의 일 실시예에 따른 계단형 패턴 형성 방법으로, 기판 상에 층간 절연막 및 희생막을 반복 적층하여 적층 구조물을 형성한다. 상기 적층 구조물 상에 제1 포토레지스트 패턴을 형성한다. 상기 제1 포토레지스트 패턴을 식각 마스크로 사용하여 최상부 1층의 층간 절연막 및 희생막을 식각하여 제n 예비 계단 패턴을 형성한다. 상기 제1 포토레지스트 패턴의 상부면과 측벽, 상기 제n 예비 계단 패턴의 측벽 및 상부면 상에, 무기물로 이루어지는 제1 보호막을 형성한다. 상기 제1 포토레지스트 패턴의 측벽의 제1 보호막을 제거하여 제1 보호막 패턴을 형성한다. 상기 제1 보호막 패턴에 의해 노출되는 상기 제1 포토레지스트 패턴의 측벽 부위를 일부 제거하여 제2 포토레지스트 패턴을 형성한다. 상기 제2 포토레지스트 패턴을 식각 마스크로 사용하여 최상부 1층의 층간 절연막 및 희생막과, 상기 제n 예비 계단 패턴에서 노출된 상부면 아래의 1층의 층간 절연막 및 희생막을 각각 식각하여 제n+1 예비 계단 패턴을 형성한다. 또한, 상기 제n+1 예비 계단 패턴에 대해, 상기 제1 보호막을 형성하는 공정에서부터 상기 제n+1 예비 계단 패턴을 형성하는 공정까지를 반복하여 수행함으로써, 목표한 층수의 계단 패턴을 형성한다.

본 발명의 일 실시예에서, 상기 제1 포토레지스트 패턴의 상부면 및 상기 예비 계단 패턴의 상부면 상에 형성되는 제1 보호막은 상기 제1 포토레지스트 패턴의 측벽 및 상기 예비 계단 패턴의 측벽 상에 형성되는 제1 보호막보다 두께가 두껍게 형성될 수 있다.

본 발명의 일 실시예에서, 상기 제1 보호막은 상기 적층 구조물의 최상부막과 동일한 물질을 포함할 수 있다.

본 발명의 일 실시예에서, 상기 제1 보호막은 실리콘 산화물을 포함할 수 있다. 상기 제1 보호막은 SiCl4 및 O2 가스를 반응 가스로 사용하여 형성할 수 있다.

본 발명의 일 실시예에서, 상기 제1 보호막은 상기 제n 예비 계단 패턴을 형성하기 위한 식각 공정이 수행되는 챔버 내에서 인시튜로 증착될 수 있다.

본 발명의 일 실시예에서, 상기 제n 예비 계단 패턴을 형성하기 위한 식각 공정에서부터 상기 제n+1 예비 계단 패턴을 형성하는 공정까지 동일한 식각 챔버 내에서 인시튜로 수행될 수 있다.

본 발명의 일 실시예에서, 상기 제n+1 예비 계단 패턴을 형성하는 단계에서, 상기 제2 포토레지스트 패턴 및 제n 예비 계단 패턴 상에 잔류하는 제1 보호막 패턴이 함께 제거될 수 있다.

본 발명의 일 실시예에서, 상기 제1 보호막을 형성하는 공정으로부터 상기 제n+1 예비 계단 패턴을 형성하는 공정까지는 4회 이상 반복 수행할 수 있다.

본 발명의 일 실시예에서, 상기 희생막은 실리콘 질화물 또는 폴리실리콘을 포함할 수 있다.

본 발명의 일 실시예에서, 상기 계단 패턴을 형성한 다음에, 상기 각 층의 희생막들을 제거한다. 또한, 상기 희생막 내부에 금속 물질막을 형성한다.

상기한 목적을 달성하기 위한 본 발명의 다른 실시예에 따른 계단형 패턴 형성 방법으로, 기판 상에 층간 절연막 및 희생막을 반복 적층하여 적층 구조물을 형성한다. 상기 적층 구조물 상에 1차 포토레지스트 패턴을 형성한다. 상기 1차 포토레지스트 패턴을 식각 마스크로 사용하여 최상부 1층의 층간 절연막 및 희생막을 식각하여 제n 예비 계단 패턴을 형성한다. 상기 1차 포토레지스트 패턴의 상부면 및 상기 제n 예비 계단 패턴의 상부면을 덮고, 무기물로 이루어지는 제1 보호막 패턴을 형성한다. 상기 제1 보호막 패턴에 의해 노출되는 1차 포토레지스트 패턴의 측벽 부위를 일부 제거하여 트리밍된 포토레지스트 패턴을 형성한다. 상기 트리밍된 포토레지스트 패턴을 식각 마스크로 사용하여 최상부 1층의 층간 절연막 및 희생막과, 상기 제n 예비 계단 패턴에서 노출된 상부면 아래의 1층의 층간 절연막 및 희생막을 각각 식각하여 제n+1 예비 계단 패턴을 형성한다. 상기 제n+1 예비 계단 패턴에 대해 상기 제1 보호막 패턴을 형성하는 공정으로부터 제n+1 예비 계단 패턴을 형성하는 공정까지 과정을 반복 수행하여 n차 계단 패턴을 형성한다. 적어도 상기 적층 구조물의 n차 계단 패턴의 계단 형성 부위를 덮는 2차 포토레지스트 패턴을 형성한다. 상기 제2 포토레지스트 패턴을 식각 마스크로 사용하여 최상부 1층의 층간 절연막 및 희생막을 식각하여 상기 n차 계단 패턴 아래에 제m 예비 계단 패턴을 형성한다. 상기 2차 포토레지스트 패턴의 상부면 및 상기 제m 예비 계단 패턴의 상부면 상에 제2 보호막 패턴을 형성한다. 상기 제2 보호막 패턴에 의해 노출되는 2차 포토레지스트 패턴의 측벽 부위를 일부 제거하여 트리밍된 포토레지스트 패턴을 형성한다. 상기 트리밍된 포토레지스트 패턴을 식각 마스크로 사용하여 노출된 최상부 1층의 층간 절연막 및 희생막과, 상기 제m 예비 계단 패턴에서 노출된 상부면 아래의 1층의 층간 절연막 및 희생막을 각각 식각하여 제m+1 예비 계단 패턴을 형성한다. 또한, 상기 제m+1 예비 계단 패턴에 대해 상기 제2 보호막 패턴을 형성하는 공정으로부터 상기 제m+1예비 계단 패턴을 형성하는 공정까지를 반복 수행하여 m차 계단 패턴을 형성한다.

본 발명의 일 실시예에서, 상기 제1 및 제2 보호막은 실리콘 산화물을 포함할 수 있다.

본 발명의 일 실시예에서, 상기 제n 예비 계단 패턴을 형성하는 단계로부터 상기 n차 계단 패턴을 형성하는 단계와, 상기 제m 예비 계단 패턴을 형성하는 단계로부터 상기 m차 계단 패턴을 형성하는 단계는 각각 동일한 식각 챔버 내에서 인시튜로 수행될 수 있다.

본 발명의 일 실시예에서, 상기 제1 보호막 패턴을 형성하는 단계로부터 상기 제n+1 예비 계단 패턴을 형성하는 단계는 4회 이상 반복 수행할 수 있다.

본 발명의 일 실시예에서, 상기 m차 계단 패턴을 형성한 다음에, 상기 각 층의 희생막들을 제거한다. 또한, 상기 희생막 내부에 금속 물질막을 형성한다.

설명한 것과 같이, 본 발명에 의하면 포토레지스트 패턴의 트리밍 공정을 수행할 때 기 형성되어 있는 포토레지스트 패턴의 상부면은 거의 제거되지 않는다. 이와같이, 상기 트리밍 공정에서 상기 포토레지스트 패턴의 높이 감소 및 폭의 산포가 거의 발생되지 않으므로, 더 많은 횟수의 포토 트리밍이 가능하다. 따라서, 계단형 패턴을 형성하기 위하여 수행되는 사진 공정 단계의 수가 감소된다. 그러므로, 저 비용으로 수직형 반도체 소자를 제조할 수 있다.

도 1a 내지 도 1l은 본 발명의 실시예 1에 따른 계단형 패턴의 형성 방법을 나타내는 단면도들이다.

도 2a 내지 도 2g는 계단형 패턴의 형성 방법을 나타내는 단면도들이다.

도 3a 내지 도 3c는 각각의 사진 공정 시에 생성되는 포토 얼라인 키의 일 예를 나타내는 평면도이다.

도 4a 내지 도 4d는 본 발명의 실시예 2에 따른 수직형 반도체 소자의 제조 방법을 나타내는 단면도이다.

도 5a 및 도 5b는 본 발명의 실시예 3에 따른 수직형 반도체 소자의 제조 방법을 나타내는 단면도이다.

도 2a 내지 도 2g는 계단형 패턴의 형성 방법을 나타내는 단면도들이다.

도 3a 내지 도 3c는 각각의 사진 공정 시에 생성되는 포토 얼라인 키의 일 예를 나타내는 평면도이다.

도 4a 내지 도 4d는 본 발명의 실시예 2에 따른 수직형 반도체 소자의 제조 방법을 나타내는 단면도이다.

도 5a 및 도 5b는 본 발명의 실시예 3에 따른 수직형 반도체 소자의 제조 방법을 나타내는 단면도이다.

이하, 첨부한 도면을 참조하여 본 발명의 바람직한 실시예를 상세히 설명하고자 한다.

본 발명의 각 도면에 있어서, 구조물들의 치수는 본 발명의 명확성을 기하기 위하여 실제보다 확대하여 도시한 것이다.

본 발명에서, 제1, 제2 등의 용어는 다양한 구성요소들을 설명하는데 사용될 수 있지만, 상기 구성요소들은 상기 용어들에 의해 한정되어서는 안 된다. 상기 용어들은 하나의 구성요소를 다른 구성요소로부터 구별하는 목적으로만 사용된다.

본 발명에서 사용한 용어는 단지 특정한 실시예를 설명하기 위해 사용된 것으로, 본 발명을 한정하려는 의도가 아니다. 단수의 표현은 문맥상 명백하게 다르게 뜻하지 않는 한, 복수의 표현을 포함한다. 본 출원에서, "포함하다" 또는 "가지다" 등의 용어는 명세서 상에 기재된 특징, 숫자, 단계, 동작, 구성요소, 부품 또는 이들을 조합한 것이 존재함을 지정하려는 것이지, 하나 또는 그 이상의 다른 특징들이나 숫자, 단계, 동작, 구성요소, 부품 또는 이들을 조합한 것들의 존재 또는 부가 가능성을 미리 배제하지 않는 것으로 이해되어야 한다.

본 발명에 있어서, 각 층(막), 영역, 전극, 패턴 또는 구조물들이 대상체, 기판, 각 층(막), 영역, 전극 또는 패턴들의 "상에", "상부에" 또는 "하부"에 형성되는 것으로 언급되는 경우에는 각 층(막), 영역, 전극, 패턴 또는 구조물들이 직접 기판, 각 층(막), 영역, 또는 패턴들 위에 형성되거나 아래에 위치하는 것을 의미하거나, 다른 층(막), 다른 영역, 다른 전극, 다른 패턴 또는 다른 구조물들이 대상체나 기판 상에 추가적으로 형성될 수 있다.

본문에 개시되어 있는 본 발명의 실시예들에 대해서, 특정한 구조적 내지 기능적 설명들은 단지 본 발명의 실시예를 설명하기 위한 목적으로 예시된 것으로, 본 발명의 실시예들은 다양한 형태로 실시될 수 있으며 본문에 설명된 실시예들에 한정되는 것으로 해석되어서는 안된다.

즉, 본 발명은 다양한 변경을 가할 수 있고 여러 가지 형태를 가질 수 있는 바, 특정 실시예들을 도면에 예시하고 본문에 상세하게 설명하고자 한다. 그러나, 이는 본 발명을 특정한 개시 형태에 대해 한정하려는 것이 아니며, 본 발명의 사상 및 기술 범위에 포함되는 모든 변경, 균등물 내지 대체물을 포함하는 것으로 이해되어야 한다.

실시예 1

도 1a 내지 도 1l은 본 발명의 실시예 1에 따른 계단형 패턴의 형성 방법을 나타내는 단면도들이다.

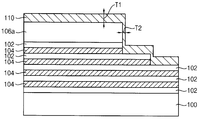

도 1a를 참조하면, 기판(100) 상에 층간 절연막(102) 및 희생막(104)을 순차적으로 반복 적층하여 적층 구조물을 형성한다. 상기 적층 구조물의 최상부 층에는 층간 절연막(102)이 형성될 수 있다.

상기 층간 절연막(102)은 실리콘 산화물을 증착시켜 형성할 수 있다. 상기 희생막(104)은 상기 층간 절연막(102)과 식각 선택비를 갖는 물질로 형성한다. 일 예로, 상기 희생막(104)은 실리콘 질화물 또는 폴리실리콘으로 형성할 수 있다. 이하에서, 상기 희생막(104)은 실리콘 질화물인 것으로 설명한다.

상기 층간 절연막(102) 및 희생막(104)이 적층되는 수는 한정되지 않는다. 본 실시예에서는, 기판(100) 표면으로부터 제1 내지 제5 층간 절연막과 제1 내지 제4 희생막이 각각 교대로 적층되는 것으로 설명한다.

최상부의 층간 절연막(102) 상에 포토레지스트막을 형성한다. 상기 포토레지스트막은 스핀 코팅 공정을 통해 형성할 수 있다. 상기 포토레지스트막은 사진 공정을 통해 패터닝될 수 있을 정도의 높이로 형성할 수 있다. 예를들어, 상기 포토레지스트막은 1 내지 6㎛의 높이로 형성할 수 있다. 상기 포토레지스트막을 사진 공정에 의해 패터닝하여 제1 포토레지스트 패턴(106)을 형성한다.

상기 제1 포토레지스트 패턴(106)은 상기 최상부의 층간 절연막(102)의 가장자리 부위가 노출되도록 형성한다. 상기 제1 포토레지스트 패턴(106)에 의해 노출되는 부위의 폭(W1)은 형성하고자하는 계단형 패턴의 각 층 상부폭과 실질적으로 동일하다.

도 1b를 참조하면, 상기 제1 포토레지스트 패턴(106)을 식각 마스크로 사용하여 상기 제1 포토레지스트 패턴(106)에 의해 노출된 최상부 1층의 층간 절연막(102) 및 희생막(104)을 식각한다.

상기 식각 공정을 수행하면, 상기 제5 층간 절연막 및 제4 희생막이 일부 제거되어 최상부에 한 층의 제1 예비 계단 패턴(103)이 형성된다. 이하에서, 각 층 예비 계단 패턴의 층 수는 최상부단을 제외하고, 최상부단으로부터 하부로 생성되는 계단의 단수로 계수한다. 상기 제1 예비 계단 패턴(103)에서 노출되는 상부면은 상기 제4 층간 절연막이 된다.

도 1c를 참조하면, 상기 제1 포토레지스트 패턴(106)의 상부면, 측벽과 상기 제1 예비 계단 패턴(103)의 노출된 측벽 및 상기 제4 층간 절연막 상에 제1 보호막(108)을 형성한다. 상기 제1 보호막(108)은 수평 방향으로 평탄한 부위인 상기 제1 포토레지스트 패턴(106)의 상부면과 상기 제4 층간 절연막 표면 상에서는 제1 두께(T1)로 형성된다. 또한, 상기 제1 보호막(108)은 수직 경사 부위인 상기 제1 포토레지스트 패턴(106)의 측벽 및 제1 예비 계단 패턴(103)의 측벽 상에서는 상기 제1 두께(T1)보다 얇은 제2 두께(T2)로 형성된다. 상기 제2 두께(T2)는 상기 제1 두께(T1)의 50%이하가 되도록 한다.

상기 제1 보호막(108)은 무기물로 형성될 수 있다. 만일 탄소를 포함하는 유기물로 상기 제1 보호막(108)을 형성하면, 상기 수평 방향으로 평탄한 부위에 형성되는 막은 상기 수직 경사 부위에 형성되는 막의 두께보다 두껍게 형성되지 않는다. 또한, 상기 평탄한 부위에 형성되는 막의 두께도 균일하지 않다. 이와같이, 상기 제1 보호막을 유기물로 형성하면 막의 두께 콘트롤이 어려우며, 상기 설명한 것과 같은 두께를 갖지 못하게 된다. 때문에, 상기 제1 보호막으로 유기물을 형성하는 것은 바람직하지 않다.

상기 제1 보호막(108)은 상기 제1 포토레지스트 패턴(106)의 일부를 제거하기 위한 트리밍 공정을 수행할 때 거의 제거되지 않는 물질로 형성될 수 있다. 또한, 상기 희생막(104) 및 층간 절연막(102)을 패터닝하기 위한 식각 공정에서 상기 제1 보호막(108)이 쉽게 제거될 수 있는 물질로 형성될 수 있다.

상기 제1 보호막(108)은 상기 제1 포토레지스트 패턴에 의해 노출되어 있는 박막 즉, 상기 제4 층간 절연막과 동일한 물질로 형성될 수 있다. 이 경우, 상기 제4 층간 절연막을 패터닝할 때 잔류하는 제1 보호막(108)이 함께 제거될 수 있다. 예를들어, 상기 제1 보호막(108)은 실리콘 산화물을 포함할 수 있다.

상기 제1 보호막(108)을 형성하는 공정은 별도의 증착 챔버에서 수행되지 않으며, 식각 챔버 내에서 수행될 수 있다. 즉, 상기 식각 챔버 내에 상기 제1 보호막(108)의 소오스 가스를 유입함으로써 상기 제1 보호막(108)을 형성한다. 이와같이, 상기 제1 보호막(108)은 식각 챔버에서 형성되기 때문에, 상기 식각 챔버 내에 오염 발생이 거의 없거나 작은 소오스 가스를 사용하는 것이 바람직하다. 상기 제1 보호막(108)을 형성하기 위하여, 상기 식각 챔버 내에 SiCl4 및 O2 가스를 유입한다. 따라서, 상기 제1 보호막(108)으로써 SiOx 막을 형성한다.

도 1d를 참조하면, 상기 제1 포토레지스트 패턴(106)의 측벽과 상기 제1 예비 계단 패턴(103)의 측벽에 형성되어 있는 제1 보호막(108)을 선택적으로 식각한다. 따라서, 상기 수평 방향으로 평탄한 부위인 상기 제1 포토레지스트 패턴(106)의 상부면과 상기 제4 층간 절연막(102) 표면 상에만 제1 보호막(108)이 남아있게 되어 제1 보호막 패턴(108a)이 형성된다. 즉, 상기 제1 보호막 패턴은 적어도 상기 제1 포토레지스트 패턴의 상부면을 덮는 형상을 가질 수 있다. 상기 제1 보호막(108)을 선택적으로 식각하는 공정은 상기 제1 보호막(108)을 증착하는 식각 챔버 내에서 수행된다.

즉, 상기 제1 포토레지스트 패턴(106)의 측벽과 상기 제1 예비 계단 패턴(103)의 측벽에 형성되어 있는 제1 보호막(108)은 상기 제1 포토레지스트 패턴(106)의 상부면과 상기 제4 층간 절연막(102) 표면 상에 형성되어 있는 제1 보호막(108)보다 얇은 두께로 형성된다. 그러므로, 상기 제1 포토레지스트 패턴(106)의 측벽과 상기 제1 예비 계단 패턴(103)의 측벽에 형성되어 있는 제1 보호막(108) 부위를 제거하더라도, 상기 제1 포토레지스트 패턴(106)의 상부면과 상기 제4 층간 절연막(102) 표면 상에는 충분한 두께로 제1 보호막 패턴(108a)이 남아있을 수 있다.

도 1e를 참조하면, 상기 제1 보호막 패턴(108a)이 덮혀있지 않는 제1 포토레지스트 패턴(106)의 측벽 일부를 제거하는 제1 트리밍 공정(①)을 수행한다. 상기 제1 트리밍 공정은 상기 제1 보호막(108)을 증착할 때와 동일한 식각 챔버 내에서 수행된다.

상기 제1 트리밍 공정을 통해 상기 제1 포토레지스트 패턴(106)이 제거되는 부위의 폭은 형성하고자 하는 계단형 패턴의 각 층 상부폭과 실질적으로 동일하다. 상기 제1 포토레지스트 패턴(106)의 측벽 일부를 제거하는 제1 트리밍 공정은 산소 또는 오존을 주 식각 가스로 이용하는 건식 식각 공정을 통해 수행될 수 있다. 상기 제1 트리밍 공정을 수행하면, 상기 제1 포토레지스트 패턴(106)보다 좁은 폭의 제2 포토레지스트 패턴(106a)이 형성된다.

한편, 일반적인 경우와 같이 상기 제1 보호막 패턴(108a)이 구비되지 않으면, 상기 제1 트리밍 공정을 수행할 때 상기 제1 포토레지스트 패턴(106)의 상부면이 일부 제거되어 상기 제2 포토레지스트 패턴(106a)의 두께가 감소된다. 따라서, 트리밍을 반복 수행하게 되면, 상기 포토레지스트 패턴의 두께가 너무 얇아져서 식각 마스크로 사용하지 못하기 때문에 상기 트리밍 공정의 횟수가 매우 제한된다. 예를들어, 상기 트리밍 공정은 3회 이하로 제한될 수 있다.

그러나, 본 실시예의 경우, 상기 제1 포토레지스트 패턴(106)의 상부를 덮는 상기 제1 보호막 패턴(108a)은 트리밍 공정 시에 거의 제거되지 않는다. 그러므로, 상기 트리밍 공정에서 상기 제1 포토레지스트 패턴(106)의 상부는 거의 제거되지 않는다. 때문에, 상기 트리밍 공정에 의해 형성되는 제2 포토레지스트 패턴(106a)은 제1 포토레지스트 패턴(106)과 거의 동일한 높이를 가질 수 있다.

이와같이, 상기 트리밍 공정에 의해 포토레지스트 패턴의 폭은 변화하지만, 포토레지스트 패턴의 두께는 거의 변화하지 않는다. 그러므로, 상기 포토레지스트 패턴에 수행할 수 있는 트리밍 공정 횟수를 증가시킬 수 있다.

도 1f를 참조하면, 상기 제1 보호막 패턴(108a)의 적어도 일부를 제거한다. 예를들어, 도시된 것과 같이, 상기 제1 보호막 패턴(108a)에서 적어도 상기 제2 포토레지스트 패턴(106a)의 측방으로 돌출되는 부위가 제거되도록 할 수 있다. 이와는 다른예로, 상기 제1 보호막 패턴(108a)을 모두 제거할 수도 있다. 상기 제1 보호막 패턴(108a)의 적어도 일부를 제거하는 공정은 상기 제1 보호막(108)을 증착할 때와 동일한 식각 챔버 내에서 수행된다.

상기 제2 포토레지스트 패턴(106a)의 측방으로, 상기 제5 및 제4 층간 절연막(102)이 노출된다.

도 1g를 참조하면, 상기 제2 포토레지스트 패턴(106a)을 식각 마스크로 사용하여 노출되어 있는 층간 절연막들(102) 및 그 하부의 희생막들(104)을 각각 식각한다. 즉, 최상층으로부터 2층의 층간 절연막들(102) 및 희생막들(104)을 식각할 수 있다.

상기 제1 보호막 패턴(108a)은 상기 층간 절연막들과 동일한 물질로 형성될 수 있다. 따라서, 이 전의 공정에서 제거되지 않고 남아있는 제1 보호막 패턴(108a)은 상기 층간 절연막들(102) 및 희생막들(104)을 제거하는 공정에서 모두 제거될 수 있다.

상기 공정을 수행하면, 최상부층에 2층의 제2 예비 계단 패턴(103a)이 형성된다. 또한, 상기 제2 포토레지스트 패턴(106a)의 측방으로 상기 제4 및 제3 층간 절연막(102)이 노출된다.

상기 식각 공정은 상기 제1 보호막(108)을 증착할 때와 동일한 식각 챔버 내에서 수행된다. 이와같이, 도 1c 내지 도 1g를 참조로 설명한 공정들은 모두 동일한 식각 챔버 내에서 인시튜로 수행될 수 있다.

계속하여, 도 1c 내지 도 1g를 참조로 설명한 공정들을 반복하여 수행한다. 즉, 도 1c 내지 도 1g에서 설명한 공정들은 1회의 공정 싸이클(1 process cycle)이 되며, 상기 공정 싸이클을 수행한 횟수는 트리밍 공정의 횟수가 된다. 이하에서, 계단형 패턴 형성을 위하여 반복되는 공정 싸이클에 대해 간단하게 설명한다.

도 1h를 참조하면, 상기 제2 포토레지스트 패턴(106a)의 상부면, 측벽과 상기 제2 예비 계단 패턴(103a)의 측벽 및 상기 제4 및 제3 층간 절연막(102)의 상부면 상에 제2 보호막(110)을 형성한다. 상기 제2 보호막(110)은 상기 수평 방향으로 평탄한 부위인 상기 제2 포토레지스트 패턴(106a)의 상부면과 상기 제4 및 제3 층간 절연막(102) 표면 상에서는 제1 두께(T1)로 형성된다. 또한, 상기 제2 보호막(110)은 수직 경사 부위인 상기 제2 포토레지스트 패턴(106a)의 측벽 및 제2 예비 계단 패턴(103a)의 측벽 상에서는 상기 제1 두께(T1)보다 얇은 제2 두께(T2)로 형성된다. 상기 제2 두께(T2)는 상기 제1 두께(T1)의 50%이하가 되도록 한다. 상기 제2 보호막(110)은 상기 제1 보호막(108)과 동일한 물질로 형성될 수 있다.

도 1i를 참조하면, 상기 제2 포토레지스트 패턴(106a)의 측벽과 상기 제2 예비 계단 패턴(103a)의 측벽에 형성되어 있는 제2 보호막(110)을 선택적으로 식각하여 제2 보호막 패턴(110a)을 형성한다. 이와같이, 후속의 트리밍 공정이 수행되기 이 전에, 새로운 보호막 패턴을 형성한다.

도 1j를 참조하면, 상기 제2 보호막 패턴(110a)이 덮혀있지 않는 제2 포토레지스트 패턴(106a)의 측벽 일부를 제거하는 제2 트리밍 공정(②)을 수행하여 제3 포토레지스트 패턴(106b)을 형성한다.

도 1k를 참조하면, 상기 제2 보호막 패턴(110a)의 적어도 일부를 제거한다. 다음에, 상기 제3 포토레지스트 패턴(106b)을 식각 마스크로 이용하여 노출되어 있는 층간 절연막들(102) 및 그 하부의 희생막들(104)을 각각 식각한다. 상기 공정을 수행하면, 최상부층에 3층의 제3 예비 계단 패턴(103b)이 형성된다. 또한, 상기 제3 포토레지스트 패턴(106b)의 측방으로 상기 제2 내지 제4 층간 절연막(102)이 노출된다.

상기 공정들은 도 1f 및 도 1g를 참조로 설명한 것과 동일하다.

도 1l을 참조하면, 상기 도 1k에 도시된 구조에 대하여 상기 도 1c 내지 도 1g를 참조로 설명한 1회의 공정 싸이클을 동일하게 수행한다. 따라서, 1층의 계단형 패턴이 추가적으로 생성됨으로써 4층의 계단형 패턴이 완성된다.

이와같이, 상기 공정 싸이클들을 반복하여 수행함으로써 원하는 층수의 계단형 패턴을 형성할 수 있다.

본 실시예의 방법에 의하면, 상기 보호막 패턴에 의해 상기 트리밍 공정 시에 포토레지스트 패턴의 두께 및 형상 변화가 거의 발생되지 않는다. 때문에, 상기 트리밍 공정 횟수를 증가시킬 수 있으며, 4회 이상의 트리밍 공정을 수행할 수 있다.

이하에서는, 상기 설명한 실시예 1의 방법을 이용하여, 더 높은 층수를 갖는 계단형 패턴 형성 방법을 설명한다.

도 2a 내지 도 2g는 계단형 패턴의 형성 방법을 나타내는 단면도들이다.

도 2a를 참조하면, 기판(200) 상에 층간 절연막(202) 및 희생막(204)을 순차적으로 반복 적층한다. 최상부 층에는 층간 절연막(202)이 형성될 수 있다. 상기 층간 절연막(202) 및 희생막(204)이 적층되는 수는 한정되지 않는다. 본 실시예에서는, 기판(200) 표면으로부터 제1 내지 제19 층간 절연막(202)과 제1 내지 제18 희생막(204)이 교대로 반복 적층되는 것으로 설명한다.

본 실시예에서와 같이 계단형 패턴의 층수가 높은 경우, 트리밍 공정을 수행하더라도 1회의 사진 공정만으로 계단형 패턴을 모두 형성하기는 어렵다. 그러므로, 본 실시예에서는 3회의 사진 공정으로 계단형 패턴을 형성하는 것으로 설명한다. 따라서, 각각의 사진 및 식각 공정에서 완성되는 계단형 패턴 부위에 따라, 1차 포토 영역, 2차 포토 영역 및 3차 포토 영역을 구분할 수 있다.

먼저, 상기 최상부 층의 층간 절연막(202) 상에 제1 포토레지스트막을 형성하고 상기 제1 포토레지스트막에 대해 1차 사진 공정을 수행하여 1차 포토레지스트 패턴(206)을 형성한다. 상기 제1차 포토레지스트 패턴(206)은 최상부의 몇개의 층의 계단형 패턴을 완성하기 위한 마스크로 제공된다. 본 실시예에서는, 상기 1차 포토레지스트 패턴(206)을 이용하여 상부로부터 6층의 계단형 패턴을 형성하는 것으로 설명한다. 이 때, 상기 1차 포토레지스트 패턴(206)에 의해 상기 2차 및 3차 포토 영역의 상부면은 모두 노출된다.

도 2b를 참조하면, 상기 1차 포토레지스트 패턴(206)을 이용하여 상기 1차 포토레지스트 패턴(206)에 의해 노출된 최상부 1층의 층간 절연막(202) 및 희생막(204)을 식각한다. 상기 1차 포토레지스트 패턴(206)과 상기 식각에 의해 형성된 예비 계단 패턴 상에 제1 보호막을 형성한다. 상기 제1 보호막의 일부를 식각하여 상기 1차 포토레지스트 패턴 측벽이 노출되면서 상기 1차 포토레지스트 패턴의 상부면은 덮는 제1 보호막 패턴(208)을 형성한다. 상기 공정들은 도 1b 내지 도 1d를 참조로 설명한 것과 동일한 방법으로 수행될 수 있다.

도 2c를 참조하면, 상기 1차 포토레지스트 패턴에 대해 제1 트리밍 공정(1)을 수행하여 제2 포토레지스트 패턴을 형성한다. 이 후, 상기 제1 보호막 패턴(208)에서 적어도 상기 제2 포토레지스트 패턴의 측방으로 돌출되는 부위를 제거한다. 상기 제2 포토레지스트 패턴을 식각마스크로 사용하여 최상층으로부터 2층의 층간 절연막들(202) 및 희생막들(204)을 식각한다. 상기 공정들은 도 1e 내지 도 1g를 참조로 설명한 것과 동일한 방법으로 수행될 수 있다.

계속하여, 도 1c 내지 도 1g에서 설명한 공정들로 이루어지는 1회의 공정 싸이클들을 수 회 반복하여 수행함으로써, 상기 제1 포토 영역 내에 1차 계단형 패턴(209)을 완성한다.

상기 공정 싸이클들을 수행한 횟수와 동일한 횟수만큼 상기 1차 포토레지스트 패턴(206)에 대해 트리밍 공정이 수행된다. 또한, 상기 트리밍 공정이 수행된 횟수보다 1개 많은 층의 1차 계단형 패턴(209)이 상기 1차 포토 영역 내에 형성될 수 있다.

본 실시예에서는, 도시된 것과 같이, 5회의 트리밍 및 식각 공정을 수행하여 상기 1차 계단형 패턴(209)을 형성한다. 이 경우, 1회의 사진 공정을 통해 상부로부터 6층의 1차 계단형 패턴(209)을 형성할 수 있다. 그러나, 상기 트리밍 공정 횟수는 이에 한정되지 않으며 증가 또는 감소될 수 있다. 상기 1차 계단형 패턴(209)을 형성한 이 후에, 상기 1차 포토레지스트 패턴을 제거한다.

상기에서 설명한 것과 같이, 상기 보호막 패턴이 형성됨으로써 상기 트리밍 공정 횟수를 증가시킬 수 있다. 그러나, 상기 보호막 패턴을 형성하더라도, 상기 보호막 패턴을 제거하는 공정에서 상기 1차 포토레지스트 패턴이 다소 손상 및 제거될 수 있다. 때문에, 상기 1차 포토레지스트 패턴에 대해 트리밍 공정을 무한한 횟수로 진행할 수는 없다. 따라서, 설정된 수 회의 트리밍 공정을 수행한 이 후에는 다시 사진 공정을 수행하여야 한다.

도 2d를 참조하면, 상기 1차 계단형 패턴(209)이 형성된 구조물 상에 제2 포토레지스트막을 형성한다. 이 때, 상기 제2 포토레지스트막은 상기 1차 계단형 패턴 상에 형성되는 두께가 상기 1차 계단형 패턴이 형성되지 않은 부위의 평탄면의 층간 절연막 상에 형성되는 두께보다 얇아질 수 있다.

상기 제2 포토레지스트막에 대해 2차 사진 공정을 수행하여 2차 포토레지스트 패턴(210)을 형성한다.

상기 2차 포토레지스트 패턴(210)은 상기 1차 계단형 패턴(109) 아래에 몇개의 층의 2차 계단형 패턴을 완성하기 위한 마스크로 제공된다. 본 실시예에서는, 상기 2차 포토레지스트 패턴(210)을 이용하여 6층의 2차 계단형 패턴을 형성하는 것으로 설명한다. 또한, 상기 2차 포토레지스트 패턴(210)을 이용하여 2차 포토 영역에 2차 계단형 패턴이 형성된다. 상기 2차 포토레지스트 패턴(210)은 완성된 1차 계단형 패턴을 모두 덮는 형상을 갖는다. 반면에, 상기 2차 포토레지스트 패턴(210)에 의해 상기 3차 포토 영역의 상부면이 모두 노출된다.

상기 2차 포토레지스트 패턴(210)을 식각 마스크로 사용하여 노출된 최상부 1층의 층간 절연막 및 희생막을 식각하여 제1 예비 계단 패턴(211)을 형성한다.

계속하여, 상기 2차 포토레지스트 패턴(210)의 상부면, 측벽과 상기 제1 예비 계단 패턴(211)의 측벽 및 노출된 층간 절연막(202)의 상부면 상에 제2 보호막을 형성한다. 상기 2차 포토레지스트 패턴(210)의 측벽과 상기 제1 예비 계단 패턴(211)의 측벽에 형성되어 있는 제2 보호막을 선택적으로 식각하여 제2 보호막 패턴(212)을 형성한다.

도 2e를 참조하면, 상기 제2 보호막 패턴(212)이 덮혀있지 않는 부위인 상기 2차 포토레지스트 패턴(210)의 측벽 일부를 제거하는 제1 트리밍 공정(1)을 수행하여 제2 포토레지스트 패턴을 형성한다.

상기 제2 보호막 패턴(212)이 구비되지 않으면, 상기 트리밍 공정을 수행할 때, 상기 2차 포토레지스트 패턴(210)의 상부면도 함께 제거되어 상기 제2 포토레지스트 패턴의 두께가 감소된다. 특히, 상기 1차 계단형 패턴(209) 상에 형성된 2차 포토레지스트 패턴(210)의 두께는 다른 부위에 비해 상대적으로 얇기 때문에, 상기 트리밍 공정 시에 상기 부위의 2차 포토레지스트 패턴(210)이 제거되어 상기 1차 계단형 패턴(209)을 마스킹하지 못하는 등의 문제가 발생될 수 있다. 때문에, 상기 트리밍 공정의 횟수가 3회 이하로 제한되고 있다.

그러나, 본 실시예의 방법에 의하면, 상기 2차 포토레지스트 패턴(210) 상부면에 제2 보호막 패턴(212)이 구비되어 있다. 때문에, 상기 2차 포토레지스트 패턴(210)을 트리밍하는 공정에서 상기 2차 포토레지스트 패턴(210)의 상부면이 거의 제거되지 않는다. 따라서, 상기 트리밍 공정의 횟수를 4회 이상으로 증가시킬 수 있다.

계속하여, 상기 제2 보호막 패턴(212)에서 적어도 상기 제2 포토레지스트 패턴의 측방으로 돌출되는 부위를 제거한다. 상기 제2 포토레지스트 패턴을 식각마스크로 사용하여 최상층으로부터 2층의 층간 절연막들(202) 및 희생막들(204)을 식각한다. 상기 공정들은 도 1e 내지 도 1g를 참조로 설명한 것과 동일한 방법으로 수행될 수 있다.

계속하여, 도 1c 내지 도 1g를 참조로 설명한 공정들로 이루어지는 1회의 공정 싸이클들을 반복하여 수행한다. 상기 공정을 통해, 상기 제2 포토 영역 내에 2차 계단형 패턴(213)을 완성한다.

본 실시예에서는, 도시된 것과 같이, 5회의 트리밍 및 식각 공정을 수행하여 상기 2차 계단형 패턴(213)을 형성한다. 이 경우, 1회의 사진 공정을 통해 6층의 2차 계단형 패턴(213)을 형성할 수 있다. 상기 2차 계단형 패턴(213)을 형성한 이 후에, 상기 2차 포토레지스트 패턴을 제거한다.

도 2f를 참조하면, 상기 1차 및 2차 계단형 패턴(209, 213)이 형성된 구조물 상에 제3 포토레지스트막을 형성한다. 상기 제3 포토레지스트막에 대해 3차 사진 공정을 수행하여 3차 포토레지스트 패턴(214)을 형성한다.

상기 3차 포토레지스트 패턴(214)은 상기 2차 계단형 패턴(109) 아래에 몇개의 층의 3차 계단형 패턴을 완성하기 위한 마스크로 제공된다. 또한, 상기 3차 포토레지스트 패턴(214)을 이용하여 3차 포토 영역에 3차 계단형 패턴이 형성된다. 상기 3차 포토레지스트 패턴(214)은 완성된 1차 및 2차 계단형 패턴(209, 213)을 모두 덮는 형상을 갖는다.

이 후, 상기 3차 포토레지스트 패턴(214)을 식각 마스크로 사용하여 노출된 최상부 1층의 층간 절연막 및 희생막을 식각하여 제1 예비 계단 패턴(215)을 형성한다.

상기 3차 포토레지스트 패턴(214)의 상부면, 측벽과 상기 제1 예비 계단 패턴(215)의 측벽 및 노출된 층간 절연막(202)의 상부면 상에 제3 보호막을 형성한다. 상기 3차 포토레지스트 패턴(214)의 측벽과 상기 제1 예비 계단 패턴(215)의 측벽에 형성되어 있는 제3 보호막을 선택적으로 식각하여 제3 보호막 패턴(216)을 형성한다.

도 2g를 참조하면, 상기 제3 보호막 패턴(216)이 덮혀있지 않는 부위인 상기 3차 포토레지스트 패턴(214)의 측벽 일부를 제거하는 제1 트리밍 공정(1)을 수행하여 제2 포토레지스트 패턴을 형성한다.

계속하여, 상기 제3 보호막 패턴(216)에서 적어도 상기 제2 포토레지스트 패턴의 측방으로 돌출되는 부위를 제거한다. 상기 제2 포토레지스트 패턴을 식각마스크로 사용하여 최상층으로부터 2층의 층간 절연막들(202) 및 희생막들(204)을 식각한다. 상기 공정들은 도 1e 내지 도 1g를 참조로 설명한 것과 동일한 방법으로 수행될 수 있다.

계속하여, 도 1c 내지 도 1g를 참조로 설명한 공정들로 이루어지는 1회의 공정 싸이클들을 반복하여 수행한다. 상기 공정을 통해, 상기 제3 포토 영역 내에 3차 계단형 패턴(217)을 완성한다.

이와같이, 본 실시예에 따르면 1회 사진 공정을 수행한 후에 트리밍할 수 있는 횟수가 증가되기 때문에, 높은 층수를 갖는 계단형 패턴을 형성하는 공정에서 사진 공정을 수행하는 횟수를 감소시킬 수 있다. 따라서, 간단한 공정을 통해 높은 층수의 계단형 패턴을 용이하게 형성할 수 있다.

트리밍 횟수 확인 방법

완성된 계단형 패턴을 보고, 상기 계단형 패턴을 형성할 때 수행된 사진 공정 횟수 및 트리밍 횟수를 확인할 수 있다. 이하에서는 상기 계단형 패턴에서 사용된 사진 공정 횟수 및 트리밍 횟수를 확인하는 방법을 간단하게 설명한다.

상기 계단형 패턴을 형성하는 공정에서 수행한 사진 공정의 횟수만큼의 서로 다른 레티클이 필요하다. 예를들어, 계단형 패턴을 형성할 때 모두 5회의 사진 공정이 수행되었다면, 5개의 레티클이 필요하게 된다.

또한, 상기 사진 공정을 수행할 때마다 포토 얼라인을 수행하게 되는데, 상기 포토 얼라인시에 아들자 및 어미자를 포함하는 얼라인 키가 생기게 된다. 따라서, 상기 얼라인 키의 갯수를 확인하면, 사진 공정의 횟수를 알 수 있게 된다.

도 3a 내지 도 3c는 각각의 사진 공정 시에 생성되는 포토 얼라인 키의 일 예를 나타내는 평면도이다.

도 3a를 참조하면, 1회 사진 공정 시에 얼라인을 위하여 어미자(250a) 및 아들자(252)를 포함하는 제1 포토 얼라인 키가 생성된다. 이 때, 상기 1회 사진 공정 시에, 후속의 사진 공정 시에 사용될 포토 얼라인 키의 어미자(도 3b의 250b, 도 3c의 250c)도 함께 형성될 수 있다. 상기 후속의 사진 공정에서 사용될 포토 얼라인 키의 어미자는 상기 제1 포토 얼라인 키가 형성되는 위치와는 다른 위치에 형성될 수 있다.

도 3b를 참조하면, 2회 사진 공정 시에 얼라인을 위하여 어미자(250b) 및 아들자(254)를 포함하는 제2 포토 얼라인 키가 생성된다. 또한, 도 3c를 참조하면, 3회 사진 공정 시에도 어미자(250c) 및 아들자(256)를 포함하는 제3 포토 얼라인 키가 생성된다.

이와같이, 3회의 사진 공정이 수행된 경우에는 도 3a 내지 도 3c에 도시된 것과 같이 서로 다른 형상의 3개의 포토 얼라인 키가 생성될 수 있다. 그러므로, 상기 포토 얼라인 키를 확인하면, 사진 공정의 횟수를 알 수 있게 된다.

한편, 상기 계단형 패턴에서 계단의 전체 층수에 사진 공정 횟수를 나누게 되면, 1회 사진 공정에 의해 형성되는 계단의 층수가 구해지게 된다. 예를들어, 24층의 계단형 패턴에서 4회의 사진 공정이 수행되었을 경우에는 1회의 사진 공정에 의해 6층의 계단형 패턴이 형성되었음을 알 수 있다. 이 경우, 1층의 계단형 패턴은 1회 사진 공정에 의해 형성된 제1 포토레지스트 패턴에 의해 형성된 것이고, 나머지 5층의 계단형 패턴은 상기 제1 포토레지스트 패턴을 계속 트리밍하여 형성된 제2 내지 제6 포토레지스트 패턴에 의해 형성된 것임을 알 수 있다. 따라서, 상기 계단형 패턴의 경우, 1회의 사진 공정에서 각각 5회의 트리밍 공정이 수행되었음을 알 수 있다.

이와같이, 최종적으로 완성된 계단형 패턴에서도 트리밍 공정이 수행된 횟수를 확인할 수 있다. 따라서, 본 실시예에서와 같이, 포토레지스트 패턴에 대해 4회 이상의 트리밍 공정을 진행하였는지 여부도 확인할 수 있다.

상기 설명한 계단형 패턴 형성 방법은 수직형 반도체 소자를 제조하는데 사용될 수 있다. 예를들어, 상기 계단형 패턴 형성 방법은 금속을 포함하는 워드라인 구조물을 갖는 수직형 반도체 소자를 제조하는데 사용될 수 있다. 이 경우, 상기 계단형 패턴에 포함되어 있는 희생막 패턴을 제거하고 상기 희생막 패턴이 제거된 부위에 금속 물질을 채워넣는 공정이 추가적으로 수행될 수 있다. 따라서, 상기 금속 물질이 채워진 부위는 각 층 워드 라인으로 제공될 수 있다.

이와는 다른 예로, 상기 계단형 패턴 형성 방법은 폴리실리콘으로 형성되는 워드라인 구조물을 갖는 수직형 반도체 소자를 제조하는데 사용될 수 있다. 이 경우, 상기 계단형 패턴에서의 희생막 패턴은 폴리실리콘으로 형성할 수 있다. 따라서, 상기 계단형 패턴은 상기 수직형 반도체 소자의 층간 절연막 및 워드 라인 구조물의 적층 구조로써 제공될 수 있다.

이하에서는, 상기 계단형 패턴 형성 방법을 이용하여, 금속을 포함하는 워드 라인 구조물을 갖는 수직형 반도체 소자의 제조 방법을 간단하게 설명한다.

실시예 2

도 4a 내지 도 4d는 본 발명의 실시예 2에 따른 수직형 반도체 소자의 제조 방법을 나타내는 단면도이다.

도 4a를 참조하면, 메모리 셀들이 형성되는 셀 영역을 포함하는 반도체 기판(200)을 마련한다. 상기 셀 영역 내에는 메모리 셀들이 형성되는 셀 형성 영역 및 상기 메모리 셀들을 전기적으로 연결하는 배선들이 형성되는 연결 영역이 포함된다. 상기 반도체 기판(200)은 단결정 실리콘 기판일 수 있다.

상기 반도체 기판(200) 상에 제1 층간 절연막 및 희생막들을 순차적으로 반복 적층한다. 상기 제1 층간 절연막들은 실리콘 산화물을 증착시켜 형성할 수 있다. 상기 희생막들은 상기 제1 층간 절연막들과 식각 선택비를 갖는 물질로 형성한다. 일 예로, 상기 희생막들은 실리콘 질화물로 형성할 수 있다.

다음에, 도 2a 내지 도 2g를 참조로 설명한 공정들을 수행하여 상기 연결 영역에 계단형 몰드 패턴(228)을 형성할 수 있다.

도 4b를 참조하면, 상기 계단형 몰드 패턴(228)을 덮는 제2 층간 절연막(230)을 형성한다. 상기 계단형 몰드 패턴(228)을 관통하여 기판(200) 표면을 노출하는 복수의 채널홀들을 형성한다. 상기 채널홀 내부의 하부를 채우는 반도체 패턴(232)을 형성한다. 상기 반도체 패턴(232)은 선택적 에피택셜 성장 공정을 통해 형성할 수 있다.

상기 채널홀들의 내측벽 상에 전하 저장막 및 터널 절연막(236)을 순차적으로 형성한다. 도 4b에서는 상기 전하 저장막 및 터널 절연막을 하나의 층(236)으로 도시하였다. 또한, 상기 터널 절연막(236) 상에 상기 반도체 패턴(232)과 접촉하는 채널 패턴(238)을 형성한다. 상기 채널 패턴(238) 상에는 상기 채널홀들의 내부를 대부분 매립하는 매립 절연막 패턴(240)이 형성된다. 또한, 상기 매립 절연막 패턴(240) 상에 상기 채널 패턴(238)의 측벽과 접촉하면서 상기 채널홀의 입구 부위를 덮는 패드 패턴(242)을 형성한다.

상기 공정에 의해, 상기 채널홀 내부에는 반도체 패턴(232) 및 채널 패턴(238)을 포함하는 필러 구조물들이 형성된다.

도 4c를 참조하면, 상기 필러 구조물들 사이 부위의 있는 계단형 몰드 패턴들을 식각하여 일 방향으로 연장되는 트렌치 형상의 개구부(도시안됨)를 형성한다. 상기 개구부의 저면에는 기판(200) 표면이 노출될 수 있다. 상기 개구부의 연장 방향은 워드 라인 구조물의 연장 방향과 동일할 수 있다.

상기 개구부를 형성한 다음, 상기 개구부의 측벽에 노출되어 있는 상기 희생막 패턴들(204)을 제거하여 상기 적층된 제1 층간 절연막(202)들 사이에 갭을 형성한다.

상기 갭 및 개구부의 내부면을 따라 블록킹 유전막, 베리어 금속막 및 금속막을 형성한다. 이 후, 상기 개구부 내부에 형성된 베리어 금속막 및 금속막을 식각하여 상기 갭 내부에 워드 라인 구조물(244)을 형성한다.

상기 워드 라인 구조물(244)은 상기 희생막 패턴들(204)이 제거된 부위에 형성된다. 그러므로, 상기 워드 라인 구조물(244)의 측방 가장자리 부위는 계단 형상을 가지게 된다. 따라서, 상기 각 층 워드 라인 구조물들(244)에서 측방 가장자리 부위는 콘택과 접촉되는 워드 라인 패드 영역으로 제공된다.

또한, 상기 개구부 저면의 기판(200)에 N형의 불순물을 도핑함으로써, 소오스 라인(S/L)으로 사용되는 불순물 영역(도시안됨)을 형성한다.

이 후, 상기 구조물들을 덮는 제3 층간 절연막(246)을 형성한다.

도시하지는 않았지만, 상기 제3 층간 절연막(246) 내에 상기 패드 패턴과 접촉하는 비트 라인 콘택 및 상기 비트 라인 콘택과 전기적으로 연결되는 비트 라인을 형성한다.

도 4d를 참조하면, 상기 제3 및 제2 층간 절연막(246, 230)과 각 층의 제1 층간 절연막(202)을 관통하여 상기 워드 라인 구조물의 패드 영역과 접촉하는 콘택 플러그들(248)을 각각 형성한다.

설명한 것과 같이, 워드 라인 구조물의 패드 영역으로 제공되는 계단형 몰드 패턴을 형성할 때, 포토레지스트 패턴에 대한 트리밍 공정 횟수를 4회 이상으로 증가시킬 수 있다. 그러므로, 상기 계단형 몰드 패턴을 형성하기 위하여 수행되어야 하는 사진 공정의 횟수를 감소시킬 수 있다. 따라서, 워드 라인 구조물의 수직 적층 수가 높은 고집적화된 수직형 반도체 소자를 저비용으로 용이하게 제조할 수 있다.

이하에서는, 상기 계단형 패턴 형성 방법을 이용하여, 폴리실리콘을 포함하는 워드 라인 구조물을 갖는 수직형 반도체 소자의 제조 방법을 간단하게 설명한다.

실시예 3

도 5a 및 도 5b는 본 발명의 실시예 3에 따른 수직형 반도체 소자의 제조 방법을 나타내는 단면도이다.

도 5a를 참조하면, 메모리 셀들이 형성되는 셀 영역을 포함하는 반도체 기판(200)을 마련한다. 상기 셀 영역 내에는 메모리 셀들이 형성되는 셀 형성 영역 및 상기 메모리 셀들을 전기적으로 연결하는 배선들이 형성되는 연결 영역이 포함된다. 상기 반도체 기판(200)은 단결정 실리콘 기판일 수 있다.

상기 반도체 기판(200) 상에 제1 층간 절연막(202) 및 폴리실리콘막(260)을 순차적으로 반복 적층한다. 즉, 본 실시예에서는 희생막이 형성되는 부위에 폴리실리콘막(260)이 형성된다. 상기 제1 층간 절연막들(202)은 실리콘 산화물을 증착시켜 형성할 수 있다. 상기 폴리실리콘막(260)은 후속 공정을 통해 워드 라인 구조물로 제공된다.

다음에, 도 2a 내지 도 2g를 참조로 설명한 공정들을 수행하여 상기 연결 영역에 계단형 몰드 패턴(228a)을 형성할 수 있다.

계속하여, 상기 계단형 몰드 패턴(228a)을 덮는 제2 층간 절연막(270)을 형성한다. 상기 계단형 몰드 패턴(228a)을 관통하여 기판 표면을 노출하는 복수의 채널홀들을 형성한다.

상기 채널홀들의 내측벽 상에 블록킹 유전막(262), 전하 저장막(264) 및 터널 절연막(266)을 순차적으로 형성한다. 또한, 상기 터널 절연막(266) 상에 상기 기판(200) 표면과 접촉하는 채널 패턴(268)을 형성한다. 도시된 것과 같이, 상기 채널 패턴(268)은 상기 채널홀 내부를 완전히 채우는 형상을 가질 수 있다.

상기 공정을 수행하면, 상기 채널 패턴(268)의 측방으로 터널 절연막(266), 전하 저장막(264), 블록킹 유전막(262)이 적층된다. 따라서, 각 층별로 셀 트랜지스터들이 완성된다.

도 5b를 참조하면, 상기 제2 층간 절연막(270) 상에 제3 층간 절연막(272)을 형성한다. 도시하지는 않았지만, 상기 제3 층간 절연막(272) 내에 상기 채널 패턴(268)과 접촉하는 비트 라인 콘택 및 상기 비트 라인 콘택과 전기적으로 연결되는 비트 라인을 형성할 수 있다.

계속하여, 상기 제3 및 제2 층간 절연막(272, 270)과 각 층의 제1 층간 절연막(202)을 관통하여 상기 워드 라인 구조물의 패드 영역과 접촉하는 콘택 플러그들(274)을 각각 형성한다.

설명한 것과 같이, 워드 라인 구조물의 패드 영역으로 제공되는 계단 형상의 폴리실리콘 패턴을 형성할 때, 포토레지스트 패턴에 대한 트리밍 공정 횟수를 4회 이상으로 증가시킬 수 있다. 그러므로, 상기 폴리실리콘 패턴을 형성하기 위하여 수행되어야 하는 사진 공정의 횟수를 감소시킬 수 있다. 따라서, 워드 라인 구조물의 수직 적층 수가 높은 고집적화된 수직형 반도체 소자를 저비용으로 용이하게 제조할 수 있다.

상기 설명한 것과 같이, 본 발명에 의하면 저비용으로 수직형 메모리 소자를 제조할 수 있다.

100 : 기판 102 : 층간 절연막

104 : 희생막

106, 106a, 106b : 제1 내지 제3 포토레지스트 패턴

103, 103a, 103b : 제1 내지 제3 예비 계단 패턴

108 : 제1 보호막 108a : 제1 보호막 패턴

110 : 제2 보호막 110a : 제2 보호막 패턴

104 : 희생막

106, 106a, 106b : 제1 내지 제3 포토레지스트 패턴

103, 103a, 103b : 제1 내지 제3 예비 계단 패턴

108 : 제1 보호막 108a : 제1 보호막 패턴

110 : 제2 보호막 110a : 제2 보호막 패턴

Claims (10)

- i)기판 상에 층간 절연막 및 희생막을 반복 적층하여 적층 구조물을 형성하는 단계;

ii)상기 적층 구조물 상에 제1 포토레지스트 패턴을 형성하는 단계;

iii)상기 제1 포토레지스트 패턴을 식각 마스크로 사용하여 최상부 1층의 층간 절연막 및 희생막을 식각하여 제n 예비 계단 패턴을 형성하는 단계;

iv)상기 제1 포토레지스트 패턴의 상부면과 측벽, 상기 제n 예비 계단 패턴의 측벽 및 상부면 상에, 무기물로 이루어지는 제1 보호막을 형성하는 단계;

v)상기 제1 포토레지스트 패턴의 측벽에 위치하는 제1 보호막을 제거하여 제1 보호막 패턴을 형성하는 단계;

vi)상기 제1 보호막 패턴에 의해 노출되는 제1 포토레지스트 패턴의 측벽 부위를 일부 제거하여 제2 포토레지스트 패턴을 형성하는 단계;

vii)상기 제2 포토레지스트 패턴을 식각 마스크로 사용하여 최상부 1층의 층간 절연막 및 희생막과, 상기 제n 예비 계단 패턴에서 노출된 상부면 아래의 1층의 층간 절연막 및 희생막을 각각 식각하여 제n+1 예비 계단 패턴을 형성하는 단계;

viii)상기 제n+1 예비 계단 패턴에 대해 상기 iv) 내지 vii) 공정을 반복 수행하여 계단 패턴을 형성하는 단계를 포함하는 계단형 패턴 형성 방법. - 제1항에 있어서, 상기 제1 포토레지스트 패턴의 상부면 및 상기 예비 계단 패턴의 상부면 상에 형성되는 제1 보호막은 상기 제1 포토레지스트 패턴의 측벽 및 상기 예비 계단 패턴의 측벽 상에 형성되는 제1 보호막보다 두께가 두껍게 형성되는 것을 특징으로 하는 계단형 패턴 형성 방법.

- 제1항에 있어서, 상기 제1 보호막은 실리콘 산화물을 포함하는 것을 특징으로 하는 계단형 패턴 형성 방법.

- 제3항에 있어서, 상기 제1 보호막은 SiCl4 및 O2 가스를 반응 가스로 사용하여 형성하는 것을 특징으로 하는 계단형 패턴 형성 방법.

- 제1항에 있어서, 상기 제1 보호막은 상기 제n 예비 계단 패턴을 형성하기 위한 식각 공정이 수행되는 챔버 내에서 인시튜로 증착되는 것을 특징으로 하는 계단형 패턴 형성 방법.

- 제1항에 있어서, 상기 iii) 내지 viii) 단계는 동일한 식각 챔버 내에서 인시튜로 수행되는 것을 특징으로 하는 계단형 패턴 형성 방법.

- 제1항에 있어서, 상기 제n+1 예비 계단 패턴을 형성하는 단계에서, 상기 제2 포토레지스트 패턴 및 제n 예비 계단 패턴 상에 잔류하는 제1 보호막 패턴이 함께 제거되는 것을 특징으로 하는 계단형 패턴 형성 방법.

- 제1항에 있어서, 상기 iv) 내지 vii) 공정은 4회 이상 수행하는 것을 특징으로 하는 계단형 패턴 형성 방법.

- 제1항에 있어서, 상기 계단 패턴을 형성한 다음에,

상기 각 층의 희생막들을 제거하는 단계; 및

상기 희생막 내부에 금속 물질막을 형성하는 단계를 더 포함하는 것을 특징으로 하는 계단형 패턴 형성 방법. - i)기판 상에 층간 절연막 및 희생막을 반복 적층하여 적층 구조물을 형성하는 단계;

ii)상기 적층 구조물 상에 1차 포토레지스트 패턴을 형성하는 단계;

iii)상기 1차 포토레지스트 패턴을 식각 마스크로 사용하여 최상부 1층의 층간 절연막 및 희생막을 식각하여 제n 예비 계단 패턴을 형성하는 단계;

iv)상기 1차 포토레지스트 패턴의 상부면 및 상기 제n 예비 계단 패턴의 상부면을 덮고, 무기물로 이루어지는 제1 보호막 패턴을 형성하는 단계;

v)상기 제1 보호막 패턴에 의해 노출되는 1차 포토레지스트 패턴의 측벽 부위를 일부 제거하여 트리밍된 포토레지스트 패턴을 형성하는 단계;

vi)상기 트리밍된 포토레지스트 패턴을 식각 마스크로 사용하여 최상부 1층의 층간 절연막 및 희생막과, 상기 제n 예비 계단 패턴에서 노출된 상부면 아래의 1층의 층간 절연막 및 희생막을 각각 식각하여 제n+1 예비 계단 패턴을 형성하는 단계;

vii)상기 제n+1 예비 계단 패턴에 대해 상기 iv) 내지 vi) 공정을 반복 수행하여 n차 계단 패턴을 형성하는 단계;

viii)적어도 상기 적층 구조물의 n차 계단 패턴의 계단 형성 부위를 덮는 2차 포토레지스트 패턴을 형성하는 단계;

ix)상기 2차 포토레지스트 패턴을 식각 마스크로 사용하여 최상부 1층의 층간 절연막 및 희생막을 식각하여 상기 n차 계단 패턴 아래에 제m 예비 계단 패턴을 형성하는 단계;

x)상기 2차 포토레지스트 패턴의 상부면 및 상기 제m 예비 계단 패턴의 상부면 상에 제2 보호막 패턴을 형성하는 단계;

xi)상기 제2 보호막 패턴에 의해 노출되는 2차 포토레지스트 패턴의 측벽 부위를 일부 제거하여 트리밍된 포토레지스트 패턴을 형성하는 단계;

xii)상기 트리밍된 포토레지스트 패턴을 식각 마스크로 사용하여 노출된 최상부 1층의 층간 절연막 및 희생막과, 상기 제m 예비 계단 패턴에서 노출된 상부면 아래의 1층의 층간 절연막 및 희생막을 각각 식각하여 제m+1 예비 계단 패턴을 형성하는 단계; 및

xiii)상기 제m+1 예비 계단 패턴에 대해 상기 x) 내지 xii) 공정을 반복 수행하여 m차 계단 패턴을 형성하는 단계를 포함하는 계단형 패턴 형성 방법.

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020120093498A KR101881857B1 (ko) | 2012-08-27 | 2012-08-27 | 계단형 패턴 형성 방법 |

| US13/910,734 US9048193B2 (en) | 2012-08-27 | 2013-06-05 | Method of forming a step pattern structure |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020120093498A KR101881857B1 (ko) | 2012-08-27 | 2012-08-27 | 계단형 패턴 형성 방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20140027666A KR20140027666A (ko) | 2014-03-07 |

| KR101881857B1 true KR101881857B1 (ko) | 2018-08-24 |

Family

ID=50148346

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020120093498A KR101881857B1 (ko) | 2012-08-27 | 2012-08-27 | 계단형 패턴 형성 방법 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9048193B2 (ko) |

| KR (1) | KR101881857B1 (ko) |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8329051B2 (en) * | 2010-12-14 | 2012-12-11 | Lam Research Corporation | Method for forming stair-step structures |

| KR102045249B1 (ko) * | 2013-01-18 | 2019-11-15 | 삼성전자주식회사 | 3차원 반도체 소자의 배선 구조물 |

| JP5970004B2 (ja) * | 2014-01-09 | 2016-08-17 | 東京エレクトロン株式会社 | 半導体装置の製造方法 |

| US9728499B2 (en) * | 2014-11-26 | 2017-08-08 | Sandisk Technologies Llc | Set of stepped surfaces formation for a multilevel interconnect structure |

| US9673057B2 (en) | 2015-03-23 | 2017-06-06 | Lam Research Corporation | Method for forming stair-step structures |

| US10381361B2 (en) | 2015-09-10 | 2019-08-13 | Samsung Electronics Co., Ltd. | Method for manufacturing semiconductor device |

| US10319735B2 (en) | 2015-09-10 | 2019-06-11 | Samsung Electronics Co., Ltd. | Method for manufacturing semiconductor device |

| KR102522161B1 (ko) * | 2015-10-08 | 2023-04-17 | 삼성전자주식회사 | 반도체 소자 및 이의 제조 방법 |

| US9741563B2 (en) * | 2016-01-27 | 2017-08-22 | Lam Research Corporation | Hybrid stair-step etch |

| KR102599668B1 (ko) * | 2016-05-09 | 2023-11-07 | 삼성전자주식회사 | 수직형 반도체 소자 및 이의 제조 방법 |

| CN108572513B (zh) * | 2017-03-10 | 2023-06-27 | 三星电子株式会社 | 用于制造半导体器件的方法 |

| US10276398B2 (en) * | 2017-08-02 | 2019-04-30 | Lam Research Corporation | High aspect ratio selective lateral etch using cyclic passivation and etching |

| CN107644876B (zh) | 2017-08-28 | 2019-01-01 | 长江存储科技有限责任公司 | 台阶结构及其形成方法 |

| KR102443047B1 (ko) * | 2017-11-16 | 2022-09-14 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 장치 방법 및 그에 의해 제조된 장치 |

| WO2020077587A1 (en) | 2018-10-18 | 2020-04-23 | Yangtze Memory Technologies Co., Ltd. | Methods for forming multi-division staircase structure of three-dimensional memory device |

| CN111106122A (zh) * | 2019-11-25 | 2020-05-05 | 长江存储科技有限责任公司 | 一种半导体结构及其制作方法 |

| CN112133790A (zh) * | 2020-09-25 | 2020-12-25 | 武汉敏芯半导体股份有限公司 | 高速光电探测器制备方法 |

| CN112614915B (zh) * | 2020-12-29 | 2022-03-08 | 江苏宜兴德融科技有限公司 | 太阳能电池测试方法和太阳能电池测试中间结构 |

| CN117690861A (zh) * | 2022-08-29 | 2024-03-12 | 长鑫存储技术有限公司 | 半导体结构的制作方法及半导体结构 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011035237A (ja) | 2009-08-04 | 2011-02-17 | Toshiba Corp | 半導体装置の製造方法及び半導体装置 |

| JP2011043856A (ja) | 2005-02-23 | 2011-03-03 | Pixtronix Inc | ディスプレイ装置およびその製造方法 |

| JP2011166061A (ja) | 2010-02-15 | 2011-08-25 | Toshiba Corp | 半導体装置の製造方法 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE10234589A1 (de) | 2002-07-30 | 2004-02-12 | Robert Bosch Gmbh | Schichtsystem mit einer Siliziumschicht und einer Passivierschicht, Verfahren zur Erzeugung einer Passivierschicht auf einer Siliziumschicht und deren Verwendung |

| KR20060042498A (ko) | 2004-11-09 | 2006-05-15 | 주식회사 하이닉스반도체 | 반도체 소자의 워드 라인 스페이서 형성 방법 |

| KR100796642B1 (ko) | 2006-01-27 | 2008-01-22 | 삼성전자주식회사 | 고집적 반도체 장치 및 그 제조 방법 |

| KR101266273B1 (ko) | 2006-06-30 | 2013-05-22 | 엘지디스플레이 주식회사 | 액정표시소자의 제조방법 |

| US8058683B2 (en) | 2007-01-18 | 2011-11-15 | Samsung Electronics Co., Ltd. | Access device having vertical channel and related semiconductor device and a method of fabricating the access device |

| JP2008205016A (ja) | 2007-02-16 | 2008-09-04 | Denso Corp | 半導体装置 |

| US7741131B2 (en) | 2007-05-25 | 2010-06-22 | Electro Scientific Industries, Inc. | Laser processing of light reflective multilayer target structure |

| KR101253497B1 (ko) | 2008-06-02 | 2013-04-11 | 엘지디스플레이 주식회사 | 액정표시장치용 어레이 기판의 제조방법 |

| KR101502585B1 (ko) | 2008-10-09 | 2015-03-24 | 삼성전자주식회사 | 수직형 반도체 장치 및 그 형성 방법 |

| KR20110015338A (ko) | 2009-08-07 | 2011-02-15 | 주식회사 하이닉스반도체 | 수직채널형 비휘발성 메모리 소자 제조 방법 |

| KR101572976B1 (ko) | 2010-01-19 | 2015-12-01 | 삼성디스플레이 주식회사 | 박막 트랜지스터 표시판 제조 방법 |

| KR101778287B1 (ko) | 2010-08-30 | 2017-09-14 | 삼성전자주식회사 | 반도체 메모리 소자 및 그 제조방법 |

| KR101778286B1 (ko) * | 2011-01-03 | 2017-09-13 | 삼성전자주식회사 | 3차원 반도체 장치의 제조 방법 |

-

2012

- 2012-08-27 KR KR1020120093498A patent/KR101881857B1/ko active IP Right Grant

-

2013

- 2013-06-05 US US13/910,734 patent/US9048193B2/en active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011043856A (ja) | 2005-02-23 | 2011-03-03 | Pixtronix Inc | ディスプレイ装置およびその製造方法 |

| JP2011035237A (ja) | 2009-08-04 | 2011-02-17 | Toshiba Corp | 半導体装置の製造方法及び半導体装置 |

| JP2011166061A (ja) | 2010-02-15 | 2011-08-25 | Toshiba Corp | 半導体装置の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20140027666A (ko) | 2014-03-07 |

| US9048193B2 (en) | 2015-06-02 |

| US20140057429A1 (en) | 2014-02-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101881857B1 (ko) | 계단형 패턴 형성 방법 | |

| US11329061B2 (en) | Method for improving channel hole uniformity of a three-dimensional memory device | |

| KR101688838B1 (ko) | 연결 구조체 형성 방법 및 이를 이용한 반도체 소자의 제조 방법 | |

| US7785980B2 (en) | Method of manufacturing semiconductor device using alignment mark and mark hole | |

| KR102171221B1 (ko) | 수직형 불휘발성 메모리 장치 및 그 제조 방법 | |

| KR101818975B1 (ko) | 수직형 반도체 소자의 제조 방법 | |

| KR102720142B1 (ko) | 수직형 메모리 소자 | |

| US20240064981A1 (en) | Vertical memory devices and methods of manufacturing the same | |

| KR102578789B1 (ko) | 반도체 장치의 제조 방법 | |

| US10103166B1 (en) | Semiconductor device and critical dimension defining method thereof | |

| KR20170126140A (ko) | 수직형 반도체 소자 및 이의 제조 방법 | |

| KR101966894B1 (ko) | 계단형 패턴 형성 방법 | |

| KR100341159B1 (ko) | 2 개의 에칭 패턴을 이용하는 반도체 메모리 장치의 제조 방법 | |

| US10930671B2 (en) | Vertical memory devices | |

| TWI678725B (zh) | 半導體元件及其關鍵尺寸的定義方法 | |

| CN112909008A (zh) | 三维存储器及其制备方法 | |

| KR102727481B1 (ko) | 수직형 메모리 장치 및 이의 제조 방법 | |

| KR20230172131A (ko) | 반도체 소자의 제조 방법 | |

| KR100567053B1 (ko) | 반도체 소자의 오버레이 측정패턴 형성방법 | |

| KR102726471B1 (ko) | 정렬 키를 포함하는 반도체 소자 | |

| KR20210127432A (ko) | 수직형 메모리 소자의 제조 방법 | |

| KR100269624B1 (ko) | 반도체장치의 콘택 형성방법 | |

| KR20220168774A (ko) | 더미 게이트 구조체를 갖는 반도체 소자 | |

| KR100540334B1 (ko) | 반도체 소자의 게이트 형성 방법 | |

| JPH088349A (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant |