KR20170124624A - Tft-lcd 디스플레이 기판의 제조방법, 액정 패널 및 액정 디스플레이 장치 - Google Patents

Tft-lcd 디스플레이 기판의 제조방법, 액정 패널 및 액정 디스플레이 장치 Download PDFInfo

- Publication number

- KR20170124624A KR20170124624A KR1020177031321A KR20177031321A KR20170124624A KR 20170124624 A KR20170124624 A KR 20170124624A KR 1020177031321 A KR1020177031321 A KR 1020177031321A KR 20177031321 A KR20177031321 A KR 20177031321A KR 20170124624 A KR20170124624 A KR 20170124624A

- Authority

- KR

- South Korea

- Prior art keywords

- photoresist

- thin film

- amorphous silicon

- layer

- drain electrode

- Prior art date

Links

- 239000000758 substrate Substances 0.000 title claims abstract description 103

- 239000004973 liquid crystal related substance Substances 0.000 title claims abstract description 36

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 19

- 229920002120 photoresistant polymer Polymers 0.000 claims abstract description 150

- 239000010408 film Substances 0.000 claims abstract description 110

- 239000010409 thin film Substances 0.000 claims abstract description 105

- 229910021417 amorphous silicon Inorganic materials 0.000 claims abstract description 97

- 239000011521 glass Substances 0.000 claims abstract description 52

- 238000001312 dry etching Methods 0.000 claims abstract description 39

- 238000000034 method Methods 0.000 claims abstract description 36

- 238000001039 wet etching Methods 0.000 claims abstract description 29

- 238000000151 deposition Methods 0.000 claims abstract description 28

- 229910052751 metal Inorganic materials 0.000 claims description 93

- 239000002184 metal Substances 0.000 claims description 93

- 238000000149 argon plasma sintering Methods 0.000 claims description 2

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 claims description 2

- 230000000149 penetrating effect Effects 0.000 claims description 2

- 239000010410 layer Substances 0.000 description 115

- 239000002253 acid Substances 0.000 description 10

- 230000007935 neutral effect Effects 0.000 description 10

- 238000003384 imaging method Methods 0.000 description 6

- 238000000206 photolithography Methods 0.000 description 5

- 238000005530 etching Methods 0.000 description 4

- 238000000427 thin-film deposition Methods 0.000 description 3

- 238000002834 transmittance Methods 0.000 description 3

- 229910004205 SiNX Inorganic materials 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 229910052814 silicon oxide Inorganic materials 0.000 description 2

- 241001239379 Calophysus macropterus Species 0.000 description 1

- 229910016024 MoTa Inorganic materials 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- 240000007594 Oryza sativa Species 0.000 description 1

- 235000007164 Oryza sativa Nutrition 0.000 description 1

- 230000002378 acidificating effect Effects 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- JZLMRQMUNCKZTP-UHFFFAOYSA-N molybdenum tantalum Chemical compound [Mo].[Ta] JZLMRQMUNCKZTP-UHFFFAOYSA-N 0.000 description 1

- MGRWKWACZDFZJT-UHFFFAOYSA-N molybdenum tungsten Chemical compound [Mo].[W] MGRWKWACZDFZJT-UHFFFAOYSA-N 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 235000009566 rice Nutrition 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136227—Through-hole connection of the pixel electrode to the active element through an insulation layer

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

- G02F1/134309—Electrodes characterised by their geometrical arrangement

- G02F1/134336—Matrix

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/13625—Patterning using multi-mask exposure

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/1368—Active matrix addressed cells in which the switching element is a three-electrode device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/1288—Multistep manufacturing methods employing particular masking sequences or specially adapted masks, e.g. half-tone mask

-

- G02F2001/13625—

Landscapes

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- General Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Optics & Photonics (AREA)

- Crystallography & Structural Chemistry (AREA)

- Chemical & Material Sciences (AREA)

- Mathematical Physics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Geometry (AREA)

- Manufacturing & Machinery (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Computer Hardware Design (AREA)

- Thin Film Transistor (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Liquid Crystal (AREA)

Abstract

본 발명은 TFT-LCD 디스플레이 기판의 제조방법에 관한 것으로서, 상기 방법은, a) 유리 기판상에 게이트전극, 게이트전극 절연층, 비결정질 실리콘층과 오믹 접촉층으로부터 조성되는 활성층, 상기 활성층상의 소스전극과 드레인전극, 완화층 및 상기 드레인전극의 상방향에 위치한 완화층 상에 비아 홀을 형성하는 단계; b) 단계 a)를 마친 유리 기판 상에 전도성 박막을 침전하고, 전도성 박막상에 포토 레지스트를 도포하고, 노출과 현상을 거친 후 TFT 영역의 완화층 비아 홀 이외의 포토 레지스트를 제거하고, 픽셀 영역이 간격 부분을 형성한 일부 포토 레지스트를 제거하고, TFT 영역의 완화층 비아 홀 이외의 전도 박막을 노출시키는 단계; c) 제4차 건식 식각을 통해 단계 b)에서의 픽셀 영역이 형성하려 하는 간격 부분의 남은 포토 레지스트를 제거하고, 상기 픽셀 영역의 간격 부분을 형성하려 하는 전도성 박막을 노출시키는 단계; d) 제3차 습식 식각을 통해 단계 b)와 단계 c)에서 노출된 도전성 박막을 제거하는 단계; e) 제거되지 않은 포토 레지스트를 박리시켜, 도전성 전극을 형성하고, 도전성 전극과 완화층 비아 홀을 연결하는 단계; 를 포함한다. 본 발명은 또한, 상기 방법을 적용하여 제조한 TFT-LCD 디스플레이 기판 및 액정 디스플레이 장치를 제공한다.

Description

본 발명은 박막 트렌지스터 액정 디스플레이 장치(Thin Film Transistor Liquid Crystal Display,TFT-LCD)기술 영역에 관한 것으로서, 특히 TFT-LCD 디스플레이 기판의 제조방법, 액정 패널 및 액정 디스플레이 장치에 관한 것이다.

정보사회의 발전에 따라, 사람들의 평판 디스플레이 장치에 대한 수요도 상당히 빨리 늘어나고 있다. TFT-LCD는 부피가 작고, 전력 소모가 낮으며, 복사가 없는 등의 장점이 있고, 현재의 평판 디스플레이 장치 시장에서 주도적인 위치를 차지하였다. 그러나, 생산 공장들 간에 경쟁이 치열하여, 디스플레이 품질을 높이고, 불량률을 낮추며, 생산 단가를 낮추는 것은 TFT-LCD 생산 업체들이 이러한 치열한 경쟁에서 살아남는데 중요한 요소가 되고 있다.

종래 기술의 TFT-LCD 디스플레이 기판의 제조방법은 주로 4차 사진석판술(4Mask,photolithography)과 5차 사진석판술(5Mask)이다. 여기에서 5Mask 공정은 주로 게이트 전극 사진석판술(Gate Mask), 활성층 사진석판술(Active Mask),소스 드레인전극 사진석판술(S/D Mask),비아 홀 사진석판술(Via Hole Mask)및 픽셀 전극 사진석판술(Pixel Mask)을 포함한다. 각 Mask 공정 단계는 다시 박막 침전(Thin Film Deposition)공정, 식각(건식 식각Dry Etch과 습식 식각Wet Etch을 포함)공정 및 박리공정으로 나뉘며, 5차 박막 침전사진석판식각박리의 순환과정을 형성한다.

4Mask공정은 5Mask공정을 기초로 하여, 회색톤 사진석판술(Gray Tone Mask)또는 반색 톤 사진석판술(Half Tone Mask)또는 SSM(Single Slit Mask)공정을 이용하는 것이고, 활성층 사진석판술(Active Mask)과 소스 드레인전극 사진석판술(S/D Mask)을 병합하여 하나의 Mask를 형성하고, 조정 식각(Etch)공정을 통하여, 본래의 Active Mask와 S/D Mask의 기능을 완성한다. 즉, 1차Mask공정을 통해 양차 Mask공정의 효과를 달성한다.

그러나, 4Mask 공정을 적용하여 TFT-LCD 디스플레이 기판을 제조하든 아니면 5Mask 공정을 적용하여 제조하든, ITO 포토 마스크를 이용하여 형성되는 ITO 전극 패턴(ITO Pattern)의 간격의 거리는 최소 2.24um이고, 이보다 더 작게 하면 노출 위치(즉, 간격지점)에 대응되는 ITO 전극 패턴이 노출된 이후 식각 커팅이 불가능한 문제가 발생하고, 더 나아가 종래의 설계와 종래 제조를 통해서는 ITO 전극 패턴의 간격의 거리를 더 축소시키는 것이 어렵고, 이에 따라 ITO 전극 도안의 간격 거리를 감소시켜 TFT-LCD 디스플레이 기판의 투광율을 높이는 것도 어려워지게 된다.

상술한 종래 기술의 문제점을 해결하기 위해, 본 발명은 TFT-LCD 디스플레이 기판의 제조방법을 제공하는 것을 목적으로 하며, 상기 방법은, a) 유리 기판상에 게이트전극, 게이트전극 절연층, 비결정질 실리콘층과 오믹 접촉층으로부터 조성되는 활성층, 상기 활성층 상의 소스전극과 드레인전극, 완화층 및 상기 드레인전극의 상방향에 위치한 완화층 상에 비아 홀을 형성하는 단계; b) 단계 a)를 마친 유리 기판 상에 전도성 박막을 침전하고, 전도성 박막상에 포토 레지스트를 도포하고, 노출과 현상을 거친 후 TFT 영역의 완화층 비아 홀 이외의 포토 레지스트를 제거하고, 픽셀 영역이 간격 부분을 형성한 일부 포토 레지스트를 제거하고, TFT 영역의 완화층 비아 홀 이외의 전도 박막을 노출시키는 단계; c) 제4차 건식 식각을 통해 단계 b)에서의 픽셀 영역이 형성하려 하는 간격 부분의 남은 포토 레지스트를 제거하고, 상기 픽셀 영역의 간격 부분을 형성하려 하는 전도성 박막을 노출시키는 단계; d) 제3차 습식 식각을 통해 단계 b)와 단계 c)에서 노출된 도전성 박막을 제거하는 단계; e) 제거되지 않은 포토 레지스트를 박리시켜, 도전성 전극을 형성하고, 도전성 전극과 완화층 비아 홀을 연결하는 단계; 를 포함한다.

여기에서, 단계 a)는, a1) 유리 기판상에 게이트전극 금속막을 침전하고, 노출, 현상 및 제1차 습식 식각, 박리를 거친 후 게이트전극을 형성하는 단계; a2) 단계 a1)을 마친

유리기판 상에 연속해서 절연막, 비결정질 실리콘막 및 혼합된 비결정질 실리콘막을 침전하고, 노출, 현상 및 제1차 건식 식각, 박리를 거친 후 게이트 전극 절연층 및 비결정질 실리콘층과 오믹접촉층으로부터 조성되는 활성층을 형성하는 단계; a3) 단계 a2)를 마친 유리기판 상에 소스/드레인 전극 금속막을 침전하고, 노출, 현상 및 제2차 습식 식각, 제2차 건식 식각, 박리를 거친 후 소스전극과 드레인전극을 형성하는 단계; a4) 단계 a3)를 마친 유리기판 상에 완화층을 침전하고, 노출, 현상 및 제3차 건식 식각, 박리를 거친 후 드레인 전극의 상방향에 위치하는 완화층 비아 홀을 형성하는 단계; 를 포함할 수 있다.

또한, 단계 a)는, a1) 유리 기판상에 게이트전극 금속막을 침전하고, 노출, 현상 및 제1차 습식 식각, 박리를 거친 후 게이트전극을 형성하는 단계; a2) 단계 a1)을 마친

유리기판 상에 연속해서 절연막, 비결정질 실리콘막, 혼합된 비결정질 실리콘막 및 소스/드레인 전극 금속막을 침전하고, 노출, 현상 및 제2차 습식 식각, 제1차 건식 식각, 제3차 습식 식각, 제2차 건식 식각, 박리를 거친 후 게이트전극 절연층, 비결정질 실리콘층과 오믹접촉층으로 조성되는 활성층 및 소스전극과 드레인전극을 형성하는 단계; a3) 단계 a2)를 마친 후의 유리기판 상에 완화층을 침전하고, 노출, 현상 및 제3차 건식 식각, 박리를 거친 후 드레인 전극 상방향에 위치하는 완화층 비아 홀을 형성하는 단계; 를 포함할 수 있다.

여기에서, 단계 a1)은, a11) 세정된 유리기판 상에 게이트전극 금속막을 침전하고, 게이트전극 금속막 상에 포토 레지스트를 도포하는 단계; a12) 단계 a11)에서 게이트전극 금속막 상에 도포된 포토 레지스트에 대해, 노출, 현상을 진행한 후, 게이트 전극이 형성되는 부분 이외의 게이트 전극 금속막을 노출하는 단계; a13) 제1차 습식 식각을 통해 단계 a12)에서 노출된 게이트 전극 금속막을 제거하는 단계; a14) 게이트 전극을 형성한 부분의 포토 레지스트를 박리하여, 게이트 전극을 형성하는 단계;를 포함할 수 있다.

또한, 단계 a2)는, a21)단계 a1)을 마친 유리기판 상에 연속해서 절연막, 비결정질 실리콘 박막 및 혼합된 비결정질 실리콘 박막을 침전하고, 혼합된 비결정질 실리콘 박막 상에 포토 레지스트를 도포하는 단계; a22) 단계 a21)에서 혼합된 비결정질 실리콘 박막 상에 도포된 포토 레지스트에 대해 노출, 현상을 진행한 후, 픽셀 영역의 혼합된 비결정질 실리콘 박막을 노출하는 단계; a23)제1차 건식 식각을 통해 픽셀 영역이 노출된 혼합된 비결정질 실리콘 박막 및 그 아래 방향의 비결정질 실리콘 박막을 제거하는 단계; a24)TFT 영역의 포토 레지스트를 박리하고, 게이트 전극 절연층 및 비결정질 실리콘층과 오믹접촉층으로 조성된 활성층을 형성하는 단계;를 포함할 수 있다.

또한, 단계 a3)은, a31)단계 a2)를 마친 유리기판 상에 소스/드레인 전극 금속막을 침전하고, 소스/드레인 전극 금속막 상에 포토 레지스트를 도포하는 단계; a32)단계 a31)에서 소스/드레인 전극 금속막 상에 도포된 포토 레지스트를 노출, 현상한 다음, 채널을 형성하려 하는 소스/드레인 전극 금속막과 픽셀 영역의 소스/드레인 전극 금속막을 노출하는 단계; a33)제2차 습식 식각을 통해 단계 a32)에서 노출한 소스/드레인 전극 금속막을 제거하는 단계; a34)제2차 건식 식각을 통해 형성된 채널 안의 혼합된 비결정질 실리콘 박막 및 그 아래 방향의 비결정질 실리콘 박막의 일부분을 제거하여, 형성된 채널이 비결정질 실리콘층으로 침투하도록 하는 단계; a35)TFT 영역에서의 채널 부분 이외의 포토 레지스트를 박리하여 제거하고, 소스 전극과 드레인 전극을 형성하는 단계;를 포함할 수 있다.

또한, 단계 a3)은, a31)단계 a1)을 마친 유리기판 상에 연속해서 절연막, 비결정질 실리콘막, 혼합된 비결정질 실리콘막 및 소스/드레인 전극 금속막을 침전하고, 소스/드레인 전극 금속막 상에 포토 레지스트를 도포하는 단계; a32)단계 a31)에서 소스/드레인 전극 금속막 상에 도포된 포토 레지스트를 노출, 현상한 후, 채널을 형성하려 하는 부분의 일부 포토 레지스터를 제거하고, 픽셀 영역의 포토 레지스트를 전부 제거하여, 픽셀 영역의 소스/드레인 전극 금속막을 노출하는 단계; a33)제2차 습식 식각으로 단계 a32)에서 노출한 소스/드레인 전극 금속막을 노출하는 단계; a34)제1차 건식 식각으로 단계 a32)에서 채널을 형성하려 하는 부분 이외의 포토 레지스트를 제거하여, 채널을 형성하려 하는 부분의 소스/드레인 전극 금속막을 노출하는 단계; a35)제3차 습식 식각으로 단계 a34)에서 노출된 소스/드레인 전극 금속막을 제거하여 채널을 형성하려 하는 부분의 혼합된 비결정질 실리콘 박막을 노출하는 단계; a36)제2차 건식 식각으로 단계 a35)에서 노출한 혼합된 비결정질 실리콘 박막 및 그 아래 방향의 일부 비결정질 실리콘 박막을 제거하여, 형성하려 하는 채널을 비결정질 실리콘층에 침투시키는 단계; a37)TFT 영역에서 채널을 형성하려 하는 부분 이외의 포토 레지스트를 박리하여 제거하고, 게이트 전극 절연층, 비결정질 실리콘층과 오믹접촉층으로 조성되는 활성층 및 소스 전극과 드레인 전극을 형성하는 단계;를 포함할 수 있다.

또한, 단계 a4)는, a41)단계 a3)를 마친 유리기판 상에 완화층 박막을 침전하고, 완화층 박막 상에 포토 레지스트를 도포하는 단계; a42)단계 a41)에서 완화층 박막 상에 도포된 포토 레지스트를 노출, 현상한 후, 완화층 비아 홀 부분을 형성하려 하는 완화층 박막을 노출하는 단계; a43)제3차 건식 식각으로 단계 a42)에서 노출한 완화층 박막을 제거하는 단계; a44)완화층 비아 홀을 형성하려 하는 부분 이외의 포토 레지스트를 박리하여 제거하고, 완화층 비아 홀을 형성하는 단계;를 포함할 수 있다.

본 발명은 또한 액정 패널을 제공하는데, 상기 액정 패널은, TFT-LCD 디스플레이 기판, 상기 TFT-LCD 디스플레이 기판에 대향하여 설치되는 여광판 기판 및 상기 TFT-LCD 디스플레이 기판과 상기 여광판 기판 사이에 설치되는 액정층을 포함하고, 상기 TFT-LCD 디스플레이 기판은 상술한 제조방법으로 제조된다.

본 발명은 또한, 액정 디스플레이 장치를 제공하는데, 상기 액정 디스플레이 장치는, 액정 패널 및 상기 액정 패널과 대향하여 설치되는 백라이트 모듈을 포함하되, 상기 백라이트 모듈이 디스플레이 광원을 상기 액정 패널에 제공하여 상기 액정 패널이 형상을 디스플레이하게 하되, 상기 액정 패널은 상술한 액정패널이다.

본 발명에서의 TFT-LCD 디스플레이 기판의 제조 방법, 액정 패널 및 액정 디스플레이 장치는 전도 전극을 형성하는 단계에서 건식 식각 제조 공정을 부가함으로써 이후의 습식 식각이 픽셀 영역이 형성하는 전도 전극 패턴의 간격 거리가 효과적으로 감소할 수 있으며, TFT-LCD 디스플레이 기판의 투광율을 높이고, 생산 단가를 절약할 수 있다.

도 1은 본 발명의 일 실시예에 따른 TFT-LCD 디스플레이 기판의 정면도이다.

도 2은 본 발명의 일 실시예에 따른 TFT-LCD 디스플레이 기판의 측면도이다.

도 3은 본 발명의 일 실시예에 따른 TFT-LCD 디스플레이 기판의 제조 방법을 나타내는 순서도이다.

도 4a부터 도4e는 본 발명의 일 실시예에 따른 픽셀 영역이 ITO 전극 패턴을 형성하는 과정을 보여주는 개략도이다.

도 5는 본 발명의 일 실시예에 따라 도 1이 도시하는 TFT-LCD 디스플레이 기판의 액정 디스플레이 장치의 구조를 나타내는 개략도이다.

도 2은 본 발명의 일 실시예에 따른 TFT-LCD 디스플레이 기판의 측면도이다.

도 3은 본 발명의 일 실시예에 따른 TFT-LCD 디스플레이 기판의 제조 방법을 나타내는 순서도이다.

도 4a부터 도4e는 본 발명의 일 실시예에 따른 픽셀 영역이 ITO 전극 패턴을 형성하는 과정을 보여주는 개략도이다.

도 5는 본 발명의 일 실시예에 따라 도 1이 도시하는 TFT-LCD 디스플레이 기판의 액정 디스플레이 장치의 구조를 나타내는 개략도이다.

이제 본 발명의 실시예에 대해 상세하게 설명할 것이며, 도면에서 예를 들어 설명하되, 여기에서 서로 동일한 부호는 동일한 구성요소를 가리킨다. 이하에서는 도면을 참고하여 실시예에 대해 설명함으로써 본 발명에 대한 이해를 하도록 한다. 도면에서는, 분명하게 볼 수 있도록 층이나 구역의 두께를 확대되어 표현되어 있을 수 있다. 이하의 설명에서, 이미 공지된 구성 및/또는 기능에 대한 불필요한 설명을 통해 발생할 수 있는 혼란을 피하기 위해 공지된 구성 및/또는 기능으로서 설명이 불필요한 부분은 상세한 설명을 생략하도록 한다.

본 발명에서의 TFT-LCD 디스플레이 기판은 주로 디스플레이 영상의 픽셀과 이를 제어하여 픽셀에 데이터를 기입하는 TFT(Thin Film Transistor,박막 전계 효과 트렌지스터)로 구성되며, 본 발명은 두 방면의 제조 방법 과정을 개량한 것으로서, 이하에 실시예를 통해 상세하게 설명하도록 한다.

도 1은 본 발명의 일 실시예에 따른 TFT-LCD 디스플레이 기판의 정면도이다. 여기에서 도 1은 단지 하나의 픽셀과 하나의 FTF 만 도시하였으나, TFT-LCD 디스플레이 기판은 도 1에서 도시하는 픽셀과 TFT 디스플레이 가 배열되어 만들어지는 것임을 이해해야 한다. 도 2은 본 발명의 일 실시예에 따른 TFT-LCD 디스플레이 기판의 측면도이다.

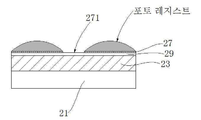

도 1 및 도 2에서 도시하는 바와 같이, 본 발명의 TFT-LCD 디스플레이 기판은 화면을 디스플레이하는 픽셀(10)과 픽셀(10)을 제어하여 데이터를 기입하는 TFT(20)를 포함하고, 여기에서 픽셀(10)이 존재하는 영역을 픽셀 영역으로 칭한다. 또한, TFT(20)이 위치하는 영역을 TFT 영역으로 칭한다. 구체적으로, TFT(20)는 유리기판(21)상에 순차적으로 형성된 게이트 전극(22), 게이트 전극 절연층(23), 비결정질 실리콘층(24)와 오믹접촉층(25)으로 조성된 활성층, 활성층 상의 소스 전극(금속층, 26a)와 드레인 전극(금속층, 26b), 완화층(29), 드레인 전극의 윗방향에 위치하고 완화층(29)상에 형성되는 완화층 비아 홀(28) 및 투명 픽셀 전극(즉, ITO(Indium Tin Oxide, 인듐 주석 산화물)전극, 27)을 포함한다. 화면을 디스플레이하는 픽셀(10)은 유리기판(21)상에 순차적으로 설치된 게이트 전극 절연층(23), 완화층(29) 및 완화층(29)상에 형성되는 ITO 전극(27)을 포함하고, 여기에서 ITO 전극(27)은 픽셀 영역에서 통상적으로 "米"자 형태의 ITO 전극 패턴을 갖춘다. 다시 말해, ITO 전극(27)은 픽셀 영역이 보이는 ITO 전극 패턴에서 간격(271)이 존재한다.

이하에서는 본 발명의 실시예에 따른 TFT-LCD 디스플레이 기판의 제조 방법에 대해 설명한다. 즉, 픽셀(10)과 TFT(20)에 대한 제조 방법에 대해서 설명한다. 도 3은 본 발명의 일 실시예에 따른 TFT-LCD 디스플레이 기판의 제조 방법을 나타내는 순서도이다. 도 4a부터 도4e는 본 발명의 일 실시예에 따른 픽셀 영역이 ITO 전극 패턴을 형성하는 과정을 보여주는 개략도이다. 또한, 도 4a부터 도4e는 도 1의 A를 따라 절단한 면을 나타내는 도면이다.

도 2와 도 3을 참조하면, 볼 발명의 일 실시예에 따른 TFT-LCD 디스플레이 기판의 제조 방법은 다음 단계들을 포함한다.

S1. 유리 기판상에 게이트 전극(22), 게이트 전극 절연층(23), 비결정질 실리콘층(24)과 오믹 접촉층(25)으로부터 조성되는 활성층, 상기 활성층상의 소스전극(금속층, 26a)과 드레인전극(금속층, 26b), 완화층(29) 및 상기 드레인전극(26a)의 상방향에 위치한 완화층(29)상에 비아 홀(28)을 형성한다.

S2. 단계 S1을 마친 유리기판(21) 상에 ITO 박막을 침전하고, ITO 박막상에 포토 레지스트를 도포한다. 픽셀 영역의 상태는 도 4a에서 도시하는 바와 같다.

*S3. ITO 포토 마스크를 이용하여 단계 S2에서 ITO 박막상에 도포된 포토 레지스트를 노출한다. 이 단계에서, ITO 포토 마스크를 통과한 후 도포된 포토 레지스트에 자외선을 조사하고, 포토 레지스트는 자외선(ultra violet-ray,UV)에 대해 감광할 수 있다. 자외선에 의해 조사됨으로써 중성에서 산성으로 바뀔 수 있고, 자외선을 받지 않은 경우 중성을 유지한다. ITO 포토 마스크는 예를 들어 4Mask 공정 중에 활성층과 소스/드레인 전극을 형성하는 단계에서 사용하는 SSM(single slit mask) 포토 마스크 또는 그레이 톤 마스크(Gray Tone Mask)또는 반색 톤 마스크(Half Tone Mask)일 수 있고, 자외선의 간섭 및 회절 효과를 통해, ITO 포토 마스크상에 반투명한 패턴 영역이 형성된다. 노출 과정에서, 자외선은 부분적으로 반투명 영역을 통과할 뿐이다. 노출량을 제어함으로써 포토 레지스트층이 부분적으로 노출되도록 할 수 있으며, 다른 부분은 충분히 노출시킬 수 있다. 현상 후에, 완전이 노출된 영역은 포토 레지스트가 없으며, 충분하게 노출되지 않은 부분의 포토 레지스트의 두께는 완전이 노출되지 않은 영역의 포토 레지스트의 두께보다 작다. 따라서, 이 단계를 마친 후, TFT 영역 안에서, 완화층 비아 홀(28) 및 그 근처에 도포된 포토 레지스트는 노출되지 않고, 그 외 다른 위치에 도포된 포토 레지스트는 충분히 노출된다. 픽셀 영역에서, 최종적으로 형성된 ITO 전극(27)에 도포된 포토 레지스트는 노출되지 않고, 최종적으로 형성된 ITO 전극 패턴의 간격(271)에 도포된 포토 레지스트는 충분하게 노출되지 않는다.

S4. 노출된 포토 레지스트(즉, 단계 S3에서 중성으로부터 산성으로 변한 포토 레지스트)를 제거하기 위해, 단계 S3에서 노출된 포토 레지스트에 대해 현상을 진행한다. 예를 들어 염기성 영상액을 이용하여 노출된 포토 레지스트를 제거한다. 또한, TFT 영역 내에서 다른 부분에 도포된 포토 레지스트를 제거하고, 상기 다른 위치에 침전된 ITO 박막을 노출시킨다. 또한, 최종적으로 형성된 ITO 전극 패턴중의 간격(271)상의 포토 레지스트를 부분적으로 제거한다. 픽셀 영역의 상태는 도 4b가 도시하는 바와 같다.

바꾸어 말하면, 단계 S3, 단계 S4에서의 노출과 현상 과정을 거친 후, TFT 영역의 완화층 비아 홀(28) 이외의 포토 레지스트를 제거하고, 픽셀 영역이 간격(271) 부분을 형성하려 한 일부 포토 레지스트를 제거하고, TFT 영역의 완화층 비아 홀 이외의 전도 박막을 노출시킨다.

S5. 제4차 건식 식각을 통해 단계 S4에서 최종적으로 형성되는 ITO 전극 패턴의 간격(271) 부분의 남은 포토 레지스트를 제거하여, 이 남은 포토 레지스트가 덮은 ITO 박막이 노출되게 한다. 픽셀 영역의 상태는 도 4c가 도시하는 바와 같다.

S6. 제3차 습식 식각을 통해 단계 S4와 단계 S5에서 노출된 ITO 박막을 제거한다. 픽셀 영역의 상태는 도 4d가 도시하는 바와 같다.

S7. 최종적으로 형성하려 하는 ITO 전극(27)을 얻어내기 위해, 단계 S3에서 노출되지 않은 포토 레지스트를 제거한다. 픽셀 영역의 상태는 도 4e에서 도시하는 바와 같다.

상술한 단계를 거쳐 형성되는 TFT-LCD 디스플레이 기판을 종래 기술과 비교하면, ITO 전극(27)을 형성하는 단계에서 건식 식각 공정을 부가함으로써, 이후 계속되는 습식 식각이 픽셀 영역이 형성하는 ITO 전극 패턴 중의 간격(271)의 거리를 1.9 ㎛가 되게 하여, 효과적으로 ITO 전극 패턴의 간격(271)의 거리를 줄일 수 있으며, TFT-LCD 디스플레이 기판의 투과율을 높일 뿐만 아니라, 생산 단가를 절약할 수 있게 된다.

단계 S1은 다음 단계들을 포함한다.

S1.1. 유리 기판(21)상에 게이트전극 금속막을 침전하고, 게이트 포토 마스크를 이용하여 노출, 현상 및 제1차 습식 식각, 박리를 거친 후 게이트전극(22)을 형성한다. 이 단계에서, 적용하는 금속은 예를 들어, 탄탈(Ta), 탄탈럼 몰리브덴(MoTa), 텅스텐 몰리브덴(MoW), 또는 알루미늄(Al)등일 수 있다.

S1.2. 단계 S1.1을 마친

유리기판(21) 상에 순차적으로 절연막, 비결정질 실리콘막 및 혼합된 비결정질 실리콘막을 침전하고, 활성층 포토 마스크를 이용하여 노출, 현상 및 제1차 건식 식각, 박리를 거친 후 게이트 전극 절연층(23) 및 비결정질 실리콘층(24)과 오믹접촉층(25, 혼합된 비결정질 실리콘 박막)으로부터 조성되는 활성층을 형성한다. 이 단계에서, 절연막은 예를 들어, SiNx또는 SiOx 단층막이거나, 또는 SiNx과SiOx으로 형성되는 복합막일 수 있다. 비결정질 실리콘 박막은 예를 들어, a-Si일 수 있다. 혼합된 비결정질 실리콘 박막은 예를 들어 n+a-Si일 수 있다.

S1.3. 단계 S1.2를 마친 유리기판(21) 상에 소스/드레인 전극 금속막을 침전하고, 소스/드레인 포토 마스크를 이용하여 노출, 현상 및 제2차 습식 식각, 제2차 건식 식각, 박리를 거친 후 소스전극과 드레인전극(금속층, 26)을 형성한다. 이 단계에서, 사용되는 금속은 예를 들어, 몰리브덴(Mo)이거나 알루미늄(Al) 등일 수 있다.

S1.4. 단계 S1.3를 마친 유리기판(21) 상에 완화층(29)을 침전하고, 완화층 비아 홀 포토 마스크를 이용하여 노출, 현상 및 제3차 건식 식각, 박리를 거친 후 드레인 전극의 상방향 및 완화층(29) 상에 위치하는 완화층 비아 홀(28)을 형성한다.

*단계 S1.1은 다음 단계들을 포함할 수 있다.

S1.11. 세정된 유리기판(21) 상에 게이트전극 금속막을 침전하고, 게이트전극 금속막 상에 포토 레지스트를 도포한다.

S1.12. 게이트 포토마스크를 이용하여 단계 a11)에서 게이트전극 금속막 상에 도포된 포토 레지스트를 노출한다. 이 단계에서, 자외선을 이용하여 게이트 포토 레지스트를 통과한 후 도포된 포토 레지스트에 자외선을 조사할 수 있다. 포토 레지스트는 자외선(ultra violet-ray,UV)에 대해 감광할 수 있다. 자외선에 의해 조사됨으로써 중성에서 산성으로 바뀔 수 있고, 자외선을 받지 않은 경우 중성을 유지한다.

S1.13. 충분히 노출된 포토 레지스트(즉, 단계 S1.12에서 중성으로부터 산성으로 변한 포토 레지스트)를 제거하기 위해, 단계 S1.12에서의 노출된 포토 레지스트에 대해 현상을 진행한다. 예를 들어 염기성 영상액을 이용하여 충분히 노출된 포토 레지스트를 제거한다. 또한, 게이트 전극(22)을 형성한 게이트전극 금속막 이외의 다른 게이트 전극 금속막을 노출한다.

S1.14. 불필요한 게이트 전극 금속막(즉, 단계 S1.13에서 노출된 게이트 전극 금속막)을 제거하기 위해, 제1차 습식 식각으로 불필요한 게이트 전극 금속막을 제거할 수 있다.

S1.15. 최종적인 게이트 전극(22)을 얻기 위해, 단계 S1.12에서 자외선에 의해 조사되지 않은 포토 레지스트를 박리하여 제거한다.

단계 S1.2는 다음 단계들을 포함할 수 있다.

S1.21. 단계 S1.1을 마친 유리기판(21) 상에 순차적으로 절연막, 비결정질 실리콘 박막 및 혼합된 비결정질 실리콘 박막을 침전하고, 혼합된 비결정질 실리콘 박막 상에 포토 레지스트를 도포한다.

S1.22. 활성층 포토 마스크를 이용하여 단계 S1.21에서 비결정질 실리콘 박막 상에 도포된 포토 레지스트를 노출한다. 이 단계에서, 활성층 포토 마스트를 통과한 후 도포된 포토 레지스트에 자외선을 조사할 수 있다. 포토 레지스트는 자외선(ultra violet-ray,UV)에 대해 감광할 수 있다. 자외선에 의해 조사됨으로써 중성에서 산성으로 바뀔 수 있고, 자외선을 받지 않은 경우 중성을 유지한다.

S1.23. 충분히 노출된 포토 레지스트(즉, 단계 S1.22에서 중성으로부터 산성으로 변한 포토 레지스트)를 제거하기 위해, 단계 S1.22에서의 노출된 포토 레지스트에 대해 현상을 진행한다. 예를 들어 염기성 영상액을 이용하여 충분히 노출된 포토 레지스트를 제거한다. 또한, 픽셀 영역의 혼합된 비결정질 실리콘 박막을 노출한다.

S1.24. 불필요한 비결정질 실리콘 박막과 혼합된 비결정질 실리콘 박막(즉, 단계 S1.23에서 노출된 혼합된 비결정질 실리콘 박막 및 그 아래의 비결정질 실리콘 박막)을 제거하기 위해, 제1차 건식 식각으로 불필요한 비결정질 실리콘 박막과 혼합된 비결정질 실리콘 박막을 제거할 수 있다.

S1.25. 최종적인 게이트 전극 절연층(23)과 비결정질 실리콘층(24)과 오믹접촉층(혼합된 비결정질 실리콘 박막, 25)으로 조성된 활성층을 얻기 위해, 단계 S1.22에서 자외선에 의해 조사되지 않은 포토 레지스트를 박리하여 제거한다.

단계 S1.2가 포함하는 단계로부터 알 수 있듯이, 단계 S1.2 이후에, 픽셀 영역 안에서, 유리 기판(21)상에서만 게이트 전극 절연층(23)을 형성할 수도 있다.

단계 S1.3은 다음 단계들을 포함할 수 있다.

*S1.31. 단계 S1.2를 마친 유리기판(21) 상에 소스/드레인 전극 금속막을 침전하고, 소스/드레인 전극 금속막 상에 포토 레지스트를 도포한다.

S1.32. 소스/드레인 전극 포토마스크를 이용하여 단계 S1.31에서 소스/드레인 전극 금속막 상에 도포된 포토 레지스트를 노출한다. 이 단계에서, 자외선을 이용하여 소스/드레인 전극 포토마스크를 통과한 후 도포된 포토 레지스트에 자외선을 조사할 수 있다. 포토 레지스트는 자외선(ultra violet-ray,UV)에 대해 감광할 수 있다. 자외선에 의해 조사됨으로써 중성에서 산성으로 바뀔 수 있고, 자외선을 받지 않은 경우 중성을 유지한다. 이 단계에서, 최종적으로 형성되는 TFT의 채널(30)의 윗 방향의 포토 레지스트가 조사되고, 또한 픽셀 영역의 포토 레지스트도 조사되며, 그 나머지 영역의 포토 레지스트는 모두 조사되지 않는다.

S1.33. 충분히 노출된 포토 레지스트(즉, 단계 S1.32에서 중성으로부터 산성으로 변한 포토 레지스트)를 제거하기 위해, 단계 S1.32에서의 노출된 포토 레지스트에 대해 현상을 진행한다. 예를 들어 염기성 영상액을 이용하여 충분히 노출된 포토 레지스트를 제거한다. 또한, 최종적으로 형성되는 TFT의 채널(30)의 윗 방향의 소스/드레인 전극 금속막 및 픽셀 영역의 소스/드레인 전극 금속막을 노출시킨다.

S1.34. 불필요한 소스/드레인 전극 금속막(즉, 단계 S1.33에서 노출된 소스/드레인 전극 금속막)을 제거하기 위해, 제2차 습식 식각으로 불필요한 소스/드레인 전극 금속막을 제거할 수 있다.

S1.35. 최종적을 형성되는 TFT의 채널(30)을 활성층에 침투시키기 위해, 제2차 건식 식각으로 채널(30) 내의 혼합된 비결정질 실리콘 박막 및 그 아래 방향의 비결정질 실리콘 박막의 일부분을 제거할 수 있다.

S1.36. 최종적인 소스 전극(금속층, 26a)과 드레인 전극(금속층, 26b)를 얻기 위해, 단계 S1.32에서 자외선에 조사되지 않은 포토 레지스트를 박리하여 제거한다.

단계 S1.4는 다음 단계들을 포함할 수 있다.

S1.41. 단계 S1.3를 마친 유리기판(21) 상에 완화층 박막을 침전하고, 완화층 박막 상에 포토 레지스트를 도포한다.

S1.42. 완화층 비아 홀 포토마스크를 이용하여 단계 S1.41에서 완화층 박막 상에 도포된 포토 레지스트를 노출한다. 이 단계에서, 자외선을 이용하여 소스/드레인 전극 포토마스크를 통과한 후 도포된 포토 레지스트에 자외선을 조사할 수 있다. 포토 레지스트는 자외선(ultra violet-ray,UV)에 대해 감광할 수 있다. 자외선에 의해 조사됨으로써 중성에서 산성으로 바뀔 수 있고, 자외선을 받지 않은 경우 중성을 유지한다. 이 실시예에서, 최종적으로 형성되는 완화층 비아 홀(28)의 위치에 있는 포토 레지스트가 조사되고, 그 나머지 영역은 모두 조사되지 않는다.

S1.43. 충분히 노출된 포토 레지스트(즉, 단계 S1.42에서 중성으로부터 산성으로 변한 포토 레지스트)를 제거하기 위해, 단계 S1.42에서의 노출된 포토 레지스트에 대해 현상을 진행한다. 예를 들어 염기성 영상액을 이용하여 충분히 노출된 포토 레지스트를 제거한다. 또한, 최종적으로 형성되는 완화층 비아 홀(28)의 위치에 있는 완화층 박막을 노출시킨다.

S1.44. 불필요한 완화층 박막(즉, 단계 S1.43에서 노출된 완화층 박막)을 제거하기 위해, 제3차 건식 식각으로 불필요한 완화층 박막을 제거할 수 있다.

S1.45. 단계 S1.42에서 자외선에 조사되지 않은 포토 레지스트를 박리 제거하여 최종적으로 완화층 비아 홀(28)을 형성한다.

단계 S1.4가 포함하는 단계로부터 알 수 있듯이, 단계 S1.4를 마친 후, 픽셀 구역의 유리기판(21) 상에 게이트 전극 절연층(23)과 완화층(29)를 형성하고, 상술한 단계 S2로부터 단계 S7까지를 통해 알 수 있듯이, 유리기판(21) 상에 게이트 전극 절연층(23), 완화층(29) 및 ITO 전극(27)을 형성한다.

본 발명의 다른 실시예로서, 상술한 실시예와 다르게, 상술한 실시예의 단계 S1이 포함하는 단계 S1.2와 단계 S1.3을 하나의 단계로 실시할 수 있으며, 구체적으로 아래와 같다.

단계 S1은 다음 단계들을 포함한다.

S2.1. 유리기판(21) 상에 게이트 전극 박막을 침전하고, 게이트 포토 마스크를 이용하여 노출, 현상 및 제1차 습식 식각, 박리 후 게이트 전극(22)를 형성한다.

S2.2. 단계 S2.1을 마친 유리기판(21) 상에 순차적으로 절연막, 비결정질 실리콘 박막, 혼합된 비결정질 실리콘 박막 및 소스/드레인 전극 금속막을 침전하고, SSM 포토 마스크를 이용하여 노출, 현상 및 두 차례 건식 식각, 두 차례 습식 식각, 박리 이후에 게이트 전극 절연층(23), 비결정질 실리콘층(24)와 오믹접촉층(혼합된 비결정질 실리콘 박막, 25)으로 조성된 활성층, 소스 전극(금속층, 26a) 및 드레인 전극(금속층, 26b)를 형성한다.

S2.3. 단계 S2.2를 마친 유리기판(21) 상에 완화층(29)를 침전하고, 완화층 비아 홀 포토 마스크를 이용하여 노출, 현상 및 제3차 건식 식각, 박리 후, 드레인 전극(26b)의 윗방향 및 완화층(29)상의 완화층 비아 홀(28)을 형성한다.

단계 S2.2는 다음 단계들을 포함할 수 있다.

S2.21. 단계 S2.1을 마친 유리기판(21) 상에 순차적으로 절연막, 비결정질 실리콘 박막, 혼합된 비결정질 실리콘 박막 및 소스/드레인 전극 금속막을 침전하고, 소스/드레인 전극 금속막에 포토 레지스트를 도포한다.

S2.22. SSM 포토 마스크를 이용하여 단계 S2.21에서 소스/드레인 전극 금속막에 도포된 포토 레지스트를 노출시킨다. 이 단계에서, 자외선을 이용하여 소스/드레인 전극 포토마스크를 통과한 후 도포된 포토 레지스트에 자외선을 조사할 수 있다. 포토 레지스트는 자외선(ultra violet-ray,UV)에 대해 감광할 수 있다. 자외선에 의해 조사됨으로써 중성에서 산성으로 바뀔 수 있고, 자외선을 받지 않은 경우 중성을 유지한다. 자외선의 간섭 및 회절 효과를 통해, SSM 포토 마스크상에 반투명한 패턴 영역이 형성된다. 노출 과정에서, 자외선은 부분적으로 반투명 영역을 통과할 뿐이다. 노출량을 제어함으로써 포토 레지스트층이 부분적으로 노출되도록 할 수 있으며, 다른 부분은 충분히 노출시킬 수 있다. 현상 후에, 완전이 노출된 영역은 포토 레지스트가 없으며, 충분하게 노출되지 않은 부분의 포토 레지스트의 두께는 완전이 노출되지 않은 영역의 포토 레지스트의 두께보다 작다. 이 단계에서, 최종적으로 형성되는 TFT의 채널(30)의 윗 방향에는 포토 레지스트가 완전히 조사되지 않고, 충분히 노출되지 않으며, 최종적으로 형성되는 TFT의 다른 부분의 포토 레지스트는 조사되지 않고, 픽셀 영역의 포토 레지스트는 완전히 조사된다.

S2.23. 노출된 포토 레지스트(즉, 단계 S2.22에서 중성으로부터 산성으로 변한 포토 레지스트)를 제거하기 위해, 단계 S2.22에서 노출된 포토 레지스트에 대해 현상을 진행한다. 예를 들어 염기성 영상액을 이용하여 노출된 포토 레지스트를 제거한다. 여기에서, 충분히 공개되지 않은 포토 레지스트는 일부분(즉, TFT 영역은 포토 레지스트에 의해 완전히 덮이고, 충분히 노출되지 않은 영역의 포토 레지스트의 두께는 노출되지 않은 영역의 포토 레지스트의 두께보다 작다)을 제거하고, 픽셀 영역의 소스/드레인 전극 금속막은 노출된다.

S2.24. 불필요한 소스/드레인 전극 금속막(즉, 단계 S2.23에서 노출된 소스/드레인 전극 금속막)을 제거하기 위해, 제2차 습식 식각으로 불필요한 소스/드레인 전극 금속막을 제거할 수 있다.

S2.25. 단계 S2.24를 마친 다음, 제1차 건식 식각을 통해 단계 S2.23에서 충분히 노출되지 않은 포토 레지스트를 제거하여, 이 충분하게 노출되지 않은 포토 레지스트가 덮은 소스/드레인 전극 금속막을 노출시킨다.

S2.26. 단계 S2.25를 마친 다음, 제3차 습식 식각을 통해 단계 S2.25에서 노출된 소스/드레인 전극 금속막을 제거하여, 이 노출된 소스/드레인 전극 금속막이 덮은 혼합된 비결정질 실리콘 박막을 노출시킨다.

*S2.27. 단계 S2.26을 마친 다음, 제2차 건식 식각을 통해 단계 S2.26에서 노출된 혼합된 비결정질 실리콘 박막을 제거하고, 이 노출된 혼합된 비결정질 실리콘 박막이 덮은 비결정질 실리콘 박막의 일부분을 제거하여, TFT의 채널(30)을 형성한다.

S2.28. 단계 S2.22에서 자외선에 조사되지 않은 포토 레지스트를 박리 제거하여, 게이트 전극 절연층(23), 비결정질 실리콘층(24)과 오믹접촉층(혼합된 비결정질 실리콘 박막, 25)으로 조성된 활성층 및 소스 전극(26a)와 드레인 전극(26b)를 형성한다.

상술한 실시예의 TFT-LCD 디스플레이 기판의 제조 방법으로 제거된 TFT-LCD 디스플레이 기판은 보통 액정 디스플레이 장치에 적용되는데, 구체적으로 도 5에서 도시한다.

도 5는 본 발명의 일 실시예에 따라 도 1이 도시하는 TFT-LCD 디스플레이 기판의 액정 디스플레이 장치의 구조를 나타내는 개략도이다.

도 5를 참조하면, 본 발명의 실시예에 따른 액정 디스플레이 장치는 액정 패널(41) 및 상기 액정 패널(41)과 대향하여 설치되는 백라이트 모듈(42)을 포함하되, 상기 백라이트 모듈(42)이 디스플레이 광원을 상기 액정 패널(41)에 제공하여 상기 액정 패널(41)이 백라이트 모듈(42)로부터 제공된 광으로 형상을 디스플레이하게 한다. 또한, 액정 패널(41)은 다음과 같이 구성된다: 상술한 실시예의 TFT-LCD 디스플레이 기판의 제조 방법으로 제조된 TFT-LCD 디스플레이 기판인 제1 기판(411), 여광판 기판인 제2 기판(412), 제1 기판(411)과 제2기판(412) 사이에 설치되는 액정층(413)으로 구성되되, 제1 기판(411)과 제2기판(412)은 서로 대향하여 설치된다.

제1 기판(411)과 대향하여 설치된 제2기판(412)는 CF(Color Filter)이라고 칭하기도 하는데, 통상적으로 투명 기판(예를 들어 유리기판) 및 투명 기판 상에 설치된 흑색 행렬 패턴, 색채 포토 레지스트 층(예를 들어, 적(R), 녹(G)그리고 청(B)광필터 패턴) 및 배향층 등을 포함한다. 본 발명에서 채용하는 제2기판(412)과 종래의 액정 패널에서의 여광판 기판이 서로 동일하다는 점을 고려하면, 그 구체적인 구조는 관련된 종래 기술을 참고할 수 있으며, 여기에서는 설명을 생략한다. 또한, 본 실시예에서 백라이트 모듈(42)도 종래의 액정 디스플레이 장치에서의 백라이트 모듈과 서로 동일하므로, 그 구체적인 구조는 관련된 종래 기술을 참고하도록 하고, 여기에서는 설명을 생략한다.

이상에서 설명한 실시예는 단지 본 발명에서 기재하는 일 실시예일 뿐으로서, 본 발명의 실시예를 토대로, 본 기술 영역의 통상의 기술자가 창조적인 노력을 들이지 않는 범위 안에서 얻을 수 있는 다른 실시예들도 본 발명의 권리범위에 속하는 것으로 보아야 한다.

Claims (13)

- a) 유리 기판상에 게이트전극, 게이트전극 절연층, 비결정질 실리콘층과 오믹접촉층으로부터 조성되는 활성층, 상기 활성층 상의 소스전극과 드레인전극, 완화층 및 상기 드레인전극의 상방향에 위치한 완화층 상에 비아 홀을 형성하는 단계;

b) 단계 a)를 마친 유리 기판 상에 전도성 박막을 침전하고, 전도성 박막상에 포토 레지스트를 도포하는 단계;

c) ITO(Indium Tin Oxide) 포토 마스크 및 자외선을 이용하여 전도성 박막 상에 포토 레지스트를 노출 - 완화층 비아 홀 및 상기 완화층 비아 홀 근처에 도포된 포토 레지스트는 노출되지 않고, 그 외 다른 영역에 도포된 포토 레지스트는 완전히 노출되고, 도전성 전극에 도포된 포토 레지스트는 노출되지 않고, 도전성 전극 패턴의 간격에 도포된 포토 레지스트는 부분적으로 노출되고, 상기 ITO 포토 마스크는 SSM(single slit mask) 포토 마스크 또는 그레이 톤 마스크(gray tone mask) 중 어느 하나임 - 하는 단계;

d) TFT 영역의 완화층 비아 홀 외부의 포토 레지스트를 제거하고, 픽셀 영역이 간격 부분을 형성하는 구간의 일부 포토 레지스트를 제거하고, TFT 영역의 완화층 비아 홀 이외의 전도 박막을 노출시키는 단계;

e) 제4차 건식 식각을 통해 단계 d)에서의 픽셀 영역이 간격을 형성하는 구간 이외의 잔여 포토 레지스트를 제거하고, 상기 픽셀 영역의 간격 부분을 형성하려 하는 전도성 박막을 노출시키는 단계;

f) 습식 식각을 통해 픽셀 영역이 형성하는 도전성 전극 패턴 중의 간격의 거리가 1.9 ㎛ 이하가 되도록 단계 d)와 단계 e)에서 노출된 도전성 박막을 제거하는 단계;

g) 제거되지 않은 포토 레지스트를 박리시켜, 도전성 전극을 형성하고, 도전성 전극과 완화층 비아 홀을 연결하는 단계; 를 포함하는, TFT-LCD 디스플레이 기판의 제조방법. - 제1항에 있어서,

상기 단계 a)는,

a1) 유리 기판상에 게이트전극 금속막을 침전하고, 노출, 현상 및 제1차 습식 식각, 박리를 거친 후 게이트전극을 형성하는 단계;

a2) 단계 a1)을 마친 유리기판 상에 연속해서 절연막, 비결정질 실리콘막 및 혼합된 비결정질 실리콘막을 침전하고, 노출, 현상 및 제1차 건식 식각, 박리를 거친 후 게이트 전극 절연층 및 비결정질 실리콘층과 오믹접촉층으로부터 조성되는 활성층을 형성하는 단계;

a3) 단계 a2)를 마친 유리기판 상에 소스/드레인 전극 금속막을 침전하고, 노출, 현상 및 제2차 습식 식각, 제2차 건식 식각, 박리를 거친 후 소스전극과 드레인전극을 형성하는 단계;

a4) 단계 a3)를 마친 유리기판 상에 완화층을 침전하고, 노출, 현상 및 제3차 건식 식각, 박리를 거친 후 드레인 전극의 상방향에 위치하는 완화층 비아 홀을 형성하는 단계; 를 포함하는, TFT-LCD 디스플레이 기판의 제조방법. - 제1항에 있어서,

상기 단계 a)는,

a1) 유리 기판상에 게이트전극 금속막을 침전하고, 노출, 현상 및 제1차 습식 식각, 박리를 거친 후 게이트전극을 형성하는 단계;

a2) 단계 a1)을 마친 유리기판 상에 연속해서 절연막, 비결정질 실리콘막, 혼합된 비결정질 실리콘막 및 소스/드레인 전극 금속막을 침전하고, 노출, 현상 및 제2차 습식 식각, 제1차 건식 식각, 제3차 습식 식각, 제2차 건식 식각, 박리를 거친 후 게이트전극 절연층, 비결정질 실리콘층과 오믹접촉층으로 조성되는 활성층 및 소스전극과 드레인전극을 형성하는 단계;

a3) 단계 a2)를 마친 후의 유리기판 상에 완화층을 침전하고, 노출, 현상 및 제3차 건식 식각, 박리를 거친 후 드레인 전극 상방향에 위치하는 완화층 비아 홀을 형성하는 단계; 를 포함하는, TFT-LCD 디스플레이 기판의 제조방법. - 제2항에 있어서,

상기 단계 a1)은,

a11) 세정된 유리기판 상에 게이트전극 금속막을 침전하고, 게이트전극 금속막 상에 포토 레지스트를 도포하는 단계;

a12) 단계 a11)에서 게이트전극 금속막 상에 도포된 포토 레지스트에 대해, 노출, 현상을 진행한 후, 게이트 전극이 형성되는 부분 이외의 게이트 전극 금속막을 노출하는 단계;

a13) 제1차 습식 식각을 통해 단계 a12)에서 노출된 게이트 전극 금속막을 제거하는 단계;

a14) 게이트 전극을 형성한 부분의 포토 레지스트를 박리하여, 게이트 전극을 형성하는 단계;를 포함하는, TFT-LCD 디스플레이 기판의 제조방법. - 제3항에 있어서,

상기 단계 a1)은,

a11) 세정된 유리기판 상에 게이트전극 금속막을 침전하고, 게이트 전극 금속막 상에 포토 레지스트를 도포하는 단계;

a12) 단계 a11)에서 게이트전극 금속막 상에 도포된 포토 레지스트에 대해, 노출, 현상을 진행한 후, 게이트 전극이 형성되는 부분 이외의 게이트 전극 금속막을 노출하는 단계;

a13) 제1차 습식 식각을 통해 단계 a12)에서 노출된 게이트 전극 금속막을 제거하는 단계;

a14) 게이트 전극을 형성한 부분의 포토 레지스트를 박리하여, 게이트 전극을 형성하는 단계;를 포함하는, TFT-LCD 디스플레이 기판의 제조방법. - 제2항에 있어서,

상기 단계 a2)는,

a21)단계 a1)을 마친 유리기판 상에 연속해서 절연막, 비결정질 실리콘 박막 및 혼합된 비결정질 실리콘 박막을 침전하고, 혼합된 비결정질 실리콘 박막 상에 포토 레지스트를 도포하는 단계;

a22) 단계 a21)에서 혼합된 비결정질 실리콘 박막 상에 도포된 포토 레지스트에 대해 노출, 현상을 진행한 후, 픽셀 영역의 혼합된 비결정질 실리콘 박막을 노출하는 단계;

a23)제1차 건식 식각을 통해 픽셀 영역이 노출된 혼합된 비결정질 실리콘 박막 및 그 아래 방향의 비결정질 실리콘 박막을 제거하는 단계;

a24)TFT 영역의 포토 레지스트를 박리하고, 게이트 전극 절연층 및 비결정질 실리콘층과 오믹접촉층으로 조성된 활성층을 형성하는 단계;를 포함하는, TFT-LCD 디스플레이 기판의 제조방법. - 제2항에 있어서,

상기 단계 a3)은,

a31)단계 a2)를 마친 유리기판 상에 소스/드레인 전극 금속막을 침전하고, 소스/드레인 전극 금속막 상에 포토 레지스트를 도포하는 단계;

a32)단계 a31)에서 소스/드레인 전극 금속막 상에 도포된 포토 레지스트를 노출, 현상한 다음, 채널을 형성하려 하는 소스/드레인 전극 금속막과 픽셀 영역의 소스/드레인 전극 금속막을 노출하는 단계;

a33)제2차 습식 식각을 통해 단계 a32)에서 노출한 소스/드레인 전극 금속막을 제거하는 단계;

a34)제2차 건식 식각을 통해 형성된 채널 안의 혼합된 비결정질 실리콘 박막 및 그 아래 방향의 비결정질 실리콘 박막의 일부분을 제거하여, 형성된 채널이 비결정질 실리콘층으로 침투하도록 하는 단계;

a35)TFT 영역에서의 채널 부분 이외의 포토 레지스트를 박리하여 제거하고, 소스 전극과 드레인 전극을 형성하는 단계;를 포함하는, TFT-LCD 디스플레이 기판의 제조방법. - 제6항에 있어서,

상기 단계 a3)은,

a31)단계 a2)를 마친 유리기판 상에 소스/드레인 전극 금속막을 침전하고, 소스/드레인 전극 금속막 상에 포토 레지스트를 도포하는 단계;

a32)단계 a31)에서 소스/드레인 전극 금속막 상에 도포된 포토 레지스트를 노출, 현상한 다음, 채널을 형성하려 하는 소스/드레인 전극 금속막과 픽셀 영역의 소스/드레인 전극 금속막을 노출하는 단계;

a33)제2차 습식 식각을 통해 단계 a32)에서 노출한 소스/드레인 전극 금속막을 제거하는 단계;

a34)제2차 건식 식각을 통해 형성된 채널 안의 혼합된 비결정질 실리콘 박막 및 그 아래 방향의 비결정질 실리콘 박막의 일부분을 제거하여, 형성된 채널이 비결정질 실리콘층으로 침투하도록 하는 단계;

a35)TFT 영역에서의 채널 부분 이외의 포토 레지스트를 박리하여 제거하고, 소스 전극과 드레인 전극을 형성하는 단계;를 포함하는, TFT-LCD 디스플레이 기판의 제조방법. - 제3항에 있어서,

상기 단계 a2)은,

a21)단계 a1)을 마친 유리기판 상에 연속해서 절연막, 비결정질 실리콘막, 혼합된 비결정질 실리콘막 및 소스/드레인 전극 금속막을 침전하고, 소스/드레인 전극 금속막 상에 포토 레지스트를 도포하는 단계;

a22)단계 a21)에서 소스/드레인 전극 금속막 상에 도포된 포토 레지스트를 노출, 현상한 후, 채널을 형성하려 하는 부분의 일부 포토 레지스터를 제거하고, 픽셀 영역의 포토 레지스트를 전부 제거하여, 픽셀 영역의 소스/드레인 전극 금속막을 노출하는 단계;

a23)제2차 습식 식각으로 단계 a22)에서 노출한 소스/드레인 전극 금속막을 노출하는 단계;

a24)제1차 건식 식각으로 단계 a22)에서 채널을 형성하려 하는 부분 이외의 포토 레지스트를 제거하여, 채널을 형성하려 하는 부분의 소스/드레인 전극 금속막을 노출하는 단계;

a25)제3차 습식 식각으로 단계 a24)에서 노출된 소스/드레인 전극 금속막을 제거하여 채널을 형성하려 하는 부분의 혼합된 비결정질 실리콘 박막을 노출하는 단계;

a26)제2차 건식 식각으로 단계 a25)에서 노출한 혼합된 비결정질 실리콘 박막 및 그 아래 방향의 일부 비결정질 실리콘 박막을 제거하여, 형성하려 하는 채널을 비결정질 실리콘층에 침투시키는 단계;

a27)TFT 영역에서 채널을 형성하려 하는 부분 이외의 포토 레지스트를 박리하여 제거하고, 게이트 전극 절연층, 비결정질 실리콘층과 오믹접촉층으로 조성되는 활성층 및 소스 전극과 드레인 전극을 형성하는 단계;를 포함하는, TFT-LCD 디스플레이 기판의 제조방법. - 제2항에 있어서,

상기 단계 a4)는,

a41)단계 a3)를 마친 유리기판 상에 완화층 박막을 침전하고, 완화층 박막 상에 포토 레지스트를 도포하는 단계;

a42)단계 a41)에서 완화층 박막 상에 도포된 포토 레지스트를 노출, 현상한 후, 완화층 비아 홀 부분을 형성하려 하는 완화층 박막을 노출하는 단계;

a43)제3차 건식 식각으로 단계 a42)에서 노출한 완화층 박막을 제거하는 단계;

a44)완화층 비아 홀을 형성하려 하는 부분 이외의 포토 레지스트를 박리하여 제거하고, 완화층 비아 홀을 형성하는 단계;를 포함하는, TFT-LCD 디스플레이 기판의 제조방법. - 제2항에 있어서,

상기 단계 a4)는,

a41)단계 a3)를 마친 유리기판 상에 완화층 박막을 침전하고, 완화층 박막 상에 포토 레지스트를 도포하는 단계;

a42)단계 a41)에서 완화층 박막 상에 도포된 포토 레지스트를 노출, 현상한 후, 완화층 비아 홀 부분을 형성하려 하는 완화층 박막을 노출하는 단계;

a43)제3차 건식 식각으로 단계 a42)에서 노출한 완화층 박막을 제거하는 단계;

a44)완화층 비아 홀을 형성하려 하는 부분 이외의 포토 레지스트를 박리하여 제거하고, 완화층 비아 홀을 형성하는 단계;를 포함하는, TFT-LCD 디스플레이 기판의 제조방법. - TFT-LCD 디스플레이 기판, 상기 TFT-LCD 디스플레이 기판에 대향하여 설치되는 여광판 기판 및 상기 TFT-LCD 디스플레이 기판과 상기 여광판 기판 사이에 설치되는 액정층을 포함하고,

상기 TFT-LCD 디스플레이 기판은 청구항 제1항의 제조방법으로 제조되는 TFT-LCD 디스플레이 기판인, 액정 패널. - 액정 패널 및 상기 액정 패널과 대향하여 설치되는 백라이트 모듈을 포함하되,

상기 백라이트 모듈이 디스플레이 광원을 상기 액정 패널에 제공하여 상기 액정 패널이 형상을 디스플레이하게 하되,

상기 액정 패널은 청구항 제12항에서 한정하는 액정패널인, 액정 디스플레이 장치.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201310439974.5 | 2013-09-24 | ||

| CN201310439974.5A CN103474396B (zh) | 2013-09-24 | 2013-09-24 | Tft-lcd阵列基板的制造方法 |

| PCT/CN2013/085597 WO2015043023A1 (zh) | 2013-09-24 | 2013-10-21 | Tft-lcd阵列基板的制造方法、液晶面板及液晶显示器 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020167001034A Division KR20160020525A (ko) | 2013-09-24 | 2013-10-21 | Tft-lcd 디스플레이 기판의 제조방법, 액정 패널 및 액정 디스플레이 장치 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20170124624A true KR20170124624A (ko) | 2017-11-10 |

| KR101880875B1 KR101880875B1 (ko) | 2018-07-20 |

Family

ID=49799194

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020177031321A KR101880875B1 (ko) | 2013-09-24 | 2013-10-21 | Tft-lcd 디스플레이 기판의 제조방법, 액정 패널 및 액정 디스플레이 장치 |

| KR1020167001034A KR20160020525A (ko) | 2013-09-24 | 2013-10-21 | Tft-lcd 디스플레이 기판의 제조방법, 액정 패널 및 액정 디스플레이 장치 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020167001034A KR20160020525A (ko) | 2013-09-24 | 2013-10-21 | Tft-lcd 디스플레이 기판의 제조방법, 액정 패널 및 액정 디스플레이 장치 |

Country Status (6)

| Country | Link |

|---|---|

| JP (1) | JP6293905B2 (ko) |

| KR (2) | KR101880875B1 (ko) |

| CN (1) | CN103474396B (ko) |

| GB (1) | GB2531203B (ko) |

| RU (1) | RU2623187C1 (ko) |

| WO (1) | WO2015043023A1 (ko) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103761935B (zh) | 2014-01-21 | 2016-01-06 | 深圳市华星光电技术有限公司 | 显示面板 |

| CN109639856B (zh) * | 2018-11-23 | 2021-03-16 | 维沃移动通信有限公司 | 一种显示屏及终端设备 |

| CN109786321B (zh) * | 2018-12-25 | 2022-07-22 | 惠科股份有限公司 | 阵列基板的制备方法、装置及显示面板 |

| CN109920729B (zh) * | 2019-03-27 | 2022-12-02 | 合肥鑫晟光电科技有限公司 | 一种显示基板的制备方法、显示装置 |

| CN113436548B (zh) * | 2021-06-23 | 2024-01-30 | 南方科技大学 | 一种黑色矩阵的制备方法 |

| CN113772963B (zh) * | 2021-09-13 | 2023-07-07 | 芜湖长信科技股份有限公司 | 一种双面线路触摸屏结构及其制备方法 |

| CN114967212B (zh) * | 2022-05-24 | 2024-03-19 | 苏州华星光电技术有限公司 | 彩膜基板及液晶显示面板 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5966589A (en) * | 1996-12-18 | 1999-10-12 | Nec Corporation | Method of fabricating thin film transistor array |

| US20010040648A1 (en) * | 2000-05-12 | 2001-11-15 | Hitachi Ltd. | Liquid crystal display device and fabrication method thereof |

| US20050142714A1 (en) * | 2003-12-27 | 2005-06-30 | Lg.Philips Lcd Co., Ltd. | Method of fabricating thin film transistor array substrate |

| KR20100065700A (ko) * | 2008-12-08 | 2010-06-17 | 엘지디스플레이 주식회사 | 액정표시장치용 박막트랜지스터의 제조방법 |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3152193B2 (ja) * | 1996-12-18 | 2001-04-03 | 日本電気株式会社 | 薄膜トランジスタアレイ基板およびその製造方法 |

| JP3436487B2 (ja) * | 1998-05-18 | 2003-08-11 | シャープ株式会社 | アクティブマトリクス基板の製造方法 |

| JP2001339072A (ja) * | 2000-03-15 | 2001-12-07 | Advanced Display Inc | 液晶表示装置 |

| JP2005062802A (ja) * | 2003-07-28 | 2005-03-10 | Advanced Display Inc | 薄膜トランジスタアレイ基板の製法 |

| KR101167304B1 (ko) * | 2004-12-31 | 2012-07-19 | 엘지디스플레이 주식회사 | 프린지 필드 스위칭 타입의 박막 트랜지스터 기판 및 그제조 방법 |

| KR100957614B1 (ko) * | 2005-10-17 | 2010-05-13 | 엘지디스플레이 주식회사 | 액정표시장치용 어레이 기판 및 그 제조 방법 |

| KR100792300B1 (ko) * | 2005-11-11 | 2008-01-07 | 비오이 하이디스 테크놀로지 주식회사 | 반투과형 액정표시장치의 어레이기판 제조방법 |

| KR100818887B1 (ko) * | 2005-12-14 | 2008-04-02 | 엘지.필립스 엘시디 주식회사 | 액정 표시장치 및 그 제조 방법 |

| CN100517075C (zh) * | 2006-03-09 | 2009-07-22 | 北京京东方光电科技有限公司 | 一种薄膜晶体管液晶显示器的阵列基板的制作方法 |

| JP5477523B2 (ja) * | 2006-06-15 | 2014-04-23 | 三国電子有限会社 | 低コスト大画面広視野角高速応答液晶表示装置 |

| CN100442132C (zh) * | 2006-11-17 | 2008-12-10 | 北京京东方光电科技有限公司 | 一种tft lcd阵列基板结构及其制造方法 |

| KR20090027920A (ko) * | 2007-09-13 | 2009-03-18 | 삼성전자주식회사 | 표시 기판 및 이를 구비한 표시 패널 |

| CN101290446B (zh) * | 2008-05-16 | 2011-10-05 | 京东方科技集团股份有限公司 | Tft-lcd阵列基板及其制造方法 |

| JP5571887B2 (ja) * | 2008-08-19 | 2014-08-13 | アルティアム サービシズ リミテッド エルエルシー | 液晶表示装置及びその製造方法 |

| JP5553513B2 (ja) * | 2009-02-09 | 2014-07-16 | 株式会社ジャパンディスプレイ | 液晶表示装置及びその製造方法 |

| CN101887897B (zh) * | 2009-05-13 | 2013-02-13 | 北京京东方光电科技有限公司 | Tft-lcd阵列基板及其制造方法 |

| JP5409238B2 (ja) * | 2009-09-29 | 2014-02-05 | Hoya株式会社 | フォトマスク、フォトマスクの製造方法、パターン転写方法及び表示装置用画素電極の製造方法 |

| CN102237305B (zh) * | 2010-05-06 | 2013-10-16 | 北京京东方光电科技有限公司 | 阵列基板及其制造方法和液晶显示器 |

| KR101298612B1 (ko) * | 2010-10-12 | 2013-08-26 | 엘지디스플레이 주식회사 | 횡전계 방식 액정표시장치용 어레이기판 및 그 제조방법 |

| CN102456619B (zh) * | 2010-10-22 | 2014-01-15 | 京东方科技集团股份有限公司 | 阵列基板及其制造方法和液晶显示器 |

| KR101529557B1 (ko) * | 2011-06-09 | 2015-06-19 | 엘지디스플레이 주식회사 | 프린지 필드형 액정표시장치의 제조방법 |

| CN102646630B (zh) * | 2011-10-11 | 2014-04-02 | 京东方科技集团股份有限公司 | 一种制造tft-lcd阵列基板的方法及其产品 |

-

2013

- 2013-09-24 CN CN201310439974.5A patent/CN103474396B/zh active Active

- 2013-10-21 GB GB1600839.3A patent/GB2531203B/en active Active

- 2013-10-21 KR KR1020177031321A patent/KR101880875B1/ko active IP Right Grant

- 2013-10-21 JP JP2016543289A patent/JP6293905B2/ja active Active

- 2013-10-21 WO PCT/CN2013/085597 patent/WO2015043023A1/zh active Application Filing

- 2013-10-21 KR KR1020167001034A patent/KR20160020525A/ko active Search and Examination

- 2013-10-21 RU RU2016110665A patent/RU2623187C1/ru active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5966589A (en) * | 1996-12-18 | 1999-10-12 | Nec Corporation | Method of fabricating thin film transistor array |

| US20010040648A1 (en) * | 2000-05-12 | 2001-11-15 | Hitachi Ltd. | Liquid crystal display device and fabrication method thereof |

| US20050142714A1 (en) * | 2003-12-27 | 2005-06-30 | Lg.Philips Lcd Co., Ltd. | Method of fabricating thin film transistor array substrate |

| KR20100065700A (ko) * | 2008-12-08 | 2010-06-17 | 엘지디스플레이 주식회사 | 액정표시장치용 박막트랜지스터의 제조방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR101880875B1 (ko) | 2018-07-20 |

| CN103474396B (zh) | 2015-09-02 |

| GB2531203B (en) | 2020-11-04 |

| RU2623187C1 (ru) | 2017-06-22 |

| JP2016533530A (ja) | 2016-10-27 |

| GB201600839D0 (en) | 2016-03-02 |

| WO2015043023A1 (zh) | 2015-04-02 |

| GB2531203A (en) | 2016-04-13 |

| JP6293905B2 (ja) | 2018-03-14 |

| KR20160020525A (ko) | 2016-02-23 |

| CN103474396A (zh) | 2013-12-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101880875B1 (ko) | Tft-lcd 디스플레이 기판의 제조방법, 액정 패널 및 액정 디스플레이 장치 | |

| US8735888B2 (en) | TFT-LCD array substrate and manufacturing method thereof | |

| US10473991B2 (en) | Manufacturing method of liquid crystal display panel | |

| US9274368B2 (en) | COA substrate, method for fabricating the same and display device | |

| TWI468822B (zh) | 液晶顯示裝置及其製造方法 | |

| JP2012248865A (ja) | アクティブマトリクス基板及びそれを備えた表示パネル | |

| US9274388B2 (en) | Array substrate having common electrode driving interface pattern with slits, and manufacturing method thereof, and liquid crystal display | |

| WO2018032670A1 (zh) | Tft基板的制作方法 | |

| US7811724B2 (en) | Method for fabricating color filter layer | |

| WO2013143321A1 (zh) | 阵列基板及其制造方法和显示装置 | |

| US8357937B2 (en) | Thin film transistor liquid crystal display device | |

| US9366932B2 (en) | TFT-LCD array substrate manufacturing method and LCD panel/device produced by the same | |

| US8263447B2 (en) | Pixel structure and manufacturing method thereof and display panel | |

| TWI396916B (zh) | 薄膜電晶體陣列基板之製作方法 | |

| WO2018196192A1 (zh) | 阵列基板制程和阵列基板 | |

| US8900938B2 (en) | Manufacturing method of array substrate, array substrate and LCD device | |

| KR101408257B1 (ko) | 액정표시장치 및 그 제조방법 | |

| US9780221B2 (en) | Thin film transistor substrate comprising a photoresist layer formed between a first dielectric layer and an amorphous silicon layer | |

| KR20080057034A (ko) | 액정표시장치 및 그 제조방법 | |

| KR101191450B1 (ko) | 포토 마스크 및 이를 이용한 액정 표시 패널의 제조 방법 | |

| KR20070072204A (ko) | 액정표시소자 및 제조방법 | |

| KR20080056569A (ko) | 액정표시장치 및 그 제조방법 | |

| KR20070068921A (ko) | 액정표시장치의 제조방법 | |

| KR20080060944A (ko) | 액정표시장치 및 그 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A107 | Divisional application of patent | ||

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E90F | Notification of reason for final refusal | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant |