JP7213360B2 - メモリ回路を備えた印刷コンポーネント - Google Patents

メモリ回路を備えた印刷コンポーネント Download PDFInfo

- Publication number

- JP7213360B2 JP7213360B2 JP2021541203A JP2021541203A JP7213360B2 JP 7213360 B2 JP7213360 B2 JP 7213360B2 JP 2021541203 A JP2021541203 A JP 2021541203A JP 2021541203 A JP2021541203 A JP 2021541203A JP 7213360 B2 JP7213360 B2 JP 7213360B2

- Authority

- JP

- Japan

- Prior art keywords

- memory

- analog

- pad

- circuit

- component

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 230000015654 memory Effects 0.000 title claims description 478

- 239000012530 fluid Substances 0.000 claims description 244

- 238000007639 printing Methods 0.000 claims description 92

- 230000004044 response Effects 0.000 claims description 68

- 239000000758 substrate Substances 0.000 claims description 34

- 230000006870 function Effects 0.000 claims description 10

- 238000010586 diagram Methods 0.000 description 29

- 230000033001 locomotion Effects 0.000 description 13

- 238000003491 array Methods 0.000 description 12

- 230000002950 deficient Effects 0.000 description 12

- 238000010304 firing Methods 0.000 description 12

- 238000004891 communication Methods 0.000 description 8

- 230000006399 behavior Effects 0.000 description 5

- 238000004519 manufacturing process Methods 0.000 description 5

- 238000002347 injection Methods 0.000 description 4

- 239000007924 injection Substances 0.000 description 4

- 238000012360 testing method Methods 0.000 description 4

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 3

- 230000004913 activation Effects 0.000 description 3

- 230000007423 decrease Effects 0.000 description 3

- 238000001514 detection method Methods 0.000 description 3

- 229910052710 silicon Inorganic materials 0.000 description 3

- 239000010703 silicon Substances 0.000 description 3

- 230000000712 assembly Effects 0.000 description 2

- 238000000429 assembly Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 238000000034 method Methods 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 238000012546 transfer Methods 0.000 description 2

- 238000010146 3D printing Methods 0.000 description 1

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- 229920002799 BoPET Polymers 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- 239000005041 Mylar™ Substances 0.000 description 1

- 230000006978 adaptation Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 238000009529 body temperature measurement Methods 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 238000007876 drug discovery Methods 0.000 description 1

- 238000001035 drying Methods 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 239000004744 fabric Substances 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 238000013507 mapping Methods 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000005459 micromachining Methods 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 238000013021 overheating Methods 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 239000000843 powder Substances 0.000 description 1

- 230000037452 priming Effects 0.000 description 1

- 238000005086 pumping Methods 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 238000012358 sourcing Methods 0.000 description 1

- 239000013589 supplement Substances 0.000 description 1

- 239000002699 waste material Substances 0.000 description 1

Images

Classifications

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B41—PRINTING; LINING MACHINES; TYPEWRITERS; STAMPS

- B41J—TYPEWRITERS; SELECTIVE PRINTING MECHANISMS, i.e. MECHANISMS PRINTING OTHERWISE THAN FROM A FORME; CORRECTION OF TYPOGRAPHICAL ERRORS

- B41J2/00—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed

- B41J2/005—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by bringing liquid or particles selectively into contact with a printing material

- B41J2/01—Ink jet

- B41J2/015—Ink jet characterised by the jet generation process

- B41J2/04—Ink jet characterised by the jet generation process generating single droplets or particles on demand

- B41J2/045—Ink jet characterised by the jet generation process generating single droplets or particles on demand by pressure, e.g. electromechanical transducers

- B41J2/04501—Control methods or devices therefor, e.g. driver circuits, control circuits

- B41J2/04536—Control methods or devices therefor, e.g. driver circuits, control circuits using history data

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B41—PRINTING; LINING MACHINES; TYPEWRITERS; STAMPS

- B41J—TYPEWRITERS; SELECTIVE PRINTING MECHANISMS, i.e. MECHANISMS PRINTING OTHERWISE THAN FROM A FORME; CORRECTION OF TYPOGRAPHICAL ERRORS

- B41J2/00—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed

- B41J2/005—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by bringing liquid or particles selectively into contact with a printing material

- B41J2/01—Ink jet

- B41J2/015—Ink jet characterised by the jet generation process

- B41J2/04—Ink jet characterised by the jet generation process generating single droplets or particles on demand

- B41J2/045—Ink jet characterised by the jet generation process generating single droplets or particles on demand by pressure, e.g. electromechanical transducers

- B41J2/04501—Control methods or devices therefor, e.g. driver circuits, control circuits

- B41J2/04541—Specific driving circuit

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B41—PRINTING; LINING MACHINES; TYPEWRITERS; STAMPS

- B41J—TYPEWRITERS; SELECTIVE PRINTING MECHANISMS, i.e. MECHANISMS PRINTING OTHERWISE THAN FROM A FORME; CORRECTION OF TYPOGRAPHICAL ERRORS

- B41J2/00—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed

- B41J2/005—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by bringing liquid or particles selectively into contact with a printing material

- B41J2/01—Ink jet

- B41J2/015—Ink jet characterised by the jet generation process

- B41J2/04—Ink jet characterised by the jet generation process generating single droplets or particles on demand

- B41J2/045—Ink jet characterised by the jet generation process generating single droplets or particles on demand by pressure, e.g. electromechanical transducers

- B41J2/04501—Control methods or devices therefor, e.g. driver circuits, control circuits

- B41J2/04543—Block driving

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B41—PRINTING; LINING MACHINES; TYPEWRITERS; STAMPS

- B41J—TYPEWRITERS; SELECTIVE PRINTING MECHANISMS, i.e. MECHANISMS PRINTING OTHERWISE THAN FROM A FORME; CORRECTION OF TYPOGRAPHICAL ERRORS

- B41J2/00—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed

- B41J2/005—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by bringing liquid or particles selectively into contact with a printing material

- B41J2/01—Ink jet

- B41J2/015—Ink jet characterised by the jet generation process

- B41J2/04—Ink jet characterised by the jet generation process generating single droplets or particles on demand

- B41J2/045—Ink jet characterised by the jet generation process generating single droplets or particles on demand by pressure, e.g. electromechanical transducers

- B41J2/04501—Control methods or devices therefor, e.g. driver circuits, control circuits

- B41J2/04551—Control methods or devices therefor, e.g. driver circuits, control circuits using several operating modes

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B41—PRINTING; LINING MACHINES; TYPEWRITERS; STAMPS

- B41J—TYPEWRITERS; SELECTIVE PRINTING MECHANISMS, i.e. MECHANISMS PRINTING OTHERWISE THAN FROM A FORME; CORRECTION OF TYPOGRAPHICAL ERRORS

- B41J2/00—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed

- B41J2/005—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by bringing liquid or particles selectively into contact with a printing material

- B41J2/01—Ink jet

- B41J2/015—Ink jet characterised by the jet generation process

- B41J2/04—Ink jet characterised by the jet generation process generating single droplets or particles on demand

- B41J2/045—Ink jet characterised by the jet generation process generating single droplets or particles on demand by pressure, e.g. electromechanical transducers

- B41J2/04501—Control methods or devices therefor, e.g. driver circuits, control circuits

- B41J2/04555—Control methods or devices therefor, e.g. driver circuits, control circuits detecting current

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B41—PRINTING; LINING MACHINES; TYPEWRITERS; STAMPS

- B41J—TYPEWRITERS; SELECTIVE PRINTING MECHANISMS, i.e. MECHANISMS PRINTING OTHERWISE THAN FROM A FORME; CORRECTION OF TYPOGRAPHICAL ERRORS

- B41J2/00—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed

- B41J2/005—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by bringing liquid or particles selectively into contact with a printing material

- B41J2/01—Ink jet

- B41J2/015—Ink jet characterised by the jet generation process

- B41J2/04—Ink jet characterised by the jet generation process generating single droplets or particles on demand

- B41J2/045—Ink jet characterised by the jet generation process generating single droplets or particles on demand by pressure, e.g. electromechanical transducers

- B41J2/04501—Control methods or devices therefor, e.g. driver circuits, control circuits

- B41J2/04563—Control methods or devices therefor, e.g. driver circuits, control circuits detecting head temperature; Ink temperature

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B41—PRINTING; LINING MACHINES; TYPEWRITERS; STAMPS

- B41J—TYPEWRITERS; SELECTIVE PRINTING MECHANISMS, i.e. MECHANISMS PRINTING OTHERWISE THAN FROM A FORME; CORRECTION OF TYPOGRAPHICAL ERRORS

- B41J2/00—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed

- B41J2/005—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by bringing liquid or particles selectively into contact with a printing material

- B41J2/01—Ink jet

- B41J2/015—Ink jet characterised by the jet generation process

- B41J2/04—Ink jet characterised by the jet generation process generating single droplets or particles on demand

- B41J2/045—Ink jet characterised by the jet generation process generating single droplets or particles on demand by pressure, e.g. electromechanical transducers

- B41J2/04501—Control methods or devices therefor, e.g. driver circuits, control circuits

- B41J2/0458—Control methods or devices therefor, e.g. driver circuits, control circuits controlling heads based on heating elements forming bubbles

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B41—PRINTING; LINING MACHINES; TYPEWRITERS; STAMPS

- B41J—TYPEWRITERS; SELECTIVE PRINTING MECHANISMS, i.e. MECHANISMS PRINTING OTHERWISE THAN FROM A FORME; CORRECTION OF TYPOGRAPHICAL ERRORS

- B41J2/00—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed

- B41J2/005—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by bringing liquid or particles selectively into contact with a printing material

- B41J2/01—Ink jet

- B41J2/015—Ink jet characterised by the jet generation process

- B41J2/04—Ink jet characterised by the jet generation process generating single droplets or particles on demand

- B41J2/045—Ink jet characterised by the jet generation process generating single droplets or particles on demand by pressure, e.g. electromechanical transducers

- B41J2/04501—Control methods or devices therefor, e.g. driver circuits, control circuits

- B41J2/04586—Control methods or devices therefor, e.g. driver circuits, control circuits controlling heads of a type not covered by groups B41J2/04575 - B41J2/04585, or of an undefined type

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/06—Addressing a physical block of locations, e.g. base addressing, module addressing, memory dedication

- G06F12/0615—Address space extension

- G06F12/063—Address space extension for I/O modules, e.g. memory mapped I/O

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1668—Details of memory controller

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/12—Digital output to print unit, e.g. line printer, chain printer

- G06F3/1293—Printer information exchange with computer

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1051—Data output circuits, e.g. read-out amplifiers, data output buffers, data output registers, data output level conversion circuits

- G11C7/1069—I/O lines read out arrangements

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/16—Storage of analogue signals in digital stores using an arrangement comprising analogue/digital [A/D] converters, digital memories and digital/analogue [D/A] converters

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/26—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2207/00—Indexing scheme relating to arrangements for writing information into, or reading information out from, a digital store

- G11C2207/10—Aspects relating to interfaces of memory device to external buses

- G11C2207/105—Aspects related to pads, pins or terminals

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Human Computer Interaction (AREA)

- Particle Formation And Scattering Control In Inkjet Printers (AREA)

- Electronic Switches (AREA)

- Accessory Devices And Overall Control Thereof (AREA)

- Ink Jet (AREA)

- Credit Cards Or The Like (AREA)

- Dot-Matrix Printers And Others (AREA)

- Facsimiles In General (AREA)

- Recording Measured Values (AREA)

Description

以下の詳細な説明では、本明細書の一部を形成する添付の図面が参照される。添付の図面には、本開示を実施することができる種々の特定の例が、例として示されている。本開示の範囲から逸脱することなく、他の例を利用することができ、構造的又は論理的な変更を行うことができることを理解されたい。したがって、以下の詳細な説明は、限定的な意味で解釈されるべきではなく、本開示の範囲は、添付の特許請求の範囲によって定義される。本明細書に記載された様々な例の特徴は、特に断りのない限り、部分的又は全体的に互いに組み合わされてもよいことを理解されたい。

Claims (26)

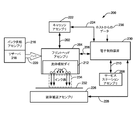

- 印刷コンポーネントのメモリ回路であって、

前記印刷コンポーネントに動作信号を伝達する複数の信号経路に接続するための、アナログパッドを含む複数のI/Oパッドと、

前記印刷コンポーネントに関連するメモリ値を記憶するためのメモリコンポーネントと、

メモリ読み取りを表す前記I/Oパッドを介してプリンタから前記印刷コンポーネントに伝達されている一連の動作信号に応答して、前記アナログパッドに前記プリンタへのアナログ応答信号を提供することにより、前記メモリ読み取りによって選択された前記印刷コンポーネントのメモリ要素に対応する前記メモリコンポーネントに記憶されたメモリ値を表すアナログ電気値を前記アナログパッド上に提供する制御回路と

を含む、メモリ回路。 - 前記制御回路は、メモリ書き込みを表す前記I/Oパッド上の一連の動作信号に応答して、前記メモリ書き込みによって識別された前記記憶されたメモリ値を更新する、請求項1に記載のメモリ回路。

- 前記アナログパッドにアクセスする非メモリ読み取り機能を表す前記I/Oパッドを介して前記印刷コンポーネントに伝達されている一連の動作信号に応答して、前記アナログパッドにアナログ応答信号を提供することにより、前記非メモリ読み取り機能に対応する記憶されたメモリ値を表すアナログ電気値を前記アナログパッド上に提供する、請求項1又は請求項2に記載のメモリ回路。

- 前記非メモリ読み取り機能は、少なくとも1つのアナログコンポーネントの読み取りを含む、請求項3に記載のメモリ回路。

- 前記少なくとも1つのアナログコンポーネントは、少なくとも1つの検知回路を含む、請求項4に記載のメモリ回路。

- 前記アナログパッドは、アナログ検知パッドである、請求項1~5の何れか一項に記載のメモリ回路。

- 前記アナログパッドは、アナログ検知回路に接続されている、請求項1~6の何れか一項に記載のメモリ回路。

- 前記メモリコンポーネントと前記制御回路は、同じ基板上にある、請求項1~7の何れか一項に記載のメモリ回路。

- 前記メモリコンポーネントは、前記メモリ値を記憶するメモリセルのアレイを含む、請求項1~8の何れか一項に記載のメモリ回路。

- 前記メモリ値は、ルックアップテーブルとして前記メモリコンポーネントに記憶されている、請求項1~9の何れか一項に記載のメモリ回路。

- 前記メモリ回路は、前記I/Oパッドを介して、前記印刷コンポーネントと並列に前記信号経路に結合されるものである、請求項1~10の何れか一項に記載のメモリ回路。

- 印刷コンポーネントであって、

前記印刷コンポーネントの動作を制御するための動作信号を伝達するための、アナログパッドを含むいくつかのI/Oパッドと、

前記I/Oパッドに結合され、流体アクチュエータのアレイを含む流体噴射回路と、

前記I/Oパッドに結合されたメモリ回路であって、

前記印刷コンポーネントに関連するメモリ値を記憶するためのメモリコンポーネントと、

メモリ読み取りを表す前記I/Oパッドを介してプリンタから前記印刷コンポーネントに伝達されている一連の動作信号に応答して、前記メモリ読み取りによって選択された前記流体噴射回路のメモリ要素に対応する前記メモリコンポーネントに記憶されたメモリ値を表す前記プリンタへのアナログ応答信号を前記アナログパッド上に提供する制御回路と

を含むメモリ回路と

を含む、印刷コンポーネント。 - 前記制御回路は、メモリ書き込みを表す前記I/Oパッドによって伝達されている一連の動作信号に応答して、前記メモリ書き込みによって識別された記憶されたメモリ値を更新する、請求項12に記載の印刷コンポーネント。

- 前記制御回路は、前記アナログパッドにアクセスする非メモリ読み取り機能を表す前記I/Oパッドを介して前記印刷コンポーネントに伝達されている一連の動作信号に応答して、前記アナログパッドにアナログ応答信号を提供することにより、前記非メモリ読み取り機能に対応する記憶されたメモリ値を表すアナログ電気値を前記アナログパッド上に提供する、請求項12又は請求項13に記載の印刷コンポーネント。

- 前記アナログパッドは、アナログ検知パッドである、請求項12~14の何れか一項に記載の印刷コンポーネント。

- 前記アナログパッドは、アナログ検知回路に接続されている、請求項12~15の何れか一項に記載の印刷コンポーネント。

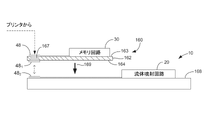

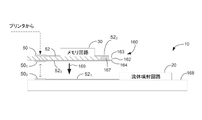

- 前記流体噴射回路と前記メモリ回路は、別個の基板上にある、請求項12~16の何れか一項に記載の印刷コンポーネント。

- 前記メモリコンポーネントは、前記メモリ値を記憶するメモリセルのアレイを含む、請求項12~17の何れか一項に記載の印刷コンポーネント。

- 前記メモリ値は、ルックアップテーブルとして前記メモリコンポーネントに記憶されている、請求項12~18の何れか一項に記載の印刷コンポーネント。

- 前記メモリ回路は、前記流体噴射回路と並列に前記I/Oパッドに結合されている、請求項12~19の何れか一項に記載の印刷コンポーネント。

- 前記印刷コンポーネントは、プリントヘッドを含む、請求項12~20の何れか一項に記載の印刷コンポーネント。

- 前記印刷コンポーネントは、一体型プリントヘッドを含む、請求項12~20の何れか一項に記載の印刷コンポーネント。

- 印刷コンポーネントであって、

複数の流体噴射ダイであって、各ダイが、

流体アクチュエータのアレイと、

メモリ要素のアレイであって、各メモリ要素が、前記印刷コンポーネントに関連するデータを表すデータビットを記憶する、メモリ要素のアレイと、

前記印刷コンポーネントの動作を制御するための動作信号を伝達するためのいくつかのI/Oパッドであって、前記流体噴射ダイの各々に並列に接続されたアナログ検知パッドを含む、いくつかのI/Oパッドと、

前記I/Oパッドに結合されたメモリ回路であって、

前記印刷コンポーネントに関連するメモリ値を記憶するためのメモリコンポーネントと、

前記流体噴射ダイのメモリ要素のメモリ読み取りを表す前記I/Oパッドを介してプリンタから前記印刷コンポーネントに伝達されている一連の動作信号に応答して、前記メモリ読み取りによって選択された前記メモリ要素に対応する前記メモリコンポーネントに記憶されたメモリ値を表す前記プリンタへのアナログ応答信号を前記アナログ検知パッド上に提供する制御回路と

を含むメモリ回路と

を含む、印刷コンポーネント。 - 前記複数の流体噴射ダイは、カラープリントペンを形成するように配置されている、請求項23に記載の印刷コンポーネント。

- 前記カラープリントペンは、シアンのプリントペンを含む第1の流体噴射ダイ、黄色のプリントペンを含む第2の流体噴射ダイ、及びマゼンタのプリントペンを含む第3の流体噴射ダイを含む、請求項24に記載の印刷コンポーネント。

- 前記複数の流体噴射ダイのうちの第1の部分は、カラープリントペンを形成するように構成され、第2の部分は、単色プリントペンを形成するように構成されている、請求項23~25の何れか一項に記載の印刷コンポーネント。

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| USPCT/US2019/016817 | 2019-02-06 | ||

| PCT/US2019/016817 WO2020162920A1 (en) | 2019-02-06 | 2019-02-06 | Communicating print component |

| USPCT/US2019/016725 | 2019-02-06 | ||

| PCT/US2019/016725 WO2020162887A1 (en) | 2019-02-06 | 2019-02-06 | Multiple circuits coupled to an interface |

| PCT/US2019/044446 WO2020162969A1 (en) | 2019-02-06 | 2019-07-31 | Print component with memory circuit |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2022517409A JP2022517409A (ja) | 2022-03-08 |

| JP7213360B2 true JP7213360B2 (ja) | 2023-01-26 |

Family

ID=67544483

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2021541203A Active JP7213360B2 (ja) | 2019-02-06 | 2019-07-31 | メモリ回路を備えた印刷コンポーネント |

| JP2021541205A Active JP7146101B2 (ja) | 2019-02-06 | 2019-07-31 | メモリ回路を備えた印刷コンポーネント |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2021541205A Active JP7146101B2 (ja) | 2019-02-06 | 2019-07-31 | メモリ回路を備えた印刷コンポーネント |

Country Status (15)

| Country | Link |

|---|---|

| US (6) | US11453212B2 (ja) |

| EP (6) | EP4223541A3 (ja) |

| JP (2) | JP7213360B2 (ja) |

| KR (2) | KR102667043B1 (ja) |

| CN (4) | CN113412197B (ja) |

| AU (4) | AU2019428188B2 (ja) |

| BR (4) | BR112021014778A2 (ja) |

| CA (4) | CA3126914A1 (ja) |

| CL (2) | CL2021001879A1 (ja) |

| ES (1) | ES2924338T3 (ja) |

| IL (2) | IL284655B2 (ja) |

| MX (4) | MX2021008849A (ja) |

| PL (1) | PL3710274T3 (ja) |

| SA (1) | SA521422685B1 (ja) |

| WO (4) | WO2020162972A1 (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| AU2019428181B2 (en) | 2019-02-06 | 2023-11-16 | Hewlett-Packard Development Company, L.P. | Data packets comprising random numbers for controlling fluid dispensing devices |

| EP4223541A3 (en) | 2019-02-06 | 2023-08-16 | Hewlett-Packard Development Company, L.P. | Print component with memory circuit |

| MX2021008895A (es) | 2019-02-06 | 2021-08-19 | Hewlett Packard Development Co | Componente de impresion de comunicacion. |

| CN113316518B (zh) | 2019-02-06 | 2022-10-14 | 惠普发展公司,有限责任合伙企业 | 流体分配设备部件及其形成方法、以及流体分配系统 |

| US11787173B2 (en) | 2019-02-06 | 2023-10-17 | Hewlett-Packard Development Company, L.P. | Print component with memory circuit |

| MX2021009121A (es) * | 2019-02-06 | 2021-09-08 | Hewlett Packard Development Co | Componente de impresion con conjunto de memoria usando se?al intermitente de reloj. |

| AU2019428638B2 (en) | 2019-02-06 | 2023-11-09 | Hewlett-Packard Development Company, L.P. | Integrated circuit with address drivers for fluidic die |

| IL284504B2 (en) * | 2019-02-06 | 2024-09-01 | Hewlett Packard Development Co | Ring for print head |

| CN113412191B (zh) | 2019-02-06 | 2022-10-14 | 惠普发展公司,有限责任合伙企业 | 流体喷射设备 |

| US11407218B2 (en) | 2019-02-06 | 2022-08-09 | Hewlett-Packard Development Company, L.P. | Identifying random bits in control data packets |

| EP4366952A1 (en) * | 2021-07-06 | 2024-05-15 | Hewlett-Packard Development Company, L.P. | Integrated circuits including first and second power supply nodes for writing and reading memory cells |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002519808A (ja) | 1998-06-30 | 2002-07-02 | サンディスク コーポレイション | 集積回路技術を用いたアナログ及びマルチレベル記憶技法 |

| US20180086122A1 (en) | 2013-10-15 | 2018-03-29 | Hewlett-Packard Development Company, L.P. | Authentication value for a fluid ejection device |

| WO2019009904A1 (en) | 2017-07-06 | 2019-01-10 | Hewlett-Packard Development Company, L.P. | SELECTORS FOR NOZZLES AND MEMORY ELEMENTS |

Family Cites Families (100)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6111845A (ja) * | 1984-06-27 | 1986-01-20 | Nec Corp | 印字デ−タ制御装置 |

| JPH0671875A (ja) | 1992-06-30 | 1994-03-15 | Fuji Xerox Co Ltd | インクジェット記録装置 |

| US6116714A (en) | 1994-03-04 | 2000-09-12 | Canon Kabushiki Kaisha | Printing head, printing method and apparatus using same, and apparatus and method for correcting said printing head |

| JPH08127162A (ja) | 1994-11-02 | 1996-05-21 | Hitachi Ltd | 画像プリンタ |

| JP2702426B2 (ja) | 1994-12-16 | 1998-01-21 | 日本電気データ機器株式会社 | サーマルヘッド装置 |

| CA2168994C (en) | 1995-03-08 | 2000-01-18 | Juan J. Becerra | Method and apparatus for interleaving pulses in a liquid recorder |

| US5625603A (en) | 1995-06-07 | 1997-04-29 | Sgs-Thomson Microelectronics, Inc. | Integrated circuit with unequally-sized, paired memory coupled to odd number of input/output pads |

| US6022094A (en) | 1995-09-27 | 2000-02-08 | Lexmark International, Inc. | Memory expansion circuit for ink jet print head identification circuit |

| US5745409A (en) * | 1995-09-28 | 1998-04-28 | Invox Technology | Non-volatile memory with analog and digital interface and storage |

| DE69601927T2 (de) | 1995-11-21 | 1999-09-09 | Citizen Watch Co. | Ansteuerungsverfahren und -vorrichtung für einen tintenstrahldrucker |

| JPH1018953A (ja) * | 1996-07-03 | 1998-01-20 | Ngk Spark Plug Co Ltd | 内燃機関の燃焼状態検出装置 |

| US5942900A (en) | 1996-12-17 | 1999-08-24 | Lexmark International, Inc. | Method of fault detection in ink jet printhead heater chips |

| US6672706B2 (en) | 1997-07-15 | 2004-01-06 | Silverbrook Research Pty Ltd | Wide format pagewidth inkjet printer |

| JPH11207948A (ja) | 1997-11-14 | 1999-08-03 | Canon Inc | 記録装置及び記録制御方法 |

| US6038166A (en) | 1998-04-01 | 2000-03-14 | Invox Technology | High resolution multi-bit-per-cell memory |

| JPH11341347A (ja) * | 1998-05-11 | 1999-12-10 | Newcore Technol Inc | 信号変換処理装置 |

| US6154157A (en) * | 1998-11-25 | 2000-11-28 | Sandisk Corporation | Non-linear mapping of threshold voltages for analog/multi-level memory |

| US6938976B2 (en) | 1999-06-16 | 2005-09-06 | Eastman Kodak Company | Printer and method therefor adapted to sense data uniquely associated with a consumable loaded into the printer |

| WO2002004219A1 (en) | 2000-06-30 | 2002-01-17 | Silverbrook Research Pty Ltd | Controlling the timing of printhead nozzle firing |

| JP4081963B2 (ja) | 2000-06-30 | 2008-04-30 | セイコーエプソン株式会社 | 記憶装置および記憶装置に対するアクセス方法 |

| EP1250233A1 (en) | 2001-01-09 | 2002-10-23 | Encad, Inc. | Ink jet printhead quality management system and method |

| JP4304868B2 (ja) | 2001-02-05 | 2009-07-29 | コニカミノルタホールディングス株式会社 | メモリ装置を有する画像形成装置及び判断処理方法 |

| US6616260B2 (en) | 2001-05-25 | 2003-09-09 | Hewlett-Packard Development Company, L.P. | Robust bit scheme for a memory of a replaceable printer component |

| US7510255B2 (en) | 2001-08-30 | 2009-03-31 | Seiko Epson Corporation | Device and method for detecting temperature of head driver IC for ink jet printer |

| JP2004050637A (ja) | 2002-07-19 | 2004-02-19 | Canon Inc | インクジェットヘッド用基板、インクジェットヘッド及び該インクジェットヘッドを備えたインクジェット記録装置 |

| TW536479B (en) | 2002-09-05 | 2003-06-11 | Benq Corp | Inkjet printer using thermal sensing elements to identify different types of cartridges |

| KR100495667B1 (ko) | 2003-01-13 | 2005-06-16 | 삼성전자주식회사 | 아날로그/디지털 입력 모드를 제공하는 입출력 버퍼 |

| US7311385B2 (en) | 2003-11-12 | 2007-12-25 | Lexmark International, Inc. | Micro-fluid ejecting device having embedded memory device |

| JP4262070B2 (ja) | 2003-12-02 | 2009-05-13 | キヤノン株式会社 | 記録ヘッドの素子基体、記録ヘッド及び記録ヘッドの制御方法 |

| TWI243990B (en) | 2003-12-26 | 2005-11-21 | Ind Tech Res Inst | Printer, inkjet print head, identification circuit of inkjet print head and identification method thereof |

| MXPA04012681A (es) | 2003-12-26 | 2005-07-01 | Canon Kk | Recipiente para liquido y sistema de suministro de liquido. |

| US7267417B2 (en) | 2004-05-27 | 2007-09-11 | Silverbrook Research Pty Ltd | Printer controller for supplying data to one or more printheads via serial links |

| CN100548683C (zh) | 2004-05-27 | 2009-10-14 | 佳能株式会社 | 打印头基板、打印头、头盒和打印设备 |

| US7328956B2 (en) | 2004-05-27 | 2008-02-12 | Silverbrook Research Pty Ltd | Printer comprising a printhead and at least two printer controllers connected to a common input of the printhead |

| KR100694053B1 (ko) | 2004-07-30 | 2007-03-12 | 삼성전자주식회사 | 잉크젯 프린터의 프린트 헤드 구동 장치 및 이에 적합한반도체 회로 기판 |

| US7413272B2 (en) | 2004-11-04 | 2008-08-19 | Applied Materials, Inc. | Methods and apparatus for precision control of print head assemblies |

| US7365387B2 (en) | 2006-02-23 | 2008-04-29 | Hewlett-Packard Development Company, L.P. | Gate-coupled EPROM cell for printhead |

| CN101064187A (zh) | 2006-04-27 | 2007-10-31 | 松下电器产业株式会社 | 半导体集成电路装置 |

| US7613661B2 (en) | 2006-08-02 | 2009-11-03 | Pitney Bowes Inc. | Method and system for detecting duplicate printing of indicia in a metering system |

| US7425047B2 (en) | 2006-10-10 | 2008-09-16 | Silverbrook Research Pty Ltd | Printhead IC compatible with mutally incompatible print engine controllers |

| US7719901B2 (en) * | 2007-06-05 | 2010-05-18 | Micron Technology, Inc. | Solid state memory utilizing analog communication of data values |

| US20090040286A1 (en) | 2007-08-08 | 2009-02-12 | Tan Theresa Joy L | Print scheduling in handheld printers |

| DK2209645T3 (da) | 2007-11-14 | 2013-05-13 | Hewlett Packard Development Co | Inkjet print-hoved med delte datalinjer |

| EP2263146B3 (en) | 2008-03-14 | 2018-09-05 | Hewlett-Packard Development Company, L.P. | Secure access to fluid cartridge memory |

| US7815273B2 (en) | 2008-04-01 | 2010-10-19 | Hewlett-Packard Development Company, L.P. | Fluid ejection device |

| US7768832B2 (en) | 2008-04-07 | 2010-08-03 | Micron Technology, Inc. | Analog read and write paths in a solid state memory device |

| US20090265596A1 (en) | 2008-04-22 | 2009-10-22 | Mediatek Inc. | Semiconductor devices, integrated circuit packages and testing methods thereof |

| JP5647822B2 (ja) | 2009-07-24 | 2015-01-07 | ローム株式会社 | サーマルプリントヘッド、サーマルプリンタおよびプリンタシステム |

| US8516304B2 (en) | 2009-08-18 | 2013-08-20 | Lexmark International, Inc. | Integrated circuit including a programmable logic analyzer with enhanced analyzing and debugging capabilities and a method therefor |

| BRPI1004997A2 (pt) | 2009-11-11 | 2013-02-26 | Seiko Epson Corp | dispositivo eletrânico e mÉtodo de controle do mesmo |

| WO2011127183A2 (en) | 2010-04-07 | 2011-10-13 | Intellipaper , Llc | Memomy programming methods and memory programming devices |

| JP5678290B2 (ja) | 2010-04-27 | 2015-02-25 | 株式会社デュプロ | インクジェット記録装置 |

| JP5737966B2 (ja) | 2011-01-25 | 2015-06-17 | キヤノン株式会社 | 液体吐出ヘッドおよび液体吐出ヘッドの製造方法 |

| EP2726296B1 (en) | 2011-07-01 | 2018-09-05 | Hewlett-Packard Development Company, L.P. | Method and apparatus to regulate temperature of printheads |

| JP5410486B2 (ja) | 2011-09-21 | 2014-02-05 | 富士フイルム株式会社 | 液体吐出ヘッド、液体吐出装置及び液体吐出ヘッドの異常検知方法 |

| WO2013048376A1 (en) | 2011-09-27 | 2013-04-04 | Hewlett-Packard Development Company, L.P. | Circuit that selects eproms individually and in parallel |

| KR101787183B1 (ko) | 2011-09-30 | 2017-10-18 | 휴렛-팩커드 디벨롭먼트 컴퍼니, 엘.피. | 인증 시스템 및 방법 |

| US8882217B2 (en) | 2011-10-27 | 2014-11-11 | Hewlett-Packard Development Company, L.P. | Printhead assembly including memory elements |

| TWI461959B (zh) | 2012-04-26 | 2014-11-21 | Issc Technologies Corp | 輸出輸入介面裝置 |

| ES2707071T3 (es) | 2012-08-30 | 2019-04-02 | Hewlett Packard Development Co | Componente de impresión reemplazable con código de identidad de fábrica |

| RU2635080C2 (ru) | 2012-11-30 | 2017-11-08 | Хьюлетт-Паккард Дивелопмент Компани, Л.П. | Устройство выброса текучей среды со встроенным датчиком уровня чернил |

| US9224480B2 (en) | 2013-02-27 | 2015-12-29 | Texas Instruments Incorporated | Dual-function read/write cache for programmable non-volatile memory |

| WO2014133534A1 (en) | 2013-02-28 | 2014-09-04 | Hewlett-Packard Development Company, L.P. | Print head bit information mapping |

| FI124954B (fi) | 2013-04-30 | 2015-04-15 | Outotec Oyj | Menetelmä kultaa sisältävän liuoksen valmistamiseksi ja prosessijärjestely kullan ja hopean talteenottamiseksi |

| US8888226B1 (en) | 2013-06-25 | 2014-11-18 | Hewlett-Packard Development Company, L.P. | Crack detection circuits for printheads |

| US9889664B2 (en) | 2013-09-20 | 2018-02-13 | Hewlett-Packard Development Company, L.P. | Molded printhead structure |

| US9919524B2 (en) | 2013-11-27 | 2018-03-20 | Hewlett-Packard Development Company, L.P. | Printhead with bond pad surrounded by dam |

| WO2015102639A1 (en) | 2014-01-03 | 2015-07-09 | Hewlett-Packard Development Company, Lp | Fluid ejection device with integrated ink level sensors |

| EP3236471A3 (en) | 2014-01-31 | 2018-01-17 | Hewlett-Packard Development Company, L.P. | Three-dimensional addressing for erasable programmable read only memory |

| US9196373B2 (en) * | 2014-02-26 | 2015-11-24 | Sandisk 3D Llc | Timed multiplex sensing |

| US9953991B2 (en) | 2014-03-14 | 2018-04-24 | Hewlett-Packard Development Company, L.P. | EPROM cell with modified floating gate |

| JP6369191B2 (ja) * | 2014-07-18 | 2018-08-08 | セイコーエプソン株式会社 | 回路装置、電子機器、移動体及び無線通信システム |

| EP3456542B1 (en) | 2014-10-29 | 2020-04-01 | Hewlett-Packard Development Company, L.P. | Printhead die |

| US9472288B2 (en) | 2014-10-29 | 2016-10-18 | Hewlett-Packard Development Company, L.P. | Mitigating parasitic current while programming a floating gate memory array |

| WO2016068927A1 (en) | 2014-10-30 | 2016-05-06 | Hewlett-Packard Development Company, L.P. | Printhead with a number of shared enclosed selectors |

| CN107073949B (zh) | 2014-10-30 | 2019-03-26 | 惠普发展公司,有限责任合伙企业 | 打印头感测室循环 |

| GB2533967B (en) | 2015-01-12 | 2021-08-25 | Advanced Risc Mach Ltd | Adapting the usage configuration of integrated circuit input-output pads |

| PL3293009T3 (pl) * | 2015-01-30 | 2021-12-13 | Hewlett-Packard Development Company, L.P. | Wykrywanie pęknięć dla głowicy z wieloma matrycami głowicy drukującej |

| JP6430858B2 (ja) | 2015-02-27 | 2018-11-28 | 理想科学工業株式会社 | 基板接続システム及びインクジェット記録装置 |

| US9493002B2 (en) | 2015-04-10 | 2016-11-15 | Funai Electric Co., Ltd. | Printhead condition detection system |

| WO2016167763A1 (en) | 2015-04-15 | 2016-10-20 | Hewlett-Packard Development Company, L.P. | Printheads with high dielectric eprom cells |

| WO2016175853A1 (en) | 2015-04-30 | 2016-11-03 | Hewlett-Packard Development Company, L.P. | Printer fluid impedance sensing in a printhead |

| WO2017065743A1 (en) | 2015-10-13 | 2017-04-20 | Hewlett-Packard Development Company, L.P. | Printhead with s-shaped die |

| CN106685425B (zh) | 2015-11-11 | 2021-06-29 | 国民技术股份有限公司 | 一种音频信号处理装置及其模拟前端电路 |

| CN109152831A (zh) | 2015-12-29 | 2019-01-04 | 安口生物公司 | 贝伐珠单抗的缓冲制剂 |

| WO2017189009A1 (en) | 2016-04-29 | 2017-11-02 | Hewlett-Packard Development Company, L.P. | Printing apparatus and methods for detecting fluid levels |

| KR101907028B1 (ko) | 2016-07-06 | 2018-10-11 | 주식회사 유엑스팩토리 | 아날로그 디지털 인터페이스 sram 구조 |

| WO2018017066A1 (en) | 2016-07-19 | 2018-01-25 | Hewlett-Packard Development Company, L.P. | Fluid level sensors |

| US10044360B2 (en) | 2016-08-16 | 2018-08-07 | Microchip Technology Incorporated | ADC controller with temporal separation |

| MX2019002357A (es) | 2016-09-01 | 2019-09-26 | Hs Mfg Group Llc | Métodos para la derivación biológica de superficies celulósicas. |

| US10800168B2 (en) | 2016-10-06 | 2020-10-13 | Hewlett-Packard Development Company, L.P. | Input control signals propagated over signal paths |

| HUE058193T2 (hu) | 2017-01-31 | 2022-07-28 | Hewlett Packard Development Co | Memóriabankok és kiválasztási regiszterek elhelyezése |

| WO2018156617A2 (en) | 2017-02-22 | 2018-08-30 | The Regents Of The University Of Michigan | Compositions and methods for delivery of polymer / biomacromolecule conjugates |

| WO2018156171A1 (en) | 2017-02-27 | 2018-08-30 | Hewlett-Packard Development Company, L.P. | Nozzle sensor evaluation |

| US11117368B2 (en) | 2017-04-14 | 2021-09-14 | Hewlett-Packard Development Company, L.P. | Fluidic die |

| DE112017007727T5 (de) | 2017-07-06 | 2020-03-19 | Hewlett-Packard Development Company, L.P. | Decoder für speicher von fluidausstossvorrichtungen |

| WO2019017867A1 (en) | 2017-07-17 | 2019-01-24 | Hewlett-Packard Development Company, L.P. | FLUIDIC MATRIX |

| US10692570B2 (en) * | 2018-07-11 | 2020-06-23 | Sandisk Technologies Llc | Neural network matrix multiplication in memory cells |

| EP4223541A3 (en) | 2019-02-06 | 2023-08-16 | Hewlett-Packard Development Company, L.P. | Print component with memory circuit |

| CN113316518B (zh) | 2019-02-06 | 2022-10-14 | 惠普发展公司,有限责任合伙企业 | 流体分配设备部件及其形成方法、以及流体分配系统 |

-

2019

- 2019-07-31 EP EP23165056.5A patent/EP4223541A3/en active Pending

- 2019-07-31 CA CA3126914A patent/CA3126914A1/en active Pending

- 2019-07-31 KR KR1020217024126A patent/KR102667043B1/ko active IP Right Grant

- 2019-07-31 CA CA3126915A patent/CA3126915A1/en active Pending

- 2019-07-31 BR BR112021014778-0A patent/BR112021014778A2/pt unknown

- 2019-07-31 CN CN201980091460.0A patent/CN113412197B/zh active Active

- 2019-07-31 AU AU2019428188A patent/AU2019428188B2/en active Active

- 2019-07-31 PL PL19750041.6T patent/PL3710274T3/pl unknown

- 2019-07-31 BR BR112021014728-4A patent/BR112021014728A2/pt unknown

- 2019-07-31 ES ES19750041T patent/ES2924338T3/es active Active

- 2019-07-31 US US16/768,125 patent/US11453212B2/en active Active

- 2019-07-31 MX MX2021008849A patent/MX2021008849A/es unknown

- 2019-07-31 EP EP19750038.2A patent/EP3710271B1/en active Active

- 2019-07-31 AU AU2019428305A patent/AU2019428305B2/en active Active

- 2019-07-31 IL IL284655A patent/IL284655B2/en unknown

- 2019-07-31 EP EP19750039.0A patent/EP3710272B1/en active Active

- 2019-07-31 CN CN201980090978.2A patent/CN113382873B/zh active Active

- 2019-07-31 MX MX2021008897A patent/MX2021008897A/es unknown

- 2019-07-31 CA CA3126913A patent/CA3126913C/en active Active

- 2019-07-31 JP JP2021541203A patent/JP7213360B2/ja active Active

- 2019-07-31 EP EP19750040.8A patent/EP3710273B1/en active Active

- 2019-07-31 IL IL284654A patent/IL284654B2/en unknown

- 2019-07-31 KR KR1020217024129A patent/KR20210104153A/ko active IP Right Grant

- 2019-07-31 EP EP22162575.9A patent/EP4046802B1/en active Active

- 2019-07-31 US US16/768,588 patent/US11590752B2/en active Active

- 2019-07-31 CN CN201980089330.3A patent/CN113302062B/zh active Active

- 2019-07-31 WO PCT/US2019/044520 patent/WO2020162972A1/en unknown

- 2019-07-31 AU AU2019428241A patent/AU2019428241B2/en active Active

- 2019-07-31 US US16/768,096 patent/US11498326B2/en active Active

- 2019-07-31 MX MX2021009125A patent/MX2021009125A/es unknown

- 2019-07-31 WO PCT/US2019/044446 patent/WO2020162969A1/en active Application Filing

- 2019-07-31 BR BR112021015327-6A patent/BR112021015327A2/pt unknown

- 2019-07-31 WO PCT/US2019/044494 patent/WO2020162970A1/en unknown

- 2019-07-31 CN CN201980091059.7A patent/CN113382874B/zh active Active

- 2019-07-31 BR BR112021015360-8A patent/BR112021015360A2/pt unknown

- 2019-07-31 US US16/768,541 patent/US11491782B2/en active Active

- 2019-07-31 AU AU2019428071A patent/AU2019428071B2/en active Active

- 2019-07-31 MX MX2021009110A patent/MX2021009110A/es unknown

- 2019-07-31 WO PCT/US2019/044507 patent/WO2020162971A1/en unknown

- 2019-07-31 CA CA3126920A patent/CA3126920C/en active Active

- 2019-07-31 EP EP19750041.6A patent/EP3710274B1/en active Active

- 2019-07-31 JP JP2021541205A patent/JP7146101B2/ja active Active

-

2021

- 2021-07-14 CL CL2021001879A patent/CL2021001879A1/es unknown

- 2021-07-26 CL CL2021001962A patent/CL2021001962A1/es unknown

- 2021-08-02 SA SA521422685A patent/SA521422685B1/ar unknown

-

2022

- 2022-10-06 US US17/961,476 patent/US11780222B2/en active Active

-

2023

- 2023-08-11 US US18/448,794 patent/US12030312B2/en active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002519808A (ja) | 1998-06-30 | 2002-07-02 | サンディスク コーポレイション | 集積回路技術を用いたアナログ及びマルチレベル記憶技法 |

| US20180086122A1 (en) | 2013-10-15 | 2018-03-29 | Hewlett-Packard Development Company, L.P. | Authentication value for a fluid ejection device |

| WO2019009904A1 (en) | 2017-07-06 | 2019-01-10 | Hewlett-Packard Development Company, L.P. | SELECTORS FOR NOZZLES AND MEMORY ELEMENTS |

Also Published As

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7213360B2 (ja) | メモリ回路を備えた印刷コンポーネント |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20210716 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20220517 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220812 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20220830 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20221125 |

|

| C60 | Trial request (containing other claim documents, opposition documents) |

Free format text: JAPANESE INTERMEDIATE CODE: C60 Effective date: 20221125 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20221212 |

|

| C21 | Notice of transfer of a case for reconsideration by examiners before appeal proceedings |

Free format text: JAPANESE INTERMEDIATE CODE: C21 Effective date: 20221213 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20230110 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20230116 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7213360 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: R3D02 |