JP5655277B2 - 薄膜トランジスタおよびアクティブマトリクスディスプレイ - Google Patents

薄膜トランジスタおよびアクティブマトリクスディスプレイ Download PDFInfo

- Publication number

- JP5655277B2 JP5655277B2 JP2009106130A JP2009106130A JP5655277B2 JP 5655277 B2 JP5655277 B2 JP 5655277B2 JP 2009106130 A JP2009106130 A JP 2009106130A JP 2009106130 A JP2009106130 A JP 2009106130A JP 5655277 B2 JP5655277 B2 JP 5655277B2

- Authority

- JP

- Japan

- Prior art keywords

- thin film

- film transistor

- semiconductor layer

- electrode

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Thin Film Transistor (AREA)

Description

のアレイと、該アレイのソース電極又はドレイン電極に接続された画素電極と、該画素電

極上に配置された画像表示媒体とを備える画像表示装置である。

酸化物を含む半導体層は、酸素密度が低い、言い換えれば酸素欠損が多いほど、その電気抵抗は低くなるという特徴を持つ。上記構成の本発明薄膜トランジスタは、前記ゲート絶縁層の界面付近は電気抵抗が低く、かつ界面から離れた層の電気抵抗は高くなることを意味する。この場合、トランジスタのいわゆるチャネル部分の抵抗は低いまま、チャネル層から離れたソース、ドレイン電極間近傍の半導体層の電気抵抗のみ高くなるため、ゲート電圧が正の場合にチャネル部分を流れるオン電流は高く、ゲート電圧が負の場合にチャネル層周辺を流れるオフ電流は小さくなる。したがって、該半導体層が酸素密度勾配を持たない場合と比較して、オンオフ比を向上させることができる。

絶縁基板101には、例えばガラスやプラスチック基板を用いることができる。プラスチック基板としては、例えば、ポリメチルメタクリレート、ポリアクリレート、ポリカーボネート、ポリスチレン、ポリエチレンサルファイド、ポリエーテルスルホン、ポリオレフィン、ポリエチレンテレフタレート、ポリエチレンナフタレート(PEN)、シクロオレフィンポリマー、ポリエーテルサルフェン(PES)、トリアセチルセルロース、ポリビニルフルオライドフィルム、エチレン−テトラフルオロエチレン共重合樹脂、耐候性ポリエチレンテレフタレート、耐候性ポリプロピレン、ガラス繊維強化アクリル樹脂フィルム、ガラス繊維強化ポリカーボネート、透明性ポリイミド、フッ素系樹脂、環状ポリオレフィン系樹脂等を使用することができる。これらの基板は単独で使用することもでき、二種以上を積層した複合基板を使用することもできる。

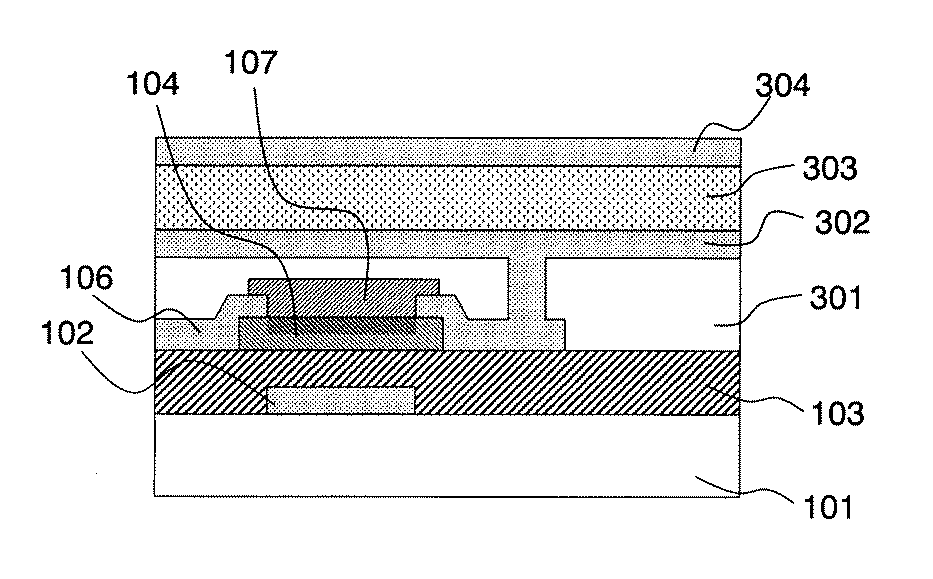

本発明の画像表示装置は、上記薄膜トランジスタを画素ごとに少なくとも一つ配置した薄膜トランジスタアレイとし、画像表示媒体303と接続する。画像表示媒体の例としては、電気泳動方式の表示媒体(電子ペーパー)や、液晶表示媒体、有機EL、無機EL等が挙げられる。

実施例1では図1に示したような本発明の薄膜トランジスタを作製した。

比較例1では半導体層104表面にO2プラズマを照射しなかったこと以外は、実施例1と同様の工程で薄膜トランジスタを作製した。

実施例2では、酸素含有プラズマの照射にアルゴン(Ar)と酸素(O2)の混合プラズマを用いたこと以外は実施例1と同様の工程で本発明の薄膜トランジスタを作製した。

実施例3では、酸素含有プラズマの照射工程にN2Oプラズマを用いたこと以外は実施例1と同様の工程で本発明の薄膜トランジスタを作製した。

比較例2では、プラズマの照射に酸素の含まない窒素(N2)プラズマを用いたこと以外は実施例1と同様の工程で本発明の薄膜トランジスタを作製した。

実施例4では図3に示したような本発明の薄膜トランジスタを作製した。

比較例3では半導体層104表面にO2プラズマを照射しなかったこと以外は、実施例4と同様の工程で薄膜トランジスタを作製した。

実施例5では、O2プラズマを照射した基板上にフォトレジストをスピンコートで膜厚3μmとして成膜し、パターニングを行い保護層6を形成したこと以外は実施例4と同様の工程で薄膜トランジスタ素子を作製した。各成膜工程は表3に示した。

比較例4では、半導体層104表面にO2プラズマを照射しなかったこと以外は、実施例5と同様の工程で薄膜トランジスタを作製した。

102 ゲート電極

103 ゲート絶縁層

104 半導体層

104b 高酸素密度化領域(プラズマ照射領域)

105 ソース電極

106 ドレイン電極

107 保護層

301 層間絶縁層

302 画素電極

303 画像表示媒体

304 対向電極

Claims (10)

- 絶縁基板上に少なくともゲート電極と、ゲート絶縁層が順次積層され、前記ゲート絶縁層上に酸化物を含む半導体層とソース電極およびドレイン電極が設けられたボトムゲート型の薄膜トランジスタであって、

前記半導体層表面の一部を覆うように前記ソース電極及びドレイン電極が形成されており、前記ソース電極及びドレイン電極を形成後に、前記ソース電極及びドレイン電極に覆われていない前記半導体層表面の領域に、N 2 Oプラズマを投入電力が100W以上200W以下で1分以上3分以下照射することで酸素を注入することを特徴とする薄膜トランジスタ。 - 前記酸化物を含む半導体層がInとGaとZnの少なくとも一種を含むことを特徴とする請求項1に記載の薄膜トランジスタ。

- 前記ソース電極及びドレイン電極に覆われていない前記半導体層上に保護層を有することを特徴とする請求項1または2のいずれかに記載の薄膜トランジスタ。

- 前記保護層は無機材料であることを特徴とする請求項3に記載の薄膜トランジスタ。

- 前記保護層は有機材料であることを特徴とする請求項3に記載の薄膜トランジスタ。

- 絶縁基板上にゲート電極を形成する工程と、

該ゲート電極上にゲート絶縁層を形成する工程と、

該ゲート絶縁層上に酸化物を含む半導体を形成する工程と、

該半導体層上にソース電極及びドレイン電極を形成する工程と、

該半導体層の表面に投入電力が100W以上200W以下で1分以上3分以下N2Oプラズマを照射する工程と、

を有することを特徴とする薄膜トランジスタの製造方法。 - 絶縁基板上にゲート電極を形成する工程と、

該ゲート電極上にゲート絶縁層を形成する工程と、

該ゲート絶縁層上にソース電極及びドレイン電極を形成する工程と、

該ソース電極及びドレイン電極の一部を覆うように酸化物を含む半導体層を形成する工程と、

該半導体層の表面に投入電力が100W以上200W以下で1分以上3分以下N2Oプラズマを照射する工程と、

を有することを特徴とする薄膜トランジスタの製造方法。 - 前記半導体層の表面にN2Oプラズマを照射した後に、該半導体層上に保護層を形成する工程を有することを特徴とする請求項6または7に記載の薄膜トランジスタの製造方法。

- 請求項1乃至5のいずれか1項に記載の薄膜トランジスタのアレイと、該アレイのソース電極又はドレイン電極に接続された画素電極と、該画素電極上に配置された画像表示媒体とを備える画像表示装置。

- 前記画像表示媒体が電気泳動方式によるものであることを特徴とする請求項9に記載の画像表示装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009106130A JP5655277B2 (ja) | 2009-04-24 | 2009-04-24 | 薄膜トランジスタおよびアクティブマトリクスディスプレイ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009106130A JP5655277B2 (ja) | 2009-04-24 | 2009-04-24 | 薄膜トランジスタおよびアクティブマトリクスディスプレイ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010258196A JP2010258196A (ja) | 2010-11-11 |

| JP5655277B2 true JP5655277B2 (ja) | 2015-01-21 |

Family

ID=43318771

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009106130A Expired - Fee Related JP5655277B2 (ja) | 2009-04-24 | 2009-04-24 | 薄膜トランジスタおよびアクティブマトリクスディスプレイ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5655277B2 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5645737B2 (ja) * | 2011-04-01 | 2014-12-24 | 株式会社神戸製鋼所 | 薄膜トランジスタ構造および表示装置 |

| US9553195B2 (en) * | 2011-06-30 | 2017-01-24 | Applied Materials, Inc. | Method of IGZO and ZNO TFT fabrication with PECVD SiO2 passivation |

| CN103765596B (zh) | 2011-08-11 | 2018-07-13 | 出光兴产株式会社 | 薄膜晶体管 |

| JP5679933B2 (ja) * | 2011-08-12 | 2015-03-04 | 富士フイルム株式会社 | 薄膜トランジスタ及びその製造方法、表示装置、イメージセンサー、x線センサー並びにx線デジタル撮影装置 |

| JP5933895B2 (ja) * | 2011-11-10 | 2016-06-15 | 株式会社半導体エネルギー研究所 | 半導体装置および半導体装置の作製方法 |

| JP2013232598A (ja) * | 2012-05-01 | 2013-11-14 | Panasonic Corp | 薄膜トランジスタの製造方法及び薄膜トランジスタ |

| CN111081734A (zh) | 2014-03-17 | 2020-04-28 | 松下电器产业株式会社 | 薄膜晶体管元件基板及其制造方法、和有机el显示装置 |

| KR102364105B1 (ko) * | 2020-05-18 | 2022-02-17 | 충북대학교 산학협력단 | 공정 시간에 따른 산화물 박막 트랜지스터의 제조방법 및 그 제조방법에 의해 제조된 산화물 박막 트랜지스터 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4870403B2 (ja) * | 2005-09-02 | 2012-02-08 | 財団法人高知県産業振興センター | 薄膜トランジスタの製法 |

| JP4870404B2 (ja) * | 2005-09-02 | 2012-02-08 | 財団法人高知県産業振興センター | 薄膜トランジスタの製法 |

| JP4609797B2 (ja) * | 2006-08-09 | 2011-01-12 | Nec液晶テクノロジー株式会社 | 薄膜デバイス及びその製造方法 |

| JP2009031742A (ja) * | 2007-04-10 | 2009-02-12 | Fujifilm Corp | 有機電界発光表示装置 |

| JP5339772B2 (ja) * | 2007-06-11 | 2013-11-13 | 富士フイルム株式会社 | 電子ディスプレイ |

| JP2009031750A (ja) * | 2007-06-28 | 2009-02-12 | Fujifilm Corp | 有機el表示装置およびその製造方法 |

-

2009

- 2009-04-24 JP JP2009106130A patent/JP5655277B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2010258196A (ja) | 2010-11-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7547434B2 (ja) | 表示装置 | |

| JP5320746B2 (ja) | 薄膜トランジスタ | |

| KR101891841B1 (ko) | 박막 트랜지스터 및 그의 제조 방법, 박막 트랜지스터를 구비하는 화상 표시 장치 | |

| JP5655277B2 (ja) | 薄膜トランジスタおよびアクティブマトリクスディスプレイ | |

| JP2010087223A (ja) | 薄膜トランジスタおよびアクティブマトリクスディスプレイ | |

| US8487308B2 (en) | Thin film transistor and image display unit | |

| JP2007115808A (ja) | トランジスタ | |

| JP2009021480A (ja) | 薄膜トランジスタ基板及びこれを用いた画像表示装置 | |

| JP2008076823A (ja) | 表示装置 | |

| JP6260326B2 (ja) | 薄膜トランジスタ装置及びその製造方法 | |

| JP2011049297A (ja) | 薄膜トランジスタの製造方法 | |

| JP5617214B2 (ja) | 薄膜トランジスタ及びその製造方法並びに画像表示装置 | |

| KR101298611B1 (ko) | 산화물 박막 트랜지스터 및 그 제조방법 | |

| JP5604938B2 (ja) | 薄膜トランジスタ及びその製造方法 | |

| WO2018038107A1 (ja) | 有機薄膜トランジスタとその製造方法および画像表示装置 | |

| JP6209918B2 (ja) | 薄膜トランジスタ、及び薄膜トランジスタの製造方法 | |

| JPWO2019078267A1 (ja) | 有機薄膜トランジスタ、その製造方法、アクティブマトリクスアレイおよび画像表示装置 | |

| JP6264015B2 (ja) | 薄膜トランジスタ及び薄膜トランジスタの製造方法 | |

| WO2017208923A1 (ja) | 有機薄膜トランジスタおよび画像表示装置 | |

| JP5782695B2 (ja) | 薄膜トランジスタ、薄膜トランジスタを備える画像表示装置、薄膜トランジスタの製造方法、画像表示装置の製造方法 | |

| JP5577796B2 (ja) | 薄膜トランジスタ及びその製造方法 | |

| JP2014107280A (ja) | 薄膜トランジスタ及びその製造方法 | |

| JP6286988B2 (ja) | 薄膜トランジスタの製造方法 | |

| JP2012204398A (ja) | 薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置 | |

| JP2014157907A (ja) | 薄膜トランジスタ及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120316 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131015 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131017 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131203 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140507 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140620 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20141028 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20141110 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5655277 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |