JP4597767B2 - ダイバーシチ受信機のサンプリングクロック制御方法およびダイバーシチ受信機 - Google Patents

ダイバーシチ受信機のサンプリングクロック制御方法およびダイバーシチ受信機 Download PDFInfo

- Publication number

- JP4597767B2 JP4597767B2 JP2005147907A JP2005147907A JP4597767B2 JP 4597767 B2 JP4597767 B2 JP 4597767B2 JP 2005147907 A JP2005147907 A JP 2005147907A JP 2005147907 A JP2005147907 A JP 2005147907A JP 4597767 B2 JP4597767 B2 JP 4597767B2

- Authority

- JP

- Japan

- Prior art keywords

- branch

- received

- signal

- received signal

- diversity receiver

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000005070 sampling Methods 0.000 title claims description 76

- 238000000034 method Methods 0.000 title claims description 32

- 230000015572 biosynthetic process Effects 0.000 claims description 52

- 238000003786 synthesis reaction Methods 0.000 claims description 52

- 238000004364 calculation method Methods 0.000 claims description 48

- 238000011084 recovery Methods 0.000 claims description 46

- 239000006185 dispersion Substances 0.000 claims description 2

- 238000010586 diagram Methods 0.000 description 20

- 238000001514 detection method Methods 0.000 description 14

- 230000008929 regeneration Effects 0.000 description 7

- 238000011069 regeneration method Methods 0.000 description 7

- 230000014509 gene expression Effects 0.000 description 6

- 230000005540 biological transmission Effects 0.000 description 5

- 230000006866 deterioration Effects 0.000 description 5

- 238000005562 fading Methods 0.000 description 4

- 230000015556 catabolic process Effects 0.000 description 3

- 238000006731 degradation reaction Methods 0.000 description 3

- 230000002194 synthesizing effect Effects 0.000 description 3

- 230000007423 decrease Effects 0.000 description 2

- 239000000203 mixture Substances 0.000 description 2

- 239000002131 composite material Substances 0.000 description 1

- 230000018109 developmental process Effects 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 238000010606 normalization Methods 0.000 description 1

Images

Landscapes

- Radio Transmission System (AREA)

- Mobile Radio Communication Systems (AREA)

Description

その他の方式として同期用のシンボルが挿入されている場合には同期シンボル信号と受信信号との相互相関演算を行う、いわゆる相互相関方式等もある。

Claims (12)

- 複数のアンテナによって受信したOFDM方式の受信信号を合成あるいは選択するダイバーシチ受信機において、前記複数のアンテナによって受信した受信信号を、それぞれのブランチの受信信号品質に基づいた比率で合成し、当該合成した結果に基づいて前記それぞれのブランチのA/D変換器に共通に用いられるサンプリングクロックを制御し、

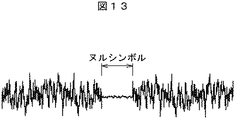

前記それぞれのブランチの受信信号品質に基づいた比率は、それぞれのブランチでの前記受信信号のキャリアレベルと雑音レベルとから算出される該受信信号のC/Nに基づく比率であり、前記雑音レベルは、ヌルシンボルの受信レベルを測定することで検出される雑音レベルか、前記受信信号と前記受信信号を有効シンボル長遅延させた信号との差分の絶対値であってガードインターバル期間内でかつマルチパスに残留成分を含まない期間の前記絶対値から算出される雑音レベルかのいずれかを用いることを特徴とするダイバーシチ受信機のサンプリングクロック制御方法。 - 複数のアンテナの信号を受信したOFDM方式の受信信号を合成あるいは選択するダイバーシチ受信機において、前記複数のアンテナによって受信した受信信号と該受信信号を有効シンボル長遅延させた信号との自己相関演算結果の信号、あるいは前記受信信号と所定の同期用シンボル信号との相互相関演算結果の信号のいずれかの信号を、それぞれのブランチの受信信号品質に基づいた比率で合成し、当該合成結果に基づいて前記それぞれのブランチのA/D変換器に共通に用いられるサンプリングクロックを制御し、

前記それぞれのブランチの受信信号品質に基づいた比率は、それぞれのブランチでの前記受信信号のキャリアレベルと雑音レベルとから算出される該受信信号のC/Nに基づく比率であり、前記雑音レベルは、ヌルシンボルの受信レベルを測定することで検出される雑音レベルか、前記受信信号と前記受信信号を有効シンボル長遅延させた信号との差分の絶対値であってガードインターバル期間内でかつマルチパスに残留成分を含まない期間の前記絶対値から算出される雑音レベルかのいずれかを用いることを特徴とするダイバーシチ受信機のサンプリングクロック制御方法。 - 複数のアンテナの信号を受信したOFDM方式の受信信号を合成あるいは選択するダイバーシチ受信機において、前記ダイバーシチ受信機の再生クロックにより生成した基準タイミングと、それぞれのブランチの受信サンプル系列から算出した特定のタイミングとの位相差を、それぞれのブランチの受信信号品質に基づいた比率で合成し、当該合成結果に基づいて前記それぞれのブランチのA/D変換器に共通に用いられるサンプリングクロックを制御し、

前記それぞれのブランチの受信信号品質に基づいた比率は、それぞれのブランチでの前記受信信号のキャリアレベルと雑音レベルとから算出される該受信信号のC/Nに基づく比率であり、前記雑音レベルは、ヌルシンボルの受信レベルを測定することで検出される雑音レベルか、前記受信信号と前記受信信号を有効シンボル長遅延させた信号との差分の絶対値であってガードインターバル期間内でかつマルチパスに残留成分を含まない期間の前記絶対値から算出される雑音レベルかのいずれかを用いることを特徴とするダイバーシチ受信機のサンプリングクロック制御方法。 - 複数のアンテナの信号を受信したOFDM方式の受信信号を合成あるいは選択するダイバーシチ受信機において、それぞれのブランチで独立のサンプリングクロック再生処理を行い、それぞれのサンプリングクロックを、それぞれのブランチの受信信号品質に基づいた比率で合成し、当該合成結果に基づいて前記ダイバーシチ受信機のサンプリングクロックを制御し、

前記それぞれのブランチの受信信号品質に基づいた比率は、それぞれのブランチでの前記受信信号のキャリアレベルと雑音レベルとから算出される該受信信号のC/Nに基づく比率であり、前記雑音レベルは、ヌルシンボルの受信レベルを測定することで検出される雑音レベルか、前記受信信号と前記受信信号を有効シンボル長遅延させた信号との差分の絶対値であってガードインターバル期間内でかつマルチパスに残留成分を含まない期間の前記絶対値から算出される雑音レベルかのいずれかを用いることを特徴とするダイバーシチ受信機のサンプリングクロック制御方法。 - 複数のアンテナの信号を受信したOFDM方式の受信信号を合成あるいは選択するダイバーシチ受信機において、それぞれのブランチで独立のサンプリングクロック再生処理を行い、それぞれのブランチ毎のサンプリングクロックから生成したタイミングと、それぞれのブランチのサンプリングクロックとは別の前記ダイバーシチ受信機の再生クロックにより生成した基準タイミングとの位相差を、それぞれのブランチの受信信号品質に基づいた比率で合成し、当該合成結果に基づいて前記ダイバーシチ受信機のサンプリングクロックを制御し、

前記それぞれのブランチの受信信号品質に基づいた比率は、それぞれのブランチでの前記受信信号のキャリアレベルと雑音レベルとから算出される該受信信号のC/Nに基づく比率であり、前記雑音レベルは、ヌルシンボルの受信レベルを測定することで検出される雑音レベルか、前記受信信号と前記受信信号を有効シンボル長遅延させた信号との差分の絶対値であってガードインターバル期間内でかつマルチパスに残留成分を含まない期間の前記絶対値から算出される雑音レベルかのいずれかを用いることを特徴とするダイバーシチ受信機のサンプリングクロック制御方法。 - 前記受信信号品質に基づいた比率は、それぞれのブランチでの前記受信信号のキャリアレベルに比例し、雑音レベルの二乗に反比例した比率か、それを正規化させた比率のいずれかを用いることを特徴とする請求項1、2或いは4に記載のダイバーシチ受信機のサンプリングクロック制御方法。

- 複数のアンテナによって受信したOFDM方式の受信信号を合成あるいは選択するダイバーシチ受信機において、前記複数のアンテナによって受信した受信信号を、それぞれのブランチの受信信号品質に基づいた比率で合成し、当該合成した結果に基づいて前記それぞれのブランチのA/D変換器に共通に用いられるサンプリングクロックを制御するクロック再生部を備え、

前記それぞれのブランチの受信信号品質に基づいた比率は、それぞれのブランチでの前記受信信号のキャリアレベルと雑音レベルとから算出される該受信信号のC/Nに基づく比率であり、前記雑音レベルは、ヌルシンボルの受信レベルを測定することで検出される雑音レベルか、前記受信信号と前記受信信号を有効シンボル長遅延させた信号との差分の絶対値であってガードインターバル期間内でかつマルチパスに残留成分を含まない期間の前記絶対値から算出される雑音レベルかのいずれかを用いることを特徴とするダイバーシチ受信機。 - 複数のアンテナの信号を受信したOFDM方式の受信信号を合成あるいは選択するダイバーシチ受信機において、前記複数のアンテナによって受信した受信信信号と該受信信号を有効シンボル長遅延させた信号との自己相関演算結果の信号、あるいは前記受信信号と所定の同期用シンボル信号との相互相関演算結果の信号のいずれかの信号を、それぞれのブランチの受信信号品質に基づいた比率で合成し、当該合成結果に基づいて前記それぞれのブランチのA/D変換器に共通に用いられるサンプリングクロックを制御するクロック再生部を備え、

前記それぞれのブランチの受信信号品質に基づいた比率は、それぞれのブランチでの前記受信信号のキャリアレベルと雑音レベルとから算出される該受信信号のC/Nに基づく比率であり、前記雑音レベルは、ヌルシンボルの受信レベルを測定することで検出される雑音レベルか、前記受信信号と前記受信信号を有効シンボル長遅延させた信号との差分の絶対値であってガードインターバル期間内でかつマルチパスに残留成分を含まない期間の前記絶対値から算出される雑音レベルかのいずれかを用いることを特徴とするダイバーシチ受信機。 - 複数のアンテナの信号を受信したOFDM方式の受信信号を合成あるいは選択するダイバーシチ受信機において、前記ダイバーシチ受信機の再生クロックにより生成した基準タイミングと、それぞれのブランチの受信サンプル系列から算出した特定のタイミングとの位相差を、それぞれのブランチの受信信号品質に基づいた比率で合成し、当該合成結果に基づいて前記それぞれのブランチのA/D変換器に共通に用いられるサンプリングクロックを制御するクロック再生部を備え、

前記それぞれのブランチの受信信号品質に基づいた比率は、それぞれのブランチでの前記受信信号のキャリアレベルと雑音レベルとから算出される該受信信号のC/Nに基づく比率であり、前記雑音レベルは、ヌルシンボルの受信レベルを測定することで検出される雑音レベルか、前記受信信号と前記受信信号を有効シンボル長遅延させた信号との差分の絶対値であってガードインターバル期間内でかつマルチパスに残留成分を含まない期間の前記絶対値から算出される雑音レベルかのいずれかを用いることを特徴とするダイバーシチ受信機。 - 複数のアンテナの信号を受信したOFDM方式の受信信号を合成あるいは選択するダイバーシチ受信機において、それぞれのブランチで独立のサンプリングクロック再生処理を行い、それぞれのサンプリングクロックを、それぞれのブランチの受信信号品質に基づいた比率で合成し、当該合成結果に基づいて前記ダイバーシチ受信機のサンプリングクロックを制御するクロック再生部を備え、

前記それぞれのブランチの受信信号品質に基づいた比率は、それぞれのブランチでの前記受信信号のキャリアレベルと雑音レベルとから算出される該受信信号のC/Nに基づく比率であり、前記雑音レベルは、ヌルシンボルの受信レベルを測定することで検出される雑音レベルか、前記受信信号と前記受信信号を有効シンボル長遅延させた信号との差分の絶対値であってガードインターバル期間内でかつマルチパスに残留成分を含まない期間の前記絶対値から算出される雑音レベルかのいずれかを用いることを特徴とするダイバーシチ受信機。 - 複数のアンテナの信号を受信したOFDM方式の受信信号を合成あるいは選択するダイバーシチ受信機において、それぞれのブランチで独立のサンプリングクロック再生処理を行い、それぞれのブランチ毎のサンプリングクロックから生成したタイミングと、それぞれのブランチのサンプリングクロックとは別の前記ダイバーシチ受信機の再生クロックにより生成した基準タイミングとの位相差を、それぞれのブランチの受信信号品質に基づいた比率で合成し、当該合成結果に基づいて前記ダイバーシチ受信機のサンプリングクロックを制御するクロック再生部を備え、

前記それぞれのブランチの受信信号品質に基づいた比率は、それぞれのブランチでの前記受信信号のキャリアレベルと雑音レベルとから算出される該受信信号のC/Nに基づく比率であり、前記雑音レベルは、ヌルシンボルの受信レベルを測定することで検出される雑音レベルか、前記受信信号と前記受信信号を有効シンボル長遅延させた信号との差分の絶対値であってガードインターバル期間内でかつマルチパスに残留成分を含まない期間の前記絶対値から算出される雑音レベルかのいずれかを用いることを特徴とするダイバーシチ受信機。 - 前記受信信号品質に基づいた比率は、前記位相差の分散値の逆数や前記位相差の標準偏差値の逆数のいずれかを用いることを特徴とする請求項3或いは5に記載のダイバーシチ受信機のサンプリングクロック制御方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005147907A JP4597767B2 (ja) | 2005-05-20 | 2005-05-20 | ダイバーシチ受信機のサンプリングクロック制御方法およびダイバーシチ受信機 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005147907A JP4597767B2 (ja) | 2005-05-20 | 2005-05-20 | ダイバーシチ受信機のサンプリングクロック制御方法およびダイバーシチ受信機 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006325077A JP2006325077A (ja) | 2006-11-30 |

| JP4597767B2 true JP4597767B2 (ja) | 2010-12-15 |

Family

ID=37544396

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005147907A Active JP4597767B2 (ja) | 2005-05-20 | 2005-05-20 | ダイバーシチ受信機のサンプリングクロック制御方法およびダイバーシチ受信機 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4597767B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009094839A (ja) * | 2007-10-10 | 2009-04-30 | Fujitsu Microelectronics Ltd | Ofdm受信装置 |

| JP5408305B2 (ja) * | 2012-07-02 | 2014-02-05 | 富士通セミコンダクター株式会社 | Ofdm受信装置 |

| JP6984734B2 (ja) * | 2018-03-23 | 2021-12-22 | 日本電気株式会社 | 制御装置、遅延差調整方法、及び遅延差調整プログラム |

| JP7574071B2 (ja) | 2020-12-21 | 2024-10-28 | 日本放送協会 | 受信装置 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04150320A (ja) * | 1990-10-11 | 1992-05-22 | Nec Corp | ダイバシティ受信装置 |

| JPH0918399A (ja) * | 1995-07-03 | 1997-01-17 | Nippon Telegr & Teleph Corp <Ntt> | 検波後ダイバーシチ受信回路 |

| JPH114186A (ja) * | 1997-06-12 | 1999-01-06 | Mitsubishi Electric Corp | 合成ダイバーシチ受信機 |

| JP2001168833A (ja) * | 1999-12-08 | 2001-06-22 | Toshiba Corp | Ofdm受信装置 |

| JP2002026867A (ja) * | 2000-07-12 | 2002-01-25 | Toshiba Corp | データ選択復調装置 |

-

2005

- 2005-05-20 JP JP2005147907A patent/JP4597767B2/ja active Active

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04150320A (ja) * | 1990-10-11 | 1992-05-22 | Nec Corp | ダイバシティ受信装置 |

| JPH0918399A (ja) * | 1995-07-03 | 1997-01-17 | Nippon Telegr & Teleph Corp <Ntt> | 検波後ダイバーシチ受信回路 |

| JPH114186A (ja) * | 1997-06-12 | 1999-01-06 | Mitsubishi Electric Corp | 合成ダイバーシチ受信機 |

| JP2001168833A (ja) * | 1999-12-08 | 2001-06-22 | Toshiba Corp | Ofdm受信装置 |

| JP2002026867A (ja) * | 2000-07-12 | 2002-01-25 | Toshiba Corp | データ選択復調装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2006325077A (ja) | 2006-11-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP1618696B1 (en) | Frequency synchronization apparatus and frequency synchronization method | |

| JP4938679B2 (ja) | キャリア間干渉除去装置及びこれを用いた受信装置 | |

| EP1349337B1 (en) | Multicarrier reception with interference detection | |

| EP1742401A1 (en) | Ofdm receiver apparatus and ofdm receiving method | |

| JP3836125B1 (ja) | 復調装置、受信装置及び復調方法 | |

| JP4317335B2 (ja) | ダイバーシティ受信機 | |

| JP5624527B2 (ja) | シングルキャリア受信装置 | |

| KR100778919B1 (ko) | 패턴 시퀀스의 동기화 | |

| JP4597767B2 (ja) | ダイバーシチ受信機のサンプリングクロック制御方法およびダイバーシチ受信機 | |

| JP2005260331A (ja) | Ofdm受信装置 | |

| JP4424378B2 (ja) | フレーム同期装置及びその制御方法 | |

| JP4044022B2 (ja) | Mfsk受信システム | |

| JP4520825B2 (ja) | ガードインターバル検出装置およびガードインターバル検出方法、並びに、周波数オフセット検出装置 | |

| US7539167B2 (en) | Spread spectrum receiver and method for carrier frequency offset compensation in such a spread spectrum receiver | |

| EP4012933A1 (en) | Lora advanced receiver | |

| US7463692B2 (en) | Device and method for symbol clock recovery in digital television | |

| KR100585965B1 (ko) | 수신기 위상 보정장치 및 그 방법 | |

| JP5509672B2 (ja) | ダイバーシチ受信装置及びダイバーシチ受信方法 | |

| JP5599677B2 (ja) | ダイバシティ受信装置及びダイバシティ受信方法 | |

| JP2001223668A (ja) | 受信タイミング検出回路、周波数オフセット補正回路、受信装置及びその受信方法 | |

| JP4463738B2 (ja) | Ofdm受信装置 | |

| JP2008104015A (ja) | 自動周波数制御装置、受信機、通信装置および通信システム | |

| JP2005229207A (ja) | Ofdm受信装置、および、ofdm受信信号のオフセット補正方法 | |

| JP4745410B2 (ja) | 無線通信復調装置 | |

| US7936847B2 (en) | Removal of matched waveform interference |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080416 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100527 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100622 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20100803 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20100803 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100820 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100907 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100922 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4597767 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131001 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |