JP2014086431A - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP2014086431A JP2014086431A JP2012231399A JP2012231399A JP2014086431A JP 2014086431 A JP2014086431 A JP 2014086431A JP 2012231399 A JP2012231399 A JP 2012231399A JP 2012231399 A JP2012231399 A JP 2012231399A JP 2014086431 A JP2014086431 A JP 2014086431A

- Authority

- JP

- Japan

- Prior art keywords

- region

- electrode

- drift region

- source

- semiconductor device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 104

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 25

- 239000000758 substrate Substances 0.000 claims abstract description 34

- 230000002093 peripheral effect Effects 0.000 claims description 26

- 238000005468 ion implantation Methods 0.000 claims description 6

- 230000020169 heat generation Effects 0.000 abstract description 5

- 239000000126 substance Substances 0.000 abstract 2

- 230000000149 penetrating effect Effects 0.000 abstract 1

- 238000000034 method Methods 0.000 description 26

- 239000012535 impurity Substances 0.000 description 10

- 239000000463 material Substances 0.000 description 10

- 238000005530 etching Methods 0.000 description 8

- 239000011229 interlayer Substances 0.000 description 7

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 4

- 238000001312 dry etching Methods 0.000 description 4

- 239000010410 layer Substances 0.000 description 4

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 4

- 230000004888 barrier function Effects 0.000 description 3

- 238000010438 heat treatment Methods 0.000 description 3

- 229920002120 photoresistant polymer Polymers 0.000 description 3

- 229910010271 silicon carbide Inorganic materials 0.000 description 3

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 2

- QAOWNCQODCNURD-UHFFFAOYSA-N Sulfuric acid Chemical compound OS(O)(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-N 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 239000002772 conduction electron Substances 0.000 description 2

- 230000005684 electric field Effects 0.000 description 2

- 238000010992 reflux Methods 0.000 description 2

- 238000001039 wet etching Methods 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 239000012298 atmosphere Substances 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 1

- 238000001020 plasma etching Methods 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/7813—Vertical DMOS transistors, i.e. VDMOS transistors with trench gate electrode, e.g. UMOS transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66053—Multistep manufacturing processes of devices having a semiconductor body comprising crystalline silicon carbide

- H01L29/66068—Multistep manufacturing processes of devices having a semiconductor body comprising crystalline silicon carbide the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/7803—Vertical DMOS transistors, i.e. VDMOS transistors structurally associated with at least one other device

- H01L29/7804—Vertical DMOS transistors, i.e. VDMOS transistors structurally associated with at least one other device the other device being a pn-junction diode

- H01L29/7805—Vertical DMOS transistors, i.e. VDMOS transistors structurally associated with at least one other device the other device being a pn-junction diode in antiparallel, e.g. freewheel diode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/7811—Vertical DMOS transistors, i.e. VDMOS transistors with an edge termination structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/16—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only elements of Group IV of the Periodic Table

- H01L29/1608—Silicon carbide

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Computer Hardware Design (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Manufacturing & Machinery (AREA)

- Electrodes Of Semiconductors (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Abstract

【課題】並列接続されたMOSトランジスタとダイオードが同一基板上に形成され、且つ半導体素子に流れる電流による内部での発熱の集中が抑制された半導体装置及びその製造方法を提供する。

【解決手段】半導体基体上に配置されたドリフト領域と、ドリフト領域の上部に埋め込まれたウェル領域と、ウェル領域の上部に埋め込まれたソース領域と、ソース領域とウェル領域を貫通し、底部がドリフト領域に達する溝の内壁に配置されたゲート絶縁膜と、溝の内部に埋め込まれたゲート電極と、ゲート電極の周囲でソース領域と電気的に接続するソース電極と、半導体基体を介してドリフト領域と電気的に接続するドレイン電極と、ゲート電極及びソース電極が配置された領域として定義されるセル領域の周囲においてドリフト領域上に配置され、ドリフト領域との間でヘテロ接合を形成するアノード電極とを備える。

【選択図】図1

【解決手段】半導体基体上に配置されたドリフト領域と、ドリフト領域の上部に埋め込まれたウェル領域と、ウェル領域の上部に埋め込まれたソース領域と、ソース領域とウェル領域を貫通し、底部がドリフト領域に達する溝の内壁に配置されたゲート絶縁膜と、溝の内部に埋め込まれたゲート電極と、ゲート電極の周囲でソース領域と電気的に接続するソース電極と、半導体基体を介してドリフト領域と電気的に接続するドレイン電極と、ゲート電極及びソース電極が配置された領域として定義されるセル領域の周囲においてドリフト領域上に配置され、ドリフト領域との間でヘテロ接合を形成するアノード電極とを備える。

【選択図】図1

Description

本発明は、複数の半導体素子を同一半導体基板上に形成した半導体装置及びその製造方法に関する。

半導体装置の面積の増大を抑制するために、同一半導体基板上に複数の半導体素子を形成する方法が採用されている。例えば、並列接続されたMOSトランジスタとダイオードとを同一半導体基板に形成する方法が提案されている(例えば、特許文献1参照)。

しかしながら、MOSトランジスタとダイオードとを同一半導体基板に形成した場合に、これらの素子が隣接して配置されていると、MOSトランジスタが導通状態になって電流が流れる経路(即ち、ソース電極からドレイン電極への経路)とダイオードの順方向に流れる電流の経路(即ち、アノード電極からカソード電極への経路)が近接する。このため、MOSトランジスタの導通とダイオードの導通が交互に繰り返される使い方の場合に、電流が流れることによる発熱が内部に集中するという問題があった。

上記問題点に鑑み、本発明の目的は、並列接続されたMOSトランジスタとダイオードが同一基板上に形成され、且つこれらの半導体素子に流れる電流による内部での発熱の集中が抑制された半導体装置及びその製造方法を提供することである。

本発明は、半導体基体上にそれぞれ配置された第1導電型のドリフト領域、第2導電型のウェル領域及び第1導電型のソース領域と、ソース領域とウェル領域を貫通して底部がドリフト領域に達する溝の内壁に配置されたゲート絶縁膜と、溝の内部に埋め込まれたゲート電極と、ソース領域と電気的に接続するソース電極と、半導体基体を介してドリフト領域と電気的に接続するドレイン電極と、ゲート電極及びソース電極が配置された領域として定義されるセル領域の周囲においてドリフト領域上に配置され、ドリフト領域との間でヘテロ接合を形成するアノード電極とを備える。

本発明によれば、MOSトランジスタとダイオードが分離して配置されるので、これらの半導体素子に流れる電流による内部での発熱の集中が抑制された半導体装置及びその製造方法を提供することができる。

次に、図面を参照して、本発明の実施形態を説明する。以下の図面の記載において、同一又は類似の部分には同一又は類似の符号を付している。ただし、図面は模式的なものであり、厚みと平面寸法との関係、各層の厚みの比率等は現実のものとは異なることに留意すべきである。したがって、具体的な厚みや寸法は以下の説明を参酌して判断すべきものである。又、図面相互間においても互いの寸法の関係や比率が異なる部分が含まれていることはもちろんである。

又、以下に示す実施形態は、この発明の技術的思想を具体化するための装置や方法を例示するものであって、この発明の実施形態は、構成部品の材質、形状、構造、配置等を下記のものに特定するものでない。この発明の実施形態は、特許請求の範囲において、種々の変更を加えることができる。

(第1の実施形態)

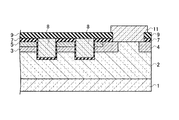

本発明の第1の実施形態に係る半導体装置100は、図1に示すように、半導体基体1と、半導体基体1上に配置された第1導電型のドリフト領域2と、ドリフト領域2の上部の一部に埋め込まれた第2導電型のウェル領域3と、ウェル領域3の上部の一部に埋め込まれた第1導電型のソース領域5と、ソース領域5とウェル領域3を貫通し、底部がドリフト領域2に達する溝の内壁に配置されたゲート絶縁膜7と、溝の内部に埋め込まれたゲート電極8とを備える。ソース領域5はソース電極13と電気的に接続され、半導体基体1はドレイン電極14と接続されている。

本発明の第1の実施形態に係る半導体装置100は、図1に示すように、半導体基体1と、半導体基体1上に配置された第1導電型のドリフト領域2と、ドリフト領域2の上部の一部に埋め込まれた第2導電型のウェル領域3と、ウェル領域3の上部の一部に埋め込まれた第1導電型のソース領域5と、ソース領域5とウェル領域3を貫通し、底部がドリフト領域2に達する溝の内壁に配置されたゲート絶縁膜7と、溝の内部に埋め込まれたゲート電極8とを備える。ソース領域5はソース電極13と電気的に接続され、半導体基体1はドレイン電極14と接続されている。

図1に示した半導体装置100は、ゲート電極8及びソース電極13が配置された領域として定義されるセル領域210の周囲においてドリフト領域2上に配置され、ドリフト領域2との間でヘテロ接合を形成するアノード電極11を更に備える。

第1導電型と第2導電型とは互いに反対導電型である。すなわち、第1導電型がN型であれば、第2導電型はP型であり、第1導電型がP型であれば、第2導電型はN型である。以下では、第1導電型がN型、第2導電型がP型の場合を例示的に説明する。なお、半導体基体1は高濃度のN型の炭化珪素(SiC)基体であるとし、ドリフト領域2は低濃度のN型のSiC層であるとする。

ソース電極13は、セル領域210においてソース領域5の上方に配置されている。ゲート電極8の上方に配置されたソース電極13とゲート電極8とは、ソース領域5上及びウェル領域3上に配置された層間絶縁膜9によって絶縁分離されている。そして、ゲート電極8が埋め込まれた溝の周囲に設けられた層間絶縁膜9の開口部において、ソース領域5とソース電極13が接続している。

ゲート電極8は、ゲート絶縁膜7を介して、ドリフト領域2、ウェル領域3及びN+型ソース領域5と対向している。ゲート電極8は、例えば第1導電型(N型)のポリシリコンゲート電極である。

上記のドリフト領域2、ウェル領域3、ソース領域5、ゲート電極8などによって、セル領域210にトレンチ構造のMOSトランジスタが構成される。

図1に示すように、セル領域210の周囲の領域(以下において「外周領域220」という。)において、アノード電極11の下部が、層間絶縁膜9、及びウェル領域3上に延伸したゲート絶縁膜7に形成された溝に埋め込まれている。そして、外周領域220でウェル領域3の外周を囲むドリフト領域2の上面と、アノード電極11の下部とが接触している。これにより、アノード電極11とドリフト領域2との間でヘテロ接合が形成され、外周領域220においてヘテロ接合ダイオードが構成される。

アノード電極11としては、アノード電極11とドリフト領域2との界面にヘテロ接合が形成されるように、例えばP型の半導体膜などを採用可能である。

上記のように、図1に示した半導体装置100は、セル領域210にMOSトランジスタが配置され、セル領域210の周囲の外周領域220にヘテロ接合ダイオードが配置された構造である。

上記のように、図1に示した半導体装置100は、セル領域210にMOSトランジスタが配置され、セル領域210の周囲の外周領域220にヘテロ接合ダイオードが配置された構造である。

図1に示した例では、半導体基体1の第1の主面101上にドリフト領域2が配置され、半導体基体1の第1の主面101に対向する第2の主面102上にドレイン電極14が配置されている。これにより、半導体基体1を介してドリフト領域2とドレイン電極14が電気的に接続されている。また、アノード電極11とドリフト領域2によって構成されるヘテロ接合ダイオードのカソード電極としてもドレイン電極14は機能する。つまり、セル領域210に形成されたMOSトランジスタと外周領域220に形成されたヘテロ接合ダイオードとは、並列接続されている。

ドリフト領域2の外縁部には、半導体基体1の外縁に沿ってドリフト領域2の上部の一部に埋め込まれた周辺ガードリング4が配置されている。周辺ガードリング4により、半導体装置1の端部における電界を緩和することができる。図1に示した例では、アノード電極11が周辺ガードリング4に接している。より具体的には、アノード電極11の底部のうち半導体基体1の外縁側の端部が、周辺ガードリング4の内側の上面に接している。

なお、ゲート電極8にゲート端子180、ソース電極13にソース端子130、ドレイン電極14のドレイン端子140、アノード電極11にアノード端子110が、それぞれ電気的に接続されている。これらの端子によって、半導体装置100の電気的な入出力が行われる。

以下に、半導体装置100の基本的な動作例を説明する。以下の説明では、例えばインバータなどの電力変換装置の電力変換素子として半導体装置100が使用される場合を想定し、順方向動作ではスイッチング素子として動作し、いわゆる還流動作である逆方向動作では受動素子として動作する。

先ず、順方向動作について説明する。ソース電極13の電位を基準としてドレイン電極14に正の電圧を印加した状態で、ゲート電極8の電圧を変化させる。これにより、ソース電極13とドレイン電極14間に流れる電流を制御することができる。

具体的には、しきい値電圧以上の正の電圧をゲート電極8に印加すると、ウェル領域3とゲート絶縁膜7の界面に反転層が形成され、伝導電子が発生する。このため、ソース電極13とドレイン電極14間に電流が流れる。

一方、ゲート電極8に印加する電圧がしきい値電圧よりも低い場合には、反転層は形成されない。このため、ソース電極13とドレイン電極14間に電流は流れない。

次に、逆方向動作について説明する。ソース電極13の電位を基準としてドレイン電極14に負の電圧を印加した場合に、アノードがアノード電極11であり、カソードがドリフト領域2であるヘテロ接合ダイオードに、還流電流が流れる。

即ち、ドリフト領域2からアノード電極11に向けては伝導電子に対するエネルギー障壁がほぼないために電子電流が流れる。これに対し、アノード電極11からドリフト領域2に向けては正孔(ホール)に対するエネルギー障壁が存在しているためにホール電流はほとんど流れない。つまり、アノード電極11とドリフト領域2により構成されるヘテロ接合ダイオードは、多数キャリア受動素子として動作する。

なお、しきい値電圧を負の方向にシフトさせ、最大電圧までゲート電圧を印加した時のドレイン電流を大きくするために、第1導電型の半導体膜をゲート電極8に使用することが好ましい。また、逆方向耐圧を高くするために、第1導電型のドリフト領域2との間のエネルギー障壁が高くなる第2導電型の半導体膜をアノード電極11に用いることが好ましい。

セル領域210には、任意の個数、形状のMOSトランジスタを配置できる。例えば、図2に示すように、半導体装置100の主面上に複数のMOSトランジスタを配置し、その周囲に環状のアノード電極11を配置してもよい。より具体的には、半導体基体1の中心領域のセル領域210に、マトリクス状に配置された複数のソース領域5、各MOSトランジスタのソース電極13にそれぞれ接続するソースパッド16、及びゲート電極8に接続するゲートパッド15が配置されている。そして、セル領域210の周囲を囲んで、環状のアノード電極11が配置されている。また、アノード電極11の周囲には、半導体基体1の外縁部に沿って環状の周辺ガードリング4が配置されている。

以上に説明したように、本発明の第1の実施形態に係る半導体装置100では、MOSトランジスタとヘテロ接合ダイオードとが分離して同一半導体基板上に配置される。このため、MOSトランジスタに流れる電流に起因して発熱の生じる箇所と、ヘテロ接合ダイオードに流れる電流に起因して発熱の生じる箇所を分離することができる。その結果、順方向動作にMOSトランジスタが導通して電流が流れ、逆方向動作時にヘテロ接合ダイオードに電流が流れることが交互に繰り返されても、半導体装置100によれば、半導体素子に流れる電流による内部での発熱の集中を抑制することができる。

更に、周辺ガードリング4上にアノード電極11の外縁部を配置することにより、周辺ガードリング4のスペースを有効に活用することができる。

図3〜図13を参照して、本発明の第1の実施形態に係る半導体装置100の製造方法を説明する。なお、以下に述べる半導体装置100の製造方法は一例であり、この変形例を含めて、これ以外の種々の製造方法により実現可能であることは勿論である。

先ず、図3に示すように、N+型炭化珪素からなる半導体基体1の第1の主面101上に、N-型炭化珪素からなるドリフト領域2をエピタキシャル成長などにより形成する。

次に、図4に示すように、イオン注入によってドリフト領域2に第2導電型のウェル領域3及び周辺ガードリング4を選択的に形成し、更にウェル領域3に第1導電型のソース領域5を選択的に形成する。これらの領域が選択的に形成されるようにイオン注入する領域をパターニングするためには、例えば下記に示す工程のように、ドリフト領域2上方に形成したマスク材を使用する。

マスク材には、シリコン酸化膜などが用いらる。また、マスク材の堆積方法としては、熱化学気相成長(CVD)法やプラズマCVD法などが採用可能である。堆積されたマスク材上に形成されたフォトレジスト膜をフォトリソグラフィ技術を用いてパターニングし、このフォトレジスト膜をエッチングマスクとしてマスク材をエッチングする。エッチング方法としては、フッ酸を用いたウェットエッチング法や、反応性イオンエッチングなどのドライエッチング法が使用される。以上により、イオン注入される領域に開口部を有するようにマスク材がパターニングされる。その後、フォトレジスト膜を酸素プラズマや硫酸などを用いて除去する。

次いで、パターニングされたマスク材をマスクにして、第2導電型不純物又は第1導電型不純物をそれぞれイオン注入し、所定の位置に第2導電型のウェル領域3や周辺ガードリング4、第1導電型のソース領域5をそれぞれ形成する。第2導電型不純物としては、アルミニウム(Al)やボロン(B)などが用いられる。第1導電型不純物としては、砒素(As)や窒素(N)などが用いられる。なお、半導体基体1の基体温度を600℃程度に加熱して状態でイオン注入することにより、イオン注入領域に結晶欠陥が生じるのを抑制することができる。

イオン注入後、マスク材を例えばフッ酸を用いたウェットエッチングによって除去する。次いで、イオン注入した不純物を熱処理によって活性化する。熱処理温度は例えば1700℃程度である。好適には、アルゴン(Ar)雰囲気中や窒素雰囲気中で熱処理が行われる。以上により、ウェル領域3、周辺ガードリング4及びソース領域5が形成される。

次に、図5に示すように、ソース領域5とウェル領域3を貫通し、底部がドリフト領域2に達する溝6を、セル領域210に形成する。例えば、先ずドリフト領域2の上方に図示を省略するエッチング用マスクを形成する。エッチング用マスクの材料として絶縁膜などが使用され、溝6を形成する領域に開口部が形成されるようにエッチング用マスクはパターニングされている。そして、エッチング用マスクをマスクにしてソース領域5、ウェル領域3及びドリフト領域2の一部をエッチング除去し、溝6を形成する。溝6の形成には、ドライエッチング法が採用可能である。図5に示すように、溝6の深さはウェル領域3の深さよりも深くなければならない。

次いで、図6に示すように、全面にゲート絶縁膜7を形成する。このとき、溝6の底面及び側面にもゲート絶縁膜が形成される。ゲート絶縁膜7には酸化膜などが使用され、膜厚は例えば10nm〜100nm程度である。

次に、図7に示すように、溝6を埋め込むようにして、ゲート絶縁膜7上に第1導電型(N型)不純物がドープされた第1半導体膜80を成長させる。第1導電型不純物は砒素やリン(P)などが用いられる。第1半導体膜80の成長方法としては、公知の低圧CVD法などが用いられる。そして、図8に示すように、溝6内部にのみ第1半導体膜80が残るように、第1半導体膜80の上部をエッチング除去する。その後、第1半導体膜80中の第1導電型不純物を活性化することにより、ゲート電極8が形成される。

次に、図9に示すように、全面に層間絶縁膜9を形成する。そして、ヘテロ接合ダイオードが形成される領域のゲート絶縁膜7と層間絶縁膜9をドライエッチングにより除去し、図10に示すように、ヘテロ接合ダイオード形成用の溝10を形成する。この溝10を埋め込んで、図11に示すようにアノード電極11が形成される。例えば、第2導電型(P型)不純物がドープされた第2半導体膜を形成した後、この第2半導体膜中の第2導電型不純物を活性化してアノード電極11を形成する。

その後、ソース電極13がソース領域5と接する部分のゲート絶縁膜7と層間絶縁膜9をドライエッチングにより除去し、図12に示すように、溝12を形成する。この溝12を埋め込むようにして、図13に示すように、ゲート電極8の周囲でソース領域5に接続するソース電極13がセル領域210内に形成される。更に、半導体基体1の第2の主面102上に、アノード電極11と共に外周領域220においてヘテロ接合ダイオードを構成するカソード電極を兼ねるドレイン電極14が形成される。以上により、半導体装置100が完成する。

上記のような本発明の第1の実施形態に係る半導体装置100の製造方法によれば、MOSトランジスタが形成されるセル領域210とヘテロ接合ダイオードが形成される外周領域220とを分離することにより、半導体素子に流れる電流による発熱の集中の抑制を可能にした半導体装置100を提供することができる。

(第2の実施形態)

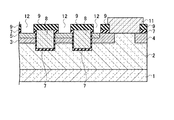

図14に、本発明の第2の実施形態に係る半導体装置100を示す。図14に示した半導体装置100は、アノード電極11の底部がウェル領域3の底面の位置よりも深い位置でドリフト領域2に接している。つまり、図1に示した半導体装置100のアノード電極11よりも、図14に示した半導体装置100の方が膜厚が厚い。更に、図14に示した半導体装置100では、アノード電極11の底部の両端部を覆うようにして、周辺ガードリング4が配置されている。つまり、図1に示した半導体装置100では、アノード電極11の底部において半導体基体1の外縁側の端部にのみ周辺ガードリング4が配置されているのに対し、図14に示した半導体装置100では、アノード電極11の底部のセル領域210に近い側の端部にも周辺ガードリング4が配置されている。

図14に、本発明の第2の実施形態に係る半導体装置100を示す。図14に示した半導体装置100は、アノード電極11の底部がウェル領域3の底面の位置よりも深い位置でドリフト領域2に接している。つまり、図1に示した半導体装置100のアノード電極11よりも、図14に示した半導体装置100の方が膜厚が厚い。更に、図14に示した半導体装置100では、アノード電極11の底部の両端部を覆うようにして、周辺ガードリング4が配置されている。つまり、図1に示した半導体装置100では、アノード電極11の底部において半導体基体1の外縁側の端部にのみ周辺ガードリング4が配置されているのに対し、図14に示した半導体装置100では、アノード電極11の底部のセル領域210に近い側の端部にも周辺ガードリング4が配置されている。

このため、図14に示した半導体装置100では、MOSトランジスタの外側の端部に周辺ガードリング4が接近する。その結果、MOSトランジスタの外部の端部における電界を、より効果的に緩和することができる。

その他の構成については、図1に示す第1の実施形態と同様であり、重複した記載を省略する。

図14に示した半導体装置100を製造するためには、周辺ガードリング4を深く形成し、アノード電極11を埋め込むヘテロ接合ダイオード形成用の溝10を図10に示した場合よりも深く形成すればよい。

上記のように、本発明は第1及び第2の実施形態によって記載したが、この開示の一部をなす論述及び図面はこの発明を限定するものであると理解すべきではない。この開示から当業者には様々な代替実施形態、実施例及び運用技術が明らかとなろう。即ち、本発明はここでは記載していない様々な実施形態等を含むことは勿論である。したがって、本発明の技術的範囲は上記の説明から妥当な特許請求の範囲に係る発明特定事項によってのみ定められるものである。

本発明の半導体装置及び半導体装置の製造方法は、トランジスタとダイオードが同一半導体基板に形成される半導体装置を製造する製造業を含む電子機器産業に利用可能である。

1…半導体基体

2…ドリフト領域

3…ウェル領域

4…周辺ガードリング

5…ソース領域

6…溝

7…ゲート絶縁膜

8…ゲート電極

9…層間絶縁膜

11…アノード電極

13…ソース電極

14…ドレイン電極

15…ゲートパッド

16…ソースパッド

100…半導体装置

101…第1の主面

102…第2の主面

210…セル領域

220…外周領域

2…ドリフト領域

3…ウェル領域

4…周辺ガードリング

5…ソース領域

6…溝

7…ゲート絶縁膜

8…ゲート電極

9…層間絶縁膜

11…アノード電極

13…ソース電極

14…ドレイン電極

15…ゲートパッド

16…ソースパッド

100…半導体装置

101…第1の主面

102…第2の主面

210…セル領域

220…外周領域

Claims (5)

- 半導体基体と、

前記半導体基体上に配置された第1導電型のドリフト領域と、

前記ドリフト領域の上部の一部に埋め込まれた第2導電型のウェル領域と、

前記ウェル領域の上部の一部に埋め込まれた第1導電型のソース領域と、

前記ソース領域と前記ウェル領域を貫通し、底部が前記ドリフト領域に達する溝の内壁に配置されたゲート絶縁膜と、

前記溝の内部に埋め込まれたゲート電極と、

前記ゲート電極の周囲で前記ソース領域と電気的に接続するソース電極と、

前記半導体基体上に配置され、前記半導体基体を介して前記ドリフト領域と電気的に接続するドレイン電極と、

前記ゲート電極及び前記ソース電極が配置された領域として定義されるセル領域の周囲において前記ドリフト領域上に配置され、前記ドリフト領域との間でヘテロ接合を形成するアノード電極と

を備えることを特徴とする半導体装置。 - 前記半導体基体の外縁部に沿って、前記ドリフト領域の上部の一部に埋め込まれた環状の周辺ガードリングを更に備えることを特徴とする請求項1に記載の半導体装置。

- 前記アノード電極が前記周辺ガードリングに接していることを特徴とする請求項2に記載の半導体装置。

- 前記アノード電極の底部の前記セル領域に近い側の端部に前記周辺ガードリングが配置されていることを特徴とする請求項3に記載の半導体装置。

- 半導体基体の第1の主面上に第1導電型のドリフト領域を形成するステップと、

イオン注入により、前記ドリフト領域の上部の一部に第2導電型のウェル領域を選択的に形成するステップと、

イオン注入により、前記ウェル領域の上部の一部に第1導電型のソース領域を選択的に形成するステップと、

前記ソース領域と前記ウェル領域を貫通し、底部が前記ドリフト領域に達する溝を形成するステップと、

前記溝の内面にゲート絶縁膜を形成するステップと、

前記溝を埋め込んで第1導電型のゲート電極を形成するステップと、

前記ゲート電極の周囲で前記ソース領域上にソース電極を形成するステップと、

前記ゲート電極及び前記ソース電極が配置された領域として定義されるセル領域の周囲において、底部が前記ドリフト領域に達し、前記ドリフト領域との間でヘテロ接合を形成するアノード電極を形成するステップと、

前記半導体基体の前記第1の主面に対向する第2の主面上に、前記アノード電極と共にヘテロ接合ダイオードを構成するカソード電極を兼ねるドレイン電極を形成するステップと

を含むことを特徴とする半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012231399A JP2014086431A (ja) | 2012-10-19 | 2012-10-19 | 半導体装置及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012231399A JP2014086431A (ja) | 2012-10-19 | 2012-10-19 | 半導体装置及びその製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2014086431A true JP2014086431A (ja) | 2014-05-12 |

Family

ID=50789258

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012231399A Pending JP2014086431A (ja) | 2012-10-19 | 2012-10-19 | 半導体装置及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2014086431A (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN108695317A (zh) * | 2017-04-06 | 2018-10-23 | 三菱电机株式会社 | 半导体装置、半导体装置的制造方法及电力变换装置 |

| JP2022009745A (ja) * | 2020-01-10 | 2022-01-14 | 株式会社東芝 | 半導体装置 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003133557A (ja) * | 2001-10-26 | 2003-05-09 | Hitachi Ltd | 半導体装置 |

| JP2010206107A (ja) * | 2009-03-05 | 2010-09-16 | Nissan Motor Co Ltd | 半導体装置 |

| JP2010225615A (ja) * | 2009-03-19 | 2010-10-07 | Denso Corp | 炭化珪素半導体装置およびその製造方法 |

| JP2012004197A (ja) * | 2010-06-15 | 2012-01-05 | Nissan Motor Co Ltd | 半導体装置及びその製造方法 |

| WO2012017878A1 (ja) * | 2010-08-02 | 2012-02-09 | 日産自動車株式会社 | 半導体装置 |

| JP2012124329A (ja) * | 2010-12-08 | 2012-06-28 | Rohm Co Ltd | SiC半導体装置 |

-

2012

- 2012-10-19 JP JP2012231399A patent/JP2014086431A/ja active Pending

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003133557A (ja) * | 2001-10-26 | 2003-05-09 | Hitachi Ltd | 半導体装置 |

| JP2010206107A (ja) * | 2009-03-05 | 2010-09-16 | Nissan Motor Co Ltd | 半導体装置 |

| JP2010225615A (ja) * | 2009-03-19 | 2010-10-07 | Denso Corp | 炭化珪素半導体装置およびその製造方法 |

| JP2012004197A (ja) * | 2010-06-15 | 2012-01-05 | Nissan Motor Co Ltd | 半導体装置及びその製造方法 |

| WO2012017878A1 (ja) * | 2010-08-02 | 2012-02-09 | 日産自動車株式会社 | 半導体装置 |

| JP2012124329A (ja) * | 2010-12-08 | 2012-06-28 | Rohm Co Ltd | SiC半導体装置 |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN108695317A (zh) * | 2017-04-06 | 2018-10-23 | 三菱电机株式会社 | 半导体装置、半导体装置的制造方法及电力变换装置 |

| JP2018181949A (ja) * | 2017-04-06 | 2018-11-15 | 三菱電機株式会社 | 半導体装置、半導体装置の製造方法、および電力変換装置 |

| US10957691B2 (en) | 2017-04-06 | 2021-03-23 | Mitsubishi Electric Corporation | Semiconductor device, semiconductor device manufacturing method, and power conversion apparatus |

| JP2022009745A (ja) * | 2020-01-10 | 2022-01-14 | 株式会社東芝 | 半導体装置 |

| JP7196265B2 (ja) | 2020-01-10 | 2022-12-26 | 株式会社東芝 | 半導体装置 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5565461B2 (ja) | 半導体装置 | |

| JP5691259B2 (ja) | 半導体装置 | |

| US20110012132A1 (en) | Semiconductor Device | |

| US10361266B2 (en) | Semiconductor device | |

| WO2011033550A1 (ja) | 半導体装置 | |

| JP2017092368A (ja) | 半導体装置および半導体装置の製造方法 | |

| CN107683530B (zh) | 电力用半导体装置 | |

| JP2013222932A (ja) | 炭化珪素半導体装置およびその製造方法 | |

| JP6028807B2 (ja) | 半導体装置及びその製造方法 | |

| JP6802454B2 (ja) | 半導体装置およびその製造方法 | |

| US10032866B2 (en) | Semiconductor device and method of manufacturing semiconductor device | |

| JP2019004078A (ja) | 半導体装置および半導体装置の製造方法 | |

| JP2018082055A (ja) | 半導体装置および半導体装置の製造方法 | |

| US10756200B2 (en) | Silicon carbide semiconductor element and method of manufacturing silicon carbide semiconductor | |

| JP2018116986A (ja) | 半導体装置および半導体装置の製造方法 | |

| US8835935B2 (en) | Trench MOS transistor having a trench doped region formed deeper than the trench gate | |

| JP2019216223A (ja) | 半導体装置 | |

| JP2012186318A (ja) | 高耐圧半導体装置 | |

| CN108574000B9 (zh) | 半导体装置和半导体装置的制造方法 | |

| JP2014127547A (ja) | 半導体装置の製造方法 | |

| JP2012174895A (ja) | 高耐圧半導体装置 | |

| CN105409006A (zh) | 半导体装置 | |

| JP2012004197A (ja) | 半導体装置及びその製造方法 | |

| JP2022003711A (ja) | 半導体装置 | |

| TW201535722A (zh) | 半導體裝置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150828 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20160905 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20161004 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20170606 |