CN114823550B - Chip packaging structure and packaging method suitable for batch production - Google Patents

Chip packaging structure and packaging method suitable for batch production Download PDFInfo

- Publication number

- CN114823550B CN114823550B CN202210736592.8A CN202210736592A CN114823550B CN 114823550 B CN114823550 B CN 114823550B CN 202210736592 A CN202210736592 A CN 202210736592A CN 114823550 B CN114823550 B CN 114823550B

- Authority

- CN

- China

- Prior art keywords

- chip

- substrate

- shell

- section

- central section

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000004806 packaging method and process Methods 0.000 title claims abstract description 69

- 238000000034 method Methods 0.000 title claims abstract description 44

- 238000010923 batch production Methods 0.000 title claims abstract description 6

- 239000000758 substrate Substances 0.000 claims abstract description 115

- 230000007704 transition Effects 0.000 claims abstract description 17

- 239000000565 sealant Substances 0.000 claims description 30

- 238000012360 testing method Methods 0.000 claims description 25

- 230000008569 process Effects 0.000 claims description 20

- 229910000679 solder Inorganic materials 0.000 claims description 13

- 229910052751 metal Inorganic materials 0.000 claims description 7

- 239000002184 metal Substances 0.000 claims description 7

- QUCZBHXJAUTYHE-UHFFFAOYSA-N gold Chemical compound [Au].[Au] QUCZBHXJAUTYHE-UHFFFAOYSA-N 0.000 claims description 6

- 239000007769 metal material Substances 0.000 claims description 5

- 229920005989 resin Polymers 0.000 claims description 5

- 239000011347 resin Substances 0.000 claims description 5

- 238000005520 cutting process Methods 0.000 claims description 4

- 239000011257 shell material Substances 0.000 description 39

- 230000035939 shock Effects 0.000 description 17

- 238000010586 diagram Methods 0.000 description 15

- 238000003466 welding Methods 0.000 description 14

- 230000035882 stress Effects 0.000 description 10

- 239000000463 material Substances 0.000 description 9

- 238000004519 manufacturing process Methods 0.000 description 8

- 230000017525 heat dissipation Effects 0.000 description 7

- 230000000694 effects Effects 0.000 description 5

- 239000000945 filler Substances 0.000 description 5

- 239000000919 ceramic Substances 0.000 description 4

- 239000000523 sample Substances 0.000 description 4

- 238000012216 screening Methods 0.000 description 4

- 238000007789 sealing Methods 0.000 description 4

- 230000032683 aging Effects 0.000 description 3

- 230000009286 beneficial effect Effects 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 3

- 230000007613 environmental effect Effects 0.000 description 2

- 229920006332 epoxy adhesive Polymers 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 238000012858 packaging process Methods 0.000 description 2

- 239000013464 silicone adhesive Substances 0.000 description 2

- 238000005476 soldering Methods 0.000 description 2

- 239000000243 solution Substances 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 229910010293 ceramic material Inorganic materials 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- SBYXRAKIOMOBFF-UHFFFAOYSA-N copper tungsten Chemical compound [Cu].[W] SBYXRAKIOMOBFF-UHFFFAOYSA-N 0.000 description 1

- 238000005336 cracking Methods 0.000 description 1

- 230000001351 cycling effect Effects 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 238000005538 encapsulation Methods 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 230000004907 flux Effects 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 239000010931 gold Substances 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 238000009776 industrial production Methods 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 238000002844 melting Methods 0.000 description 1

- 230000008018 melting Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000000465 moulding Methods 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 238000013522 software testing Methods 0.000 description 1

- 238000010998 test method Methods 0.000 description 1

- 238000012795 verification Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/02—Containers; Seals

- H01L23/04—Containers; Seals characterised by the shape of the container or parts, e.g. caps, walls

- H01L23/053—Containers; Seals characterised by the shape of the container or parts, e.g. caps, walls the container being a hollow construction and having an insulating or insulated base as a mounting for the semiconductor body

- H01L23/057—Containers; Seals characterised by the shape of the container or parts, e.g. caps, walls the container being a hollow construction and having an insulating or insulated base as a mounting for the semiconductor body the leads being parallel to the base

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/52—Mounting semiconductor bodies in containers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/54—Providing fillings in containers, e.g. gas fillings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/02—Containers; Seals

- H01L23/06—Containers; Seals characterised by the material of the container or its electrical properties

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/16—Fillings or auxiliary members in containers or encapsulations, e.g. centering rings

- H01L23/18—Fillings characterised by the material, its physical or chemical properties, or its arrangement within the complete device

- H01L23/24—Fillings characterised by the material, its physical or chemical properties, or its arrangement within the complete device solid or gel at the normal operating temperature of the device

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Dispersion Chemistry (AREA)

- Structures Or Materials For Encapsulating Or Coating Semiconductor Devices Or Solid State Devices (AREA)

- Encapsulation Of And Coatings For Semiconductor Or Solid State Devices (AREA)

Abstract

The invention discloses a chip packaging structure and a packaging method suitable for batch production. The structure comprises a substrate, a chip and a shell, wherein the chip is fixedly connected with the substrate, the shell is of a semi-closed structure with a downward opening, a central section and a platform stage extend from the center of the shell to the periphery of the shell, and the bottom plane of the platform stage is lower than that of the central section in the vertical direction; the central section is connected with the step section through a transition section; the top surface of the chip is fixedly connected with the bottom surface of the central section. The packaging structure can improve the efficiency of radiating heat to the upper part of the shell, has structural integrity and stability, and can resist high temperature and high thermal impact.

Description

Technical Field

The invention relates to the technical field of integrated circuit packaging, in particular to a chip packaging structure and a chip packaging method suitable for batch production.

Background

The package structure of an integrated circuit may be defined as a portion of the integrated circuit structure that is used to provide electrical connections to the outside, as well as mechanical and environmental protection for the integrated circuit chip. Environmental protection refers to the protection of an integrated circuit chip from the environment and other electronic devices. Therefore, the package structure of the integrated circuit is generally used not only for mechanically supporting the chip, but more importantly, as a container for holding and protecting the chip. In addition, the package structure of the integrated circuit has the function of diffusing heat removal generated by the chip or system, allowing electrical signals to enter and exit the chip to provide interconnections between chips of the electronic system.

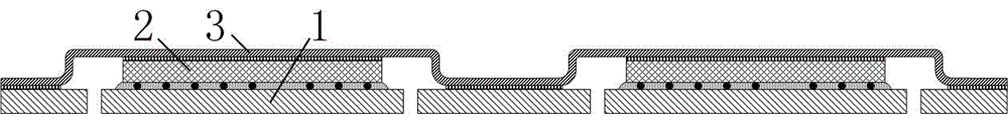

The existing chip packaging structure adopting molding packaging cannot achieve high-reliability chip indexes such as high temperature resistance and high thermal shock resistance in a special application environment due to inherent defects of materials, and cannot meet the application in a special scene. In order to improve the heat dissipation performance of the chip package structure, chinese patent application with publication number CN111341741A proposes a power device package structure with improved heat dissipation performance. Fig. 1 shows its basic structure. As shown in fig. 1, the structure includes a substrate 1, a chip 2, a case 3, and a heat dissipation plate 4 on the chip. However, although this structure increases the heat dissipation plate structure, the heat dissipation plate 4 does not contact the housing 3, and heat cannot be efficiently dissipated above the chip, so that the efficiency of dissipating heat above the chip is limited. In addition, the substrate of this structure is a copper substrate, and is still mainly a substrate heat dissipation method, and heat on the substrate is likely to have an adverse effect on the structure and wiring of the substrate itself. On the other hand, because the shell 3 of the structure is a conventional structure, the shell 3 needs to be covered above the chip structure one by one in the process of the chip packaging process, and the one by one placing mode needs complex mechanical action, so that the packaging process cannot be produced in large scale in batch.

The ceramic cover plate packaged structure has the problems of low packaging density, poor production efficiency and low yield consistency, and the ceramic substrate size can only reach 120mm x 120mm due to the fact that ceramic materials are fragile and difficult to sinter, so that batch packaging based on large-size substrates cannot be carried out. Therefore, a chip package structure and a corresponding chip package method that are suitable for mass production with high efficiency and low cost and can meet the requirement of high reliability in a special application environment are in great demand in the industry.

In particular, chips for special applications such as aviation, aerospace, exploration, and military applications are generally required to have high temperature resistance and high temperature impact resistance. For example, in some applications, it is desirable that the chip package structure be able to maintain its structural integrity and performance integrity in an environment in which the chip package is cycled over 500 cycles at temperatures in the range of-65 degrees Celsius to 150 degrees Celsius. In the conventional chip package structure shown in fig. 1, for example, structural damage or cracks are likely to occur in a harsh application environment due to a small contact area at a joint between the housing 3 and the substrate 1, mismatch of thermal expansion systems of materials, and the like.

Disclosure of Invention

Technical problem to be solved

The invention aims to solve the problem that the existing chip packaging structure is easy to damage under high temperature and high temperature impact; the invention also aims to solve the problems that the existing chip packaging structure is complex in process and not beneficial to industrial scale production.

(II) technical scheme

In order to solve the technical problems, the invention provides a chip packaging structure suitable for batch production, which comprises a substrate, chips and a shell, wherein the chips are fixedly connected with the substrate, the shell is of a semi-closed structure with a downward opening, a central section and a platform stage extend from the center of the shell to the periphery of the shell, and the bottom plane of the platform stage is lower than that of the central section in the vertical direction; the central section is connected with the step section through a transition section; the top surface of the chip is fixedly connected with the bottom surface of the central section.

According to a preferred embodiment of the present invention, the upper surface of the substrate located around the chip abuts against the lower surface of the stage.

According to the preferred embodiment of the invention, the distance between the upper surface of the substrate positioned at the periphery of the chip and the lower surface of the stage is 50 to 200 micrometers.

According to a preferred embodiment of the present invention, the upper surface of the substrate located around the chip is fixedly connected to the lower surface of the stage.

According to a preferred embodiment of the invention, the chip has a gap between its outer side in the vertical direction and the transition section.

According to a preferred embodiment of the invention, the width of the gap in the horizontal direction is 0.3 to 0.5 mm.

According to a preferred embodiment of the present invention, the gap is filled with a sealant.

According to the preferred embodiment of the invention, at least two through holes are formed in the substrate facing the gap, and the through holes are used for pouring the sealant.

According to a preferred embodiment of the invention, the transition section is an inclined section.

According to a preferred embodiment of the invention, the housing is made of a unitary metal material.

According to a preferred embodiment of the invention, the top surface of the table stage is flush with the central section.

According to a preferred embodiment of the present invention, the difference between the CTE values of the substrate and the housing in the horizontal direction is less than or equal to 5ppm/° c.

According to a preferred embodiment of the present invention, the difference between the CTE values of the substrate and the chip in the horizontal direction is less than or equal to 15 ppm/c.

According to the preferred embodiment of the invention, the substrate and the chip are electrically connected by adopting a gold-gold interconnection mode.

In another aspect, the present invention provides a chip packaging method, including the following steps: fixedly connecting a plurality of chips on a substrate, wherein the chips are arranged at intervals; covering a shell on a substrate connected with the chip, wherein the shell is provided with a plurality of semi-closed units, each semi-closed unit extends from the center of the semi-closed unit to the periphery to form a central section and a step section, and the central section is connected with the step section through a transition section; fixedly connecting the top surface of the semi-closed unit of the chip with the bottom surface of the central section of the semi-closed unit of the shell to form a whole-plate packaging structure; and cutting the whole board packaging structure to obtain a plurality of chip packaging structures.

According to a preferred embodiment of the present invention, the fixedly connecting the plurality of chips on the substrate includes: and electrically connecting the substrate with the plurality of chips in a gold-gold interconnection mode.

According to the preferred embodiment of the invention, the chip and the substrate are welded by a low-temperature ultrasonic welding mode without welding materials.

According to a preferred embodiment of the present invention, the upper surface of the substrate located around the chip is fixedly connected to the lower surface of the stage while the top surface of the chip is fixedly connected to the bottom surface of the central section of the semi-enclosed unit of the housing.

According to a preferred embodiment of the invention, the method further comprises: and filling a sealant in the gap, wherein the gap is positioned between the outer side surface of the chip in the vertical direction and the transition section.

According to a preferred embodiment of the present invention, at least two through holes are opened on the substrate facing the gap, and the through holes are used for pouring the sealant.

According to a preferred embodiment of the invention, the method further comprises: the housing is formed by an integral press forming process of a metal plate.

The invention further provides a chip packaging structure which is manufactured by the chip packaging method.

(III) advantageous effects

The shell of the packaging structure is an integrated step structure, can effectively remove the application generated by thermal expansion, and can resist high temperature and high thermal shock by matching and selecting the CTE difference between the shell material and the chip material.

The shell of the packaging structure is of a semi-closed integrated step structure with a downward opening, and the chip and the shell can be directly radiated by the solder with strong heat conductivity, so that the efficiency of radiating the chip packaging structure to the upper part of the shell is improved. And because the space below the shell is fully utilized, the volume of the filler is reduced, and the production cost is reduced.

The substrate and the shell of the packaging structure can be made of large-size whole plate materials, so that the packaging structure is easy to realize the process, low in cost and suitable for large-scale industrial production.

Drawings

Fig. 1 is a schematic structural diagram of a chip package structure in the prior art.

Fig. 2 is a schematic structural diagram of a chip package structure according to a first embodiment of the invention.

Fig. 3 is a top view of the first embodiment shown in fig. 2.

Fig. 4 is a schematic structural diagram of a chip package structure according to a second embodiment of the invention.

Fig. 5 is a top view of the second embodiment shown in fig. 4.

Fig. 6 is a schematic structural diagram of a chip package structure according to a third embodiment of the invention.

Fig. 7 is a schematic structural diagram of a chip package structure according to a fourth embodiment of the invention.

Fig. 8A to fig. 13B are schematic process diagrams of an embodiment of a chip packaging method of the invention.

Fig. 14 and 15 show schematic structural diagrams of an integrated testing apparatus for performing a large-scale screening on the whole-board chip package structure of the present invention.

FIG. 16 is a schematic diagram of an integrated testing apparatus for testing an integrated chip package structure.

Detailed Description

In order that the objects, technical solutions and advantages of the present invention will become more apparent, the present invention will be further described in detail with reference to the accompanying drawings in conjunction with the following specific embodiments.

As mentioned above, the conventional chip package structure and the corresponding process cannot obtain a chip package structure applicable to a special environment, for example, for some application environments, the chip package structure requires more than 500 times of temperature cycles within a range of-65 ℃ to 150 ℃, and has a complete structure and good functions. This requires the chip package structure to have superior high temperature and thermal shock resistance. Therefore, the invention provides a chip packaging structure with a shell of a semi-closed integrated step structure with a downward opening and a corresponding packaging method.

Fig. 2 is a schematic structural diagram of a chip package structure according to a first embodiment of the invention. As shown in fig. 2, the package structure includes a substrate 1, a chip 2, and a case 3. The substrate 1 is placed on a PCB board, and the chip 2 is fixed above the substrate 1, i.e. on the other side of the PCB board. Above the chip 2, a housing 3 is placed thereon and forms a semi-closed structure with an opening facing downward.

Fig. 3 is a top view of the first embodiment shown in fig. 2. The shape of the housing 3 in the top view direction may be square, rectangular, circular, or the like, and in this embodiment, the shape of the housing 3 in the top view direction is rectangular. However, it is to be understood that there is no particular limitation on the shape of the case or the shape of the substrate or the chip in the present invention, and the shape of the case may be appropriately selected depending on the shape of the chip itself. Preferably, the housing 3 is shaped to conform to the chip or substrate in plan view, but is sized slightly larger than the substrate 1 so that the housing 3 can completely cover the substrate 1 when inverted over the substrate and chip.

In this embodiment, the upper and lower surfaces of the substrate 1 are covered with metal conductive layers and interconnected by a reserved line (not shown) in the substrate 1. The bonding points under the chip 2 are fixedly connected with the wiring points on the substrate by means of solder ball bonding. The ball mounting process is performed on the chip 2 or the substrate before soldering, and the underfill process is performed on the soldered area between the substrate 1 and the chip 2 after soldering, preferably using a filler material having good thermal conductivity and sealing property. Compared with the traditional method that bonding wires are adopted inside the chip ceramic package, the packaging volume of the embodiment can be reduced by 2 to 3 times.

In the embodiment, the shell is made of a metal material and adopts an integrated step structure, and the ductility of the metal and the geometric characteristics of the step part enable the shell to absorb internal stress generated by the deformation of the shell caused by thermal expansion when the shell is subjected to thermal shock, so that the shell has excellent thermal shock resistance. Further, in a preferred embodiment, the difference between the CTE values of the substrate and the chip 2 in the horizontal direction is 15 ppm/DEG C or less. For some special application environments, the package structure is required to have a complete structure and good functions by cycling the temperature for more than 500 times within the range of-65 ℃ to 150 ℃, and the package structure is required to have ultra-excellent structural stability under high temperature and high thermal shock. The inventor finds out through theoretical calculation and experimental verification that when the difference between the CTE values of the substrate 1 and the housing 3 in the horizontal direction is less than or equal to 5 ppm/DEG C and the difference between the CTE values of the substrate and the chip is kept within 15 (ppm/DEG C), the packaging structure of the embodiment can keep complete structure and good function through more than 500 temperature cycle tests at-65-150 ℃ by matching with the packaging structure of the integrated stepped housing.

In this embodiment, as a preferred embodiment, the substrate and the chip 2 are electrically connected by using a gold-gold interconnection. And welding the pins of the chip 2 with the bonding pads on the substrate in a low-temperature ultrasonic welding mode without welding flux. Due to the adoption of a gold-gold interconnection mode, the problem that welding fails due to the Kenkard effect generated during welding between a conventional aluminum bonding pad and a gold ball can be solved, the cracking of a welding point is prevented, and the structural stability and the thermal shock resistance under the chip packaging environment are further improved. And moreover, the low-temperature solderless welding technology is adopted, so that the thermal deformation of the substrate caused by high-temperature welding is avoided, and compared with the conventional reflow welding technology, the reflow caused by the melting of the solder is avoided, so that foreign matters possibly generated between chip pins are prevented, and the yield of the device is increased.

Referring again to fig. 2, the present invention proposes to use an integrated housing structure, that is, the housing has a semi-closed structure with a downward opening, and the top surface and the peripheral side surface of the semi-closed structure form a continuous structure. Further, the housing forms an integral stepped structure. That is, the center section 31 and the step section 32 extend from the center of the housing 3 to the periphery, and the step section 32 is lower than the center section 31 in the vertical direction. The integrated step structure enables the top surface three-dimensional shape of the shell 3 to be matched with the top surface three-dimensional shape integrally formed by the chip and the substrate, reduces the redundant space part below the shell, and can improve the efficiency of radiating the chip packaging structure to the upper side of the shell. Meanwhile, the space below the shell is fully utilized, so that the volume of the filler is reduced, and the production cost is reduced.

In this exemplary embodiment, the top side of the chip 2 is fixedly connected, preferably soldered, to the bottom side of the central section 31 of the housing 3; through making chip 2 and casing 3 fixed mutually, increased the structural stability of device to, when adopting welded connection, the heat that chip 2 produced in work can be directly conducted to casing 3 via the solder, increased radiating efficiency, be favorable to packaging structure to keep normal work under high temperature state. More preferably, the case 3 is made of a metal having high thermal conductivity, such as tungsten copper, so as to further improve heat dissipation efficiency.

Referring to fig. 2 again, in this embodiment, as a preferred embodiment, the upper surface of the substrate 1 located around the chip 2 abuts against the lower surface of the step section 32 of the housing 3. The step section 32 of the housing 3 is thus directly supported by the base plate 1 without being fixed, so that the encapsulation structure has more structural integrity and robustness in the vertical direction. Further, since the substrate 1 and the case 3 are not welded and fixed, the case 3 is "floated" on the substrate 1, and thus, structural deformation due to a difference in thermal expansion coefficient between the case and the substrate is not caused, and thus, structural stability in the horizontal direction can be further improved.

As an implementation manner of this embodiment, the upper surface of the substrate 1 located at the periphery of the chip 2 is fixedly connected to the lower surface of the stage 32 of the housing 3. This embodiment is to enhance structural stability in the vertical direction. In order to prevent warping in the horizontal direction due to thermal shock, it is preferable that the Coefficient of Thermal Expansion (CTE) between the substrate 1 and the case is close, for example, not higher than 5ppm/° c in this embodiment. In addition, the fixed connection is preferably fixed connection in a welding mode, and is preferably solder with good heat conductivity, so that the substrate can be more effectively radiated through the shell, and the overall radiating efficiency of the packaging structure is improved.

Fig. 4 is a schematic diagram of a package structure according to a second embodiment of the invention. In this embodiment, the upper surface of the substrate 1, which is located around the chip 2, and the lower surface of the stage 32 of the housing 3 do not abut against each other, but are spaced apart by a small distance, for example 50 to 200 micrometers, preferably 100 micrometers. Due to the distance between the two, the restriction of the housing 3 in the horizontal and vertical directions will be smaller, thereby avoiding the substrate from warping under thermal shock conditions. Meanwhile, because the distance between the two is extremely small, the substrate 1 can still limit the movement of the shell 3 in the vertical direction to a certain extent, so that the packaging structure can also keep certain structural integrity and stability in the vertical direction.

Referring again to fig. 2 and 3, the portions between the center section and the step section, and between the mesa section and the second step section are referred to as the transition section and the second transition section, respectively. In the first and second exemplary embodiments, it is preferred that the outer side of the chip 2 in the vertical direction is at a distance, referred to herein as the gap, from the transition. Because there is the clearance for chip 2 thermal expansion in the horizontal direction can not push against the changeover portion of casing, and like this, chip 2's mechanical stress under the thermal shock can be effectively released, has prevented packaging structure's overall structure from being destroyed.

In order to seal the chip 2, the gap is filled with a sealant, which is generally a resin material having good flexibility and sealing property, such as silicone adhesive or epoxy adhesive. Meanwhile, in order to pour the sealant in the process, at least two through holes are formed in the position, facing the gap, of the substrate 1, wherein at least one through hole is used for pouring the sealant, and at least one through hole is used as an air outlet when the sealant is poured. The sealant is typically cured after the injection is complete. After the sealant is injected and the packaging structure is subjected to thermal shock, the mechanical stress generated by the thermal expansion of the chip 2 is transmitted to the sealant, and the deformation of the sealant is not hindered at the through hole due to the existence of the through hole, so that the mechanical stress generated by the thermal expansion of the chip 2 can be removed to a certain extent by the deformation of the sealant, and the whole structure of the packaging structure cannot be damaged due to the thermal shock. The width of the gap in the horizontal direction is preferably 0.3 to 0.5 mm, taking into consideration the overall size of the package structure and the stress relief effect.

Fig. 5 is a schematic diagram of a package structure according to a third embodiment of the invention. In this embodiment, unlike the second embodiment, the transition section is an inclined section 33. Fig. 6 is a top view of this embodiment, where the dark areas are sloped transitions. The inclined section is not only beneficial to the removal of the application in the horizontal direction, but also beneficial to the removal of the application in the vertical direction. For example, in the horizontal direction, when the gap is filled with the sealant, the stress in the horizontal direction generated by the thermal expansion of the chip is not completely released by the sealant, and the stress can be further released by the inclined section. Further, the angle between the inclined section and the horizontal plane is preferably 45 to 90 degrees.

Fig. 7 is a schematic structural diagram of a chip package structure according to a fifth embodiment of the invention. This fifth embodiment differs from the first embodiment in that the top surface of the step section 32 is flush with the central section 31. That is, the inner side surface of the step section 32 is still in an integral step structure, but the outer side surface thereof is simplified to be in a single step continuous structure. In this embodiment, because the surface structure of casing is simpler for packaging structure appearance is more regular, simultaneously, to the manufacturing of casing, because the casing has once less buckled, therefore simple in the technology.

Fig. 8A to fig. 13B are schematic process diagrams of an embodiment of a chip packaging method of the invention.

S1, fixedly connecting chips on a substrate, wherein the chips are arranged at intervals;

fig. 8A shows a cross-sectional view of the substrate 1, and fig. 8B is the top view of the substrate. As can be seen from fig. 8A and 8B, pairs of small holes are reserved on the substrate, and each pair of small holes is used as a chip fixing position. Fig. 9A and 9B are schematic views after the chip is fixedly attached to the substrate. FIG. 9A is a cross-sectional view schematically showing the case of two chips; fig. 9B is a top view showing a case where a plurality of chips are arranged in a 4 × 3 matrix. It should be understood that more chips may be provided on a single substrate as the process allows in order to improve the efficiency of mass production.

As shown in fig. 9A, in this embodiment, the substrate 1 is a BT resin substrate, and preferably, the thermal expansion coefficient between the BT substrate 1 and the chip 2 is close to, for example, not higher than 15 ppm/degree centigrade, and the joint of the source and the drain under the chip 2 is fixedly connected to the wiring point on the substrate by means of solder ball bonding. The upper and lower surfaces of the substrate 1 are covered with metal conductive layers and interconnected by a reserved line in the substrate. The ball mounting process is performed on the chip 2 or the substrate before the bonding, and the underfill process is performed on the bonding region between the substrate 1 and the chip 2 after the flip-chip bonding between the substrate 1 and the chip 2 after the bonding, preferably using a filler having good thermal conductivity and sealing property. Compared with the traditional method that bonding wires are adopted inside the chip ceramic package, the packaging volume of the embodiment can be reduced by 2 to 3 times. Compared with a bonding mode, the welding mode of the solder ball is characterized in that a bonding wire is eliminated, so that the conduction resistance from the drain electrode and the source electrode of the device to a PCB is greatly reduced, and the parasitic influence caused by the bonding wire is greatly reduced.

Preferably, when the number of the chips is large, the substrate is adsorbed and fixed on a carrier due to the thinness of the substrate, so that the carrier can better support the substrate, and the chips can be fixed on the substrate later.

As shown in fig. 9B, each chip is secured in the middle of a pair of small holes.

And S2, covering the shell on the substrate connected with the chip.

In this embodiment, the housing has an integral stepped structure. For this purpose, step S2 may be preceded by a step of forming the housing. In this embodiment, the housing is formed by performing an integral press forming process on a metal plate material. The integral stamping is a method with simple process, high yield and low cost for metal materials with strong ductility, and shells with different sizes or shapes can be produced by adopting different stamping dies.

As mentioned above, the housing formed by stamping has a plurality of semi-closed units, each semi-closed unit extends from the center of the housing to the periphery to form a central section 31 and a step section 32, and the step section 32 is lower than the central section 31 in the vertical direction. The integrated step structure enables the top surface three-dimensional shape of the shell 3 to be matched with the top surface three-dimensional shape integrally formed by the chip and the substrate, reduces the redundant space part below the shell, and can improve the efficiency of radiating the chip packaging structure to the upper side of the shell. Meanwhile, the space below the shell is fully utilized, so that the volume of the filler is reduced, and the production cost is reduced.

And S3, fixedly connecting the top surface of the chip with the bottom surface of the central section of the semi-closed unit of the shell, and simultaneously, fixedly connecting the upper surface of the substrate, which is positioned on the periphery of the chip, with the lower surface of the stage.

The fixed connection is preferably fixed connection in a welding mode, and is preferably solder with good heat conductivity, so that the substrate can be effectively radiated through the shell, and the overall radiating efficiency of the packaging structure is improved. In order to prevent warping in the horizontal direction due to thermal shock, in this embodiment, it is preferable that the coefficient of thermal expansion between the substrate 1 and the case be close to, for example, not higher than 5ppm/° c.

Fig. 10A is a cross-section showing a step of coating solder on the surface of the chip 2 and the upper surface of the substrate around the chip, and fig. 10B is a top view. As shown in fig. 10B, the solder is disposed on the chip 2 and applied to the rest of the substrate at a distance from the chip and the aperture in the substrate.

In other embodiments, the step S3 may only fixedly connect the top surface of the chip 2 with the bottom surface of the central section of the semi-enclosed unit of the housing, but does not fixedly connect the upper surface of the substrate 1 of the chip 2, which is located at the periphery of the chip, with the lower surface of the stage, and in this case, only the chip 2 may be coated with solder. One way of achieving this is that the upper surface of the substrate 1, which is located around the chip 2, abuts against the lower surface of the stage 32 of the housing 3, or else with a small distance therebetween, for example 50 to 200 microns, preferably 100 microns. In the latter case, the restriction of the housing 3 in the horizontal and vertical directions is smaller due to the distance therebetween, thereby preventing the substrate from being warped under thermal shock conditions. Further, since the substrate 1 and the case 3 are not welded and fixed, the case 3 is "floated" on the substrate 1, and thus, structural deformation due to a difference in thermal expansion coefficient between the case and the substrate is not caused, and thus, structural stability in the horizontal direction can be further improved. Meanwhile, because the distance between the two is extremely small, the substrate 1 can still limit the movement of the shell 3 in the vertical direction to a certain extent, so that the packaging structure can also keep certain structural integrity and stability in the vertical direction.

Fig. 11 shows a view after covering the upper case on the chip or substrate coated with solder. As can be seen from fig. 10, the housing is bonded to the chip or substrate to form a unitary structure. Preferably, when the number of chips is large, the shell can be adsorbed and fixed on a carrier due to the thinness of the shell, so that the carrier can better support the shell to facilitate the subsequent covering on the substrate.

And S4, filling sealant in the gap.

As shown in fig. 12A, the gap refers to a gap between an outer side surface of the chip in the vertical direction and the transition section.

In order to seal the chip 2, the gap is filled with a sealant, which is generally a resin material having good flexibility and sealing performance, such as silicone adhesive or epoxy adhesive. Meanwhile, in order to pour the sealant in the process, at least two through holes are formed in the position, facing the gap, of the substrate 1, wherein at least one through hole is used for pouring the sealant, and at least one through hole is used as an air outlet when the sealant is poured. The sealant is typically cured after the injection is complete, resulting in the structure shown in fig. 12A and 12B, where fig. 12B is a top view. After the sealant is injected, when the packaging structure is subjected to thermal shock, the mechanical stress generated by the thermal expansion of the chip 2 is transmitted to the sealant, and the deformation of the sealant is not hindered at the through hole due to the existence of the through hole, so that the mechanical stress generated by the thermal expansion of the chip 2 can be removed to a certain extent by the deformation of the sealant, and the whole structure of the packaging structure cannot be damaged due to the thermal shock. The width of the gap in the horizontal direction is preferably 0.3 to 0.5 mm, taking into consideration the overall size of the package structure and the stress relief effect.

It should be noted that the process of pouring the sealant needs to be performed under a vacuum environment.

And S5, cutting the whole board packaging structure to obtain a plurality of chip packaging structures.

As shown in fig. 13A and 13B, in this step, the chip package structure having completed the package is cut to obtain a finished chip package structure.

It should be noted that, before step S5, the entire board chip package structure) may be screened in a large scale, and the device finished product may be subjected to criterion according to the screening result. In order to meet the high reliability requirements, in particular the thermal shock resistance, ageing processes are included in the test process.

Fig. 14 and 15 show schematic structural diagrams of an integrated testing apparatus for performing a large-scale screening on the whole-board chip package structure of the present invention. Fig. 14 is a top view, and fig. 15 is a cross-sectional view. As shown in fig. 14 and 15, the integrated testing apparatus 10 includes a main board 101, a plurality of position limiting frames 102 corresponding to the positions of the chip package structure on the main board, and retractable probes 103 in the position limiting frames 103. The position of the probe 103 corresponds to the pin position on the back side of the substrate.

FIG. 16 is a schematic diagram of an integrated testing apparatus for testing an integrated chip package structure. As shown in fig. 16, during testing, the limit frame of the testing apparatus is abutted against the back surface of the substrate 1, so that the probes 103 are aligned with the pins on the back surface of each substrate and rebound, and a testing circuit (not shown) on the testing apparatus completes the testing.

Compared with the prior art that finished devices of the chip packaging structure need to be placed into a testing device one by one, the invention does not need procedures of transferring, placing and the like one by one, and greatly improves the testing efficiency.

In addition, when ageing, can go on in the pin that the integration back splint device that ages that has a plurality of test probes integrated connects the base plate back of whole board chip package structure, need not to carry out one by one to the device and shift and place and can accomplish whole board chip package structure's ageing, greatly improved efficiency of software testing. Particularly, for the test of the high-reliability chip package structure, because the test times are many, the test device and the test method of the whole-board chip package structure can make almost all tests (except for the last test after the cutting is finished) be performed on the whole board, thereby greatly improving the test and screening efficiency after the package.

The above-mentioned embodiments are intended to illustrate the objects, technical solutions and advantages of the present invention in further detail, and it should be understood that the above-mentioned embodiments are only exemplary embodiments of the present invention and are not intended to limit the present invention, and any modifications, equivalents, improvements and the like made within the spirit and principle of the present invention should be included in the protection scope of the present invention.

Claims (15)

1. The utility model provides a be suitable for batch production's chip package structure, includes base plate, chip and casing, the chip with base plate fixed connection, its characterized in that:

the shell is of a semi-closed structure with a downward opening and is made of integrated metal materials, a central section and a platform stage extend from the center of the shell to the periphery of the shell, and the bottom plane of the platform stage is lower than that of the central section in the vertical direction;

the central section is connected with the step section through a transition section;

the top surface of the chip is fixedly connected with the bottom surface of the central section;

the upper surface of the substrate positioned around the chip is abutted against the lower surface of the stage;

the substrate is BT resin, and the difference of CTE values of the substrate and the shell in the horizontal direction is less than or equal to 5 ppm/DEG C;

the difference of the CTE values of the substrate and the chip in the horizontal direction is less than or equal to 15 ppm/DEG C;

the packaging structure can pass more than 500 times of temperature cycle tests at-65-150 ℃.

2. The chip package structure according to claim 1, wherein the substrate is electrically connected to the chip by gold-gold interconnection.

3. The chip packaging structure according to claim 1, wherein a gap is provided between an outer side surface of the chip in a vertical direction and the transition section.

4. The chip package structure according to claim 3, wherein the gap has a width in a horizontal direction of 0.3 to 0.5 mm.

5. The chip package structure of claim 3, wherein the gap is filled with a sealant.

6. The chip package structure according to claim 5, wherein at least two through holes are formed in the substrate facing the gap, and the through holes are used for pouring the sealant.

7. The chip packaging structure of claim 1, wherein,

the transition section is an inclined section.

8. The chip packaging structure of any one of claims 1 to 7, wherein a top surface of the mesa stage is flush with the central section.

9. A chip packaging method is characterized by comprising the following steps:

electrically connecting a plurality of chips on a substrate, the plurality of chips being arranged at a distance from each other, wherein the substrate is a BT resin having a difference in CTE value in a horizontal direction from the chip of 15 ppm/DEG C or less;

covering a shell on a substrate connected with the chip, wherein the shell is made of an integrated metal material and is provided with a plurality of semi-closed units, each semi-closed unit extends from the center of the shell to the periphery to form a central section and a step section, and the central section and the step section are connected through a transition section, and the difference of CTE (coefficient of thermal expansion) values of the substrate and the shell in the horizontal direction is less than or equal to 5 ppm/DEG C;

fixedly connecting the top surface of the semi-closed unit of the chip with the bottom surface of the central section of the semi-closed unit of the shell, and simultaneously abutting the upper surface of the substrate positioned around the chip with the lower surface of the stage to form a whole-plate packaging structure;

and cutting the whole plate packaging structure to obtain a plurality of chip packaging structures, wherein the packaging structures can pass more than 500 times of temperature cycle tests at-65-150 ℃.

10. The chip packaging method of claim 9, wherein fixedly attaching the plurality of chips to the substrate comprises: and electrically connecting the substrate with the plurality of chips in a gold-gold interconnection mode.

11. The chip packaging method of claim 10, wherein the chip is bonded to the substrate by low temperature ultrasonic bonding without solder.

12. The chip packaging method of claim 9, further comprising: and filling a sealant in the gap, wherein the gap is positioned between the outer side surface of the chip in the vertical direction and the transition section.

13. The chip packaging method according to claim 12, wherein at least two through holes are formed in the substrate facing the gap, and the through holes are used for pouring the sealant.

14. The chip packaging method of claim 9, further comprising: the housing is formed by an integral press forming process of a metal plate.

15. A chip packaging structure, characterized by being manufactured by the chip packaging method of any one of claims 9 to 14.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202210736592.8A CN114823550B (en) | 2022-06-27 | 2022-06-27 | Chip packaging structure and packaging method suitable for batch production |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202210736592.8A CN114823550B (en) | 2022-06-27 | 2022-06-27 | Chip packaging structure and packaging method suitable for batch production |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN114823550A CN114823550A (en) | 2022-07-29 |

| CN114823550B true CN114823550B (en) | 2022-11-11 |

Family

ID=82523506

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN202210736592.8A Active CN114823550B (en) | 2022-06-27 | 2022-06-27 | Chip packaging structure and packaging method suitable for batch production |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN114823550B (en) |

Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO1999019832A1 (en) * | 1997-10-15 | 1999-04-22 | Siemens Aktiengesellschaft | Carrier element for a semiconductor chip for installing in chip cards |

| US6215180B1 (en) * | 1999-03-17 | 2001-04-10 | First International Computer Inc. | Dual-sided heat dissipating structure for integrated circuit package |

| CN101110397A (en) * | 2006-07-18 | 2008-01-23 | 日月光半导体制造股份有限公司 | Chip packaging structure |

| CN101878527A (en) * | 2007-11-30 | 2010-11-03 | 斯盖沃克斯瑟路申斯公司 | Wafer level packaging using flip chip mounting |

| CN103715150A (en) * | 2012-09-30 | 2014-04-09 | 申宇慈 | Die cap and flip chip package with die cap |

| CN104465548A (en) * | 2014-12-10 | 2015-03-25 | 华进半导体封装先导技术研发中心有限公司 | Three-dimensional flexible packaging structure and injection molding method thereof |

| CN210224006U (en) * | 2019-07-15 | 2020-03-31 | 星科金朋半导体(江阴)有限公司 | Packaging structure of multi-chip |

| CN111341741A (en) * | 2020-03-17 | 2020-06-26 | 中国科学院微电子研究所 | Power device packaging structure and packaging method for improving heat dissipation capability |

| CN113302757A (en) * | 2021-03-03 | 2021-08-24 | 泉州三安半导体科技有限公司 | LED packaging device and preparation method thereof |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6963141B2 (en) * | 1999-12-31 | 2005-11-08 | Jung-Yu Lee | Semiconductor package for efficient heat spreading |

| TW200428623A (en) * | 2003-06-11 | 2004-12-16 | Siliconware Precision Industries Co Ltd | Semiconductor package with heat sink |

| CN1319163C (en) * | 2003-08-29 | 2007-05-30 | 矽品精密工业股份有限公司 | Semiconductor package with radiating fins |

| TWI259566B (en) * | 2004-08-31 | 2006-08-01 | Via Tech Inc | Exposed heatsink type semiconductor package and manufacture process thereof |

| TWI255047B (en) * | 2005-06-22 | 2006-05-11 | Siliconware Precision Industries Co Ltd | Heat dissipating semiconductor package and fabrication method thereof |

| KR101037229B1 (en) * | 2006-04-27 | 2011-05-25 | 스미토모 베이클리트 컴퍼니 리미티드 | Semiconductor device and semiconductor device manufacturing method |

| DE102012213916A1 (en) * | 2011-11-08 | 2013-05-08 | Robert Bosch Gmbh | Electronic module for a control unit |

| CN108231700B (en) * | 2016-12-21 | 2020-03-03 | 苏州迈瑞微电子有限公司 | Chip packaging structure and method |

| CN112216672A (en) * | 2019-07-11 | 2021-01-12 | 苏州旭创科技有限公司 | Hybrid carrier plate, manufacturing method thereof, assembly and optical module |

| CN111987046A (en) * | 2020-08-28 | 2020-11-24 | 上海申矽凌微电子科技有限公司 | Straw hat-shaped packaging structure |

-

2022

- 2022-06-27 CN CN202210736592.8A patent/CN114823550B/en active Active

Patent Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO1999019832A1 (en) * | 1997-10-15 | 1999-04-22 | Siemens Aktiengesellschaft | Carrier element for a semiconductor chip for installing in chip cards |

| US6215180B1 (en) * | 1999-03-17 | 2001-04-10 | First International Computer Inc. | Dual-sided heat dissipating structure for integrated circuit package |

| CN101110397A (en) * | 2006-07-18 | 2008-01-23 | 日月光半导体制造股份有限公司 | Chip packaging structure |

| CN101878527A (en) * | 2007-11-30 | 2010-11-03 | 斯盖沃克斯瑟路申斯公司 | Wafer level packaging using flip chip mounting |

| CN103715150A (en) * | 2012-09-30 | 2014-04-09 | 申宇慈 | Die cap and flip chip package with die cap |

| CN104465548A (en) * | 2014-12-10 | 2015-03-25 | 华进半导体封装先导技术研发中心有限公司 | Three-dimensional flexible packaging structure and injection molding method thereof |

| CN210224006U (en) * | 2019-07-15 | 2020-03-31 | 星科金朋半导体(江阴)有限公司 | Packaging structure of multi-chip |

| CN111341741A (en) * | 2020-03-17 | 2020-06-26 | 中国科学院微电子研究所 | Power device packaging structure and packaging method for improving heat dissipation capability |

| CN113302757A (en) * | 2021-03-03 | 2021-08-24 | 泉州三安半导体科技有限公司 | LED packaging device and preparation method thereof |

Also Published As

| Publication number | Publication date |

|---|---|

| CN114823550A (en) | 2022-07-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100702968B1 (en) | Semiconductor package having floated heat sink, stack package using the same and manufacturing method thereof | |

| KR910004506B1 (en) | Inverted chip carrier | |

| US7061122B2 (en) | Components, methods and assemblies for multi-chip packages | |

| TWI419243B (en) | Low profile ball grid array (bga) package with exposed die and method of making same | |

| US20110260334A1 (en) | Semiconductor device | |

| EP0822738A2 (en) | Column array connections | |

| KR20160012589A (en) | Semiconductor package stack structure having interposer substrate | |

| JP2003249607A (en) | Semiconductor device and manufacturing method therefor, circuit board and electronic device | |

| KR20090039411A (en) | Semiconductor package, module, system having a solder ball being coupled to a chip pad and manufacturing method thereof | |

| JP2000269408A (en) | Semiconductor device and manufacture thereof | |

| JPH1145956A (en) | Packaged integrated circuit element and production thereof | |

| KR20010066939A (en) | Semiconductor device and method of producing the same | |

| KR20030018642A (en) | Stack chip module | |

| JP3213703B2 (en) | Reworkable microelectronic multichip module | |

| WO2004112129A1 (en) | Electronic device | |

| JPH09293808A (en) | Semiconductor device | |

| KR102561718B1 (en) | Integrated circuit packaging system with interposer support structure mechanism and method of manufacture thereof | |

| US7151308B2 (en) | Semiconductor chip package | |

| CN114823550B (en) | Chip packaging structure and packaging method suitable for batch production | |

| JP2010010269A (en) | Semiconductor device, intermediate for manufacturing semiconductor device, and method of manufacturing them | |

| KR101445766B1 (en) | Semiconductor package and method of manufacturing the same | |

| JP2003069187A (en) | Board connection supporting tool for electronic component mount board and method for connecting board | |

| JP4038021B2 (en) | Manufacturing method of semiconductor device | |

| JPH06204385A (en) | Semiconductor device mounted pin grid array package substrate | |

| JPH0964080A (en) | Semiconductor device and method of manufacturing it |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PB01 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| GR01 | Patent grant | ||

| GR01 | Patent grant |