WO2017196391A1 - Constructing, representing, and encoding polar codes - Google Patents

Constructing, representing, and encoding polar codes Download PDFInfo

- Publication number

- WO2017196391A1 WO2017196391A1 PCT/US2016/063650 US2016063650W WO2017196391A1 WO 2017196391 A1 WO2017196391 A1 WO 2017196391A1 US 2016063650 W US2016063650 W US 2016063650W WO 2017196391 A1 WO2017196391 A1 WO 2017196391A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- polar code

- permutation vector

- code permutation

- vector

- generate

- Prior art date

Links

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/13—Linear codes

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/63—Joint error correction and other techniques

- H03M13/635—Error control coding in combination with rate matching

- H03M13/6356—Error control coding in combination with rate matching by repetition or insertion of dummy data, i.e. rate reduction

Definitions

- Embodiments pertain to wireless communications. Some embodiments relate to constructing, representing and encoding polar codes. BACKGROUND

- 3GPP LTE systems With the increase in different types of devices communicating with various network devices, usage of 3GPP LTE systems has increased. The penetration of mobile devices (user equipment or UEs) in modern society has continued to drive demand for a wide variety of networked devices in a number of disparate environments. The use of networked UEs using 3GPP LTE systems has increased in all areas of home and work life. Fifth generation (5G) wireless systems are forthcoming, and are expected to enable even greater speed, connectivity, and usability.

- 5G Fifth generation

- Polar coding is a new error correction coding technique with theoretical guarantees to achieve the capacity of

- FIG.1 is a diagram of a polar code encoder in accordance with some embodiments.

- FIG.2 is a flow diagram of a method to encode input bits using a polar code in accordance with some embodiments.

- FIG.3 is a flow diagram of a method to generate a polar code in accordance with some embodiments.

- FIG.4 is a functional diagram of a User Equipment (UE) using a polar encoder in accordance with some embodiments.

- UE User Equipment

- FIG.5 is a diagram of a size N polar code generator in accordance with some embodiments.

- FIG.6 is a flow diagram of a method for generating a representation of a polar code permutation vector using a smaller size polar code permutation vector and a bit sequence in accordance with some embodiments.

- FIG.7 is a flow diagram illustrating example functionalities for generating a polar code permutation vector, in accordance with an example embodiment.

- FIG.8 illustrates a block diagram of a communication device such as an Evolved Node-B (eNB) or a user equipment (UE), in accordance with some embodiments.

- eNB Evolved Node-B

- UE user equipment

- FIG.1 is a diagram of a polar code encoder in accordance with some embodiments.

- the polar code encoder 100 may include a zero padding block 102, a polar code permutation block 104 and a generator matrix GN 106, where N is the size of the polar code encoder and the number of generated output bits.

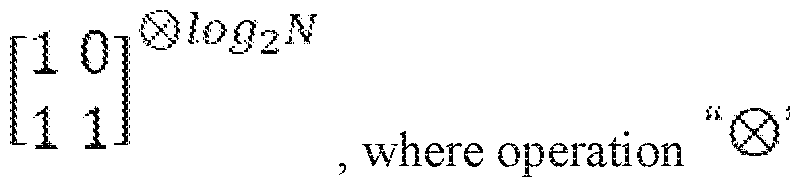

- Polar codes belong to a class of affine codes that can be generated by subsets of the rows of the generator matrix 106: , where denotes a Kronecker power.

- a rate code (which may or may not be used as a polar code) may be generated by picking any K rows of as a generator matrix.

- One or more codes in this class can be encoded by the matrix multiplication , where is set to a data bit if the i ⁇ th row of is in the code's generator matrix, and otherwise is set to a predetermined value, e.g., zeros.

- Such a code can be referred to as a polar code if its generator matrix includes K rows of that satisfy row is in the matrix and row is not.

- Bhattacharyya parameter which is the reliability associated with communicating the i th bit on the W(i) channel.

- polar codes are channel-specific designs. These codes may have good performance under successive cancellation (SC) decoding and indeed achieve channel capacity. Although very few codes are true polar codes according to this strict definition (in particular, if the order of s is unique for a given W, there is a unique polar code for that channel and given rate), many codes that do not necessarily adhere to the above rule may be called polar codes. In some embodiments, all of these codes share the property that be %small% if the i ⁇ th row is included in the generator matrix. Embodiments of the present disclosure also follow this practice and thus the codes here will also be called polar codes.

- Embodiments of the present disclosure are directed to a class of polar codes that have excellent performance under list decoding, without the aid of an external CRC. This simplifies their decoding, and eliminates CRC overhead.

- a single %permutation% is used to represent codes of arbitrary rates. That is, for a given code length, codes of all rates can be encoded using the same mechanism.

- the reliability of each bit under SC decoding can be estimated closely by a recursive %polarize--quantize% technique. A linear-time algorithm may be used to estimate values very closely and one or more of the most reliable bits may be selected.

- K input data bits 110 (V 1 , *, V k ) are to be encoded by a rate K/N code.

- the zero padding block 102 may be used to zero pad the input bits 110 V 1 , *, V k with (N-K) bits of predetermined values (for example, zero bits) to obtain the length N vector 112 .

- This vector is then permuted by the polar code permutation vector PN 104, and the permuted N-bit vector 114 is

- FIG.2 is a flow diagram of a method to encode input bits using a polar code in accordance with some embodiments.

- the example method 200 may start at 202, when a length N input vector (e.g., 112) may be generated based on K input data bits (e.g., 110), where K and N may be integers with K being less than or equal to than N.

- the input data bits 110 may be zero-padded so that the input vector 112 of length N is generated, which may include the K input bits and (N-K) zeros (or other predetermined bits).

- the input vector 112 is permuted by the polar code permutation vector 104 to generate the permuted N-bit vector 114.

- the permuted N-bit vector 114 is encoded by the generator matrix GN 106 to generate coded data bits XN 116 as output.

- the coded data bits X N 116 can be transmitted.

- Example polar code permutation vectors (that is, permutations) for code lengths are given in Listing A below.

- One or more other permutation vectors may be derived from the permutations listed in Listing A. For example, if system requirements dictate that data be encoded at rates then any permutation derived from by permuting the first numbers among themselves can be used. Similarly, the numbers can be permuted among themselves, and so can the numbers , and so on.

- any other permutation that can be derived from may be used as well.

- One suitable class of such permutations is defined by setting a threshold , with all numbers in the derived permutation being at most positions away from their positions in . In other words, if is the derived permutation, the following condition is satisfied for some

- Such a derived permutation may be preferred if, for instance, it can be more efficiently represented in memory. In this regard, there may be a trade-off between how large is and how robust a

- the choice of the derived permutation may be based on error performance versus

- Approximately optimal polar codes for SC decoding may be constructed using the %polarize--quantize% technique.

- bit selection using this technique may not lead to codes that are competitive with the state- of-the-art LDPC or Turbo codes unless the decoding of these polar codes is augmented by a CRC stage.

- the quantization technique used in embodiments of the present disclosure to estimate the bit reliabilities leads to only slight performance loss under SC decoding (which in many cases may not be the decoder of choice), but dramatically improves performance under list decoding.

- generation of the permutations listed in Listing A may start by estimating the bit-channel reliabilities for all channel signal-to-noise ratios (SNRs) from, e.g., -8dB to 11dB, with 0.5dB increments. These constructions are then tested at different rates and channel conditions. In some examples, the construction SNR that achieves optimal performance may be between 0dB and 2dB above the true channel SNR.

- SNRs channel signal-to-noise ratios

- the permutations may be generated using the technique described below and illustrated in the flow diagram of FIG.3.

- FIG.3 is a flow diagram of a method 300 to generate a polar code in accordance with some embodiments.

- the permutation vector length may be fixed at length N.

- Bit-channel estimation may be performed with underlying transmission channel SNRs ranging from , with increments of .

- a plurality of estimates of channel reliability e.g., Z(Wi)

- Z(Wi) Z(Wi)

- the underlying channel SNR may be referred to as .

- the polar code permutation vector is initialized as an empty permutation vector. At the end of the flow diagram in FIG.3 this vector will have length N.

- an iteration loop may be performed with SNR values of with increments at SNRinc.

- SNRinc For construction rules at

- BLER target block error rate

- the construction rule with the highest rate may be selected.

- it may be determined for the selected construction rule and its rate, whether the data bits associated with the rule are a superset of a previous permutation vector (e.g., a permutation vector generated during a previous iteration cycle).

- the new bit positions are appended to the permutation vector.

- the next best construction rule is selected and processing may resume at 308.

- an error notification may be presented and no permutation vector is generated.

- the permutation vector may be appended with any missing bit positions so that a total of N positions are included in the permutation vector.

- the above technique may simultaneously provide that the constructed codes are nested so that codes of lower rate are sub-codes of those at higher rates, and that codes of all rates have error performance that satisfies a pre-determined error rate.

- Many refinements and variations on the above technique are possible. For example, a more finely nested construction may be obtained by considering construction and channel SNRs at smaller SNR increments.

- FIG.4 is a functional diagram of a User Equipment (UE) using a polar encoder in accordance with some embodiments.

- UE User Equipment

- the UE 400 may include application circuitry 402, baseband circuitry 404, Radio Frequency (RF) circuitry 406, front-end module (FEM) circuitry 408, and multiple antennas 410A-410D, coupled together at least as shown.

- RF Radio Frequency

- FEM front-end module

- other circuitry or arrangements may include one or more elements or components of the application circuitry 402, the baseband circuitry 404, the RF circuitry 406 or the FEM circuitry 408, and may also include other elements or components in some cases.

- !processing circuitry may include one or more elements or components, some or all of which may be included in the application circuitry 402 or the baseband circuitry 404.

- !transceiver circuitry may include one or more elements or components, some or all of which may be included in the RF circuitry 406 or the FEM circuitry 408. These examples are not limiting, however, as the processing circuitry or the transceiver circuitry may also include other elements or components in some cases.

- the application circuitry 402 may include one or more application processors.

- the application circuitry 402 may include circuitry such as, but not limited to, one or more single-core or multi- core processors.

- the processor(s) may include any combination of general- purpose processors and dedicated processors (e.g., graphics processors, application processors, etc.).

- the processors may be coupled with or may include memory/storage and may be configured to execute instructions stored in the memory/storage to enable various applications or operating systems to run on the system to perform one or more of the functionalities described herein.

- the baseband circuitry 404 may include circuitry such as, but not limited to, one or more single-core or multi-core processors.

- the baseband circuitry 404 may include one or more baseband processors or control logic to process baseband signals received from a receive signal path of the RF circuitry 406 and to generate baseband signals for a transmit signal path of the RF circuitry 406.

- Baseband processing circuity 404 may interface with the application circuitry 402 for generation and processing of the baseband signals and for controlling operations of the RF circuitry 406.

- the baseband circuitry 404 may include a second generation (2G) baseband processor 404a, third generation (3G) baseband processor 404b, fourth generation (4G) baseband processor 404c, or other baseband processor(s) 404d for other existing generations, generations in development or to be developed in the future (e.g., fifth generation (5G), 6G, etc.).

- the baseband circuitry 404 e.g., one or more of baseband processors 404a-d

- the radio control functions may include, but are not limited to, signal modulation/demodulation, encoding/decoding, radio frequency shifting, etc.

- modulation/demodulation circuitry of the baseband circuitry 404 may include Fast-Fourier Transform (FFT), precoding, or constellation mapping/demapping functionality.

- encoding/decoding circuitry of the baseband circuitry 404 may include Low Density Parity Check (LDPC) encoder/decoder functionality, optionally along- side other techniques such as, for example, block codes, convolutional codes, turbo codes, or the like, which may be used to support legacy protocols.

- LDPC Low Density Parity Check

- Embodiments of modulation/demodulation and encoder/decoder functionality are not limited to these examples and may include other suitable functionality in other embodiments.

- the baseband circuitry 404 may include elements of a protocol stack such as, for example, elements of an evolved universal terrestrial radio access network (EUTRAN) protocol including, for example, physical (PHY) 405a, media access control (MAC) 405b, radio link control (RLC) 405c, packet data convergence protocol (PDCP) 405d, and/or radio resource control (RRC) 405e elements.

- EUTRAN evolved universal terrestrial radio access network

- PHY physical

- MAC media access control

- RLC radio link control

- PDCP packet data convergence protocol

- RRC radio resource control

- a central processing unit (CPU) 404e of the baseband circuitry 404 may be configured to run elements of the protocol stack for signaling of the PHY, MAC, RLC, PDCP or RRC layers.

- the baseband circuitry may include one or more audio digital signal processor(s) (DSP) 404f.

- the audio DSP(s) 404f may be include elements for

- compression/decompression and echo cancellation may include other suitable processing elements in other embodiments.

- Components of the baseband circuitry may be suitably combined in a single chip, a single chipset, or disposed on a same circuit board in some embodiments. In some embodiments, some or all of the constituent components of the

- baseband circuitry 404 and the application circuitry 402 may be

- SOC system on chip

- the baseband circuitry 404 may provide for communication compatible with one or more radio technologies.

- the baseband circuitry 404 may support communication with an evolved universal terrestrial radio access network (EUTRAN) or other wireless metropolitan area networks (WMAN), a wireless local area network (WLAN), a wireless personal area network (WPAN).

- EUTRAN evolved universal terrestrial radio access network

- WMAN wireless metropolitan area networks

- WLAN wireless local area network

- WPAN wireless personal area network

- Embodiments in which the baseband circuitry 404 is configured to support radio communications of more than one wireless protocol may be referred to as multi-mode baseband circuitry.

- the baseband circuitry 204 may include a polar code encoder 404g, which may be configured to perform one or more of the functionalities disclosed herein in connection with construction, representation and encoding of polar codes, including polar code permutation vectors.

- the encoder 404g may be similar to the polar code encoder 100 of FIG.1, and performing one or more of the functions described herein and also illustrated in one or more of the flow diagrams in the attached figures.

- RF circuitry 406 may enable communication with wireless networks using modulated electromagnetic radiation through a non-solid medium.

- the RF circuitry 406 may include switches, filters, amplifiers, etc. to facilitate the communication with the wireless network.

- RF circuitry 406 may include a receive signal path which may include circuitry to down-convert RF signals received from the FEM circuitry 408 and provide baseband signals to the baseband circuitry 404.

- RF circuitry 406 may also include a transmit signal path which may include circuitry to up- convert baseband signals provided by the baseband circuitry 404 and provide RF output signals to the FEM circuitry 408 for transmission.

- the RF circuitry 406 may include a receive signal path and a transmit signal path.

- the receive signal path of the RF circuitry 406 may include mixer circuitry 406a, amplifier circuitry 406b and filter circuitry 406c.

- the transmit signal path of the RF circuitry 406 may include filter circuitry 406c and mixer circuitry 406a.

- RF circuitry 406 may also include synthesizer circuitry 406d for synthesizing a frequency for use by the mixer circuitry 406a of the receive signal path and the transmit signal path.

- the mixer circuitry 406a of the receive signal path may be configured to down-convert RF signals received from the FEM circuitry 408 based on the synthesized frequency provided by synthesizer circuitry 406d.

- the amplifier circuitry 406b may be configured to amplify the down- converted signals and the filter circuitry 406c may be a low-pass filter (LPF) or band-pass filter (BPF) configured to remove unwanted signals from the down-converted signals to generate output baseband signals.

- LPF low-pass filter

- BPF band-pass filter

- Output baseband signals may be provided to the baseband circuitry 404 for further processing.

- the output baseband signals may be zero-frequency baseband signals, although this is not a requirement.

- mixer circuitry 406a of the receive signal path may comprise passive mixers, although the scope of the embodiments is not limited in this respect.

- the mixer circuitry 406a of the transmit signal path may be configured to up-convert input baseband signals based on the synthesized frequency provided by the synthesizer circuitry 406d to generate RF output signals for the FEM circuitry 408.

- the baseband signals may be provided by the baseband circuitry 404 and may be filtered by filter circuitry 406c.

- the filter circuitry 406c may include a low-pass filter (LPF), although the scope of the embodiments is not limited in this respect.

- LPF low-pass filter

- the mixer circuitry 406a of the receive signal path and the mixer circuitry 406a of the transmit signal path may include two or more mixers and may be arranged for quadrature

- the mixer circuitry 406a of the receive signal path and the mixer circuitry 406a of the transmit signal path may include two or more mixers and may be arranged for image rejection (e.g., Hartley image rejection). In some embodiments, the mixer circuitry 406a of the receive signal path and the mixer circuitry 406a may be arranged for direct downconversion or direct upconversion, respectively. In some embodiments, the mixer circuitry 406a of the receive signal path and the mixer circuitry 406a of the transmit signal path may be configured for super-heterodyne operation.

- the output baseband signals and the input baseband signals may be analog baseband signals, although the scope of the embodiments is not limited in this respect. In some alternate

- the output baseband signals and the input baseband signals may be digital baseband signals.

- the RF circuitry 406 may include analog-to-digital converter (ADC) and digital-to-analog converter (DAC) circuitry and the baseband circuitry 404 may include a digital baseband interface to communicate with the RF circuitry 406.

- ADC analog-to-digital converter

- DAC digital-to-analog converter

- the baseband circuitry 404 may include a digital baseband interface to communicate with the RF circuitry 406.

- a separate radio IC circuitry may be provided for processing signals for each spectrum, although the scope of the embodiments is not limited in this respect.

- the synthesizer circuitry 406d may be a fractional-N synthesizer or a fractional N/N;1 synthesizer, although the scope of the embodiments is not limited in this respect as other types of frequency synthesizers may be suitable.

- synthesizer circuitry 406d may be a delta-sigma synthesizer, a frequency multiplier, or a synthesizer comprising a phase-locked loop with a frequency divider.

- the synthesizer circuitry 406d may be configured to synthesize an output frequency for use by the mixer circuitry 406a of the RF circuitry 406 based on a frequency input and a divider control input.

- the synthesizer circuitry 406d may be a fractional N/N;1 synthesizer.

- frequency input may be provided by a voltage controlled oscillator (VCO), although that is not a requirement.

- VCO voltage controlled oscillator

- Divider control input may be provided by either the baseband circuitry 404 or the applications processor 402 depending on the desired output frequency.

- a divider control input (e.g., N) may be determined from a look-up table based on a channel indicated by the applications processor 402.

- Synthesizer circuitry 406d of the RF circuitry 406 may include a divider, a delay-locked loop (DLL), a multiplexer and a phase accumulator.

- the divider may be a dual modulus divider (DMD) and the phase accumulator may be a digital phase accumulator (DPA).

- the DMD may be configured to divide the input signal by either N or N;1 (e.g., based on a carry out) to provide a fractional division ratio.

- the DLL may include a set of cascaded, tunable, delay elements, a phase detector, a charge pump and a D-type flip-flop.

- the delay elements may be configured to break a VCO period up into Nd equal packets of phase, where Nd is the number of delay elements in the delay line.

- Nd is the number of delay elements in the delay line.

- synthesizer circuitry 406d may be configured to generate a carrier frequency as the output frequency, while in other embodiments, the output frequency may be a multiple of the carrier frequency (e.g., twice the carrier frequency, four times the carrier frequency) and used in conjunction with quadrature generator and divider circuitry to generate multiple signals at the carrier frequency with multiple different phases with respect to each other.

- the output frequency may be a LO frequency (fLO).

- the RF circuitry 406 may include an IQ/polar converter.

- FEM circuitry 408 may include a receive signal path, which may include circuitry configured to operate on RF signals received from one or more of the antennas 410A-D, amplify the received signals and provide the amplified versions of the received signals to the RF circuitry 406 for further processing.

- FEM circuitry 408 may also include a transmit signal path which may include circuitry configured to amplify signals for transmission provided by the RF circuitry 406 for transmission by one or more of the one or more antennas 410A-D.

- the FEM circuitry 408 may include a TX/RX switch to switch between transmit mode and receive mode operation.

- the FEM circuitry may include a receive signal path and a transmit signal path.

- the receive signal path of the FEM circuitry may include a low-noise amplifier (LNA) to amplify received RF signals and provide the amplified received RF signals as an output (e.g., to the RF circuitry 406).

- LNA low-noise amplifier

- the transmit signal path of the FEM circuitry 408 may include a power amplifier (PA) to amplify input RF signals (e.g., provided by RF circuitry 406), and one or more filters to generate RF signals for subsequent transmission (e.g., by one or more of the one or more antennas 410.

- PA power amplifier

- the UE 400 may include additional elements such as, for example, memory/storage, display, camera, sensor, or input/output (I/O) interface.

- a single !permutation" technique for generating a polar code permutation vector may provide optimal performance with relatively low processing resource requirements.

- a large memory may be required during processing.

- 13 x 8192 106496 bits are required, which is 13KB (this large codeword is listed in Listing A).

- an approximation of the !permutation" (or permutation vector) may be utilized with smaller memory requirement with marginal performance degradation.

- a polar code permutation vector of a large codeword size may be represented using a permutation vector of a smaller size and a bit sequence. More specifically, two sets of small codeword

- permutation vectors may be generated. One is the small codeword permutation vector and the other may be prepared from the small codeword permutation vector and a value that represents the size of the permutation vector. The two smaller permutation vectors may then be compared with the long codeword (optimal) permutation. More specifically, indices from both small codeword permutation vectors are compared with a corresponding index in the optimal permutation to determine which one provides less offset from the optimal permutation. A corresponding position in the bit sequence is then marked with 1, if less offset is provided from the second permutation vector, otherwise the corresponding position in the bit sequence is marked with 0.

- the bit sequence can be represented by a binary run-length code, as further explained below.

- the device 400 of FIG.4, and/or circuitry of the device 400 such as the RF circuitry 406, the baseband circuitry 404, and/or other circuitry may be configured to: receive an indication of a codeword to be represented using polar codes, where the codeword size is larger than a small codeword size used to represent the codeword ⁇ generate a small codeword permutation and a bit sequence to represent the codeword ⁇ and send the represented codeword.

- the device 400 such as the RF circuitry 406, the baseband circuitry 404, and/or other circuitry may be configured to: generate a first polar code permutation of a first size and a first binary sequence ⁇ determine a permutation replica based on the first polar code permutation ⁇ and output indices from the first polar code permutation and the permutation replica based on the first binary sequence to form a second polar code permutation for the second size

- the electronic device 400 such as the RF circuitry 406, the baseband circuitry 404, and/or other circuitry may be configured to perform one or more processes, techniques, and/or methods as described herein, or portions thereof.

- One such process may include identifying or causing to identify a large codeword to be represented using polar codes ⁇ representing or causing to represent the large codeword using a small codeword permutation and a bit sequence ⁇ and transmitting or causing to transmit the represented codeword.

- Another such process may include acquiring or causing to acquire a first polar code permutation of a first size and a first binary sequence ⁇ obtaining or causing to obtain a permutation replica based on the first polar code permutation ⁇ and reading or causing to read out indices from the first polar code permutation and the permutation replica based on the first binary sequence to form a second polar code permutation for the second size.

- FIG.4 Even though the components of FIG.4 are discussed in reference to a UE, the same components and functionalities may also be associated with an evolved Node B (eNB).

- eNB evolved Node B

- FIG.5 is a diagram of a size N polar code generator in accordance with some embodiments.

- the generator 500 may include two polar code generators (502 and 504) for polar codes of size N/2.

- the order of bit positions within the permutation vector contains information of ordering of a bit channel at the information bit position where information bits are loaded in the order of permutation and according to the coding rate. Remaining bits may be filled with predetermined values, e.g. zeros.

- the optimal polar code permutation vector is of size N and the polar code construction rule is based on size N/2 polar code permutation vector.

- a size N permutation vector may be generated based on the following techniques described in FIG.6.

- FIG.6 is a flow diagram of a method for generating a representation of a polar code permutation vector using a smaller size polar code permutation vector and a bit sequence in accordance with some embodiments.

- the optimal permutation vector of size N is designated as !Opt" (ultimately, Opt will be represented by a polar code permutation vector of size N/2, Approx_Perm, and a bit sequence, BitSequence).

- the first smaller permutation vector of size N/2 is designated as Set1.

- a second polar code permutation vector is designated as Set2 and is generated by adding the size of the smaller permutation vector (i.e., N/2) to the first smaller permutation vector Set1.

- the initialization therefore, may be represented as follows:

- IDX [0:1:N-1]

- the Permutation_N/2 indicates the permutation vector for size N/2, and it contains information of ordering of bit channel at the information bit position where information bits are loaded in the order of permutation and according to coding rate, and remaining bits are filled with predetermined values (frozen), e.g. zeros.

- the Approx_Perm is the polar code construction (or polar code permutation vector) for size N polar code obtained using the N/2 polar code permutation vector and BitSequence is the bit index which indicates which of the two smaller permutations supplies each position in the larger permuatation.

- Approx_Perm is the smaller polar code permutation vector (of size N/2) which can be used with the BitSequence to represent the optimal (size N) polar code permutation vector (i.e., Opt).

- an iteration may be performed for values of K from 0 to (N-1), with K being increased by 1 at every iteration.

- BitSequence [BitSequence 0]

- BitSequence [BitSequence 0]

- Approx_Perm may replace the new size of Permutation_N/2 for a next size.

- the generated short codeword permutation vector with length N/2 may be used with BitSequence to construct size N permutation vector.

- the BitSequence can be represented by binary run-length code as follows:

- BitSequence [1111111111110111111110 *] may be represented as [12A1A8A*] or [12, 1, 8, *], where ?A# or ?,# represents the switching point of 1 or 0, and the number in front of that symbol is length of the run of 1s or 0s.

- the shortened index may be excluded from the Set1/Set2, and therefore, also from Approx_Perm and BitSequence.

- the shortened index may be predetermined, e.g. last S bits, where S is the number of bits to be shortened.

- permutation vector i.e., permutation vector with 64 values

- FIG.7 is a flow diagram illustrating example functionalities for generating a polar code permutation vector, in accordance with an example embodiment.

- the example method 700 may start at 702, when a plurality of input vectors may be generated by adding zeros to a set of input bits.

- the input vectors 112 may be generated by zero- padding the input bits 110 (FIG.1).

- a polar code permutation vector may be generated based on a plurality of estimates of channel reliability of a transmission channel. The plurality of estimates may be determined using a pre-defined range of signal-to-noise ratios (SNRs) of the transmission channel (e.g., 302 at FIG.3).

- SNRs signal-to-noise ratios

- the permutation vector may be applied to the plurality of input vectors to obtain a plurality of output permuted vectors.

- the permutation vector 104 may be applied to the input vectors 112 to obtain a plurality of output permuted vectors 114.

- the plurality of output permuted vectors may be polar coded using a generator matrix, to generate an encoded information block for transmission to an evolved Node-B (eNB) via the transmission channel.

- eNB evolved Node-B

- the permuted vectors 114 may be polar coded using the generator matrix 106.

- the permutation vector (e.g., 104) may indicate positions of the input bits within the output vectors associated with a block error rate (BLER) below a threshold level.

- BLER block error rate

- FIG.8 illustrates a block diagram of a communication device such as an eNB or a UE, in accordance with some embodiments.

- the communication device 800 may operate as a standalone device or may be connected (e.g., networked) to other communication devices.

- the communication device 800 may operate in the capacity of a server communication device, a client communication device, or both in server-client network environments.

- the communication device 800 may act as a peer

- the communication device 800 may be a UE, eNB, PC, a tablet PC, a STB, a PDA, a mobile telephone, a smart phone, a web appliance, a network router, switch or bridge, or any communication device capable of executing instructions (sequential or otherwise) that specify actions to be taken by that communication device.

- the term %communication device% shall also be taken to include any collection of communication devices that individually or jointly execute a set (or multiple sets) of instructions to perform any one or more of the methodologies discussed herein, such as cloud computing, software as a service (SaaS), other computer cluster configurations.

- Examples, as described herein, may include, or may operate on, logic or a number of components, modules, or mechanisms.

- Modules are tangible entities (e.g., hardware) capable of performing specified operations and may be configured or arranged in a certain manner.

- circuits may be arranged (e.g., internally or with respect to external entities such as other circuits) in a specified manner as a module.

- the whole or part of one or more computer systems (e.g., a standalone, client or server computer system) or one or more hardware processors may be configured by firmware or software (e.g., instructions, an application portion, or an application) as a module that operates to perform specified operations.

- the software may reside on a communication device readable medium.

- the software when executed by the underlying hardware of the module, causes the hardware to perform the specified operations.

- %module% is understood to encompass a tangible entity, be that an entity that is physically constructed, specifically configured (e.g., hardwired), or temporarily (e.g., transitorily) configured (e.g., programmed) to operate in a specified manner or to perform part or all of any operation described herein.

- modules are temporarily configured, each of the modules need not be instantiated at any one moment in time.

- the modules comprise a general- purpose hardware processor configured using software

- the general-purpose hardware processor may be configured as respective different modules at different times.

- Software may accordingly configure a hardware processor, for example, to constitute a particular module at one instance of time and to constitute a different module at a different instance of time.

- Communication device 800 may include a hardware processor 802 (e.g., a central processing unit (CPU), a graphics processing unit (GPU), a hardware processor core, or any combination thereof), a main memory 804 and a static memory 806, some or all of which may communicate with each other via an interlink (e.g., bus) 808.

- the communication device 800 may further include a display unit 810, an alphanumeric input device 812 (e.g., a keyboard), and a user interface (UI) navigation device 814 (e.g., a mouse).

- the display unit 810, input device 812 and UI navigation device 814 may be a touch screen display.

- the communication device 800 may additionally include a storage device (e.g., drive unit) 816, a signal generation device 818 (e.g., a speaker), a network interface device 820, and one or more sensors 821, such as a global positioning system (GPS) sensor, compass, accelerometer, or other sensor.

- the communication device 800 may include an output controller 828, such as a serial (e.g., universal serial bus (USB), parallel, or other wired or wireless (e.g., infrared (IR), near field communication (NFC), etc.) connection to communicate or control one or more peripheral devices (e.g., a printer, card reader, etc.).

- a serial e.g., universal serial bus (USB), parallel, or other wired or wireless (e.g., infrared (IR), near field communication (NFC), etc.) connection to communicate or control one or more peripheral devices (e.g., a printer, card reader, etc.).

- USB universal serial bus

- NFC

- the storage device 816 may include a communication device readable medium 822 on which is stored one or more sets of data structures or instructions 824 (e.g., software) embodying or utilized by any one or more of the techniques or functions described herein.

- the instructions 824 may also reside, completely or at least partially, within the main memory 804, within static memory 806, or within the hardware processor 802 during execution thereof by the communication device 800.

- one or any combination of the hardware processor 802, the main memory 804, the static memory 806, or the storage device 816 may constitute communication device readable media.

- the communication device readable medium 822 is illustrated as a single medium, the term %communication device readable medium% may include a single medium or multiple media (e.g., a centralized or distributed database, and/or associated caches and servers) configured to store the one or more instructions 824.

- the term %communication device readable medium% may include any medium that is capable of storing, encoding, or carrying instructions for execution by the communication device 800 and that cause the communication device 800 to perform any one or more of the techniques of the present disclosure, or that is capable of storing, encoding or carrying data structures used by or associated with such instructions.

- Non-limiting communication device readable medium examples may include solid-state memories, and optical and magnetic media. Specific examples of

- communication device readable media may include: non-volatile memory, such as semiconductor memory devices (e.g., Electrically Programmable Read-Only Memory (EPROM), Electrically Erasable Programmable Read- Only Memory (EEPROM)) and flash memory devices ⁇ magnetic disks, such as internal hard disks and removable disks ⁇ magneto-optical disks ⁇ Random Access Memory (RAM) ⁇ and CD-ROM and DVD-ROM disks.

- non-volatile memory such as semiconductor memory devices (e.g., Electrically Programmable Read-Only Memory (EPROM), Electrically Erasable Programmable Read- Only Memory (EEPROM)) and flash memory devices ⁇ magnetic disks, such as internal hard disks and removable disks ⁇ magneto-optical disks ⁇ Random Access Memory (RAM) ⁇ and CD-ROM and DVD-ROM disks.

- communication device readable media may include non-transitory communication device readable media.

- communication device readable media may include communication device readable media that is not a transitory propagating signal.

- the instructions 824 may further be transmitted or received over a communications network 826 using a transmission medium via the network interface device 820 utilizing any one of a number of transfer protocols (e.g., frame relay, internet protocol (IP), transmission control protocol (TCP), user datagram protocol (UDP), hypertext transfer protocol (HTTP), etc.).

- transfer protocols e.g., frame relay, internet protocol (IP), transmission control protocol (TCP), user datagram protocol (UDP), hypertext transfer protocol (HTTP), etc.

- Example communication networks may include a local area network (LAN), a wide area network (WAN), a packet data network (e.g., the Internet), mobile telephone networks (e.g., cellular networks), Plain Old Telephone (POTS) networks, and wireless data networks (e.g., Institute of Electrical and Electronics Engineers (IEEE) 802.11 family of standards known as Wi-Fi®, IEEE 802.16 family of standards known as WiMax®), IEEE 802.15.4 family of standards, a Long Term Evolution (LTE) family of standards, a Universal Mobile Telecommunications System (UMTS) family of standards, peer-to-peer (P2P) networks, among others.

- LAN local area network

- WAN wide area network

- POTS Plain Old Telephone

- wireless data networks e.g., Institute of Electrical and Electronics Engineers (IEEE) 802.11 family of standards known as Wi-Fi®, IEEE 802.16 family of standards known as WiMax®

- IEEE 802.15.4 family of standards e.g., Institute of Electrical and Electronics Engineers (IEEE

- the network interface device 820 may include one or more physical jacks (e.g., Ethernet, coaxial, or phone jacks) or one or more antennas to connect to the communications network 826.

- the network interface device 820 may include a plurality of antennas to wirelessly communicate using at least one of single-input multiple-output (SIMO), MIMO, or multiple-input single-output (MISO) techniques.

- SIMO single-input multiple-output

- MIMO multiple-input single-output

- MISO multiple-input single-output

- the network interface device 820 may wirelessly communicate using Multiple User MIMO techniques.

- the term %transmission medium% shall be taken to include any intangible medium that is capable of storing, encoding or carrying instructions for execution by the communication device 800, and includes digital or analog communications signals or other intangible medium to facilitate

- UE user equipment

- eNB Evolved Node-B

- functionalities described herein as being performed by the UE may be performed by the eNB, and vice versa (i.e., the polar code

- Example 1 is an apparatus of a user equipment (UE), the apparatus comprising: memory ⁇ and processing circuitry coupled to the memory, the processing circuitry configured to: generate input vectors by adding zeros to a set of input bits ⁇ generate a polar code permutation vector based on estimates of channel reliability of a transmission channel, the estimates determined using a pre-defined range of signal-to-noise ratios (SNRs) of the transmission channel ⁇ apply the polar code permutation vector to the input vectors to obtain output permuted vectors ⁇ and polar code the output permuted vectors using a generator matrix, to generate an encoded information block for transmission to an evolved Node-B (eNB) via the transmission channel, wherein the polar code permutation vector indicates positions of the input bits within the output permuted vectors associated with a block error rate (BLER) below a threshold level.

- SNRs signal-to-noise ratios

- Example 2 the subject matter of Example 1 optionally includes wherein to generate the polar code permutation vector, the processing circuitry is further configured to: initialize the polar code permutation vector as an empty vector.

- Example 3 the subject matter of Example 2 optionally includes wherein to generate the polar code permutation vector, the processing circuitry is further configured to: iterate between a minimum SNR and a maximum SNR at a pre-determined SNR increment value, to generate the estimates of channel reliability, wherein each estimate of channel reliability is associated with one or more construction codes indicating output bit positions with the BLER below the threshold level.

- Example 4 the subject matter of Example 3 optionally includes wherein to generate the polar code permutation vector, the processing circuitry is further configured to: for SNR values between the minimum SNR and the maximum SNR, iterate with increments at the pre-determined SNR increment value: for a particular one of the input vectors, select a

- Example 5 the subject matter of Example 4 optionally includes wherein to generate the polar code permutation vector, the processing circuitry is further configured to, during the iteration: select a construction code from the one or more construction codes, associated with a highest channel rate among the determined channel rates ⁇ and append new bit positions associated with the selected construction code to the polar code permutation vector.

- Example 6 the subject matter of Example 5 optionally includes wherein to generate the polar code permutation vector, the processing circuitry is further configured to, during the iteration: determine for the selected construction code and the highest channel rate, whether the new bit positions are a superset of a previous polar code permutation vector generated during a previous iteration ⁇ and append the new bit positions to the polar code permutation vector upon determining that the new bit positions are a superset of the previous polar code permutation vector.

- Example 7 the subject matter of Example 6 optionally includes wherein to generate the polar code permutation vector, the processing circuitry is further configured to, subsequent to the iteration: determine whether a number of bit positions within the polar code permutation vector matches a number of inputs to the generator matrix ⁇ and upon determining one or more bit positions are missing, add the missing bit positions to the polar code permutation vector.

- Example 8 the subject matter of any one or more of Examples 1@7 optionally include wherein the generator matrix is of a type denotes a Kronecker power and N denotes a size of the output permuted vectors.

- Example 9 the subject matter of any one or more of Examples 1@8 optionally include wherein a number of the input vectors matches a number of bit positions within the polar code permutation vector.

- Example 10 the subject matter of any one or more of Examples 1@9 optionally include wherein the processing circuitry is further configured to: generate a second polar code permutation vector based on the estimates of channel reliability of a transmission channel, wherein the second polar code permutation vector is smaller than the polar code permutation vector.

- Example 11 the subject matter of Example 10 optionally includes wherein the second polar code permutation vector is half the size of the polar code permutation vector.

- Example 12 the subject matter of any one or more of Examples 10@11 optionally include wherein the processing circuitry is further configured to: generate a third polar code permutation vector using the second polar code permutation vector and a size of the second polar code permutation vector ⁇ generate a bit sequence of size equal to the size of the polar code permutation vector, wherein a bit at a bit position in the bit sequence indicates whether a value at the bit position within the polar code permutation vector is the same as a value at the bit position within the polar code permutation vector or a value at the bit position within the second polar code permutation vector.

- Example 13 the subject matter of Example 12 optionally includes wherein the processing circuitry is further configured to: encode the third polar code permutation vector and the bit sequence as a representation of the polar code permutation vector, for transmission to the eNB.

- Example 14 the subject matter of any one or more of Examples 1@13 optionally include a transceiver coupled to an antenna, the transceiver configured to transmit the encoded information block to the eNB.

- Example 15 is an apparatus of an evolved Node B (eNB) configured to communicate with a user equipment (UE), the apparatus comprising: memory ⁇ and processing circuitry, the processing circuitry configured to: acquire a bit sequence and a first polar code permutation vector from the memory ⁇ generate using the bit sequence and the first polar code permutation vector, a second polar code permutation vector, the second polar code permutation vector having a number of bit positions that is a multiple of a number of bit positions within the first polar code permutation vector ⁇ apply the second polar code permutation vector to input vectors to obtain output permuted vectors ⁇ and polar code the output permuted vectors using a generator matrix, to generate an encoded information block for transmission to the UE via a transmission channel.

- eNB evolved Node B

- UE user equipment

- Example 16 the subject matter of Example 15 optionally includes wherein the processing circuitry is further configured to: generate a third polar code permutation vector using the first polar code permutation vector and the number of bit positions within the first polar code permutation vector.

- the processing circuitry is further configured to: add the number of bit positions within the first polar code permutation vector to each vector value within the first polar code permutation vector to generate the third polar code permutation vector.

- Example 18 the subject matter of any one or more of Examples 16@17 optionally include wherein: the bit sequence comprises a plurality of bits at a corresponding plurality of bit positions ⁇ and a bit at a bit position of the plurality of bit positions indicates whether a value at the bit position within the second polar code permutation vector is determined based on a value at the bit position within the first polar code permutation vector or a value at the bit position within the third polar code permutation vector.

- Example 19 is a computer-readable storage medium that stores instructions for execution by one or more processors of a user equipment (UE), the one or more processors to configure the UE to: generate input vectors by adding zeros to a set of input bits ⁇ iterate between a minimum SNR and a maximum SNR at a pre-determined SNR increment value, to generate estimates of channel reliability of a transmission channel ⁇ generate a polar code permutation vector based on estimates of channel reliability of the transmission channel ⁇ apply the polar code permutation vector to the input vectors to obtain output permuted vectors ⁇ and polar code the output permuted vectors using a generator matrix, to generate an encoded information block for transmission to an evolved Node-B (eNB) via the transmission channel, wherein each estimate of channel reliability is associated with one or more construction codes indicating output bit positions with the BLER below the threshold level, and wherein the polar code permutation vector indicates positions of the input bits within the output vectors associated with a block error rate (BLER) below a threshold

- Example 20 the subject matter of Example 19 optionally includes wherein to generate the polar code permutation vector, the one or more processors further configure the UE to: initialize the polar code permutation vector as an empty vector.

- the subject matter of Example 20 optionally includes wherein to generate the permutation vector, the one or more processors further configure the UE to: select a construction code from the one or more construction codes, associated with a highest channel rate among the determined plurality of channel rates ⁇ and append new bit positions associated with the selected construction code to the permutation vector.

- Example 22 the subject matter of Example 21 optionally includes wherein to generate the permutation vector, the one or more processors further configure the UE to: determine for the selected construction code and the highest channel rate, whether the new bit positions are a superset of a previous polar code permutation vector generated during a previous iteration ⁇ and append the new bit positions to the polar code permutation vector upon determining that the new bit positions are a superset of the previous permutation vector.

- Example 23 the subject matter of Example 22 optionally includes wherein to generate the permutation vector, the one or more processors further configure the UE to: determine whether a number of bit positions within the polar code permutation vector matches a number of inputs to the generator matrix ⁇ and upon determining the number of bit positions within the polar code permutation vector does not match a number of inputs to the generator matrix and one or more bit positions are missing, add the missing bit positions to the polar code permutation vector.

- Example 24 the subject matter of any one or more of Examples 19@23 optionally include wherein the one or more processors further configure the UE to: generate a second polar code permutation vector based on the plurality estimates of channel reliability of a transmission channel, wherein the second polar code permutation vector comprises a number of values that is smaller than a number of values within the polar code permutation vector.

- Example 25 the subject matter of Example 24 optionally includes wherein the one or more processors further configure the UE to: generate a third polar code permutation vector using the second polar code permutation vector and the number of values within the second polar code permutation vector.

- Example 26 the subject matter of Example 25 optionally includes wherein the one or more processors further configure the UE to: generate a bit sequence comprising a plurality of bits, wherein a number of the plurality of bits within the bit sequence is equal to the number of values within the polar code permutation vector, wherein a bit at a bit position in the bit sequence indicates whether a value at the bit position within the polar code permutation vector is the same as a value at the bit position within the polar code permutation vector or a value at the bit position within the second polar code permutation vector.

- Example 27 the subject matter of Example 26 optionally includes wherein the one or more processors further configure the UE to: generate a binary run-length code based on the bit sequence ⁇ and encode the second polar code permutation vector and the binary run-length code as a representation of the polar code permutation vector, for transmission to the eNB.

- Example 28 is an apparatus of a user equipment (UE), the apparatus comprising: means for generating input vectors by adding zeros to a set of input bits ⁇ means for generating a polar code permutation vector based on estimates of channel reliability of a transmission channel, the estimates determined using a pre-defined range of signal-to-noise ratios (SNRs) of the transmission channel ⁇ means for applying the polar code permutation vector to the input vectors to obtain output permuted vectors ⁇ and means for polar coding the output permuted vectors using a generator matrix, to generate an encoded information block for transmission to an evolved Node-B (eNB) via the transmission channel, wherein the polar code permutation vector indicates positions of the input bits within the output permuted vectors associated with a block error rate (BLER) below a threshold level.

- SNRs signal-to-noise ratios

- Example 29 the subject matter of Example 28 optionally includes means for initializing the polar code permutation vector as an empty vector.

- the subject matter of Example 29 optionally includes means for iterating between a minimum SNR and a maximum SNR at a pre-determined SNR increment value, to generate the estimates of channel reliability, wherein each estimate of channel reliability is associated with one or more construction codes indicating output bit positions with the BLER below the threshold level.

- Example 31 the subject matter of Example 30 optionally includes for SNR values between the minimum SNR and the maximum SNR, with increments at the pre-determined SNR increment value: means for selecting a corresponding channel reliability estimate of the estimates of channel reliability, for a particular one of the input vectors ⁇ and means for determining channel rates at which the one or more construction codes associated with the channel reliability estimate satisfy the BLER being below the threshold level.

- Example 32 the subject matter of Example 31 optionally includes means for selecting a construction code from the one or more construction codes, associated with a highest channel rate among the determined channel rates ⁇ and means for appending new bit positions associated with the selected construction code to the polar code permutation vector.

- Example 33 the subject matter of Example 32 optionally includes means for determining for the selected construction code and the highest channel rate, whether the new bit positions are a superset of a previous polar code permutation vector generated during a previous iteration ⁇ and means for appending the new bit positions to the polar code permutation vector upon determining that the new bit positions are a superset of the previous polar code permutation vector.

- embodiments may include fewer features than those disclosed in a particular example.

- the following claims are hereby incorporated into the Detailed Description, with a claim standing on its own as a separate embodiment.

- the scope of the embodiments disclosed herein is to be determined with reference to the appended claims, along with the full scope of equivalents to which such claims are entitled.

- Listing A Permutations for lengths 64, 128, 256, 512, 1024, 2048, 4096, 8192.

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Probability & Statistics with Applications (AREA)

- Theoretical Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Mobile Radio Communication Systems (AREA)

Abstract

Disclosed herein are user equipment (UE) and base station (eNB) apparatus and methodology for polar code construction, representation and encoding/decoding. An apparatus of a UE may include memory and processing circuitry coupled to the memory. The processing circuitry is configured to generate input vectors by adding zeros to a set of input bits. A polar code permutation vector is generated based on estimates of channel reliability of a transmission channel. The estimates are determined using a pre-defined range of signal-to-noise ratios (SNRs) of the transmission channel. The polar code permutation vector is applied to the input vectors to obtain a output permuted vectors. The output permuted vectors are polar coded using a generator matrix, to generate an encoded information block for transmission to an evolved Node-B (eNB) via the transmission channel.

Description

CONSTRUCTING, REPRESENTING, AND ENCODING POLAR CODES PRIORITY CLAIM

[0001] This application claims the benefit of priority to United States Provisional Patent Application Serial No.62/335,261, filed May 12, 2016, and entitled !CONSTRUCTING, REPRESENTING, AND ENCODING POLAR CODES," and United States Provisional Patent Application Serial No.62/336,402, filed May 13, 2016, and entitled !POLAR CODE

CONSTRUCTION," which applications are incorporated herein by reference in their entireties. TECHNICAL FIELD

[0002] Embodiments pertain to wireless communications. Some embodiments relate to constructing, representing and encoding polar codes. BACKGROUND

[0003] With the increase in different types of devices communicating with various network devices, usage of 3GPP LTE systems has increased. The penetration of mobile devices (user equipment or UEs) in modern society has continued to drive demand for a wide variety of networked devices in a number of disparate environments. The use of networked UEs using 3GPP LTE systems has increased in all areas of home and work life. Fifth generation (5G) wireless systems are forthcoming, and are expected to enable even greater speed, connectivity, and usability.

[0004] One concern with wireless communications is using reliable error correction techniques. Polar coding is a new error correction coding technique with theoretical guarantees to achieve the capacity of

communication channels. One of the main drawbacks of known polar codes is that their performance under successive cancellation (SC) decoding is inferior to that of turbo and low-density parity-check (LDPC) codes. More involved decoders like list decoders and maximum likelihood (ML) decoders improve

known polar codes# performance only marginally. Known polar code constructions become efficient only when aided by an additional cyclic redundancy check (CRC), which contributes to increased system complexity and processing times. BRIEF DESCRIPTION OF THE FIGURES

[0005] In the figures, which are not necessarily drawn to scale, like numerals may describe similar components in different views. Like numerals having different letter suffixes may represent different instances of similar components. Some embodiments are illustrated by way of example, and not limitation, in the following figures of the accompanying drawings.

[0006] FIG.1 is a diagram of a polar code encoder in accordance with some embodiments.

[0007] FIG.2 is a flow diagram of a method to encode input bits using a polar code in accordance with some embodiments.

[0008] FIG.3 is a flow diagram of a method to generate a polar code in accordance with some embodiments.

[0009] FIG.4 is a functional diagram of a User Equipment (UE) using a polar encoder in accordance with some embodiments.

[0010] FIG.5 is a diagram of a size N polar code generator in accordance with some embodiments.

[0011] FIG.6 is a flow diagram of a method for generating a representation of a polar code permutation vector using a smaller size polar code permutation vector and a bit sequence in accordance with some embodiments.

[0012] FIG.7 is a flow diagram illustrating example functionalities for generating a polar code permutation vector, in accordance with an example embodiment.

[0013] FIG.8 illustrates a block diagram of a communication device such as an Evolved Node-B (eNB) or a user equipment (UE), in accordance with some embodiments.

DETAILED DESCRIPTION

[0014] The following description and the drawings sufficiently illustrate specific embodiments to enable those skilled in the art to practice them. A number of examples are described in the context of 3GPP

communication systems and components thereof. It will be understood that principles of the embodiments are applicable in other types of communication systems, such as Wi-Fi or Wi-Max networks, Bluetooth or other personal-area networks, Zigbee or other home-area networks, wireless mesh networks, and the like, without limitation, unless expressly limited by a corresponding claim. Given the benefit of the present disclosure, persons skilled in the relevant technologies will be able to engineer suitable variations to implement principles of the embodiments in other types of communication systems. Various diverse embodiments may incorporate structural, logical, electrical, process, and other differences. Portions and features of some embodiments may be included in, or substituted for, those of other embodiments.

Embodiments set forth in the claims encompass all presently-known, and after-arising, equivalents of those claims.

[0015] FIG.1 is a diagram of a polar code encoder in accordance with some embodiments. Referring to FIG.1, the polar code encoder 100 may include a zero padding block 102, a polar code permutation block 104 and a generator matrix GN 106, where N is the size of the polar code encoder and the number of generated output bits.

[0016] Polar codes belong to a class of affine codes that can be generated by subsets of the rows of the generator matrix 106:

, where denotes a Kronecker power. In some embodiments, a rate code (which may or may not be used as a polar code) may be generated by picking any K rows of as a generator matrix. One or more codes in this class can be encoded by the matrix multiplication , where is set to a data bit if the i^th row of is in the code's generator matrix, and otherwise

is set to a predetermined value, e.g., zeros. Such a code can be referred to as a polar code if its generator matrix includes K rows of that satisfy row is in the matrix and row is not. Here, is the channel associated with bit i, with input and output , where denotes the output of the channel with input denotes the

Bhattacharyya parameter, which is the reliability associated with communicating the ith bit on the W(i) channel. The order of

depends on the underlying channel and thus polar codes are channel-specific designs. These codes may have good performance under successive cancellation (SC) decoding and indeed achieve channel capacity. Although very few codes are true polar codes according to this strict definition (in particular, if the order of s is unique for a given W, there is a unique polar code for that channel and given rate), many codes that do not necessarily adhere to the above rule may be called polar codes. In some embodiments, all of these codes share the property that be %small% if the i^th row is included in the generator matrix. Embodiments of the present disclosure also follow this practice and thus the codes here will also be called polar codes.

[0018] Embodiments of the present disclosure are directed to a class of polar codes that have excellent performance under list decoding, without the aid of an external CRC. This simplifies their decoding, and eliminates CRC overhead. In addition, a single %permutation% is used to represent codes of arbitrary rates. That is, for a given code length, codes of all rates can be encoded using the same mechanism. [0019] The reliability of each bit under SC decoding can be estimated closely by a recursive %polarize--quantize% technique. A linear-time algorithm may be used to estimate values very closely and one or more of the most reliable bits may be selected. However, this bit selection only optimizes performance under SC decoder, but this performance itself is may not be compatible with other alternatives like Turbo and LDPC codes. In contrast, embodiments of the code constructions in the present disclosure may

be only slightly less optimal under SC decoding, but are significantly superior to other constructions under list decoding. Additionally, unlike other constructions, these codes do not need the CRC to improve decoding performance.

[0020] Referring to FIG.1, K input data bits 110 (V1, *, Vk) are to be encoded by a rate K/N code. In order to do so, the zero padding block 102 may be used to zero pad the input bits 110 V1, *, Vk with (N-K) bits of predetermined values (for example, zero bits) to obtain the length N vector 112 . This vector is then permuted by the polar code permutation vector PN 104, and the permuted N-bit vector 114 is

communicated as input to the generator matrix 106, which generates the polar coded data bits 116. The selection of the polar code permutation vector 104 may depend on N, but not on K. Therefore, codes of all rates at a given length N may be encoded by the same encoder 100.

[0021] FIG.2 is a flow diagram of a method to encode input bits using a polar code in accordance with some embodiments. Referring to FIGS.1 and 2, the example method 200 may start at 202, when a length N input vector (e.g., 112) may be generated based on K input data bits (e.g., 110), where K and N may be integers with K being less than or equal to than N. In an example, the input data bits 110 may be zero-padded so that the input vector 112 of length N is generated, which may include the K input bits and (N-K) zeros (or other predetermined bits). At 204, the input vector 112 is permuted by the polar code permutation vector 104 to generate the permuted N-bit vector 114. At 206, the permuted N-bit vector 114 is encoded by the generator matrix GN 106 to generate coded data bits XN 116 as output. At 208, the coded data bits XN 116 can be transmitted.

[0022] Example polar code permutation vectors (that is, permutations) for code lengths are given in Listing A below. One or more other permutation vectors may be derived from the permutations listed in Listing A. For example, if system requirements dictate that data be encoded at rates

then any permutation derived from by permuting the first numbers among

themselves can be used. Similarly, the numbers can be permuted among themselves, and so can the numbers , and so on.

Alternatively, any other permutation that can be derived from may be used as well. One suitable class of such permutations is defined by setting a threshold , with all numbers in the derived permutation being at most positions away from their positions in . In other words, if is the derived permutation, the following condition is satisfied for some

. Such a derived permutation may be preferred if, for instance, it can be more efficiently represented in memory. In this regard, there may be a trade-off between how large is and how robust a

performance the derived permutation will have. Thus the choice of the derived permutation may be based on error performance versus

implementation efficiency considerations.

[0023] Design of the polar code permutation vectors (or permutations) listed in Listing A.

[0024] Approximately optimal polar codes for SC decoding may be constructed using the %polarize--quantize% technique. However, bit selection using this technique may not lead to codes that are competitive with the state- of-the-art LDPC or Turbo codes unless the decoding of these polar codes is augmented by a CRC stage. The quantization technique used in embodiments of the present disclosure to estimate the bit reliabilities leads to only slight performance loss under SC decoding (which in many cases may not be the decoder of choice), but dramatically improves performance under list decoding.

[0025] In some embodiments, generation of the permutations listed in Listing A may start by estimating the bit-channel reliabilities for all channel signal-to-noise ratios (SNRs) from, e.g., -8dB to 11dB, with 0.5dB increments. These constructions are then tested at different rates and channel conditions. In some examples, the construction SNR that achieves optimal performance may be between 0dB and 2dB above the true channel SNR.

[0026] The permutations may be generated using the technique described below and illustrated in the flow diagram of FIG.3. FIG.3 is a flow diagram of a method 300 to generate a polar code in accordance with some embodiments.

[0027] At 302, the permutation vector length may be fixed at length N. Bit-channel estimation may be performed with underlying transmission channel SNRs ranging from , with increments of . In this regard, a plurality of estimates of channel reliability (e.g., Z(Wi)) may be generated for a transmission channel W(i). For example, to derive the permutations in Listing A, the following SNR values may be used:

, and . In the description below, the underlying channel SNR may be referred to as .

[0028] At 304, the polar code permutation vector is initialized as an empty permutation vector. At the end of the flow diagram in FIG.3 this vector will have length N.

[0029] At 306, an iteration loop may be performed with SNR values of with increments at SNRinc. At 308, for construction rules at

, the rate may be found, at which each construction rule achieves a target block error rate (BLER) (e.g., BLER=1+ or another predetermined rate). At 310, the construction rule with the highest rate may be selected. At 312, it may be determined for the selected construction rule and its rate, whether the data bits associated with the rule are a superset of a previous permutation vector (e.g., a permutation vector generated during a previous iteration cycle). At 316, when the data bits associated with the rule are a superset of the previous permutation vector, then the new bit positions are appended to the permutation vector. At 314, when the data bits associated with the rule are not a superset of the previous permutation vector, then the next best construction rule is selected and processing may resume at 308. In instances when no construction rule passes the test in 308, then an error notification may be presented and no permutation vector is generated. At 318, the permutation vector may be appended with any

missing bit positions so that a total of N positions are included in the permutation vector.

[0030] In some embodiments, the above technique may simultaneously provide that the constructed codes are nested so that codes of lower rate are sub-codes of those at higher rates, and that codes of all rates have error performance that satisfies a pre-determined error rate. Many refinements and variations on the above technique are possible. For example, a more finely nested construction may be obtained by considering construction and channel SNRs at smaller SNR increments.

[0031] FIG.4 is a functional diagram of a User Equipment (UE) using a polar encoder in accordance with some embodiments. In some

embodiments, the UE 400 may include application circuitry 402, baseband circuitry 404, Radio Frequency (RF) circuitry 406, front-end module (FEM) circuitry 408, and multiple antennas 410A-410D, coupled together at least as shown. In some embodiments, other circuitry or arrangements may include one or more elements or components of the application circuitry 402, the baseband circuitry 404, the RF circuitry 406 or the FEM circuitry 408, and may also include other elements or components in some cases. As an example, !processing circuitry" may include one or more elements or components, some or all of which may be included in the application circuitry 402 or the baseband circuitry 404. As another example, !transceiver circuitry" may include one or more elements or components, some or all of which may be included in the RF circuitry 406 or the FEM circuitry 408. These examples are not limiting, however, as the processing circuitry or the transceiver circuitry may also include other elements or components in some cases.

[0032] The application circuitry 402 may include one or more application processors. For example, the application circuitry 402 may include circuitry such as, but not limited to, one or more single-core or multi- core processors. The processor(s) may include any combination of general- purpose processors and dedicated processors (e.g., graphics processors, application processors, etc.). The processors may be coupled with or may include memory/storage and may be configured to execute instructions stored in the memory/storage to enable various applications or operating systems to

run on the system to perform one or more of the functionalities described herein.

[0033] The baseband circuitry 404 may include circuitry such as, but not limited to, one or more single-core or multi-core processors. The baseband circuitry 404 may include one or more baseband processors or control logic to process baseband signals received from a receive signal path of the RF circuitry 406 and to generate baseband signals for a transmit signal path of the RF circuitry 406. Baseband processing circuity 404 may interface with the application circuitry 402 for generation and processing of the baseband signals and for controlling operations of the RF circuitry 406. For example, in some embodiments, the baseband circuitry 404 may include a second generation (2G) baseband processor 404a, third generation (3G) baseband processor 404b, fourth generation (4G) baseband processor 404c, or other baseband processor(s) 404d for other existing generations, generations in development or to be developed in the future (e.g., fifth generation (5G), 6G, etc.). The baseband circuitry 404 (e.g., one or more of baseband processors 404a-d) may handle various radio control functions that enable

communication with one or more radio networks via the RF circuitry 406.