WO2001054181A2 - Process and apparatus for cleaning silicon wafers - Google Patents

Process and apparatus for cleaning silicon wafers Download PDFInfo

- Publication number

- WO2001054181A2 WO2001054181A2 PCT/US2001/002119 US0102119W WO0154181A2 WO 2001054181 A2 WO2001054181 A2 WO 2001054181A2 US 0102119 W US0102119 W US 0102119W WO 0154181 A2 WO0154181 A2 WO 0154181A2

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- wafer

- cleaning

- particles

- volts

- face

- Prior art date

Links

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02041—Cleaning

- H01L21/02043—Cleaning before device manufacture, i.e. Begin-Of-Line process

- H01L21/02052—Wet cleaning only

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B08—CLEANING

- B08B—CLEANING IN GENERAL; PREVENTION OF FOULING IN GENERAL

- B08B3/00—Cleaning by methods involving the use or presence of liquid or steam

- B08B3/04—Cleaning involving contact with liquid

- B08B3/10—Cleaning involving contact with liquid with additional treatment of the liquid or of the object being cleaned, e.g. by heat, by electricity or by vibration

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23G—CLEANING OR DE-GREASING OF METALLIC MATERIAL BY CHEMICAL METHODS OTHER THAN ELECTROLYSIS

- C23G1/00—Cleaning or pickling metallic material with solutions or molten salts

- C23G1/02—Cleaning or pickling metallic material with solutions or molten salts with acid solutions

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23G—CLEANING OR DE-GREASING OF METALLIC MATERIAL BY CHEMICAL METHODS OTHER THAN ELECTROLYSIS

- C23G1/00—Cleaning or pickling metallic material with solutions or molten salts

- C23G1/14—Cleaning or pickling metallic material with solutions or molten salts with alkaline solutions

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25F—PROCESSES FOR THE ELECTROLYTIC REMOVAL OF MATERIALS FROM OBJECTS; APPARATUS THEREFOR

- C25F1/00—Electrolytic cleaning, degreasing, pickling or descaling

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/67005—Apparatus not specifically provided for elsewhere

- H01L21/67011—Apparatus for manufacture or treatment

- H01L21/67017—Apparatus for fluid treatment

- H01L21/67028—Apparatus for fluid treatment for cleaning followed by drying, rinsing, stripping, blasting or the like

- H01L21/6704—Apparatus for fluid treatment for cleaning followed by drying, rinsing, stripping, blasting or the like for wet cleaning or washing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/67005—Apparatus not specifically provided for elsewhere

- H01L21/67011—Apparatus for manufacture or treatment

- H01L21/67017—Apparatus for fluid treatment

- H01L21/67028—Apparatus for fluid treatment for cleaning followed by drying, rinsing, stripping, blasting or the like

- H01L21/6704—Apparatus for fluid treatment for cleaning followed by drying, rinsing, stripping, blasting or the like for wet cleaning or washing

- H01L21/67057—Apparatus for fluid treatment for cleaning followed by drying, rinsing, stripping, blasting or the like for wet cleaning or washing with the semiconductor substrates being dipped in baths or vessels

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/67005—Apparatus not specifically provided for elsewhere

- H01L21/67011—Apparatus for manufacture or treatment

- H01L21/67017—Apparatus for fluid treatment

- H01L21/67028—Apparatus for fluid treatment for cleaning followed by drying, rinsing, stripping, blasting or the like

- H01L21/6704—Apparatus for fluid treatment for cleaning followed by drying, rinsing, stripping, blasting or the like for wet cleaning or washing

- H01L21/67051—Apparatus for fluid treatment for cleaning followed by drying, rinsing, stripping, blasting or the like for wet cleaning or washing using mainly spraying means, e.g. nozzles

Definitions

- the invention as shown and described herein relates to processes and apparatus for cleaning semiconductor wafers in the manufacture of microprocessors, integrated circuits, and other sophisticated electronic devices .

- the invention involves the discovery of a seemingly simple and very effective cleaning system that can remove or substantially eliminate sub 0.1 micron particles during the fabrication and processing of semi-conductor wafers .

- One embodiment of the invention relates to a simple and unique cleaning apparatus comprising a special shaped receptacle designed for a single silicon wafer and having generally flat vertical walls parallel to the wafer that provide a narrow space for " er.. ic'a flow of cleaning liquid.

- the cleaning is enhanced by charging the wafer, applying a relatively low voltage insufficient to damage or degrade the delicate circuitry.

- Another embodiment of the invention relates to a process and apparatus for wet cleaning of silicon wafers wherein at least twenty wafers are supported in a wafer carrier or cassette and electrically charged by induction to provide an effective field intensity during wet processing.

- the voltage applied to the wafers is periodically reversed to remove contaminant particles from both faces of each wafer.

- the invention may seem simple in retrospect but is revolutionary in nature because it provides solutions to boundary layer problems that have mystified and plagued the semiconductor industry for decades . It involves a breakthrough in wet processing technology that should have tremendous value in the manufacture of the most advanced microchip devices.

- microcontaminants such as particles and metallic and organic impurities have an ever-increasing impact on device yields. Keeping wafer surfaces scrupulously clean throughout the wafer processing cycle is, therefore, an essential prerequisite to obtaining high yields in the fabrication of microelectronic devices .

- Every wafer-processing step is a potential source of contamination. Only wet-chemical processing, or wet cleaning, between processing steps can reduce the number of particles on the surface of silicon wafers. Wet cleaning also removes metallic and organic contaminants as well as obstructive native- oxide films, which are not really a contaminant.

- Wafer cleaning chemistry has remained essentially unchanged over the past 30 years, the most prevalent method in the industry still being hydrogen peroxide-based wet-chemical process — most notably the RCA Standard Clean, where wafers are immersed in several chemicals sequentially to remove particles, metallics, organics, and native oxides.

- RCA Standard Clean where wafers are immersed in several chemicals sequentially to remove particles, metallics, organics, and native oxides.

- the advent of smaller geometries and contamination-sensitive features forced the industry to seek new methods of wet chemical processing or more expensive alternatives .

- the RCA Standard Clean developed by Werner Kern and other RCA scientists in the late 60 's is extremely effective in removing contamination from silicon surfaces of semiconductor wafers and is today and has been the defacto industry standard for more than a quarter of a century.

- the leading industry group, SEMATECH has set forth a detailed proposal for the 0.25 Micron Process which calls for around 360 process steps including more than 50 wet cleans.

- the detailed specifications (Steps 1 to 362) are set forth on pages B-3 to B-14 of the special printed SEMATECH publication, Technology Transfer No. 95042802-ENG.

- the 360-step wafer fabrication process described above involves only four basic operations. They are (1) layering, (2) patterning, (3) doping, and (4) heat treatments. A detailed overview of the wafer-fabrication process is set forth in Chapter 5 of the 1990 Van Zant book which is incorporated herein by reference. Pages 95 to 99 describe 11 basic steps employed in the formation of an MOS metal-gate transistor structure.

- Cleaning steps 175, 212, 248, 284, and 320 of the aforesaid 362-step fabrication scheme shown on pages B-3 to B-14, described as Clean Post CMP, are critically important and pose a difficult problem.

- circuit image size also known as the line width or feature size

- line width or feature size 0.35 micron (um) to 0.25 micron or less where a particle with a minute size, such as 0.03 to 0.05 micron, create serious problems and may be considered a "killer defect”.

- CMP chemical-mechanical planarization

- the present invention relates to unique processes and apparatus for wet processing of semiconductor wafers in which the wafers are electrically charged and more particularly to a special wafer cleaning system that is effective in removing colloidal- or sub 0.1-micron size particles that cannot be removed effectively by any known prior-art process.

- the RCA-type wafer cleaning methods that have been standard in the semiconductor industry for more than a quarter of a century have been improved substantially during the last decade by use of megasonic transducer means, mechanical scrubbers or other means that helps dislodge and remove the contaminating particles .

- Strong or violent agitation has been provided by rotating brushes, sonic energy beams, laser beams, water jets and/or other suitable impact means.

- Such wet- processing techniques have made possible effective removal of contaminants with a particle size less than 0.2 micron.

- Improved megasonic cleaning means can remove particles as small as 0.15 micron.

- wet cleaning techniques of the type mentioned above with the latest improvements may not be effective in the future in removing sub 0.1-micron particles (e.g., those with a particle size below 0.07 micron).

- the present invention provides the needed breakthrough and eliminates the need for a drastic switch from the usual wet cleaning systems to a unique dry system. It involves the amazing discovery that colloidal-size particles bonded to a wafer surface containing delicate microcircuits can easily be removed and repelled when the wafer is negatively charged in a suitable manner by applying a relatively small or limited voltage, such as 2 to 60 volts or more, insufficient to damage or degrade vulnerable portions of the microcircuits or significantly reduce the yield of top-quality microchips.

- a relatively small or limited voltage such as 2 to 60 volts or more

- the process and apparatus of the present invention are designed for use in the fabrication of microelectronic devices on semiconductor wafers where delicate microcircuits are formed on the front face of the wafer by 250 to 350 steps or more including many layering, patterning and doping operations and a large number of wet processing steps.

- the preferred process of this invention is characterized in that the front face of each process wafer is provided with a suitable negative electric charge, such as 0.4 volt to 40 volts or more during wet processing and an effective field intensity, such as 0.01 volts or more per millimeter, sufficient to dislodge and remove colloidal-size or sub 0.1-micron particles.

- the invention also contemplates reversing the charge on the wafer periodically for specific applications .

- each wafer in accordance with this invention is appropriate for batch-type wet processing operations, for example, in which 20 to 40 or more silicon wafers are treated simultaneously in one wafer carrier or cassette (e.g., see Figures 13 and 14) and also for other operations where the wafers are treated one at a time .

- the invention is particularly well suited to water rinsing operations and to RCA-type wet cleaning operations including those with special modified sequences as mentioned in U.S. Patents Nos. 5,637,151 and 5,679,171, for example.

- megasonic transducer means for directing sonic pressure waves in a direction generally parallel to the face of each wafer thereby enhancing particle removal.

- a quartz glass receptacle, A can be provided with a narrow internal cavity (e.g. of a size to receive one 200 mm, 300 mm or 400 mm wafer) having flat parallel glass wall spaced a short distance from the flat wafer faces.

- An aqueous solution or Dl water would be caused to flow from the bottom to the top of the receptacle while the surface of the wafer was electrically charged.

- a desired negative charge is preferably induced by employing a positively charged metal plate, layer or coating at the flat outer surfaces of the receptacle as shown in Figures 6 and 7, for example.

- One wet cleaning operation commonly involves RCA-type wet cleans with acid and alkaline treatments and a plurality of Dl water rinses followed by IPA drying, spin drying or other final drying step.

- the silicon wafer can be electrically charged in accordance with the present invention to a predetermined limited voltage, such as 2 to 60 volts.

- a substantially higher voltage may sometimes be tolerable, but charging the face of the wafer to a voltage of 100 volts or more can be risky and is usually unnecessary or undesirable.

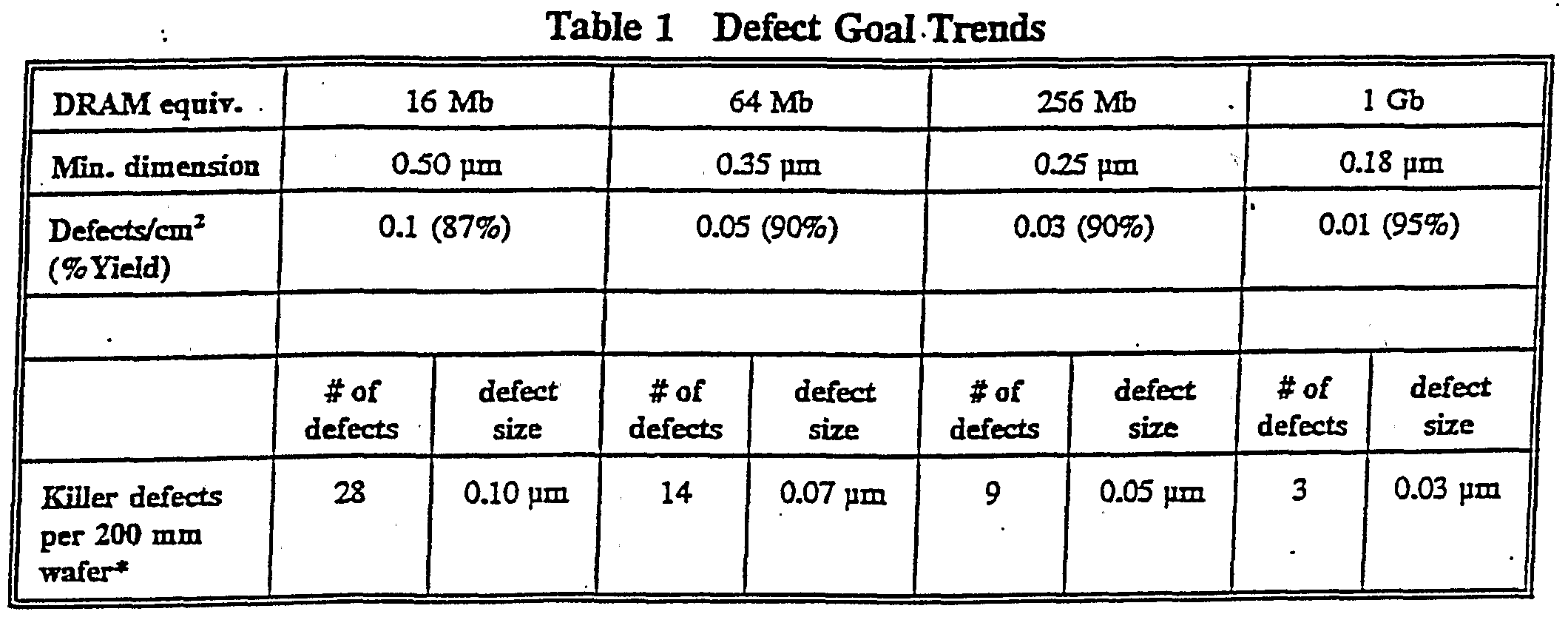

- one of the current target goals in microchip fabrication is to reduce the defect density to less than 0.03 defects per square centimeter (See Table 1).

- An object of the present invention is to reach that goal in a simple and effective manner by substantially eliminating "killer particles” and minimizing the number of troublesome particles (e.g., those with a particle size more than 10 percent of the minimum line width or feature size) which are detrimental or highly undesirable.

- killer defect is used herein in the broad sense to cover an unacceptable or intolerable defect in the microelectronic circuits of a semiconductor device or microchip caused by a contaminant particle trapped or embedded in the device during the fabrication process.

- a defect can be considered intolerable or unacceptable if it degrades the electronic circuits substantially or to such a degree that the electronic device has limited utility or is unacceptable to most customers .

- killer defect is used in a narrow sense in Table 1 on page 5 of this specification to describe trapped or embedded particles with a particle size that is at least about 20 percent of the minimum line width or feature size (identified in the table as "Mini dimension"). That table from the SEMATECH road map indicates that one of the goals is to obtain a 90-percent yield of advanced (0.25 um) wafers with no more than 0.03 killer defects per square centimeter.

- killer defect when used herein in the narrower sense, does not include colloidal-size particles with a size of 0.01 micron or less and does not cover very small microscopic particles (e.g., those with a particle size of from about 5 to about 10 percent of the minimum line width) that are detrimental or highly undesirable and could affect the quality, reliability and useful life of the device.

- Wafer Cleaning Technology when used herein in the narrower sense, does not include colloidal-size particles with a size of 0.01 micron or less and does not cover very small microscopic particles (e.g., those with a particle size of from about 5 to about 10 percent of the minimum line width) that are detrimental or highly undesirable and could affect the quality, reliability and useful life of the device.

- SC-1 solutions were based on highly concentrated mixtures of ultrapure de-ionized water (DIW), ammonium hydroxide (NH 4 OH), and hydrogen peroxide (H 2 0 2 ), in a volume ratio of 5:1:1 (5 DIW: 1 H 2 0 2 : 1 NH 4 OH).

- DIW ultrapure de-ionized water

- NH 4 OH ammonium hydroxide

- H 2 0 2 hydrogen peroxide

- wafers are immersed in these cleaning baths at 70-85 °C for 10 minutes . Higher temperatures are not recommended in order to minimize thermal decomposition of hydrogen peroxide and evaporation of ammonium hydroxide. Wafer rinsing in Dl water is usually conducted in intermediate and final steps .

- H 2 0 2 oxidizes the silicon and forms a chemical oxide; the formation of this oxide is limited by the diffusion of the oxidizing species.

- Ammonium hydroxide conversely, slowly etches this chemically grown oxide.

- Particle removal efficiency can be increased by increasing the etch rate of Si0 2 .

- the etch rate in turn, can be increased by using greater concentrations of NH 4 OH or by elevating the process temperature.

- the RCA Standard Clean developed by W. Kern and D. Puotinen in 1965 and disclosed in 1970 [1] is extremely effective at removing contamination from silicon surfaces and is the defacto industry standard [2].

- the RCA clean usually consists of two sequential steps: the Standard Clean 1 (SC-1) followed by the Standard Clean 2 (SC-2).

- SC-1 solution consisting of a mixture of ammonium-hydroxide, hydrogen- peroxide, and water, is a most efficient particle removing agent.

- Wafer rinse stages are an integral part of the chemical processes necessary in semiconductor device manufacturing. As an important stage in an integrated process, rinsing plays a central role in device yield, cost of ownership and environmental issues which continue to have increasing importance for the semiconductor industry. Because of these considerations, there are significant benefits to developing optimized rinsing processes, including better device performance, reduced water consumption, shorter cycle times, higher tool utilization and higher throughputs — all leading to lower cost of ownership.

- FEOL front end of line

- a typical sequence may include, 4 cleaning baths, 4 rinses, and a drying step. For 20 FEOL cleans this is 80 rinses. Given the number of rinses and current deionized water (DIW) use, this is 1,000 liters of DIW per wafer, just for FEOL. If one also considers back end of line (BEOL) and losses in the deionization system, over 3,700 liters of incoming water per wafer is required to meet current needs. With 5,000 wafer starts per week, this is 70 million liters of incoming water per month, just for rinsing.

- DIW current deionized water

- the thin layer of native oxide on silicon is removed by a brief immersion of the wafers in diluted (typically 1:50 or 1:100) ultrapure filtered HF solution at room temperature.

- the first step uses a mixture (SC-1) of 5:1:1 by volume of Dl water, H 2 0 2 (30%, “not stabilized"), and NH 4 0H (29 w/w% as NH 3 ) at 70°C for 5 min. followed by quench and rinse with cold ultra-filtered Dl water.

- SC-1 mixture of 5:1:1 by volume of Dl water, H 2 0 2 (30%, “not stabilized"), and NH 4 0H (29 w/w% as NH 3 ) at 70°C for 5 min. followed by quench and rinse with cold ultra-filtered Dl water.

- This deceptively simple procedure removes any remaining organics by oxidative dissolution.

- Many metal contaminants (group IB, group IIB, Au, Ag, Cu, Ni, Cd, Co, and Cr) are dissolved, complexed, and removed from the surface.

- the solution temperature should be 70°C for sufficient thermal activation, but must not exceed 80°C to avoid excessively fast decomposition of the H 2 0 2 and loss of NH 3 .

- the second step in the conventional RCA cleaning procedure uses a mixture (SC-2) consisting of 6:1:1 volume of Dl water, H 2 0 2 (30%, “not stabilized"), and HCl (37 w/w% ) .

- SC-2 removes alkali ions, NH 4 OH-insoluble hydroxides such as Al (OH) 3 , Mg (OH) 2 , and any residual trace metals (such as Cu and Au) that were not completely desorbed by SC-1.

- An optional etching step with dilute HF solution can be used between the SC-1 and SC-2 treatments of bare silicon wafers. Since the hydrous oxide film from the SC-1 treatment may entrap trace impurities, its removal before the SC-2 step should be beneficial. A 15-second immersion is 1% HF-H 2 0 (1:50) solution is sufficient to remove this film.

- Each of the chemical cleaning and rinsing operations described above using alkaline or acid solutions and pure water can be enhanced by applying to each semiconductor wafer a predetermined limited voltage, such as 2 to 60 volts or more, in accordance with the invention as described hereinafter.

- a predetermined limited voltage such as 2 to 60 volts or more

- Ultrasonics and megasonics are commonly used particle removal techniques for silicon wafer cleaning.

- sonic energy in the range of 20-40kHZ is applied to a liquid within which the wafers are immersed.

- N- is the amplitude and f the frequency of the sonic vibration.

- Particle removal in the sub 0.1 micron regime is a key requirement for advanced cleaning technologies and is essential when making modern microchips with a line width of 0.25 micron.

- megasonic cleaning technology is inadequate or ineffective in removing silica particles of such small size.

- Kern handbook confirms the inadequacy of wet cleaning technology and indicates that dry cleaning processes will have to be used in the future to obtain the ultrapurity needed for the next generation of microchips .

- wet benches are commonly used for wet cleaning operations and may employ robotic means for automatically advancing silicon wafers 25 to 40 at a time from one station to the next.

- a wet-bench set up is illustrated, for example, on page 138 of Kern's 1993 handbook.

- a typical wet bench When using RCA standard cleans (SC-1 and SC-2), a typical wet bench includes 5 or 7 recirculation immersion tanks, such as the tank shown in Patent No. 5520205, in which liquid is continuously pumped into the bottom of the tank and caused to overflow. Liquid cleaning, rinsing and drying steps in a typical wafer processing sequence (MOS gate oxidation) are shown by cross hatching in Figure 3 (Kern page 281).

- a 5-tank wet bench could, for example, start with an HF strip and Dl rinse followed by SC-1, Dl rinse, SC-2 and Dl rinse. Megasonic cleaning means would typically be used in the SC-1 bath but could also be used in the SC-2 bath and/or the rinse baths.

- a 7-tank wet bench could include a final HF bath followed by another Dl rinse.

- Dl deionized water

- the water is extremely pure with a typical resistivity of 18 mega ohms.

- the Dl water is usually dumped after use but can sometimes be cleaned and recirculated.

- a 5-tank or 7-tank wet bench of the type described above could, for example, be employed for each of the wet clean steps 2, 5, 23, 35, 37, 63, 68, 70 and 108 of the 362-step manufacturing process previously described. It will be understood that the semiconductor wafers being processed must be dried at the conclusion of each wet clean before the next dry process step.

- a spin rinse dryer or IPA dryer is commonly used for this purpose.

- the specific 362-step fabrication process of the SEMATECH publication, pages B-3 to B-14 includes the lithographic (patterning-doping) sequence of described steps 14-22 and seven other lithographic sequences 25-34, 72-81, 82-92, 110- 118, 119-128, 135-143 and 144-153 that are basically the same as the sequence 14-22, except for added inspection steps 31, 87, 124 and 149. Note also that there are slight differences at the ion implantation steps 78, 79, 89 and 90. Two other lithographic sequences 41-51 and 178-187 are quite similar but omit the implant step (20) and include added etching steps 48, 49 and 185.

- the aforesaid fabrication process also includes the previously described layering-patterning sequences 195-204 and 214-224 involving metal or oxide deposits, steps 195 and 214, and chemical-mechanical polishing, step 211. It also includes three sequences 233-242, 269-278 and 335-344 that are basically the same as the described sequence 195-204 and three sequences 247-260, 283-296 and 314-331 that are basically the same as the described sequence 211-224.

- the 362-step fabrication process includes more than 50 wet cleaning or wet processing operations that can be modified and improved in accordance with my invention as by inducing a substantial electric charge in each silicon wafer.

- These include eleven RCA-type wet cleaning operations (such as described steps 2, 5 and 23) including steps 35, 37, 63, 68, 70, 108, 129 and 154; four HF cleans, steps 65, 93, 103 and 133; five post CMP cleans, (such as described step 212) including steps 175, 248, 284 and 320; nine NMP cleans (such as described step 209) including steps 227, 245, 263, 281, 299, 317, 334 and 347; ten resist-strip with NMP (such as described steps 204 and 224) including steps 242, 260, 278, 296, 331, 344, 356 and 362 and fourteen resist-strip with H 2 S0 4 (such as described steps 13 and 22) including steps 34, 51, 62, 81, 92, 105, 118, 12

- planarization techniques are collectively known as planarization techniques.

- planarization methods do not guarantee an absolutely flat wafer surface ideally suited for subsequent lithographic operations.

- the only process that provides a global planarization of an entire wafer face is CMP, the same basic process used to flatten and polish the wafers sliced from the silicon crystal after crystal growing.

- CMP the same basic process used to flatten and polish the wafers sliced from the silicon crystal after crystal growing.

- abrasive material used for polishing i.e., silica or aluminum oxide creates a major particulate contamination problem.

- the scrubbers usually hold the wafer on a rotating vacuum chuck. While being firmly held, a rotating brush is brought in near contact with the rotating wafer while a stream of deionized water (often with a detergent) is directed onto the wafer surface. This creates a high-energy cleaning action at the wafer surface. The liquid is forced into a small space between the wafer surface and the brush ends where it achieves a high velocity, which improves the cleaning action.

- angstrom For example the terms angstrom, wafer boat, capacitor, CMP, CVD, CUM yield, Dl water, die, dopant, DRAM, feature size, integrated circuit, ion implantation, killer defect, layering, lithograph, LSI, patterning, passivation, photoresist, quartz, RTP, rinse, ULSI, VLSI, wafer and yield are defined briefly in the Glossary (pages 587 to 605) of said textbook.

- semiconductor wafer is used herein to describe a wafer of the type commonly used in the semiconductor industry.

- feature size or “line width” is used herein in the usual sense to indicate the minimum width of pattern openings or spaces in a microelectronic device or microchip.

- megasonic is used herein to describe energy waves generated from piezoelectric transducers in the 750- to 1500-kilohertz (kHz) range.

- field intensity indicates the strength of an electric field.

- An "effective field intensity” as used herein is at least about 0.01 volts per millimeter.

- charge density indicates the degree of charge or current-carrier concentration in a region (e.g., coulombs/cm 2 ) .

- electrode is used herein to describe a silicon plate or wafer or a similar metal or metal-coated plate or device that can be electrically charged and employed to induce or create an electrical charge in a process wafer in accordance with the present invention.

- a DC power source or power supply can be a direct current generator or battery or other source, such as a transformer- rectifier-filter arrangement.

- Figure 1 is a front elevational view on a reduced scale showing a unique wafer cleaning means A in the form of a flattened quartz glass receptacle 10 having a narrow internal cavity that receives a single semiconductor wafer w;

- Figure 2 is a fragmentary elevational view on a larger scale with the flat front wall 2 of the receptacle omitted and a portion of the marginal tube being shown in section, the vertical flow of liquid from the tube 5 being shown by the arrows;

- FIG. 3 is an enlarged fragmentary sectional view of the inclined tube portion 6;

- Figure 4 is an enlarged fragmentary sectional view of the marginal tube 5;

- Figure 5 is a fragmentary top view of tube portion 6;

- Figure 6 is an enlarged fragmentary sectional view taken on the line 6-6 of Figure 2;

- Figure 7 is an enlarged fragmentary sectional view similar to Figure 4 but taken on the line 7-7 of Figure 2;

- FIGS. 8 to 12 are schematic views illustrating modified forms of apparatus that could be employed in the practice of this invention.

- Figure 8 is a schematic foreshortened vertical sectional view on an enlarged scale showing a modified form of split glass receptacle (20) which may be opened for insertion or removal of the wafer;

- Figure 9 is a schematic side elevational view of the receptacle (20) on a reduced scale

- Figure 10 is an enlarged fragmentary vertical sectional view similar to Figure 8 showing a modified glass receptacle suitable for wet cleaning of flat panel displays and/or field emission displays and including electrical means for charging the panel or wafer;

- Figure 11 is a side view of the receptacle of Figure 10 similar to Figure 9;

- Figure 12 is a schematic vertical sectional view showing another modified form of wafer cleaning apparatus .

- Figure 13 is a schematic side elevational view drawn substantially to scale with parts broken away and parts in section showing a preferred embodiment of the invention wherein 25 silicon wafers are electrically charged in a tank during wet cleaning;

- Figure 14 is a schematic top view of the cleaning apparatus of Figure 13 on the same reduced scale. Description of Preferred Embodiments

- FIG. 1 to 7 One of the embodiments of the present invention is illustrated in Figures 1 to 7 and employs a flattened wafer holder and receptacle 10 designed to receive a single semiconductor wafer w.

- This embodiment and other embodiments of a similar nature using single-wafer receptacles or the like are believed well suited for modern fabrication systems, particularly those that employ silicon wafers with diameters of 200 mm or more.

- Such wet-batch cleaning apparatus e.g., of the type shown in Figures 13 and 14

- a single-wafer apparatus e.g., of the type shown in Figures 1 and 2

- Modified versions of the apparatus can, for example, include megasonic transducer means for directing sonic pressure waves in a direction generally parallel to the wafer face (e.g., see U.S. Patents No. 4,869,278; 4,998,549 and 5,037,481).

- FIGS 1 to 7 illustrate an embodiment of the present invention wherein a wafer carrier formed of glass, silicon or other suitable material has a narrow internal cavity that receives a single silicon semiconductor wafer and has means for charging the wafer to a small voltage during wet processing operations.

- a wafer carrier formed of glass, silicon or other suitable material has a narrow internal cavity that receives a single silicon semiconductor wafer and has means for charging the wafer to a small voltage during wet processing operations.

- a wafer carrier A is provided in the form of an open-top quartz glass receptacle with top surfaces 1 and a pair of identical parallel flat glass walls 2 and 3 preferably spaced apart a distance of several millimeters, usually at least twice the thickness of the silicon wafer.

- the front and rear glass walls have flat vertical surfaces at opposite sides that are welded to the flat surfaces of straight vertical side bars 4 of rectangular cross section.

- a quartz glass tube assembly 5 of semihexagonal shape is welded to the lower margins of the plates 2 and 3 which have an identical semihexagonal shape. It will be understood, of course, that the assembly 5 and the plates 2 and 3 could be semicircular, if desired, to conform more closely to the shape of the circular semiconductor wafer w.

- a modern wafer used for manufacture of advanced microchips can have a diameter of 200 to 400 millimeters.

- the glass tube assembly 5 has two oppositely inclined straight portions 6 welded to a straight horizontal portion 7.

- the flat surface 13 of tube portion 6 is welded to the flat inclined bottom surfaces of the plates 2 and 3 at opposite sides of a row of regularly spaced vertical openings 12 that direct liquid vertically in the direction of the arrows b ( Figure 3).

- the horizontal tube portion 7 has a similar flat upper surface welded to the flat horizontal bottom surfaces of plates 2 and 3 on opposite sides of a row of closely spaced vertical openings 14 as shown in Figure 4.

- the tube sections 6 and 7 can have the same cross section throughout the length of tube assembly 5 so as to provide an unobstructed passage for flow of liquid between the two side bars 4 and access to all of the multiplicity of openings 12 and 14.

- the liquid pumped into the bottom inlet openings 15 of tube portion 7 as indicated by the arrows a is directed vertically from those openings at a multiplicity of regularly or closely spaced locations as indicated by a multiplicity of vertical arrows in Figure 2.

- the water or cleaning liquid can be pressurized by the pump P, as in the embodiment of Figures

- the tube assembly 5 is designed to provide substantially uniform upward flow of liquid across the full diameter of the wafer so that laminar flow will occur and unwanted eddy currents will be minimized or substantially eliminated. This assures rapid removal of all chemicals when changing from an acid to an alkaline wash or vice versa or changing to a Dl water rinse.

- the glass receptacle A of Figures 1 and 2 is open at the top edge 1 to permit vertical movement of the wafer w into and out of the narrow internal cavity 16 defined by the flat glass walls 2 and 3 and the marginal members 4, 6 and 7 (The large top opening is unnecessary in the embodiment of Figures 8 and

- the top edge portion at 1 provides a weir for overflow of liquid and can be flat or serrated. If the liquid overflows into a tank it can be filtered and recirculated, if desired.

- Means are provided for holding and supporting a single semiconductor wafer in a vertical position midway between and parallel to the glass walls 2 and 3. if desired such means can be designed to permit or facilitate rotation of the wafer during the cleaning operation. As shown such means comprises a plurality (e.g., 3 to 5 or more) of wafer guide means 8 and 9 welded to or adhered to the marginal means 4, 6 or 7 and having grooves 11 that received and substantially fit the rounded circumferential edge portion of the wafer w.

- Such grooves can be shaped to maintain each wafer in the desired vertical position and can permit rotation of the wafer as by water pressure, sonic energy or mechanical means (e.g., see U.S. Patents Nos. 5,286,657 and 5,698,038).

- electrically- conductive plates layers or coatings are provided at or near the surface of the glass receptacle to permit charging of the wafers and thereby effect removal of submicron particles adhering to the wafer surface.

- a conductive metal coating is employed, it is preferably applied at the outer surface of the plate 2 or 3.

- a layer or coating of silicon metal could be employed at the inner surface.

- the plates 2 and 3 could be formed of silicon metal to minimize the distance from the charged plate to the wafer surface, thereby increasing the field intensity at a given voltage.

- a flat conductive metal charge plate or electrode 10 is mounted on the flat outer face of each plate 2 and 3.

- the plate is circular and has a diameter at least equal to and not substantially less than that of the wafer w, but other shapes and sizes may be appropriate or acceptable (e.g., when the wafer is rotated).

- the charge plate 10 or other charging means In order to obtain the desired uniformity it is desirable to divide the charge plate 10 or other charging means into a large number of sections so that independent computer control of the electric charge can be provided for each section. As shown the plate 10 is divided into more than 50 square sections to permit such computerized control of the charge density at each section.

- purging or cleaning of a semiconductor wafer can be carried out using wet cleaning means B of the type shown in Figures 8 and 9 comprising a flattened wafer holder and receptacle 20 formed of high-purity quartz glass having parallel flat circular wall portions 21 and 22 of uniform thickness and integral bottom and top portions 23 and 24 suitably connected to bottom inlet and top outlet pipes 44 and 45.

- a pump P is provided to cause the desired upward flow of Dl rinse water or an aqueous cleaning solution through the receptacle 20.

- the receptacle 20 can be split to form two halves 20a and 20b that fit together to form an airtight or watertight seal at the vertical split line 38.

- the receptacle may be divided into upper and lower sections with a seal at a horizontal split line.

- Suitable means may be provided to clamp or hold the two halves of the receptacle together and to maintain the desired seal.

- some type of releasable clamping or holding means 39 can be provided to hold the halves 20a and 20b together during the wet cleaning operation and perhaps during a subsequent spin drying operation.

- a series of very small glass projections or spacers 50 or other suitable holding means can be provided to locate or hold the wafer 30 or to hold it in a fixed position.

- the unique quartz glass receptacle 20 is shaped to provide a shallow flat circular cavity 25 of uniform width with very shallow portions 26 and 27 of narrow cross section and uniform width at the opposite faces 31 and 32 of the wafer.

- the receptacle can be formed in one piece or welded to join opposite halves, but this would require a narrow slot or opening at the top to permit a wafer to be lowered into and raised out of the cavity 25.

- Robotic means could be provided to lower, raise, and/or hold the wafer during wet cleaning and drying.

- the cavity 25 of the receptacle 20 is shaped to assure laminar flow of liquid over the flat front and rear surfaces 31 and 32 of the silicon wafer 30, whose circular marginal surface 33 is preferably rounded.

- the wafer may, of course, have a notch or flat portion at the margin to assure proper positioning during manufacture.

- the inlet and outlet portions 23 and 24 of the glass receptacle are provided with smooth curved surfaces 23a and 24a, respectively, shaped to assure laminar flow free of eddy currents or turbulence as the aqueous liquid flows into or out of the narrow cavity 25.

- the cavity 25 is shown as being generally circular and can have a uniform horizontal width preferably from about 2 to about 5 times the thickness (or horizontal width) of the silicon wafer 30 (e.g., a conventional 200 mm or 300 mm wafer). As shown the cavity width may be 3 or 4 times the wafer thickness so that the narrow spaces 26 and 27 between the wafer surfaces 31 and 32 and the glass surfaces 21a and 22a have a width of only a few millimeters, typically about 2 to 4 millimeters.

- the thickness of the vertical wall portions 21 and 22 is usually from about 2 to about 5 mm.

- the RCA clean system (SC-1 and SC-2, etc.) or a similar system suitable for modern wafer cleaning is preferred when carrying out the process of my invention using the single- wafer glass receptacle and also in the embodiment of Figures 13 and 14.

- the efficiency in removing submicron particles can, of course, be improved by employing megasonic energy.

- optional megasonic cleaning means can be provided with an array of piezoelectric transducers near the outer marginal portions of the wafer 30 (at 60, Figure 9). Such means is located to cause the sonic pressure waves to travel through the liquid (from location 60) in a direction parallel to the vertical wafer surface.

- Megasonic cleaning means are disclosed, for example, in Verteq Patents No. 4,869,278; 4,998,549 and 5,037,481 and 5,286,657.

- the wafer cleaning apparatus B of Figures 8 and 9 is designed to receive flat discs or wafers 30 of circular shape but could be modified as in Figure 11 for wet cleaning of rectangular discs or wafers with or without the use of megasonic energy (at 60).

- the wet cleaning process and apparatus of my invention was designed primarily for use during the manufacture of microchips from circular silicon wafers, but is also important for use during the manufacture of rectangular flat panel displays (FPDs) and field emission displays (FEDs).

- FPDs rectangular flat panel displays

- FEDs field emission displays

- the majority of FPDs are the color-active matrix liquid-crystal displays (AMLCD) most often seen as laptop computer screens.

- AMLCD color-active matrix liquid-crystal displays

- Both color and noncolor LCD displays are manufactured using microchip-fabrication technology comparable to that described herein.

- the microelectronic devices, transistors, etc. are formed on relatively large rectangular glass plates rather than on a silicon wafer.

- the typical glass plate of an FPD has a width of at least one foot (300 mm) and is a borosilicate glass.

- the glass plate e.g., plate 30'

- the glass plate is nonconductive and cannot readily be charged by induction like the silicon wafer 30 of Figure 1. For this reason it is desirable to employ apparatus of a type specially designed for cleaning the rectangular FPD plate as shown in Figure 10, for example.

- the cleaning means B' of Figures 10 and 11 is generally equivalent to the apparatus B of Figures 1 and 2 (except for the location of the glass plate 30' against or almost in contact with the flat wall portion 21' of the quartz glass receptacle 20') and is used in the same way (e.g., with the RCA clean sequences).

- the cleaning means A comprises a flattened quartz glass receptacle 20' having flat wall portions 21' and 22' of uniform thickness and integral curved bottom and top portions connected to inlet and outlet pipes 44 and 45.

- the receptacle is formed in two (non-symmetrical) halves that fit together at the vertical split line 38' to form an air-tight or liquid-tight seal throughout the periphery of the narrow cavity 25'.

- the portion 27' of that cavity between wall portion 22' and plate 30' has a horizontal width that is usually no more than 3 or 4 millimeters and may, for example, be the same as that of the cavity portion 27 of Figure 8 so as to function in the same way.

- the shape of the two-piece glass receptacle 20' differs from that of receptacle 20 at the inlet and outlet ends 28' and 29'.

- the upper and lower portions 34 and 35 of the front half (20c) of the receptacle containing wall portion 22' is preferably symmetrical with only a slight curvature.

- the upper and lower portions are also symmetrical (as in Figure 8) with a curvature (e.g., at 23') comparable to that of inlet and outlet portions 23 and 24, but the inner surface at the margin of glass plate 30' is shaped to fit the plate at its marginal edge.

- the receptacle may be made to fit the flat narrow marginal faces of the glass plate (at 33'), thereby eliminating a marginal gap.

- a marginal gap that's substantially filled with a narrow marginal strip 41 of generally triangular cross section.

- the strip extends around the entire periphery of the glass plate 30' to promote laminar flow of liquid and minimize unwanted eddy currents or the like. It can be rigid or flexible and can be formed of silicon, glass or other suitable materials.

- a small precision robot can be employed to pick up a single wafer 30 or a single FPD plate 30' and transfer it to a wet cleaning means B or B'. After the wafer or glass plate is placed in and securely located in the open half of the quartz glass receptacle 20 or 20', the receptacle is closed and held closed by clamping means or the like at 39 until the RCA or other cleaning sequence (or rinse) is completed.

- the liquid flow provided by a water pump P or in other manner by a spray technique or vapor condensation is toward the outlet end from the inlet.

- the wafer 30 for example, can be in a substantially vertical position or in an inclined or horizontal position provided the flow is toward the outlet.

- one or more receptacles 20 can be spun about a vertical or horizontal axis at any desired speed to provide a centrifugal force on the liquid at the wafer surface.

- the desired movement of the water or other liquid over the wafer surface may be obtained with or without a pump P. It will also be understood that the Dl water in the final rinse may be displaced with isopropyl alcohol prior to spin drying or other final drying operation.

- the apparatus B of Figures 8 and 9, for example, is inexpensive and well suited for laboratory research. Apparatus of this type designed for research and development work in the field of wafer cleaning happens to be convenient for use in research involving electricity.

- the glass receptacle 20, for example, can easily be provided with a silver coating or other conducive metal coating (e.g., at 47 and 48) as part of an electrical circuit.

- the simple circuit shown in Figure 10, for example, can easily be employed with the wet cleaning apparatus B or B' to apply a positive or negative charge.

- That circuit includes a battery means or DC power source D with lines 1 ' and 2 ' connected to the negative and positive terminals, respectively, and an on-off switch 3'.

- the power source D can include means to adjust and measure the voltage or emf.

- the embodiment of Figure 12 includes a thin rectangular quartz glass tank, vessel or receptacle and a plurality of permanently-mounted oxide-coated silicon wafers that serve as positive electrodes on opposite sides of each semiconductor wafer lowered into the vessel. If the vessel is designed to receive 2, 3 or 5 silicon semiconductor wafers (30), then the required number of positive silicon electrodes would, of course, be 3 , 4 and 6, respectively. It could be feasible to clean 10 or 20 semiconductor wafers at a time in a tank 5 or 10 times the size of the one shown (which is designed to receive only one such wafer). However, the system illustrated in Figures 13 and 14 would be more appropriate.

- Dl water or other liquid is pumped into the bottom of the vessel and allowed to overflow at a weir or exit to an outlet pipe (not shown).

- the system could be fully automated.

- a small precision robot would pick up a single semiconductor wafer from a 25-wafer cassette or wafer carrier and insert this one wafer into the liquid bath midway between and parallel to the two outer positive-electrode silicon wafers.

- the outer silicon-wafer electrodes of Figure 12 can be connected in a suitable manner to the positive side of a power supply. They would be carefully and gradually charged to a positive emf of say 2 to 30 volts while the semiconductor wafer being processed is charged inductively to a comparable negative emf.

- Electrodes it may be preferable to employ silicon wafers as electrodes when they are immersed in the aqueous bath as shown. All of the silicon surfaces of such electrode wafers will be completely oxidized prior to use so that substantial electrolysis will not occur in the bath. In the case where exposed conductor surfaces exist as IC components, the electrode voltages may be controlled at a low enough level to preclude destructive electrolysis.

- Figures 13 and 14 illustrate a preferred embodiment of the present invention wherein wet processing operations are carried out while a row of 20 or more aligned, parallel, regularly spaced, vertically-oriented silicon wafers w is supported on a conventional type of wafer carrier or cassette.

- a suitable type of cassette having parallel slotted vertical side walls to hold a row of rotatable wafers is shown and described in U.S. Patent No. 5,698,040 together with an overflow tank and associated equipment for circulating a cleaning liquid.

- an array W of 25 aligned vertical wafers w is supported and held in position on a wafer carrier or holder H comprising a rigid assembly 50 of quartz glass rods or bars that are integrally connected, as by welding.

- the assembly includes a bottom pair of slotted circular rods 51, an upper pair of similar slotted rods 52, a series of regularly spaced curved support arms 53 connected between the rods 51 and 52 at opposite ends of the holder H, and a pair of horizontal connecting rods or bars 54 at opposite sides of the holder adjacent to the end wafers of the array W.

- a shorter horizontal connecting rod or bar 55 extends between each pair of rods 51, and a pair of inclined rods or bars 56 are connected to the rods 52 and to a short circular lifting member 57 located near the end wafers of array W and the common horizontal axis of the 25 wafers.

- a small diameter stud portion 58 or similar means projecting outwardly from member 57 can be engaged by the lift hook of a robot to support the holder H and the wafer array W as they are raised or lowered .

- the crude wafer holder H is not conventional and is shown for convenience of illustration, it being understood that additional means, such as the slotted vertical wall means of Patent No. 5,698,040 or the slotted member 9 of Figure 2, can be employed to help locate the wafers and hold them in the desired vertical positions or allow them to rotate, if desired.

- FIG 13 portions of the row of axially aligned wafers are broken away to expose the second wafer w-2 next to the end wafer w-1, the third wafer w-3, and the adjacent fourth wafer w-4.

- the rectangular vertical side wall 62 of the overflow tank T and the thin flat circular metal sheet forming the electrode or charge plate 100 are also broken away to show the wafer carrier H.

- the conductive metal sheet can have a thickness of 1 to 3 mm or less.

- a substantially rectangular overflow vessel T formed of quartz glass or other suitable non-conductive material is provided to receive the wafer carrier and the 20 or more silicon wafers of the array W.

- the wafers may be standard 200 ⁇ mm or 300 mm wafers.

- the vessel comprises a thin-wall tank 60 in the form of a box (which could be modified, if desired, to serve as a cassette) having a flat horizontal bottom wall 61, parallel flat vertical side walls 62, and similar vertical end walls 63.

- the top edge 64 of the tank 60 is higher than the top portions of the wafers so that the array can be completely submerged in the Dl water or cleaning liquid filling the tank.

- a pair of horizontal quartz glass feed tubes 65 are welded to or attached to the end walls 63 near the bottom of the tank and are aligned with narrow horizontal slots 66 in the end walls 63 to facilitate rapid flow of liquid from the tube 65 to the interior of the tank.

- Each end wall can have a single slot 66 with a width of 1 to 2 mm and a length of about 150 to 170 mm or more or a plurality of slots with a comparable total length, such as 150 mm or more.

- water or other liquid is fed to the inlet 68 of each to be 65 by a pump P or other suitable feed means.

- the liquid fills the tank 60 and continually overflows at the top edge 64.

- Megasonic transducer means may be provided to direct sonic wave energy upwardly to assist in removal of the contaminant particles from the wafer surfaces .

- such means includes 12 transducers m fitting together side-by-side and bonded to the bottom wall 61 of the tank as shown in Figure 13.

- Each transducer m can have a width of one inch and extend parallel to the rods 51 and 52 a distance of 6 or 7 inches, preferably corresponding to the width of the wafer array W (e.g., about 150 mm).

- a flat circular electrode or charge plate 100 with a diameter about the same as or somewhat smaller than the diameter of the wafers is mounted at the outside face of each tank side wall 62 usually within 20 mm of the end wafer w.

- the plate is connected to a suitable electric power source by electric lines 101 or 102 (e.g., as in Figure 10).

- the electrode can be formed from a sheet of aluminum foil, stainless steel or silicon metal and is charged by applying a positive or negative voltage, such as 2 to 40 volts, sufficient to induce an effective charge at the outer surface of each and every wafer in the array W.

- the voltage at lines 101 and 102 is controlled and periodically reversed so that a positive charge is provided in the plate 100 at the front side of tank 60 whenever a negative charge is provided in the plate 100 at the rear side and vice versa.

- the front faces of the silicon wafers containing the microcircuits are charged by induction and will repel contaminant particles while negatively charged.

- the charge on the rear face of each wafer in the array W will be positive and may attract negatively charged particles during the time the front face of that wafer is negatively charged (i.e., by induction).

- suitable switch means can be used to reverse polarity at suitable intervals (e.g., 1 to 10 reversals per second) .

- the reversals from positive to negative should be controlled so that the front faces of the wafers with the microcircuits are negatively charged at least half and preferably most of the time (e.g., 60 to 90 percent of the time) to assure adequate particle removal.

- An important advantage of voltage reversal is the ability to clean both the front and rear faces of each wafer and to limit the number of particles deposited on the rear faces.

- the invention also contemplates charging of the wafers during cleaning by means of a conventional type of alternating current source (perhaps 20 to 30 cycles per second or more).

- the desired negative or positive electric charge can be applied to the wafer (w) during each of the necessary wet processing operations including the RCA-type wet cleans, such as steps 2, 5, 23, 129 and 154; HF cleans, such as steps 65, 93 and 133; post CMP cleans, such as steps 175, 212, 248 and 320; and resist strips with H 2 S0 4 , such as steps 13, 22, 62, 105, 143, and 187.

- the RCA-type wet cleans such as steps 2, 5, 23, 129 and 154

- HF cleans such as steps 65, 93 and 133

- post CMP cleans such as steps 175, 212, 248 and 320

- resist strips with H 2 S0 4 such as steps 13, 22, 62, 105, 143, and 187.

- the front face of the flat semiconductor wafer is negatively charged to a limited voltage, such as 2 to 60 volts, insufficient to create a substantial risk of harm or damage to any of the delicate microcircuits on that face.

- the negative charge on the wafer surface at that face is associated with a substantial charge density and an effective field intensity (preferably at least 0.01 volts/mm) sufficient to achieve or assure effective removal of contaminant colloidal-size and sub 0.05 micron particles that are bonded to or adhere to the wafer surface because of van der Waals forces and other bonding forces .

- bonds may be involved including covalent, coulombi ⁇ , ionic, electrostatic, dipole-dipole and hydrogen bonds .

- the negative charge can be obtained by use of an electric circuit that connects the silicon wafer to the negative terminal of a battery or other suitable DC power supply, it is often preferable to obtain the necessary charge by induction as by placing a positively charged conductor or electrode near the wafer as shown in the drawings. If the electrode is spaced 1 to 5 millimeters away from the wafer, an adequate field intensity (e.g., preferably at least 0.01 volts per mm) can be obtained, even with a relatively low voltage, such as 1 to 2 volts.

- the repulsive force exerted on a colloidal-size particle bonded to the wafer surface at a certain point when the surface is electrically charged at that point is directly proportional to the field intensity at that point.

- the field intensity can easily be calculated. It is directly proportional to the voltage at the electrode, inversely proportional to the dielectric constant of the liquid filling the space between the electrode and the wafer surface, and inversely proportional to the distance between the electrode and said point on the wafer surface.

- the dielectric constant commonly identified as epsilon (C) is more than 70 when the liquid is water and can be reduced to about 50 when chemicals, such as ammonium hydroxide, are added to the water (e.g., as in RCA SC-1).

- the field intensity at any point on said front face spaced 5 mm from the electrode would be 3 divided by 250 (50x5) or 0.012 volts per mm.

- Such field intensity at a point on the wafer surface containing a bonded sub 0.1-micron particle or a colloidal-size particle would be adequate and effective to dislodge and remove such a particle in the practice of the present invention.

- the voltage applied to the wafer surface is relatively low (e.g., in the range of 0.4 volt to 1.5 volts, for example), the distance from the wafer surface to the electrode may have to be less than 3 mm (e.g., in the range of 1 to 2 mm) in order to achieve the desired field intensity (e.g., adequate to assure effective removal of sub 0.1-micron or colloidal-size particles).

- the charge density at the wafer surface is preferably maintained substantially uniform and should, of course, be substantial and more than adequate to achieve effective electropurging of the wafer(s).

- Reducing the distance from the electrode to the wafer surface results in an increase in the field intensity. Such a reduction is easily accomplished in the embodiment of Figure 8. If the distance is greater than 4 mm because of the need for a glass wall near the wafer surface, it might be desirable to provide a silicon-metal layer or coating on the inner liquid-engaging face of the quartz glass wall (e.g., wall 21 or 22). In this way the distance from the positively-charged metal layer (electrode) to the wafer surface can be reduced to 1 or 2 mm. It will be understood that the spacing between the positive electrode and the wafer surface can likewise be reduced to a few millimeters in other embodiments of the invention to increase the field intensity.

- Zeta potential is important and the simplest potential of the colloid system to measure. By applying an electric field across a region of the liquid and measuring the resulting drift velocity of the colloid, the colloid mobility and potential (the zeta potential) can be determined.

- Zeta potential generally depends on the ionic concentration of the liquid in which the surface is immersed, although the exact interaction is surface and ion specific. In aqueous systems, the zeta potential varies with pH as shown, for example, in Figure 11 on Page 173 of Kern's 1993 handbook. Increasing the concentration of OH makes the zeta potential more negative, and vice vera.

- EDR electrostatic double layer repulsion

- Figure 14 on page 175 of Kern's handbook shows that colloid deposition on a hydrophilic wafer surface exhibits a dependence on pH very similar to zeta potential.

- silicon wafers and silicon particles exhibit negative zeta potentials, and EDR effectively resists the deposition of the particles on the charged wafer surface.

- negative zeta-potential particles can deposit on the negative wafers.

- it is known that such particles can deposit on the wafer from the water film that adheres to the wafer as it is withdrawn from the bath.

- hydrophobic wafers those prepared with an HF- last chemical clean, no adhering film remains during wafer withdrawal.

- each wafer with isopropyl alcohol or other suitable alcohol or nonpolar organic compound (e.g., ethyl alcohol, 1- methoxy-2-propanol or di-acetone alcohol before the wafer is dried (e.g., see U.S. Patent No. 4,911,761).

- isopropyl alcohol or other suitable alcohol or nonpolar organic compound e.g., ethyl alcohol, 1- methoxy-2-propanol or di-acetone alcohol before the wafer is dried (e.g., see U.S. Patent No. 4,911,761).

- the effectiveness of EDR as a mechanism for shielding hydrophilic wafers and retarding colloid deposition becomes marginal if that zeta potential of the colloid is about -10 millivolts (Kern page 178).

- the voltage applied to the charged wafer should be at least -10 millivolts or -0.01 volt.

- a negative voltage of only 0.05 volt could possibly be useful in the practice of the present invention.

- a megasonic transducer can be provided to supply sonic energy to assist in the electropurge cleaning of negatively charged wafers.

- the megasonic assist can also be employed when the wafer is positively charged as described above.

- the use of megasonic transducers during RCA SC-1 and SC-2 cleans is standard practice today to assist in removing sub-micron particles and is desirable but not necessary when employing the electropurge process of the present invention.

- wet cleaning operations described above using a positive or negative charge on the wafer can be carried out using a single-wafer receptacle, such as one of the general type shown in the drawings hereof, made of a suitable material, such as quartz glass or Teflon.

- the electric charge applied to the wafer surface being cleaned would be such as to provide an effective field intensity (e.g., preferably at least 0.01 volts/mm and more preferably at least 0.02 volts/mm) .

- typical RCA clean sequences include use of sulfuric acid (SPM) and hydrofluoric acid before the SC-1 and SC-2 cleans.

- Original RCA standard cleans employed substantial amounts of ammonium hydroxide and hydrochloric acid in the SC-1 and SC-2 recipes.

- a typical recipe was 29%NH 4 OH:30%H 2 O 2 :DI water (1:1:5 by volume) or 37%HC1 :30%H 2 O 2 :DI water (1:1:5). More dilute RCA-type cleaning solutions can be used.

- the electropurge wafer cleaning process of this invention is preferably carried out using conventional cleaning liquids or conventional RCA-type cleaning systems and that megasonic transducer means are desirable (e.g., particularly when cleaning the wafers with an ammoniacal hydrogen peroxide solution, such as SC-1) to set up high pressure waves in the cleaning solution.

- the transducers can be made of a suitable piezoelectric material, such as lead zirconate titanate or other commonly used material, and perform well at frequencies of 850 to 900 kHz, for example.

- Excellent results can, for example, be obtained with a process and apparatus of the type described in connection with Figures 13 and 14 using standard 5-tank or 7-tank wet benches of the type previously described herein with the standard or commonly used cleaning sequences.

- a typical 5-tank wet bench can start with an HF strip and Dl water rinse followed by SC- 1, Dl rinse, SC-2 and Dl rinse.

- a 7-tank wet bench used during the practice of this invention (e.g., to clean the 25- wafer array W) could include a final HF bath followed by another Dl rinse for a few minutes before the final drying operations .

- the tank when using a tank comparable to the tank 60 of Figures 13 and 14 and provided with electrode means, such as the flat electrodes 100, to charge the wafers, the tank could be filled with an RCA SC-1 solution with a high pH of at least about 10 or higher when using the usual 5:1 volume ratio of Dl water and ammoniom hydroxide.

- the temperature of the SC-1 solution could be in the range of 45° to 60°C and the total time in the tank could be about 8 to about 10 minutes. If the megasonic assist is omitted, a higher temperature, such as 65° to 70°C could be advantageous to limit the time to 10 minutes or less.

- the concentration of the wet cleaning solutions can be very important. It becomes important to obtain a clean and smooth or atomically flat silica wafer surface (e.g., with surface roughness values preferably under 2 Angstroms), in order to avoid excessive etching and unacceptable surface roughness, dilution of the RCA-type cleaning solutions may be desirable.

- the wet cleaning or wet etching solutions should be diluted with substantial amounts of Dl water.

- a solution of 49%HF:98%H 2 S0 4 :H 2 0 (1:0.5:30) has been found suitable for wet chemical etching of the sacrificial Si0 2 layer.

- a dilute solution can be used, such as NH 4 OH:H 2 0 2 :H 2 0 (1:8:64).

- the dilute or ultra- dilute RCA clean can employ a 100:1 or 1000:1 dilution of 37%HC1 in water at 45 °C, for example.

- Metal removal efficiency of this solution is very high with or without the assistance of megasonic energy, particularly when the dilute solution is employed in the electropurge process of this invention (e.g., with a wafer charge of 2 to 60 volts and a field intensity of at least 0.02 volts/mm) .

- electropurge cleaning with limited wafer charges can be effective with the dilute RCA and ultra-dilute RCA (SC- 1 and SC-2) cleans with or without the assistance of megasonic energy.

- the electric charge applied to the silicon wafers in the practice of this invention should be limited and may be relatively small (e.g., from 1 to 60 volts). Excessive voltage should be avoided to minimize the risk of harm or damage to the delicate or sensitive microcircuits. A voltage of 100 volts or more is usually unnecessary or disadvantageous and might be imprudent for the more highly advanced microchips because of the potential detrimental, degrading or undermining affects on the more vulnerable or sensitive portions of the delicate microcircuits .

- the surface should be charged with an effective negative voltage (e.g., preferably at least about one volt) to provide an effective field intensity (e.g., preferably at least about 0.01 volts/mm) at said surface.

- an effective negative voltage e.g., preferably at least about one volt

- an effective field intensity e.g., preferably at least about 0.01 volts/mm

- Such field intensity can be at least 0.02 volts/mm and sufficient to cause or permit effective removal of sub 0.1- micron particles but insufficient to create a substantial risk of adverse affects or harm to the more vulnerable portions of the microcircuits .

- low voltages in the range of 2 to 60 volts is prudent and often preferred, particularly during BEOL wet processing where there are more problems and difficulties and the risk of harm or loss due to excessive voltage is much greater.

- Such low voltages provide a higher degree of safety and can be remarkably effective in dislodging, removing and repelling sub 0.05-micron and colloidal-size contaminant particles which cause "killer defects" in advanced microchips, such as those having feature sizes of from 0.10 to 0.15 micron .

- the present invention is a godsend to the semiconductor industry, which heretofore had no practical and effective way to eliminate "killer” particles of sub 0.1-micron size or to reach target defect-density goals, such as those set forth in TABLE 1 on page 5 hereof.

- That table describes the SEMATECH yield model and equipment defect goals based on the model for pilot line and high-volume manufacturing. The table is taken from a printed SEMATECH publication dated July 31, 1994 and entitled “Contamination-Free Manufacturing Handbook" (Identified as 94062428A-TR) . That publication provides information that covers most, if not all, aspects of contamination control methodology for semiconductor equipment and processes.

- SIA Roadmap estimates process-specific defect densities for future 0.25-micron (um) to 0.05-micron devices (up to the year 2012) and proposes defect targets for future generations of devices based on 60% yield for initial production.

- One major advantage exemplified by the wafer cleaning systems described previously in connection with Figures 1 to 7 and Figure 8, is the unique ability to clean both the front and back faces of each silicon wafer simultaneously (e.g., when the wafer is located between two positive electrodes to induce a negative charge in both faces ) .

- that major advantage can also be achieved (e.g., when treating 10 to 20 or more silicon wafers at one time as in Figure 14) by providing a suitable positively-charged metal electrode plate or disk between each adjacent pair of wafers.

- a suitable positively-charged metal electrode plate or disk between each adjacent pair of wafers.

- 12 of those disks could be silicon wafers with microcircuits being formed on the front faces and the other 13 could be positively-charged electrodes formed of a suitable conductive metal, such as stainless steel, aluminum or silicon (i.e., a bare unpatterned silicon wafer functioning as the positive electrode).

- the electrical apparatus used to charge the positive electrodes to the desired voltage in the embodiments just described can, of course, include a conventional DC power source with suitable switch means or the like to provide for reversals of polarity, if desired.

- An AC power source can be used instead to provide periodic voltage reversals (e.g., 10 to 30 or more cycles per second).

- the AC voltage curve or wave profile can, for example, be controlled in such manner that a positive voltage is provided during 80 to 90 percent of each cycle and a negative voltage is provided during the other 10 to 20 percent.

- Such a special AC electrical system could be particularly advantageous in the specific embodiment of Figures .13 and 14 (where the front and back faces are oppositely charged) to reduce or minimize the redeposit of particles on the wafer faces during the brief time that they are positively charged, thereby reducing the need for megasonic assistance.

- the 12 transducers at the bottom wall could then be omitted, if desired.

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Materials Engineering (AREA)

- Metallurgy (AREA)

- Organic Chemistry (AREA)

- Physics & Mathematics (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- General Chemical & Material Sciences (AREA)

- Mechanical Engineering (AREA)

- Electrochemistry (AREA)

- Cleaning Or Drying Semiconductors (AREA)

Abstract

Description

Claims

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| AU2001232914A AU2001232914A1 (en) | 2000-01-22 | 2001-01-19 | Process and apparatus for cleaning silicon wafers |

| EP01904990A EP1250712A2 (en) | 2000-01-22 | 2001-01-19 | Process and apparatus for cleaning silicon wafers |

| JP2001553573A JP2003522406A (en) | 2000-01-22 | 2001-01-19 | Method and apparatus for cleaning silicon wafer |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US49016200A | 2000-01-22 | 2000-01-22 | |

| US09/490,162 | 2000-01-22 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| WO2001054181A2 true WO2001054181A2 (en) | 2001-07-26 |

| WO2001054181A3 WO2001054181A3 (en) | 2002-01-03 |

Family

ID=23946860

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| PCT/US2001/002119 WO2001054181A2 (en) | 2000-01-22 | 2001-01-19 | Process and apparatus for cleaning silicon wafers |

Country Status (4)

| Country | Link |

|---|---|

| EP (1) | EP1250712A2 (en) |

| JP (1) | JP2003522406A (en) |

| AU (1) | AU2001232914A1 (en) |

| WO (1) | WO2001054181A2 (en) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN109158373A (en) * | 2018-11-09 | 2019-01-08 | 江苏德润光电科技有限公司 | A kind of polysilicon chip Intelligent cleaning device |

| CN111063609A (en) * | 2019-12-18 | 2020-04-24 | 武汉百臻半导体科技有限公司 | Semiconductor chip cleaning method |

| WO2023226643A1 (en) * | 2022-05-26 | 2023-11-30 | 高景太阳能股份有限公司 | Real-time automatic control silicon wafer production method and system, medium, and device |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100672754B1 (en) * | 2004-05-10 | 2007-01-22 | 주식회사 하이닉스반도체 | Method for making semiconductor device having trench isolation |

| JP2006319282A (en) * | 2005-05-16 | 2006-11-24 | Fuji Electric Device Technology Co Ltd | Manufacturing method of semiconductor device |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0567939A2 (en) * | 1992-04-29 | 1993-11-03 | Texas Instruments Incorporated | Method of removing small particles from a surface |

| US5887607A (en) * | 1997-07-07 | 1999-03-30 | Micron Technology, Inc. | Wafer processing apparatus |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01255226A (en) * | 1988-04-04 | 1989-10-12 | Matsushita Electric Ind Co Ltd | Substrate cleaning apparatus |

| JPH0382029A (en) * | 1989-08-24 | 1991-04-08 | Nec Corp | Wet type treatment equipment |

| JP2920165B2 (en) * | 1991-11-29 | 1999-07-19 | エス・イー・エス株式会社 | Overflow tank for single wafer cleaning |

| JP3036990B2 (en) * | 1992-08-28 | 2000-04-24 | 広島日本電気株式会社 | Semiconductor substrate cleaning equipment |

| JPH09120952A (en) * | 1995-10-25 | 1997-05-06 | Sony Corp | Surface treatment method for wafer |

| JP2834097B2 (en) * | 1996-09-03 | 1998-12-09 | 山口日本電気株式会社 | Reticle cleaning equipment |

| JPH11288908A (en) * | 1998-04-02 | 1999-10-19 | Komatsu Ltd | Method and device for cleaning semiconductor wafer and wafer cassette |

-

2001

- 2001-01-19 JP JP2001553573A patent/JP2003522406A/en not_active Withdrawn

- 2001-01-19 EP EP01904990A patent/EP1250712A2/en not_active Withdrawn

- 2001-01-19 AU AU2001232914A patent/AU2001232914A1/en not_active Abandoned

- 2001-01-19 WO PCT/US2001/002119 patent/WO2001054181A2/en not_active Application Discontinuation

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0567939A2 (en) * | 1992-04-29 | 1993-11-03 | Texas Instruments Incorporated | Method of removing small particles from a surface |

| US5887607A (en) * | 1997-07-07 | 1999-03-30 | Micron Technology, Inc. | Wafer processing apparatus |

Non-Patent Citations (7)

| Title |

|---|

| PATENT ABSTRACTS OF JAPAN vol. 014, no. 009 (E-870), 10 January 1990 (1990-01-10) -& JP 01 255226 A (MATSUSHITA ELECTRIC IND CO LTD), 12 October 1989 (1989-10-12) * |

| PATENT ABSTRACTS OF JAPAN vol. 015, no. 254 (E-1083), 27 June 1991 (1991-06-27) -& JP 03 082029 A (NEC CORP), 8 April 1991 (1991-04-08) * |

| PATENT ABSTRACTS OF JAPAN vol. 017, no. 538 (E-1440), 28 September 1993 (1993-09-28) -& JP 05 152273 A (SUGAI:KK), 18 June 1993 (1993-06-18) * |

| PATENT ABSTRACTS OF JAPAN vol. 018, no. 336 (E-1568), 24 June 1994 (1994-06-24) -& JP 06 084874 A (HIROSHIMA NIPPON DENKI KK), 25 March 1994 (1994-03-25) * |

| PATENT ABSTRACTS OF JAPAN vol. 1997, no. 09, 30 September 1997 (1997-09-30) -& JP 09 120952 A (SONY CORP), 6 May 1997 (1997-05-06) * |

| PATENT ABSTRACTS OF JAPAN vol. 1998, no. 08, 30 June 1998 (1998-06-30) & JP 10 078649 A (NEC YAMAGUCHI LTD), 24 March 1998 (1998-03-24) * |

| PATENT ABSTRACTS OF JAPAN vol. 2000, no. 01, 31 January 2000 (2000-01-31) -& JP 11 288908 A (KOMATSU LTD), 19 October 1999 (1999-10-19) * |

Cited By (4)