KR100978568B1 - Manufacturing method of nitride semiconductor light emitting device - Google Patents

Manufacturing method of nitride semiconductor light emitting device Download PDFInfo

- Publication number

- KR100978568B1 KR100978568B1 KR1020080040732A KR20080040732A KR100978568B1 KR 100978568 B1 KR100978568 B1 KR 100978568B1 KR 1020080040732 A KR1020080040732 A KR 1020080040732A KR 20080040732 A KR20080040732 A KR 20080040732A KR 100978568 B1 KR100978568 B1 KR 100978568B1

- Authority

- KR

- South Korea

- Prior art keywords

- nitride semiconductor

- semiconductor layer

- sacrificial layer

- layer pattern

- base substrate

- Prior art date

Links

Images

Landscapes

- Led Devices (AREA)

Abstract

질화물 반도체 발광소자의 제조 방법이 개시된다. 본 질화물 반도체 발광소자의 제조 방법은, 베이스 기판 상에 희생층 패턴을 형성하는 단계, 희생층 패턴 및 희생층 패턴을 통해 노출된 베이스 기판 상에 제1 질화물 반도체층을 형성하는 단계, 희생층 패턴과 동일한 패턴을 갖도록 제1 질화물 반도체층을 식각하는 단계, 제1 질화물 반도체층을 수평 성장시키는 단계, 제1 질화물 반도체층 상에 활성층 및 제2 질화물 반도체층을 형성하는 단계, 및 희생층 패턴을 식각하여 베이스 기판을 제1 질화물 반도체층으로부터 분리시키는 단계를 포함한다. A method of manufacturing a nitride semiconductor light emitting device is disclosed. The method of manufacturing the nitride semiconductor light emitting device may include forming a sacrificial layer pattern on a base substrate, forming a first nitride semiconductor layer on the exposed base substrate through the sacrificial layer pattern and the sacrificial layer pattern, and the sacrificial layer pattern. Etching the first nitride semiconductor layer so as to have the same pattern as, forming the first nitride semiconductor layer horizontally, forming the active layer and the second nitride semiconductor layer on the first nitride semiconductor layer, and sacrificial layer pattern. Etching to separate the base substrate from the first nitride semiconductor layer.

발광소자, 희생층, 식각 Light emitting element, sacrificial layer, etching

Description

본 발명은 질화물 반도체 발광소자의 제조 방법에 관한 것으로, 보다 상세하게는, 베이스 기판의 제거가 용이한 질화물 반도체 발광소자의 제조 방법에 관한 것이다. The present invention relates to a method for manufacturing a nitride semiconductor light emitting device, and more particularly, to a method for manufacturing a nitride semiconductor light emitting device that is easy to remove the base substrate.

일반적으로 질화물계 반도체 발광소자는 사파이어 기판에 성장하지만, 이러한 사파이어 기판은 단단하고 전기적으로 부도체이며 열전도 특성이 좋지 않아 질화물계 반도체 발광소자의 크기를 줄여 제조원가를 절감하거나, 광출력 및 칩의 특성을 개선시키는데 한계가 있다. 특히, 발광소자의 고출력화를 위해서는 대전류 인가가 필수이기 때문에 발광소자의 열 방출 문제를 해결하는 것이 중요하다. 이러한 문제를 해결하기 위한 수단으로, 종래에는 레이저 리프트 오프(Laser Lift-Off: 이하, 'LLO' 라 칭함)를 이용하여 사파이어 기판을 제거한 수직구조 질화물 반도체 발광소자가 제안되었다.In general, nitride-based semiconductor light emitting devices are grown on a sapphire substrate, but these sapphire substrates are hard, electrically nonconductive, and have poor thermal conductivity, thereby reducing the size of the nitride-based semiconductor light emitting devices, thereby reducing manufacturing costs, or reducing light output and chip characteristics. There is a limit to improvement. In particular, it is important to solve the heat dissipation problem of the light emitting device because a large current is required for high output of the light emitting device. As a means for solving this problem, a vertical nitride semiconductor light emitting device in which a sapphire substrate is removed using a laser lift-off (hereinafter referred to as LLO) has been conventionally proposed.

도 1a 내지 도 1c는 종래 질화물 반도체 발광소자의 제조 방법을 도시한 도 면이다. 우선, 도 1a에 도시된 바와 같이, 사파이어 기판(11) 상에 제1 질화물 반도체층(12), 활성층(13), 제2 질화물 반도체층(14) 및 p형 전극(16)을 순차적으로 형성한다. 1A to 1C are diagrams illustrating a manufacturing method of a conventional nitride semiconductor light emitting device. First, as shown in FIG. 1A, the first

이 후, 도 1b에서와 같이, 사파이어 기판(11) 상에 레이저빔을 조사하여 사파이어 기판(11)과 제1 질화물 반도체층(12) 사이에 국부적인 열을 발생시킴으로써, 사파이어 기판(11)과 제1 질화물 반도체층(12)의 경계 영역의 질화물 반도체 물질을 분해하는 방법을 이용하여 제1 질화물 반도체층(12)으로부터 사파이어 기판(11)을 분리시킨다. 그리고, 도 1c에서와 같이, 제1 질화물 반도체층(12)의 일면에 n형 전극(15)을 형성하여 수직구조의 질화물 반도체 발광소자를 제조할 수 있다. 이 경우, 사파이어 기판(11)을 분리하기 위해 이용되는 레이저 빔 조사시, 레이저 빔의 높은 열로 인해 제1 질화물 반도체층(12)이 손상되거나, 심각한 경우에는 제1 질화물 반도체층(12)이 깨져버리게 된다. 이에 따라, 제품 수율이 저하되며, 질화물 반도체 발광소자의 구동시 누설 전류가 발생한다는 문제점이 있었다. Thereafter, as shown in FIG. 1B, by irradiating a laser beam on the

본 발명은 상술한 문제점을 해결하기 위한 것으로, 본 발명의 목적은, 베이스 기판과 제1 질화물 반도체층 사이에 희생층 패턴을 형성한 후, 희생층 패턴을 식각함으로써 제1 질화물 반도체층으로부터 베이스 기판을 용이하게 분리시킬 수 있는 질화물 반도체 발광소자의 제조 방법에 관한 것이다. SUMMARY OF THE INVENTION The present invention has been made to solve the above problems, and an object of the present invention is to form a sacrificial layer pattern between the base substrate and the first nitride semiconductor layer, and then, by etching the sacrificial layer pattern, the base substrate from the first nitride semiconductor layer. The present invention relates to a method for manufacturing a nitride semiconductor light emitting device which can be easily separated.

이상과 같은 목적을 달성하기 위한 본 발명의 일 실시예에 따른 질화물 반도체 발광소자의 제조 방법은, 베이스 기판 상에 희생층 패턴을 형성하는 단계, 상기 희생층 패턴 및 상기 희생층 패턴을 통해 노출된 베이스 기판 상에 제1 질화물 반도체층을 형성하는 단계, 상기 희생층 패턴과 동일한 패턴을 갖도록 제1 질화물 반도체층을 식각하는 단계, 상기 제1 질화물 반도체층을 수평 성장시키는 단계, 상기 제1 질화물 반도체층 상에 활성층 및 제2 질화물 반도체층을 형성하는 단계, 및 상기 희생층 패턴을 식각하여 상기 베이스 기판을 제1 질화물 반도체층으로부터 분리시키는 단계를 포함한다. In the method of manufacturing a nitride semiconductor light emitting device according to an embodiment of the present invention for achieving the above object, forming a sacrificial layer pattern on a base substrate, the sacrificial layer pattern and the sacrificial layer pattern exposed through Forming a first nitride semiconductor layer on the base substrate, etching the first nitride semiconductor layer to have the same pattern as the sacrificial layer pattern, horizontally growing the first nitride semiconductor layer, and forming the first nitride semiconductor Forming an active layer and a second nitride semiconductor layer on the layer, and etching the sacrificial layer pattern to separate the base substrate from the first nitride semiconductor layer.

이 경우, 상기 제1 질화물 반도체층은 상기 희생층 패턴의 상면 및 양 측면을 감싸도록 형성될 수 있다. In this case, the first nitride semiconductor layer may be formed to surround the top surface and both side surfaces of the sacrificial layer pattern.

본 제조 방법은, 상기 희생층 패턴을 식각하기 전에, 상기 희생층 패턴이 노출되도록 상기 베이스 기판, 희생층 패턴, 제1 질화물 반도체층, 활성층, 제2 질화물 반도체층 및 제2전극을 절단하는 단계를 포함한다. The manufacturing method may include cutting the base substrate, the sacrificial layer pattern, the first nitride semiconductor layer, the active layer, the second nitride semiconductor layer, and the second electrode to expose the sacrificial layer pattern before etching the sacrificial layer pattern. It includes.

그리고, 상기 베이스 기판과 상기 수평 성장된 제1 질화물 반도체층 사이에 위치하는 상기 희생층 패턴은 공극을 포함할 수 있다. The sacrificial layer pattern positioned between the base substrate and the horizontally grown first nitride semiconductor layer may include a void.

또한, 상기 제1 질화물 반도체층을 식각하는 단계 후에, 상기 희생층 패턴을 통해 노출된 상기 베이스 기판 상에 희생 물질을 증착시키는 단계를 더 포함할 수도 있다. 이 경우, 상기 희생층 패턴은 실리콘 산화막 또는 실리콘 질화막으로 이루어질 수 있다. The method may further include depositing a sacrificial material on the base substrate exposed through the sacrificial layer pattern after etching the first nitride semiconductor layer. In this case, the sacrificial layer pattern may be formed of a silicon oxide film or a silicon nitride film.

상기 희생층 패턴은 50㎚ 내지 20㎛ 범위의 두께로 형성될 수 있다. The sacrificial layer pattern may be formed to a thickness in the range of 50nm to 20㎛.

본 제조 방법은, 상기 베이스 기판이 제1 질화물 반도체층으로부터 분리되면, 상기 제1 질화물 반도체층의 일면에 제1 전극을 형성하는 단계를 더 포함할 수 있다. The manufacturing method may further include forming a first electrode on one surface of the first nitride semiconductor layer when the base substrate is separated from the first nitride semiconductor layer.

또한, 상기 제2 질화물 반도체층이 형성되면, 상기 제2 질화물 반도체층 상에 제2 전극을 형성하는 단계, 상기 제2 전극 상에 접착층을 형성하는 단계, 및 상기 접착층 상에 지지 구조물을 형성하는 단계를 더 포함할 수도 있다. 이 경우, 상기 지지 구조물은 도전성 기판일 수 있다. 또한, 상기 접착층은 금(Au), 니켈(Ni), 구리(Cu), 주석(Sn), 텅스텐(W) 및 은(Ag) 중 적어도 하나 이상의 물질로 이루어질 수 있다. 그리고, 상기 베이스 기판은, 사파이어 기판, Si 기판, SiC 기판 및 ZnO 기판 및 GaAs 기판 중 어느 하나인 것일 수 있다. In addition, when the second nitride semiconductor layer is formed, forming a second electrode on the second nitride semiconductor layer, forming an adhesive layer on the second electrode, and forming a support structure on the adhesive layer It may further comprise a step. In this case, the support structure may be a conductive substrate. In addition, the adhesive layer may be made of at least one material of gold (Au), nickel (Ni), copper (Cu), tin (Sn), tungsten (W), and silver (Ag). The base substrate may be any one of a sapphire substrate, a Si substrate, a SiC substrate, a ZnO substrate, and a GaAs substrate.

한편, 상기 희생층 패턴은 불산 용액 또는 BOE(Buffered Oxide Etchant) 용액을 이용하여 선택적으로 습식 식각될 수 있다. The sacrificial layer pattern may be selectively wet etched using a hydrofluoric acid solution or a buffered oxide etchant (BOE) solution.

본 발명에 따르면, 베이스 기판과 제1 질화물 반도체층 사이에 희생층 패턴을 형성하여 반도체 구조물을 형성하고 난 후, 희생층 패턴을 식각함으로써, 제1 질화물 반도체층으로부터 베이스 기판을 용이하게 분리시킬 수 있게 된다. 이에 따라, 사파이어 기판, Si 기판, GaAs 기판, SiC 기판 또는 ZnO 기판 등과 같은 베이스 기판의 제거시, 레이저 리프트 오프 방법을 이용하지 않아 제1 질화물 반도체층의 손상률이 감소되어 제품 수율이 향상되며, 질화물 반도체 발광소자의 구동시 누설 전류가 발생을 감소시킬 수 있게 된다. According to the present invention, after forming a sacrificial layer pattern between the base substrate and the first nitride semiconductor layer to form a semiconductor structure, by etching the sacrificial layer pattern, it is possible to easily separate the base substrate from the first nitride semiconductor layer Will be. Accordingly, when removing a base substrate such as a sapphire substrate, a Si substrate, a GaAs substrate, a SiC substrate, or a ZnO substrate, the damage rate of the first nitride semiconductor layer is reduced by not using a laser lift-off method, thereby improving product yield. When the nitride semiconductor light emitting device is driven, leakage current can be reduced.

이하에서는 첨부된 도면을 참조하여 본 발명을 보다 자세하게 설명한다. Hereinafter, with reference to the accompanying drawings will be described in detail the present invention.

도 2a 내지 도 2g는 본 발명의 일 실시예에 따른 질화물 반도체 발광소자의 제조 방법을 설명하기 위한 도면이다. 도 2a를 참조하면, 우선, 베이스 기판(110) 상에 희생층 패턴(120)을 형성한다. 이 경우, 베이스 기판(110)은 질화물 반도체 발광소자를 구성하는 반도체 구조물을 성장시키기 위한 성장 기판으로, 사파이어 기판, Si 기판 및 GaAs 기판, SiC 기판 및 ZnO 기판 중 어느 하나가 이용될 수 있다. 2A to 2G are views for explaining a method of manufacturing a nitride semiconductor light emitting device according to an embodiment of the present invention. Referring to FIG. 2A, first, a

또한, 희생층 패턴(120)은 베이스 기판(110) 상에 희생 물질을 증착시킨 후, 일정 패턴으로 선택적 식각함으로써 형성할 수 있다. 이 경우, 희생층 패턴(120)은 선택적 습식 식각에 의해 제거될 수 있는 것으로, 이 후, 베이스 기판(110)과 반도 체 구조물을 분리시키기 위한 역할을 한다. 이를 구현하기 위해서, 희생층 패턴(120)은 베이스 기판(110) 상에서, 최외측면이 외부로 노출되도록 형성되어야 하며, 약 50㎚ 내지 20㎛ 범위 내의 두께로 형성되어야 한다. 또한, 희생층 패턴(120)은 습식 식각이 가능하며, 반도체 구조물 형성을 위한 질화물 박막의 성장 분위기에서 안정적인 희생 물질이 이용될 수 있다. 이를 만족하는 희생 물질로는, 실리콘 산화막 또는 실리콘 질화막 등이 있을 수 있다. In addition, the

이 후, 도 2b에 도시된 바와 같이, 베이스 기판(110)과 희생층 패턴(120) 상에 제1 질화물 반도체층(130)을 성장시킨다. 구체적으로, 희생층 패턴(120)과 희생층 패턴(120)을 통해 노출되어 있는 베이스 기판(110) 상에 질화물 반도체 물질을 유기화학금속증착법(MOCVD)을 이용하여 성장시킴으로써, 제1 질화물 반도체층(130)을 형성할 수 있게 된다. Thereafter, as shown in FIG. 2B, the first

한편, 도면을 통해 도시하고 있지는 않으나, 베이스 기판(110) 상에 질화물 반도체 기저층(미도시)을 형성하고 난 후, 부분 식각하여 일정 패턴을 형성할 수도 있다. 그리고 난 후, 식각된 부분 상에 희생층 패턴(120)을 형성하고, 질화물 반도체 기저층을 측면 성장시켜 희생층 패턴(120) 상에 제1 질화물 반도체층(130)을 형성할 수도 있다. 이 같은 방법을 이용하는 경우에는, 제1 질화물 반도체층(130)의 성장이 보다 용이할 수 있다. Although not illustrated through the drawings, a nitride semiconductor base layer (not shown) may be formed on the

다음, 도 2c에 도시된 바와 같이, 제1 질화물 반도체층(130)을 희생층 패 턴(120)과 동일한 패턴(점선으로 표시된 부분)으로 식각함으로써, 희생층 패턴(120)의 측면 및 베이스 기판(110)의 일부면이 노출되도록 한다. 그리고, 도 2d에서와 같이, 희생층 패턴(120)과 동일한 패턴을 갖는 제1 질화물 반도체층(130)을 수평 성장시킴으로써, 측면이 연결되도록 한다. 이에 따라, 제1 질화물 반도체층(130)은 희생층 패턴(120) 상에서 하나의 연결된 층 형태를 갖게 된다. 이 경우, 베이스 기판(110)과 수평 성장된 제1 질화물 반도체층(130) 사이에 위치하는 희생층 패턴(120)은 패턴 사이의 공간에 의해 공극(G)을 포함할 수 있게 된다. Next, as shown in FIG. 2C, the first

한편, 도 2e 도시된 바와 같이, 제1 질화물 반도체층(130) 상에 활성층(140), 제2 질화물 반도체층(150), 제2 전극(160), 접착층(170) 및 지지 구조물(180)을 순차적으로 형성한다. 구체적으로, 활성층(140)은 InGaN/GaN MQW(다중양자우물구조)이며, 제2 질화물 반도체층(150)은 p형 질화물 반도체층으로, p-GaN층이 될 수 있다. 그리고, 제2 질화물 반도체층(150) 상에 형성되는 제2 전극(160)은 p형 전극이 될 수 있다. 2E, the

또한, 지지 구조물(180)은 제1 질화물 반도체층(130), 활성층(140) 및 제2 질화물 반도체층(150)으로 구성되는 반도체 구조물을 지지하기 위한 것으로, 제2 전극(160)과의 전기적 연결을 위해 도전성 기판이 이용될 수 있다. 이 경우, 제2 전극(160)과 지지 구조물(180)은 접착층(170)에 의해 접착되어 있는 것으로, 금(Au), 니켈(Ni), 구리(Cu), 주석(Sn), 텅스텐(W) 및 은(Ag) 중 적어도 하나 이상의 금속 물질이 이용될 수 있다. In addition, the

이 후, 도 2f에서와 같이, 습식 식각을 이용하여 희생층 패턴(120)만을 선택적으로 식각함으로써, 제1 질화물 반도체층(130)으로부터 베이스 기판(110)을 분리할 수 있게 된다. 구체적으로, 희생층 패턴(120)은 불산 용액이나, BOE(Buffered Oxide Etchant) 용액을 이용하여 제거될 수 있다. 이 경우, 희생층 패턴(120)에 포함된 공극(G)에 의해 희생층 패턴(120)의 식각 공정에 소요되는 시간이 단축될 수 있게 된다. 이 같이, 식각 용액을 이용한 화학적 방법으로 희생층 패턴(120)을 식각함으로써, 반도체 구조물, 특히, 제1 질화물 반도체층(130)에 기계적인 힘이나 열이 공급되지 않게 된다. 이에 따라, 베이스 기판(110) 분리시, 제1 질화물 반도체층(130)의 손상을 방지할 수 있게 되며, 베이스 기판(110)의 분리가 용이해진다. Thereafter, as shown in FIG. 2F, by selectively etching only the

다음, 도 2g에 도시된 바와 같이, 희생층 패턴(120)이 제거됨에 따라 베이스 기판(110)이 분리되면서, 제1 질화물 반도체층(130)의 일면이 노출된다. 제1 질화물 반도체층(130)의 일면 상에 제1 전극(190), 즉, n형 전극을 형성함으로써 질화물 반도체 발광소자(100)를 제조할 수 있게 된다.Next, as shown in FIG. 2G, as the

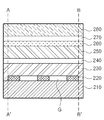

도 3a 내지 도 3h는 본 발명의 다른 실시예에 따른 질화물 반도체 발광소자의 제조 방법을 설명하기 위한 도면이다. 도 3a를 참조하면, 우선, 베이스 기판(210) 상에 희생층 패턴(220)을 형성한다. 구체적으로, 사파이어 기판, Si 기판 및 GaAs 기판, SiC 기판 및 ZnO 기판 중 어느 하나의 기판을 베이스 기판(210)으로 하여, 베이스 기판(210) 상에 희생 물질을 증착시킨다. 그리고, 희생 물질을 일정 패턴으로 선택적 식각함으로써, 희생층 패턴(220)을 형성할 수 있게 된다. 이 경우, 희생층 패턴(220)으로는, 실리콘 산화막 또는 실리콘 질화막 등의 희생 물질이 이용될 수 있다. 3A to 3H are views for explaining a method of manufacturing a nitride semiconductor light emitting device according to another embodiment of the present invention. Referring to FIG. 3A, first, a

이 후, 도 3b에 도시된 바와 같이, 베이스 기판(210)과 희생층 패턴(220) 상에 제1 질화물 반도체층(230)을 성장시킨다. 구체적으로, 희생층 패턴(220)을 통해 노출되어 있는 베이스 기판(210) 상에 질화물 반도체 물질을 유기화학금속증착법(MOCVD)을 이용하여 성장시킴으로써, 제1 질화물 반도체층(230)을 형성할 수 있게 된다. 이 경우, 제1 질화물 반도체층(230)은 희생층 패턴(220)의 상면 및 측면을 모두 둘러싸는 형태로 형성된다. 이에 따라, 희생층 패턴(220)은 제1 질화물 반도체층(230)에 의해 밀봉된다.Thereafter, as shown in FIG. 3B, the first

다음, 도 3c에 도시된 바와 같이, 제1 질화물 반도체층(230)을 희생층 패턴(220)과 동일한 패턴(점선으로 표시된 부분)으로 식각함으로써, 제1 질화물 반도체층(230)을 통해 희생층 패턴(220)의 측면 및 베이스 기판(210) 일부면이 노출되도록 한다. 이 경우, 희생층 패턴(220)을 구성하는 각 패턴 중 양단에 위치한 패턴의, 최외곽 부분의 제1 질화물 반도체층(230)은 식각하지 않고 남겨둔다. Next, as shown in FIG. 3C, the first

그리고, 도 3d에서와 같이, 희생층 패턴(220)과 동일한 패턴을 갖는 제1 질화물 반도체층(230)을 수평 성장시킴으로써, 측면이 연결되도록 한다. 이에 따라, 제1 질화물 반도체층(230)은 희생층 패턴(220) 상에서 하나의 연결된 층 형태를 갖게 된다. 이 경우, 베이스 기판(210)과 수평 성장된 제1 질화물 반도체층(230) 사이에 위치하는 희생층 패턴(220)은 패턴 사이의 공간에 의해 공극(G)을 포함할 수 있게 된다. As shown in FIG. 3D, the first

한편, 도 3e에 도시된 바와 같이, 제1 질화물 반도체층(230) 상에 활성층(240), 제2 질화물 반도체층(250), 제2 전극(260), 접착층(270) 및 지지 구조물(280)을 순차적으로 형성한다. 구체적으로, 활성층(240)은 InGaN/GaN MQW(다중양자우물구조)이며, 제2 질화물 반도체층(250)은 p형 질화물 반도체층으로, p-GaN층이 될 수 있다. 또한, 제2 질화물 반도체층(250) 상에 형성되는 제2 전극(260)은 p형 전극이 될 수 있다. Meanwhile, as shown in FIG. 3E, the

그리고, 희생층 패턴(220)이 외부로 노출될 수 있도록 구조물(베이스 기판 상에 희생층 패턴, 제1 질화물 반도체층, 활성층, 제2 질화물 반도체층, 제2 전극, 접착층 및 지지 구조물이 차례로 형성된 구조물)을 A-A' 및 'B-B' 절단선을 따라 절단한다. 이 경우, 절단선은 희생층 패턴(220)이 외부로 노출될 수 있도록, 상기 구조물 중 희생층 패턴(220)이 존재하는 영역 내에서 결정될 수 있으며, 바람직하게는, 희생층 패턴(220)의 최외측면을 기준으로 결정될 수도 있다. 이 같은 공정을 수행함으로써, 희생층 패턴(220) 형성시, 형성 위치를 고려할 필요가 없게 된다. 즉, 희생층 패턴(220)의 최외측면을 베이스 기판(210)의 양측면과 일직선상에 위치하도록 형성할 필요가 없게 된다. Then, the

이 후, 도 3f에서와 같이, 구조물의 절단에 의해 희생층 패턴(220)이 노출되면, 도 3g에서와 같이, 희생층 패턴(220)만을 선택적으로 습식 식각하여 제1 질화물 반도체층(230)으로부터 베이스 기판(210)을 분리한다. 구체적으로, 희생층 패턴(220)은 불산 용액이나, BOE(Buffered Oxide Etchant) 용액을 이용하여 제거될 수 있다. 이 경우, 희생층 패턴(220)에 포함된 공극(G)에 의해 희생층 패턴(220)의 식각 공정에 소요되는 시간을 단축할 수 있게 된다. 이 같이, 식각 용액을 이용한 화학적 방법으로 희생층 패턴(220)을 식각함으로써, 베이스 기판(210)의 분리가 용이해진다. 3F, when the

다음, 도 3h에 도시된 바와 같이, 희생층 패턴(220)이 제거됨에 따라 베이스 기판(210)이 분리되면서, 제1 질화물 반도체층(230)의 일면이 노출된다. 제1 질화물 반도체층(230)의 일면 상에 제1 전극(290), 즉, n형 전극을 형성함으로써 질화물 반도체 발광소자(200)를 제조할 수 있게 된다.Next, as shown in FIG. 3H, as the

도 4a 내지 도 4h는 본 발명의 또 다른 실시예에 따른 질화물 반도체 발광소자의 제조 방법을 설명하기 위한 도면이다. 도 4a를 참조하면, 우선, 베이스 기판(310) 상에 희생층 패턴(320)을 형성한다. 이 후, 도 4b에 도시된 바와 같이, 베이스 기판(310)과 희생층 패턴(320) 상에 제1 질화물 반도체층(230)을 성장시킨다. 4A to 4H are views for explaining a method of manufacturing a nitride semiconductor light emitting device according to another embodiment of the present invention. Referring to FIG. 4A, first, a

다음, 도 4c에 도시된 바와 같이, 제1 질화물 반도체층(330)을 희생층 패턴(320)과 동일한 패턴(점선으로 표시된 부분)으로 식각함으로써, 제1 질화물 반도체층(330)을 통해 희생층 패턴(320)의 측면 및 베이스 기판(310) 일부면이 노출되도록 한다. 그리고, 도 4d에서와 같이, 희생층 패턴(320)을 통해 노출된 베이스 기판(310) 상에 희생 물질을 증착시킴으로써, 희생층 패턴(320)을 하나의 연결된 층 형태로 형성한다. 이에 따라, 제1 질화물 반도체층(330)이 식각된 부분을 통해 희생층 패턴(320)이 노출되는 형태를 갖는다. Next, as shown in FIG. 4C, the first

그리고, 도 4e에 도시된 바와 같이, 층 형태를 갖는 희생층 패턴(320) 상에 제1 질화물 반도체층(330)을 수평 성장시킴으로써, 측면이 연결되도록 한다. 이에 따라, 제1 질화물 반도체층(330)은 희생층 패턴(320) 상에 하나의 연결된 층 형태를 갖게 된다. 즉, 베이스 기판(310) 상에 희생층 패턴(320) 및 제1 질화물 반도체층(330)이 차례로 적층된 구조를 갖는다. As shown in FIG. 4E, the first

한편, 도 4f에 도시된 바와 같이, 제1 질화물 반도체층(330) 상에 활성층(340), 제2 질화물 반도체층(350), 제2 전극(360), 접착층(370) 및 지지 구조물(380)을 순차적으로 형성한다. Meanwhile, as shown in FIG. 4F, the

이 후, 도 4g에 도시된 바와 같이, 희생층 패턴(320)만을 선택적으로 습식 식각함으로써, 제1 질화물 반도체층(330)으로부터 베이스 기판(310)을 분리할 수 있게 된다. 구체적으로, 희생층 패턴(320)은 불산 용액이나, BOE(Buffered Oxide Etchant) 용액을 이용하여 제거될 수 있다. 이 경우, 식각 용액을 이용한 화학적 방법으로 희생층 패턴(320)을 식각함으로써, 베이스 기판(310)을 분리하는 과정에서 반도체 구조물, 특히, 제1 질화물 반도체층(330)에 기계적인 힘이나 열이 공급되지 않게 된다. 이에 따라, 베이스 기판(310) 분리시, 제1 질화물 반도체층(330)의 손상을 방지할 수 있게 되며, 베이스 기판(310)의 분리가 용이해진다. Thereafter, as shown in FIG. 4G, by selectively wet etching only the

다음, 도 4g에서와 같이, 희생층 패턴(320)이 제거됨에 따라 베이스 기판(310)이 분리되면서, 제1 질화물 반도체층(330)의 일면이 노출된다. 제1 질화물 반도체층(330)의 일면 상에 제1 전극(390), 즉, n형 전극을 형성함으로써 질화물 반도체 발광소자(300)를 제조할 수 있게 된다. Next, as shown in FIG. 4G, as the

이상에서는 본 발명의 바람직한 실시 예에 대하여 도시하고 설명하였지만, 본 발명은 상술한 적정의 실시 예에 한정되지 아니하며, 청구범위에서 청구하는 본 발명의 요지를 벗어남이 없이 당해 발명이 속하는 기술분야에서 통상의 지식을 가진 자에 의해 다양한 변형실시가 가능한 것은 물론이고, 이러한 변형실시들은 본 발명의 기술적 사상이나 전망으로부터 개별적으로 이해되어서는 안 될 것이다.While the above has been shown and described with respect to preferred embodiments of the present invention, the present invention is not limited to the above-described appropriate embodiments, it is usually in the art without departing from the gist of the invention claimed in the claims. Various modifications can be made by those skilled in the art, and these modifications should not be individually understood from the technical spirit or the prospect of the present invention.

도 1a 내지 도 1c는 종래 질화물 반도체 발광소자의 제조 방법을 설명하기 위한 도면, 1A to 1C are views for explaining a method of manufacturing a conventional nitride semiconductor light emitting device;

도 2a 내지 도 2e는 본 발명의 일 실시예에 따른 질화물 반도체 발광소자의 제조 방법을 설명하기 위한 도면, 2A to 2E are views for explaining a method of manufacturing a nitride semiconductor light emitting device according to an embodiment of the present invention;

도 3a 내지 도 3g는 본 발명의 다른 실시예에 따른 질화물 반도체 발광소자의 제조 방법을 설명하기 위한 도면, 그리고, 3A to 3G are views for explaining a method of manufacturing a nitride semiconductor light emitting device according to another embodiment of the present invention, and

도 4a 내지 도 4h는 본 발명의 또 다른 실시예에 따른 질화물 반도체 발광소자의 제조 방법을 설명하기 위한 도면이다. 4A to 4H are views for explaining a method of manufacturing a nitride semiconductor light emitting device according to another embodiment of the present invention.

* 도면의 주요 부분에 대한 부호 설명 * Explanation of symbols on the main parts of the drawings

110, 210, 310 : 베이스 기판 120, 220, 320 : 희생층110, 210, 310:

130, 230, 330 : 제1 질화물 반도체층 130, 230, and 330: first nitride semiconductor layer

Claims (13)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020080040732A KR100978568B1 (en) | 2008-04-30 | 2008-04-30 | Manufacturing method of nitride semiconductor light emitting device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020080040732A KR100978568B1 (en) | 2008-04-30 | 2008-04-30 | Manufacturing method of nitride semiconductor light emitting device |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20090114870A KR20090114870A (en) | 2009-11-04 |

| KR100978568B1 true KR100978568B1 (en) | 2010-08-27 |

Family

ID=41556065

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020080040732A KR100978568B1 (en) | 2008-04-30 | 2008-04-30 | Manufacturing method of nitride semiconductor light emitting device |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR100978568B1 (en) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101399460B1 (en) | 2012-10-23 | 2014-05-28 | 한국기계연구원 | Method for manufacturing substrate embedded nanopattern of different materials |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101039970B1 (en) | 2010-02-11 | 2011-06-09 | 엘지이노텍 주식회사 | Method for forming a semiconductor layer and fabricating light emitting device |

| TWI408732B (en) | 2010-12-23 | 2013-09-11 | Nat Univ Chung Hsing | The epitaxial structure with easy removal of the sacrificial layer and its manufacturing method |

| KR20150012538A (en) * | 2013-07-25 | 2015-02-04 | 서울바이오시스 주식회사 | Method of fabricating light emitting device |

| CN114730813A (en) * | 2019-12-13 | 2022-07-08 | 苏州晶湛半导体有限公司 | Method for manufacturing semiconductor structure |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002241198A (en) | 2001-02-13 | 2002-08-28 | Hitachi Cable Ltd | GaN SINGLE CRYSTAL SUBSTRATE AND METHOD FOR PRODUCING THE SAME |

| KR100553366B1 (en) | 2004-05-14 | 2006-02-20 | 엘지전자 주식회사 | Method for manufacturing semiconductor device of Nitride chemical |

| KR100638869B1 (en) | 2005-06-21 | 2006-10-27 | 삼성전기주식회사 | Method of fabricating nitride type compound layer, gan substrate and vertical structure nitride type semiconductor light emitting device |

| KR100797180B1 (en) | 2005-06-25 | 2008-01-23 | (주)에피플러스 | Semiconductor light Emitting device having improved luminance and method thereof |

-

2008

- 2008-04-30 KR KR1020080040732A patent/KR100978568B1/en not_active IP Right Cessation

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002241198A (en) | 2001-02-13 | 2002-08-28 | Hitachi Cable Ltd | GaN SINGLE CRYSTAL SUBSTRATE AND METHOD FOR PRODUCING THE SAME |

| KR100553366B1 (en) | 2004-05-14 | 2006-02-20 | 엘지전자 주식회사 | Method for manufacturing semiconductor device of Nitride chemical |

| KR100638869B1 (en) | 2005-06-21 | 2006-10-27 | 삼성전기주식회사 | Method of fabricating nitride type compound layer, gan substrate and vertical structure nitride type semiconductor light emitting device |

| KR100797180B1 (en) | 2005-06-25 | 2008-01-23 | (주)에피플러스 | Semiconductor light Emitting device having improved luminance and method thereof |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101399460B1 (en) | 2012-10-23 | 2014-05-28 | 한국기계연구원 | Method for manufacturing substrate embedded nanopattern of different materials |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20090114870A (en) | 2009-11-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100714589B1 (en) | Method for Manufacturing Vertical Structure Light Emitting Diode | |

| KR100691363B1 (en) | Method for manufacturing vertical structure light emitting diode | |

| KR100735496B1 (en) | Method for forming the vertically structured gan type light emitting diode device | |

| CN102341924B (en) | Use the method for compliance integrated structure bonding semiconductor device | |

| TWI559573B (en) | Light emitting diode | |

| EP2262012A2 (en) | Light-emitting element and a production method therefor | |

| CN104025319A (en) | Semiconductor device and method of fabricating the same | |

| US20140145204A1 (en) | Light-emitting diode and method for preparing the same | |

| KR20100068839A (en) | Fabricating method of light emitting element | |

| TW201036210A (en) | Quasi-vertical light emitting diode | |

| JP5774712B2 (en) | Semiconductor device and manufacturing method thereof | |

| JP5658604B2 (en) | Manufacturing method of semiconductor light emitting device | |

| KR100978568B1 (en) | Manufacturing method of nitride semiconductor light emitting device | |

| JP5077224B2 (en) | Group III nitride semiconductor light emitting device and method for manufacturing the same | |

| KR20150012538A (en) | Method of fabricating light emitting device | |

| KR20070044099A (en) | Nitride-based light emitting diode and manufacturing method of the same | |

| KR101072200B1 (en) | Light emitting device and method for fabricating the same | |

| KR20150074516A (en) | Method of separating substrate and method of fabricating light emitting device using the same | |

| KR101111748B1 (en) | Method of manufacturing vertical structure nitride-gallium-based semiconductor light emitting device | |

| JP5934720B2 (en) | Group III nitride semiconductor device and manufacturing method thereof | |

| KR101316121B1 (en) | Method of fabricating vertical light emitting diode | |

| JP2010056457A (en) | Method of manufacturing light emitting element array | |

| KR20140123318A (en) | Method for separating growth substrate using stress and method for fabricating semiconductor device using the same | |

| KR20140074040A (en) | Light emitting diode and method for fabricating the same | |

| KR102649711B1 (en) | Method for manufacturing ultra-thin type semiconductor die |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| N231 | Notification of change of applicant | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20130731 Year of fee payment: 4 |

|

| LAPS | Lapse due to unpaid annual fee |