KR100783647B1 - A method for skew compensation and an apparatus using the method - Google Patents

A method for skew compensation and an apparatus using the method Download PDFInfo

- Publication number

- KR100783647B1 KR100783647B1 KR1020060029602A KR20060029602A KR100783647B1 KR 100783647 B1 KR100783647 B1 KR 100783647B1 KR 1020060029602 A KR1020060029602 A KR 1020060029602A KR 20060029602 A KR20060029602 A KR 20060029602A KR 100783647 B1 KR100783647 B1 KR 100783647B1

- Authority

- KR

- South Korea

- Prior art keywords

- test

- skew

- memory

- center position

- sample memory

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/56—External testing equipment for static stores, e.g. automatic test equipment [ATE]; Interfaces therefor

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/56—External testing equipment for static stores, e.g. automatic test equipment [ATE]; Interfaces therefor

- G11C2029/5602—Interface to device under test

Landscapes

- Tests Of Electronic Circuits (AREA)

Abstract

반도체 메모리 테스트 장비의 스큐 보정 방법 및 스큐 보정 기능을 갖는 반도체 메모리 테스트 장비가 개시되어 있다. 상기 방법은 샘플 메모리의 스큐를 획득하는 단계; 샘플 메모리를 테스트 장비에 실장하여 각 핀들의 테스트 유효 구간 및 센터 포지션의 위치를 검색하는 단계; 상기 각 핀들의 유효 구간내의 센터 포지션이 되는 시점을 획득하는 단계; 상기 유효 구간내의 센터 포지션이 되는 시점에 대해 상기 샘플 메모리의 스큐값을 적용하여 보정하는 단계; 및 상기 유효 구간내의 센터 포지션이 되는 시점에 대해 상기 샘플 메모리의 스큐값을 적용하여 보정되는 값에 대해 테스트 장비의 저장부에 저장하는 단계를 통해 달성된다.Disclosed are a skew correction method and a semiconductor memory test device having a skew correction function. The method includes obtaining a skew of a sample memory; Mounting the sample memory to the test equipment to retrieve the test valid interval and the position of the center position of each pin; Acquiring a time point at which a center position within an effective period of each of the pins is obtained; Correcting by applying a skew value of the sample memory to a time point at which the center position within the valid period is reached; And storing a value to be corrected by applying a skew value of the sample memory to a time point at which the center position is within the valid period, and storing the corrected value in the storage unit of the test equipment.

따라서, 메모리 테스트 시스템은 대량의 메모리를 동시에 테스트함에 있어 중요한 안정성 및 신뢰성을 확보하기 위해 보정시 외부의 측정 장비를 사용하지 않고, 샘플 메모리 디바이스 자체를 이용하여 자동으로 보정할 수 있도록 하여 신뢰성 및 안정성 그리고 정밀성을 증가시킨다. 또한 보정시 발생하는 외부장비의 의존성이 없어 개발 시간 단축 및 개발 비용의 상당 부분을 절감할 수 있도록 한다.Therefore, the memory test system can automatically calibrate using the sample memory device itself without using external measuring equipment when calibrating to ensure important stability and reliability in testing a large amount of memory at the same time. And increase precision. In addition, there is no dependence on external equipment generated during calibration, which reduces the development time and significantly reduces the development cost.

Description

도 1은 오실로스코프를 활용한 테스터 보정 시스템에 관한 종래기술 도면,1 is a prior art diagram of a tester correction system utilizing an oscilloscope,

도 2는 단락보드를 활용한 테스터 보정 시스템에 관한 종래기술 도면,2 is a prior art diagram of a tester correction system using a short board;

도 3은 본 발명에 따른 테스터 보정 시스템에 관한 도면,3 is a diagram of a tester correction system according to the present invention;

도 4는 도 3의 TPG 보드에 관한 상세도면,4 is a detailed view of the TPG board of FIG.

도 5는 본 발명을 구현하기 위한 테스터 보정 시스템의 설치 형상을 보여주는 도면,5 is a view showing the installation shape of the tester correction system for implementing the present invention,

도 6은 본 발명의 바람직한 실시예에 따른 테스트 보정 방법에 관한 도면,6 is a diagram of a test correction method according to a preferred embodiment of the present invention;

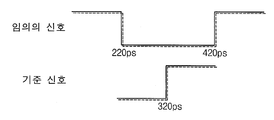

도 7a는 샘플 메모리 스큐 측정에 관한 도면,7A is a diagram of a sample memory skew measurement,

도 7b는 TPG 보드의 유효 구간 측정에 관한 도면,7b is a diagram regarding a valid section measurement of a TPG board;

도 7c는 샘플 메모리의 스큐값을 적용한 실제 신호 처리에 관한 도면,7C is a diagram of actual signal processing applying a skew value of a sample memory;

본 발명은 메모리 테스트 장비에 관한 것으로, 좀더 상세하게는 반도체 메모리 테스트 장비의 스큐 보정 방법 및 스큐 보정 기능을 갖는 반도체 메모리 테스트 장비에 관한 것이다.The present invention relates to a memory test equipment, and more particularly to a semiconductor memory test equipment having a skew correction method and a skew correction function of the semiconductor memory test equipment.

테스트 중인 디바이스(DUT)를 성공적으로 테스트하기 위해, 각각의 전송라인을 따라 디바이스 핀에 인가된 신호는 서로에 대해 정확한 타이밍에 도착해야한다. 테스터 신호를 DUT에 전송하는 전송라인은 전형적으로 길이가 다양하고, 이것은 서로에 대해 각각 지연시간도 다양하다는 것을 의미한다.To successfully test the device under test (DUT), the signals applied to the device pins along each transmission line must arrive at the correct timing for each other. Transmission lines that transmit tester signals to the DUT typically vary in length, which means that the delay times vary with respect to each other.

따라서 신호 타이밍을 정확하게 제어하기 위하여, 각각의 채널에 대한 지연 정도가 측정되어야 하고, 타이밍 교정 공정 전에 지연을 고려한 보정이 선행되어야 한다.Therefore, in order to accurately control the signal timing, the delay degree for each channel must be measured, and the correction considering the delay must be preceded before the timing correction process.

이러한 메모리 테스트 시스템은 컴퓨터와 여러 테스트 기기의 조합으로 이루어지며, 테스트 프로그램의 명령어 집합을 실행함으로써 테스트 하드웨어를 제어한다.Such a memory test system is a combination of a computer and various test devices, and controls test hardware by executing an instruction set of a test program.

메모리 테스트 시스템은 정확하고 안정적으로 신뢰성있는 테스트 결과를 측정하기 위하여 주기적으로 테스트에 필요한 각종 파라미터를 테스트 전에 필수적으로 보정하게 된다.The memory test system periodically corrects various parameters necessary for the test before the test in order to measure the test results accurately and reliably and reliably.

보정 작업은 메모리 테스트에서 중요한 요소로서, 일반적으로 외부의 전용 파라미터 보정 장비를 구축하여 각 파라미터의 신호를 입력받아 각 신호의 유효한 구간을 결정하여 보정하는 방식을 사용한다.Correction work is an important element in memory test. In general, an external dedicated parameter correction device is built and a signal of each parameter is input to determine a valid section of each signal.

이러한 시스템의 경우 외부의 보정 장비 구축에 많은 비용이 소요되며, 보정 시 시간도 오래 걸리는 단점이 있다. 또한 시스템의 정확성 및 안정성을 확보받기 위해 일정 주기적으로 한번씩 반드시 보정 과정을 수행하여야 한다. 주기적으로 보정작업을 거쳐야 한다는 것은 테스트 시간이 오래 걸린다는 것을 의미한다.Such a system is expensive to build external calibration equipment, and takes a long time to calibrate. In addition, the calibration process must be performed at regular intervals to ensure the accuracy and stability of the system. Being calibrated periodically means that the test takes a long time.

주기적으로 보정 작업을 수행해야 하는 테스트 시스템에서 메모리 장치의 테스트 생산성은 매우 낮을 수 밖에 없다.In test systems that require periodic calibrations, the test device's test productivity is very low.

종래의 테스트 장비 보정 시스템에 관하여 도면을 참조하여 설명하기로 한다.A conventional test equipment calibration system will be described with reference to the drawings.

도 1은 오실로스코프를 활용한 테스터 보정 시스템에 관한 종래기술 도면이다. 도 1을 참조하면, 가장 끝단에서 신호를 측정할 수 있도록 별도의 보드(3)를 소켓 위에 올려놓은 상태에서 테스터(2)에서 발생된 신호를 GPIB(General purpose interface bus)와 같은 범용 인터페이스를 이용하여 오실로스코프(1)로 연결한다.1 is a prior art diagram of a tester correction system utilizing an oscilloscope. Referring to FIG. 1, a signal generated by the

그리고 테스터(2)에서 발생된 신호를 오실로스코프(1)를 이용해서 측정후 스큐를 조정할 수 있는데, 피시험 메모리(Device Under Test, 이하 'DUT'라 칭함) 또는 특정 핀을 기준 삼아 전체 핀에 대한 보정을 수행하게 된다. 이 방식은 측정하고자 하는 대상에 대해 모두 다 적용할 수 있으므로 정밀도가 우수하다. 반면 각 핀 별로 순차적으로 진행해야 하므로 시간이 오래 걸리고, 이를 위한 인력 낭비도 심하다.After measuring the signal generated by the tester (2) using the oscilloscope (1), the skew can be adjusted.The device under test (hereinafter referred to as 'DUT') or a specific pin is used as a reference for the entire pin. Calibration will be performed. This method is highly accurate because it can be applied to any object to be measured. On the other hand, since each pin must proceed sequentially, it takes a long time and wastes manpower for this.

도 2는 단락보드를 활용한 테스터 보정 시스템에 관한 종래기술 도면이다. 도 2를 참조하면, 소켓보드(12) 위에 전원 핀을 제외한 모든 신호가 단락된 단락 보드(11)를 올려놓고 모든 드라이버를 통해서 동일한 신호를 보내서 중첩된 신호를 기준신호로 잡고, 이 신호를 기초로 다른 신호들과 비교하여 비교 차이만큼 스큐를 조정한다.2 is a prior art diagram of a tester correction system utilizing a short board. Referring to FIG. 2, a

상기 방식은 모든 피시험 메모리 장치에 대해서 보정이 가능하기 때문에 시간이 단축되는 효과가 있다. 그러나, 단락 보드 제작시 PCB(Printed Circuit Board) 패턴 길이나 임피던스가 맞지 않을 경우 정밀도가 떨어지는 단점이 있다.This method has an effect of shortening the time since all the memory devices under test can be calibrated. However, when the short circuit board is manufactured, if the printed circuit board (PCB) pattern length or impedance does not match, there is a disadvantage that the precision is lowered.

현재까지 개발된 테스트 시스템은 외부의 보정 장비를 별도로 구축하여야 하고, 보정 장비가 있다 하더라도 정밀도가 우수하면 시간이 오래 걸리거나, 시간이 단축되면 정밀도가 떨어지는 문제점이 혼재되어 있어, 이에 대한 보정 장치 개선이 요청되고 있다.The test system developed to date has to build external calibration equipment separately, and even if there is a calibration equipment, there is a problem that it takes a long time if the precision is excellent, or that the precision falls if the time is shortened. Is being requested.

본 발명은 이러한 문제점을 해결하기 위한 것으로, 테스트 장비의 보정 장비를 구비하지 않고도 테스트 장비의 스큐를 보정할 수 있는 반도체 메모리 테스트 장비의 스큐 보정 방법 및 스큐 보정 기능을 갖는 반도체 메모리 테스트 장비를 제공하는데 목적이 있다.The present invention is to solve this problem, to provide a skew correction method and a semiconductor memory test equipment having a skew correction function of the semiconductor memory test equipment that can correct the skew of the test equipment without having the calibration equipment of the test equipment There is a purpose.

또한, 샘플 메모리의 각 핀에 해당하는 스큐값을 테스트 장비에 저장해둠으로써, 테스트 대상을 모두 테스트 할 때마다 보정 작업을 수행할 필요가 없는 테스트 장비를 제공하는데 또 다른 목적이 있다.In addition, by storing the skew value corresponding to each pin of the sample memory in the test equipment, another object of the test equipment is to provide a test equipment that does not need to be calibrated for every test object.

이러한 목적을 달성하기 위한 본 발명에 따른 반도체 메모리 테스트 장비의 스큐 보정 방법은 샘플 메모리의 스큐를 획득하는 단계; 샘플 메모리를 테스트 장비에 실장하여 각 핀들의 테스트 유효 구간 및 센터 포지션의 위치를 검색하는 단계; 상기 각 핀들의 유효 구간내의 센터 포지션이 되는 시점을 획득하는 단계; 상기 유효 구간내의 센터 포지션이 되는 시점에 대해 상기 샘플 메모리의 스큐값을 적용하여 보정하는 단계; 및 상기 유효 구간내의 센터 포지션이 되는 시점에 대해 상기 샘플 메모리의 스큐값을 적용하여 보정되는 값에 대해 테스트 장비의 저장부에 저장하는 단계를 포함한다.Skew correction method of the semiconductor memory test equipment according to the present invention for achieving this object comprises the steps of obtaining a skew of the sample memory; Mounting the sample memory to the test equipment to retrieve the test valid interval and the position of the center position of each pin; Acquiring a time point at which a center position within an effective period of each of the pins is obtained; Correcting by applying a skew value of the sample memory to a time point at which the center position within the valid period is reached; And storing a value corrected by applying a skew value of the sample memory to a time point at which the center position is within the valid interval, in the storage unit of the test equipment.

상기 방법은 테스트하고자 하는 핀 별로 각각 반복 수행함을 특징으로 한다.The method is characterized in that the repetition is performed for each pin to be tested.

상기 샘플 메모리의 스큐를 획득하는 단계는 샘플 메모리를 실장하기 전에 각 채널 별로 반복 실험하여 스큐값을 얻는 것을 특징으로 한다.The step of acquiring the skew of the sample memory may be performed by repeatedly experimenting with each channel before mounting the sample memory to obtain a skew value.

상기 샘플 메모리를 실장하여 각 핀들의 테스트 유효 구간 검색 및 센터 포지션의 위치를 검색하는 단계는 유효 구간 내에 센터 포지션이 위치하는 시점이 발견될 때 까지 테스트하는 채널에 대해서 소정의 간격으로 딜레이하여 검색하는 것을 특징으로 한다.The test memory section search and the position of the center position of each pin by mounting the sample memory may be performed by delaying the test channel at a predetermined interval until the time point at which the center position is located within the valid section is found. It is characterized by.

상기 유효 구간내의 센터 포지션이 되는 시점에 대해 상기 샘플 메모리의 스큐값을 적용하여 보정하는 단계에서, 유효구간 및 센터 포지션에 대한 시점에 대해 스큐값만큼 감산하여 시점을 보정하는 것을 특징으로 한다.In the step of correcting by applying a skew value of the sample memory to the time point at which the center position within the effective period, the viewpoint is corrected by subtracting the skew value from the time point for the effective section and the center position.

또한 상기의 목적을 달성하기 위한 본 발명에 따른 스큐 보정 기능을 갖는 반도체 메모리 테스트 장비는 메모리 장치를 테스트하기 위한 전기적/물리적 신호 를 처리하는 테스트 보드; 상기 테스트 보드에 샘플 메모리를 실장하여 샘플 메모리의 각 핀들에 대한 유효 구간내의 센터 포지션이 되는 시점을 획득하고, 샘플 메모리의 스큐값 만큼 보정한 값을 저장부에 저장하여, 피시험 메모리마다 저장부에 저장된 스큐값을 적용하여 테스트하는 TPG(Timing Pattern Generator) 보드; 및 상기 TPG 보드로 샘플 메모리의 스큐값을 전달하고, 상기 TPG 보드에서 테스트되는 각 채널에 대한 정상/불량 여부를 수신하며, 테스트에 필요한 프로그램을 제공하는 컴퓨터를 포함한다.In addition, the semiconductor memory test equipment having a skew correction function according to the present invention for achieving the above object includes a test board for processing an electrical / physical signal for testing a memory device; A sample memory is mounted on the test board to obtain a time point at which the center position is within an effective period of each pin of the sample memory, and a value corrected by the skew value of the sample memory is stored in a storage unit, and stored for each memory to be tested. Timing Pattern Generator (TPG) board for testing by applying a skew value stored in the; And a computer that transmits a skew value of a sample memory to the TPG board, receives a normal / bad status for each channel tested in the TPG board, and provides a program for testing.

상기 샘플 메모리는 메모리 특성에 따라 발생하는 스큐값을 획득하기 위해 테스트 전에 측정 과정이 미리 수행된 메모리인 특징이 있다.The sample memory is characterized in that the measurement process is performed in advance before the test to obtain a skew value generated according to the memory characteristics.

상기 테스트 보드는 다수개의 메모리를 실장하기 위한 DUT(Device Under test) 보드를 적어도 하나 이상 구비한다.The test board includes at least one device under test (DUT) board for mounting a plurality of memories.

상기 TPG 보드는 테스트 패턴 신호를 발생시키는 패턴 발생부; 신호의 시퀀스를 제어하는 시퀀셜 제어부; 샘플 메모리의 각 채널에 대한 스큐 값을 저장하는 저장부; 상기 저장부에 저장된 각 채널별 스큐값만큼 보정하여 각 채널의 신호를 처리하도록 제어신호를 출력하는 제어부; 및 각 채널별로 인가되는 신호에 대한 온/오프를 전달하는 릴레이부들을 포함하며, 상기 릴레이부들은 각각 신호의 전달 및 검출을 수행하기 위한 드라이버 및 비교기를 구비하는 것을 특징으로 한다.The TPG board comprises a pattern generator for generating a test pattern signal; A sequential controller for controlling a sequence of signals; A storage unit for storing a skew value for each channel of the sample memory; A control unit outputting a control signal to process a signal of each channel by correcting the skew value for each channel stored in the storage unit; And relay unit for transmitting the on / off for the signal applied for each channel, each relay unit is characterized in that it comprises a driver and a comparator for performing the signal transmission and detection, respectively.

이하, 첨부한 도면들을 참조하여, 본 발명의 바람직한 실시예를 보다 상세하게 설명하고자 한다. 실시예의 설명에 있어서, 이해의 편의를 돕기 위하여 동일한 구성요소에 대해서는 다른 도면에 도시되어 있더라도 동일한 부호를 부여하였다.Hereinafter, with reference to the accompanying drawings, it will be described in detail a preferred embodiment of the present invention. In the description of the embodiments, the same components are designated by the same reference numerals for the convenience of understanding, even though shown in different drawings.

도 3은 본 발명에 따른 테스터 보정 시스템에 관한 도면이다. 도 3을 참조하면, 본 발명에 따른 테스터 보정 시스템은 메모리 장치를 테스트하기 위한 전기적/물리적 신호를 처리하는 테스트 보드와, 메모리 장치에 전기적인 신호를 인가하여 동작을 테스트하는 TPG(Timing Pattern Generator) 보드(200)와, 메모리 테스트 장비의 전반적인 제어를 담당하는 컴퓨터(Personal Computer, 300)와, 전원을 공급하는 전원공급부(410)와 TPG 보드의 열을 냉각시키기 위한 냉각기(405)를 구비한다.3 is a diagram of a tester correction system according to the present invention. Referring to FIG. 3, a tester correction system according to the present invention includes a test board for processing an electrical / physical signal for testing a memory device, and a timing pattern generator (TPG) for testing an operation by applying an electrical signal to the memory device. A

또한 상기 테스트 보드는 다수개의 메모리를 실장하기 위한 DUT(Device Under test) 보드(100)를 적어도 하나 이상 구비한다.In addition, the test board includes at least one device under test (DUT)

그리고 테스트를 수행하기 전에 메모리 자체적으로 갖게 되는 스큐를 미리 측정하여 샘플 메모리로 처리한다.Before the test is performed, the skew of the memory itself is measured in advance and processed into sample memory.

샘플 메모리는 각 채널 별로 반복 실험하여 정밀하다고 판단되는 것을 이용하는 것이 바람직하다.It is preferable to use a sample memory that is determined to be accurate by repeating experiments for each channel.

도 4는 도 3의 TPG 보드에 관한 상세도면이다. 도 4를 참조하면, 상기 TPG 보드(200)는 테스트 패턴 신호를 발생시키는 패턴 발생부(ALPG, 201)와, 신호의 시퀀스를 제어하는 시퀀셜 제어부(204)와, 샘플 메모리의 각 채널에 대한 스큐 값을 저장하는 EEPROM(205)과, TPG 보드(200)의 전반 적인 신호 처리에 관한 제어를 담당하는 제어부(210) 그리고 각 채널별로 인가되는 신호에 대한 온/오프를 전달하는 릴레이부들(203)로 구성된다.4 is a detailed view of the TPG board of FIG. Referring to FIG. 4, the

상기 릴레이부들(203)은 각각 신호의 전달 및 검출을 수행하기 위한 드라이버(DR)/비교기(CP)(202)를 더 구비한다. 디지털 신호 처리를 위한 DPS(211)와 아날 로그 신호를 처리하는 아날로그 처리부가 더 포함된다.Each of the

상기와 같이 구현된 상태에서 PC(300)에서 커맨드가 인터페이스 보드를 통해 상기 TPG 보드(200)로 전달된다. 상기 커맨드는 상기 TPG 보드(200)내의 ALPG(201) 및 시퀀셜 제어부(204)로 인가되고, 테스트 패턴이 발생된다. 상기 테스트 패턴은 드라이버(202)에서 DUT의 스펙에 맞도록 변환되고 상기 릴레이부(203)를 통해 DUT로 전달된다. In the state implemented as described above, a command is transmitted from the PC 300 to the

테스트 패턴에 의해 DUT에서 발생하는 신호는 상기 릴레이부(203)를 통해 비교기(202)로 전달되고, 최종적으로 PC까지 전달되어 DUT의 정상/불량 여부를 판별할 수 있도록 한다.The signal generated from the DUT by the test pattern is transmitted to the

상기와 같이 구성된 상태에서도 드라이버와 메모리에 인가하는 전기적 신호에 높은 전류량이 요구되므로 시간의 경과 또는 여러 요인에 의해 스큐가 변동될 가능성이 있다.Even in the above-described state, since a high amount of current is required for the electrical signals applied to the driver and the memory, there is a possibility that the skew may vary due to time or various factors.

즉, 인가/측정하고자 하는 신호가 정상이어야 하는데도, 불량으로 판정될 가능성이 있는 것이다.That is, even if the signal to be applied / measured should be normal, there is a possibility that it is determined to be defective.

본 발명은 메모리 테스트 시스템에서 장비 보정 과정을 거쳐 인가/측정하고자 하는 신호간의 스큐를 일치시켜주어 테스트의 신뢰성을 확보하기 위함이다.The present invention is to ensure the reliability of the test by matching the skew between the signal to be applied / measured through the equipment calibration process in the memory test system.

도 5는 본 발명을 구현하기 위한 테스터 보정 시스템의 설치 형상을 보여주는 도면이다. 도 5를 참조하면 테스터 보정을 위해 소켓 위에 별도의 장비가 추가되지 않는다. 다만 샘플 디바이스만이 설치되어 샘플 디바이스의 스큐만을 측정할 수 있도록 한다.5 is a view showing the installation shape of the tester correction system for implementing the present invention. Referring to FIG. 5, no additional equipment is added to the socket for calibrating the tester. Only the sample device is installed so that only the skew of the sample device can be measured.

이렇게 도 5에 도시된 형태에 따라 샘플 디바이스의 스큐가 측정된 이후의 테스터 보정 방법을 설명하면 다음과 같다.The tester correction method after the skew of the sample device is measured according to the form shown in FIG. 5 will now be described.

도 6은 본 발명의 바람직한 실시예에 따른 테스트 보정 방법에 관한 도면이다. 도 6을 참조하면, 샘플 디바이스 스큐 측정이 수행되면(S100), 각 핀들의 /RAS, /CAS, /WE, DQ 등에 관하여 테스트 유효 구간을 검색한다(S102). 이후 미리 측정하여 알고 있는 샘플 디바이스의 스큐 측정값을 적용하여 현 메모리 테스트 시스템의 측정된 유효 구간의 실제 센터 포지션을 결정하고(S104), TPG 보드의 EEPROM에 스큐 데이터를 저장한다(S106).6 is a diagram of a test calibration method according to a preferred embodiment of the present invention. Referring to FIG. 6, when sample device skew measurement is performed (S100), a test valid interval is searched for / RAS, / CAS, / WE, DQ, etc. of each pin (S102). Subsequently, the actual center position of the measured valid interval of the current memory test system is determined by applying the measured skew value of the known sample device in advance (S104), and the skew data is stored in the EEPROM of the TPG board (S106).

상기 방법을 타이밍 관계도(도 7)를 이용하여 상세히 설명하면 다음과 같다.The method will be described in detail with reference to the timing relationship diagram (Fig. 7).

도 7a는 샘플 메모리 스큐 측정에 관한 도면이고, 도 7b는 TPG 보드의 유효 구간 측정에 관한 도면이고, 도 7c는 샘플 메모리의 스큐값을 적용한 실제 신호 처리에 관한 도면이다.FIG. 7A is a diagram illustrating a sample memory skew measurement, FIG. 7B is a diagram illustrating a valid section measurement of a TPG board, and FIG. 7C is a diagram illustrating actual signal processing applying a skew value of the sample memory.

도 7a에서는 미리 측정하여 알고 있는 임의의 신호의 스큐 값을 보여내고 있다. 유효구간이 200∼400ps이고 기준신호와 임의의 신호간의 유효구간의 중심과는 30ps 차이가 발생한다. 즉 30ps의 스큐가 있는 셈이다.In FIG. 7A, a skew value of an arbitrary signal measured in advance is shown. The effective section is 200-400ps and a 30ps difference occurs with the center of the valid section between the reference signal and an arbitrary signal. That's 30 ps of skew.

도 7b에서는 보정하고자 하는 현 시스템의 TPG 보드에서 샘플 메모리 디바이스를 사용하여 측정한 임의의 신호 및 기준신호를 보여주고 있다. 그리고 일정 시간(예컨대, 10ps) 간격으로 딜레이시키면서 유효구간을 검색한다.7B shows arbitrary signals and reference signals measured using a sample memory device on the TPG board of the current system to be calibrated. The effective section is searched for with a delay at a predetermined time (for example, 10 ps).

도 7c에서는 도 7a로부터 미리 알고 있는 기준신호와 유효구간의 중심과의 차이를 보상하여 센터 포지션을 결정하는 것을 나타낸다.In FIG. 7C, the center position is determined by compensating for the difference between the reference signal known from FIG. 7A and the center of the effective section.

이상 본 발명에 대하여 그 바람직한 실시예를 참조하여 설명하였지만, 해당 기술 분야의 숙련된 당업자는 하기의 특허 청구의 범위에 기재된 본 발명의 기술적 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시켜 실시할 수 있음을 이해할 수 있을 것이다. 따라서, 본 발명의 앞으로의 실시예들의 변경은 본 발명의 기술을 벗어날 수 없을 것이다.Although the present invention has been described above with reference to its preferred embodiments, those skilled in the art will variously modify the present invention without departing from the spirit and scope of the invention as set forth in the claims below. And can be practiced with modification. Accordingly, modifications to future embodiments of the present invention will not depart from the technology of the present invention.

이상 설명한 바와 같이, 본 발명에 따른 메모리 테스트 시스템은 대량의 메모리를 동시에 테스트함에 있어 중요한 안정성 및 신뢰성을 확보하기 위해 보정시 외부의 측정 장비를 사용하지 않고, 샘플 메모리 디바이스 자체를 이용하여 자동으로 보정할 수 있도록 하여 신뢰성 및 안정성 그리고 정밀성을 증가시킨다. 또한 보정시 발생하는 외부장비의 의존성이 없어 개발 시간 단축 및 개발 비용의 상당 부분을 절감할 수 있도록 한다.As described above, the memory test system according to the present invention automatically corrects using a sample memory device itself without using external measuring equipment during calibration to ensure important stability and reliability in simultaneously testing a large amount of memory. To increase reliability, stability and precision. In addition, there is no dependence on external equipment generated during calibration, which reduces the development time and significantly reduces the development cost.

Claims (9)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020060029602A KR100783647B1 (en) | 2006-03-31 | 2006-03-31 | A method for skew compensation and an apparatus using the method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020060029602A KR100783647B1 (en) | 2006-03-31 | 2006-03-31 | A method for skew compensation and an apparatus using the method |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20070098229A KR20070098229A (en) | 2007-10-05 |

| KR100783647B1 true KR100783647B1 (en) | 2007-12-07 |

Family

ID=38804316

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020060029602A KR100783647B1 (en) | 2006-03-31 | 2006-03-31 | A method for skew compensation and an apparatus using the method |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR100783647B1 (en) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102651975B1 (en) * | 2023-11-10 | 2024-03-27 | 코싸인온 주식회사 | Interactive dram signal analyzer and method for analyzing and calibrating dram signal using the same |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001126494A (en) * | 1999-10-28 | 2001-05-11 | Ando Electric Co Ltd | Semiconductor memory test device, and its test method |

| JP2002350502A (en) * | 2001-05-25 | 2002-12-04 | Ando Electric Co Ltd | Semiconductor testing apparatus |

| KR20020092680A (en) * | 2001-06-05 | 2002-12-12 | 삼성전자 주식회사 | A method for detecting and compensating the skew between test signals using boundary scan cell |

| JP2003004814A (en) * | 2001-06-21 | 2003-01-08 | Ando Electric Co Ltd | Method of correcting skew and tester for semiconductor integrated circuit |

-

2006

- 2006-03-31 KR KR1020060029602A patent/KR100783647B1/en active IP Right Grant

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001126494A (en) * | 1999-10-28 | 2001-05-11 | Ando Electric Co Ltd | Semiconductor memory test device, and its test method |

| JP2002350502A (en) * | 2001-05-25 | 2002-12-04 | Ando Electric Co Ltd | Semiconductor testing apparatus |

| KR20020092680A (en) * | 2001-06-05 | 2002-12-12 | 삼성전자 주식회사 | A method for detecting and compensating the skew between test signals using boundary scan cell |

| JP2003004814A (en) * | 2001-06-21 | 2003-01-08 | Ando Electric Co Ltd | Method of correcting skew and tester for semiconductor integrated circuit |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102651975B1 (en) * | 2023-11-10 | 2024-03-27 | 코싸인온 주식회사 | Interactive dram signal analyzer and method for analyzing and calibrating dram signal using the same |

| KR102660059B1 (en) * | 2023-11-10 | 2024-04-23 | 코싸인온 주식회사 | Method for analyzing and calibrating dram signal using interactive dram signal analyzer |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20070098229A (en) | 2007-10-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7414421B2 (en) | Insertable calibration device | |

| US6479983B1 (en) | Semiconductor device testing apparatus having timing hold function | |

| US6105157A (en) | Salphasic timing calibration system for an integrated circuit tester | |

| US6556934B2 (en) | Timing calibration method and semiconductor device testing apparatus having timing calibration function | |

| EP1295139B1 (en) | Arrangement for calibrating timing of an integrated circuit wafer tester and method | |

| JP4672057B2 (en) | Calibration of automatic test equipment | |

| US6586924B1 (en) | Method for correcting timing for IC tester and IC tester having correcting function using the correcting method | |

| US6417682B1 (en) | Semiconductor device testing apparatus and its calibration method | |

| EP1440328B1 (en) | Method and apparatus for calibration and validation of high performance dut power supplies | |

| US6492797B1 (en) | Socket calibration method and apparatus | |

| US5256964A (en) | Tester calibration verification device | |

| CN112821885A (en) | Relative time delay measurement calibration method and device for chips of each channel of ATE (automatic test equipment) | |

| US6812727B2 (en) | Semiconductor integrated circuit device and testing method thereof | |

| KR101348425B1 (en) | Device for timing calibration of automatic test equipment | |

| KR100783647B1 (en) | A method for skew compensation and an apparatus using the method | |

| US6882139B2 (en) | Electronic component, tester device and method for calibrating a tester device | |

| CN112684394A (en) | Multi-probe time sequence calibration jig and calibration method | |

| JP2000199781A (en) | Semiconductor device tester and its calibration method | |

| TWI644111B (en) | Semiconductor test method and apparatus for controlling tester | |

| US20100018286A1 (en) | Calibration apparatus, contact judging method and semiconductor testing apparatus | |

| US6677745B2 (en) | Test apparatus for parallel testing a number of electronic components and a method for calibrating the test apparatus | |

| KR100959628B1 (en) | Apparatus for synchronizing memory test board | |

| TWI220934B (en) | Ate calibration method | |

| US20080174319A1 (en) | Load Board Based Test Circuits | |

| US6829553B2 (en) | Method of and apparatus for measuring the correctness of and correcting an automatic test arrangement |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20130930 Year of fee payment: 7 |

|

| FPAY | Annual fee payment |

Payment date: 20140527 Year of fee payment: 8 |

|

| FPAY | Annual fee payment |

Payment date: 20150423 Year of fee payment: 9 |

|

| FPAY | Annual fee payment |

Payment date: 20160616 Year of fee payment: 10 |

|

| FPAY | Annual fee payment |

Payment date: 20170628 Year of fee payment: 11 |

|

| FPAY | Annual fee payment |

Payment date: 20180528 Year of fee payment: 12 |

|

| FPAY | Annual fee payment |

Payment date: 20190604 Year of fee payment: 13 |