KR100269301B1 - Capacitor for preventing barrier layer from oxidizing and manufacturing method thereof - Google Patents

Capacitor for preventing barrier layer from oxidizing and manufacturing method thereof Download PDFInfo

- Publication number

- KR100269301B1 KR100269301B1 KR1019970033246A KR19970033246A KR100269301B1 KR 100269301 B1 KR100269301 B1 KR 100269301B1 KR 1019970033246 A KR1019970033246 A KR 1019970033246A KR 19970033246 A KR19970033246 A KR 19970033246A KR 100269301 B1 KR100269301 B1 KR 100269301B1

- Authority

- KR

- South Korea

- Prior art keywords

- layer

- interlayer insulating

- contact hole

- forming

- capacitor

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L28/00—Passive two-terminal components without a potential-jump or surface barrier for integrated circuits; Details thereof; Multistep manufacturing processes therefor

- H01L28/40—Capacitors

- H01L28/60—Electrodes

- H01L28/65—Electrodes comprising a noble metal or a noble metal oxide, e.g. platinum (Pt), ruthenium (Ru), ruthenium dioxide (RuO2), iridium (Ir), iridium dioxide (IrO2)

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L28/00—Passive two-terminal components without a potential-jump or surface barrier for integrated circuits; Details thereof; Multistep manufacturing processes therefor

- H01L28/40—Capacitors

- H01L28/60—Electrodes

- H01L28/75—Electrodes comprising two or more layers, e.g. comprising a barrier layer and a metal layer

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Semiconductor Memories (AREA)

Abstract

Description

본 발명은 반도체 메모리 장치 및 그 제조 방법에 관한 것으로, 특히 장벽층의 산화를 방지하는 커패시터 및 그 제조 방법에 관한 것이다.BACKGROUND OF THE INVENTION 1. Field of the Invention The present invention relates to a semiconductor memory device and a method for manufacturing the same, and more particularly, to a capacitor for preventing oxidation of a barrier layer and a method for manufacturing the same.

DRAM(Dynamic Random Access Memory)의 집적도가 증가함에 따라, 제한된 셀 면적 내에서 커패시턴스를 증가시키기 위하여 커패시터의 유전막을 박막화하는 방법, 또는 커패시터의 유효 면적을 증가시키기 위해 커패시터 하부 전극의 구조를 입체화시키는 방법 등이 제안되고 있다.As the density of dynamic random access memory (DRAM) increases, a method of thinning a dielectric film of a capacitor to increase capacitance within a limited cell area, or a method of three-dimensionalizing a structure of a capacitor lower electrode to increase an effective area of a capacitor And the like have been proposed.

그러나, 상기한 바와 같은 방법을 채용하더라도 기존의 유전체로는 1G DRAM 이상의 메모리 소자에서는 소자 작동에 필요한 커패시턴스 값을 얻기 어렵다. 따라서, 이와 같은 문제를 해결하기 위하여 커패시터의 유전막으로서 BST(Ba(Sr, Ti)O3), PZT(Pb(Zr, Ti)O3), PLZT((Pb, Zr)(Ti, La)TiO3)와 같은 고유전율을 갖는 박막으로 대체하는 연구가 활발히 진행중에 있다. 상기와 같은 고유전막을 사용하는 커패시터에서는 전극 물질로서 Pt, Ir, Ru, RuO2, IrO2등을 사용하며, 그 중에서도 특히 우수한 내산화성을 갖는 Pt는 실리콘과의 반응성이 크기 때문에 Pt를 전극 물질로서 채용하는 경우에는 Pt와 실리콘을 격리시킬 수 있는 장벽층(Barrier layer)을 필요로 한다.However, even if the above-described method is employed, it is difficult to obtain capacitance values required for device operation in memory devices of 1G DRAM or more using existing dielectrics. Therefore, in order to solve this problem, BST (Ba (Sr, Ti) O 3 ), PZT (Pb (Zr, Ti) O 3 ), PLZT ((Pb, Zr) (Ti, La) TiO as a dielectric film of a capacitor Research into replacing thin films with high dielectric constants such as 3 ) is actively underway. In the capacitor using the high-k dielectric layer, Pt, Ir, Ru, RuO 2 , IrO 2 , and the like are used as electrode materials. Among them, Pt having particularly excellent oxidation resistance has a high reactivity with silicon, so Pt is used as an electrode material. When employed as a barrier layer, a barrier layer capable of separating Pt and silicon is required.

일반적으로 사용되는 장벽층은 예를 들면 TiN, TaN, WN1-x등과 같은 금속 질화막이며, 이와 같은 장벽층은 유전막 증착 과정 또는 후속의 산화성 가스 분위기하에서의 열처리 과정에서 장벽층의 상면 또는 측면을 통하여 유입되는 산소와 결합하여 산화되어버리는 문제가 발생한다. 장벽층을 TiN을 사용하여 형성한 경우에는 산화되면 TiO2가 형성되고, 그 결과 하부 전극에 전기적인 단락 현상이 발생하게 된다.Commonly used barrier layers are, for example, metal nitride films such as TiN, TaN, WN 1-x, etc., and the barrier layers may be formed through the top or side of the barrier layer during dielectric deposition or subsequent heat treatment under an oxidizing gas atmosphere. There is a problem that the oxygen is combined with the incoming oxygen. When the barrier layer is formed using TiN, when oxidized, TiO 2 is formed, and as a result, an electrical short circuit occurs in the lower electrode.

따라서, 커패시터의 유전막으로서 고유전막을 사용하는 경우에 장벽층의 산화를 효과적으로 방지할 수 있도록 커패시터의 구조를 개선하는 것이 필요하다.Therefore, when the high dielectric film is used as the dielectric film of the capacitor, it is necessary to improve the structure of the capacitor so as to effectively prevent oxidation of the barrier layer.

따라서, 본 발명의 목적은 커패시터의 전극 물질과 실리콘과의 반응을 방지하기 위하여 채용되는 장벽층의 산화를 효과적으로 방지할 수 있는 구조를 가지는 반도체 메모리 장치의 커패시터를 제공하는 것이다.Accordingly, an object of the present invention is to provide a capacitor of a semiconductor memory device having a structure capable of effectively preventing oxidation of a barrier layer employed to prevent a reaction between a capacitor electrode material and silicon.

본 발명의 다른 목적은 상기와 같은 특징을 가지는 반도체 메모리 장치 커패시터의 제조 방법을 제공하는 것이다.Another object of the present invention is to provide a method of manufacturing a semiconductor memory device capacitor having the above characteristics.

도 1 내지 도 8은 본 발명의 제1 실시예에 따른 반도체 메모리 장치의 커패시터를 제조하는 방법을 설명하기 위하여 공정 순서에 따라 순차적으로 도시한 단면도들이다.1 through 8 are cross-sectional views sequentially illustrating a method of manufacturing a capacitor of a semiconductor memory device according to a first embodiment of the present invention, in order of a process.

도 9 및 도 10은 본 발명의 제2 실시예에 따른 반도체 메모리 장치의 커패시터를 제조하는 방법을 설명하기 위한 단면도들이다.9 and 10 are cross-sectional views illustrating a method of manufacturing a capacitor of a semiconductor memory device according to a second embodiment of the present invention.

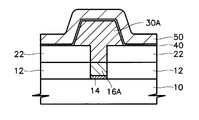

<도면의 주요 부분에 대한 부호의 설명><Description of the code | symbol about the principal part of drawing>

10 : 반도체 기판, 12 : 제1 층간 절연막 패턴10 semiconductor substrate, 12 first interlayer insulating film pattern

14 : 오믹 콘택층, 16 : 장벽 물질층14: ohmic contact layer, 16: barrier material layer

16A : 콘택 플러그, 22 : 제2 층간 절연막 패턴16A: contact plug, 22: second interlayer insulating film pattern

30 : 도전 물질층, 30A : 하부 전극30: conductive material layer, 30A: lower electrode

40 : 유전막, 50 : 상부 전극40: dielectric film, 50: upper electrode

상기 목적을 달성하기 위하여 본 발명에 따른 반도체 메모리 장치의 커패시터는 메모리 셀 트랜지스터가 형성된 반도체 기판의 소스/드레인 영역을 노출시키는 제1 콘택홀이 형성되어 있는 제1 층간 절연막 패턴과, 상기 제1 콘택홀 내에 형성되고, 상기 소스/드레인 영역에 대면하는 저면 및 상기 저면보다 더 넓은 상면을 갖춘 장벽층을 포함하는 콘택 플러그와, 상기 제1 층간 절연막 위에 형성되고 상기 장벽층의 상면을 일부만 노출시키는 제2 콘택홀이 형성되어 있는 제2 층간 절연막 패턴과, 상기 제2 콘택홀 내부 및 상기 제2 층간 절연막 패턴 위에 형성되고, 상기 장벽층과 전기적으로 연결되는 하부 전극과, 상기 하부 전극을 덮는 유전막과, 상기 유전막상에 형성된 상부 전극을 갖춘다.In order to achieve the above object, a capacitor of a semiconductor memory device according to the present invention includes a first interlayer insulating layer pattern having a first contact hole for exposing a source / drain region of a semiconductor substrate on which a memory cell transistor is formed, and the first contact. A contact plug formed in the hole and including a barrier layer having a bottom surface facing the source / drain region and an upper surface wider than the bottom surface, and an agent formed on the first interlayer insulating film and exposing only a portion of the top surface of the barrier layer; A second interlayer insulating film pattern having a second contact hole, a lower electrode formed in the second contact hole and on the second interlayer insulating film pattern, and electrically connected to the barrier layer, a dielectric film covering the lower electrode; And an upper electrode formed on the dielectric layer.

상기 장벽층은 TiN, TiAlN, TaSiN, TaAlN, TiSiN, TaSi, TiSi, Ta, TaN, CoSi 및 Co로 이루어지는 군에서 선택된 어느 하나로 구성된다.The barrier layer is composed of any one selected from the group consisting of TiN, TiAlN, TaSiN, TaAlN, TiSiN, TaSi, TiSi, Ta, TaN, CoSi and Co.

상기 하부 전극은 Pt, Ir, IrO2, Ru, RuO2및 산화물 전도체로 이루어지는 군에서 선택된 어느 하나로 구성된다.The lower electrode is composed of any one selected from the group consisting of Pt, Ir, IrO 2 , Ru, RuO 2, and oxide conductors.

상기 유전막은 STO(SrTiO3), BST(Ba(Sr, Ti)O3), PZT(Pb(Zr, Ti)O3) 및 PLZT((Pb, Zr)(Ti, La)TiO3)로 이루어지는 군에서 선택된 어느 하나로 구성된다.The dielectric film is composed of STO (SrTiO 3 ), BST (Ba (Sr, Ti) O 3 ), PZT (Pb (Zr, Ti) O 3 ) and PLZT ((Pb, Zr) (Ti, La) TiO 3 ) It consists of any one selected from the group.

상기 콘택 플러그는 상기 소스/드레인 영역과 상기 장벽층 사이에 형성된 오믹 콘택층을 더 포함할 수 있다. 바람직하게는, 상기 오믹 콘택층은 금속 실리사이드로 구성된다.The contact plug may further include an ohmic contact layer formed between the source / drain region and the barrier layer. Preferably, the ohmic contact layer is made of metal silicide.

상기 다른 목적을 달성하기 위하여, 본 발명에 따른 반도체 메모리 장치 커패시터의 제조 방법에 따르면, 반도체 기판상에 상기 반도체 기판의 일부를 노출시키는 제1 콘택홀을 포함하는 제1 층간 절연막 패턴을 형성한다. 상기 제1 콘택홀 내부에 물질 확산 방지를 위한 장벽층을 포함하는 콘택 플러그를 형성한다. 상기 콘택 플러그가 형성된 결과물상에 상기 콘택 플러그의 상면을 노출시키는 제2 콘택홀을 포함하는 제2 층간 절연막 패턴을 형성한다. 상기 제2 층간 절연막 패턴이 형성된 결과물상에 상기 제2 콘택홀을 통하여 상기 콘택 플러그와 연결되는 하부 전극을 형성한다. 상기 하부 전극 위에 유전막을 형성한다. 상기 유전막 위에 상부 전극을 형성한다.In order to achieve the above object, according to the method of manufacturing a semiconductor memory device capacitor according to the present invention, to form a first interlayer insulating film pattern including a first contact hole for exposing a portion of the semiconductor substrate on a semiconductor substrate. A contact plug including a barrier layer for preventing material diffusion is formed in the first contact hole. A second interlayer insulating layer pattern including a second contact hole exposing an upper surface of the contact plug is formed on a resultant on which the contact plug is formed. A lower electrode connected to the contact plug is formed through the second contact hole on the resultant product on which the second interlayer insulating layer pattern is formed. A dielectric film is formed on the lower electrode. An upper electrode is formed on the dielectric layer.

상기 제1 층간 절연막 패턴을 형성하는 단계는 상기 반도체 기판상에 제1 층간 절연막을 형성하는 단계와, 상기 제1 층간 절연막을 포토리소그래피 공정을 이용하여 건식 식각 공정을 적용하여 패터닝하여 기둥 형상의 제1 콘택홀을 포함하는 제1 층간 절연막 패턴을 형성하는 단계를 포함할 수 있다.The forming of the first interlayer insulating layer pattern may include forming a first interlayer insulating layer on the semiconductor substrate, and patterning the first interlayer insulating layer by using a dry etching process using a photolithography process to form a pillar-shaped material. The method may include forming a first interlayer insulating layer pattern including a first contact hole.

또는, 상기 제1 층간 절연막 패턴을 형성하는 단계는 상기 반도체 기판상에 제1 층간 절연막을 형성하는 단계와, 상기 제1 층간 절연막을 포토리소그래피 공정을 이용하여 습식 식각 및 건식 식각 공정을 순차로 적용하여 패터닝함으로써 상부측 입구가 넓은 기둥 형상의 제1 콘택홀을 포함하는 제1 층간 절연막 패턴을 형성하는 단계를 포함할 수 있다.Alternatively, the forming of the first interlayer insulating layer pattern may include forming a first interlayer insulating layer on the semiconductor substrate and sequentially applying a wet etching process and a dry etching process to the first interlayer insulating layer using a photolithography process. And forming a first interlayer insulating layer pattern including the first contact hole having a wide columnar opening by patterning.

상기 콘택 플러그를 형성하는 단계는 상기 제1 콘택홀 내부에 상기 장벽층을 채우기 전에 상기 제1 콘택홀에 의해 노출된 반도체 기판의 표면에 오믹 콘택층을 형성하는 단계를 더 포함할 수 있다. 상기 오믹 콘택층은 금속 실리사이드로 구성된다.The forming of the contact plug may further include forming an ohmic contact layer on a surface of the semiconductor substrate exposed by the first contact hole before filling the barrier layer in the first contact hole. The ohmic contact layer is composed of a metal silicide.

본 발명에 의하면, 상부로부터 하부 전극을 통해 유입되는 산소 확산의 경로가 길어져서 장벽층의 산화를 억제할 수 있을 뿐 만 아니라 장벽층의 측면이 전혀 노출되지 않으므로 장벽층의 측면을 통한 산소 유입을 완전히 차단할 수 있다.According to the present invention, the path of oxygen diffusion introduced from the top through the lower electrode is not only long to inhibit oxidation of the barrier layer, but also the side of the barrier layer is not exposed at all so that oxygen inflow through the side of the barrier layer is prevented. You can cut it off completely.

다음에, 본 발명의 바람직한 실시예에 대하여 첨부 도면을 참조하여 상세히 설명한다.Next, a preferred embodiment of the present invention will be described in detail with reference to the accompanying drawings.

도 1 내지 도 8은 본 발명의 제1 실시예에 따른 반도체 메모리 장치의 커패시터를 제조하는 방법을 설명하기 위하여 공정 순서에 따라 순차적으로 도시한 단면도들이다.1 through 8 are cross-sectional views sequentially illustrating a method of manufacturing a capacitor of a semiconductor memory device according to a first embodiment of the present invention, in order of a process.

도 1을 참조하면, 메모리 셀 트랜지스터(도시 생략)와 같은 하부 구조(underlying structure)가 형성된 반도체 기판(10)상에 상기 하부 구조를 절연시키기 위하여 제1 층간 절연막을 형성하고, 그 위에 포토리소그래피 공정을 이용하여 상기 제1 층간 절연막을 일부 노출시키는 포토레지스트 패턴(도시 생략)을 형성한다. 그 후, 상기 포토레지스트 패턴을 식각 마스크로 하여 상기 노출된 제1 층간 절연막을 건식 식각함으로써 상기 트랜지스터의 소스/드레인 영역(도시 생략)을 노출시키는 기둥 형상의 제1 콘택홀(H1)을 포함하는 제1 층간 절연막 패턴(12)을 형성한다. 그 후, 상기 포토레지스트 패턴을 제거한다.Referring to FIG. 1, a first interlayer insulating film is formed on a

도 2를 참조하면, 상기 제1 콘택홀(H1)을 통해 노출된 반도체 기판(10)의 표면상에 예를 들면 TiSi, CoSi 등과 같은 금속 실리사이드를 사용하여 오믹 콘택(ohmic contact)층(14)을 형성한다. 상기 오믹 콘택층(14)은 상기 반도체 기판(10)의 실리콘과 후속 공정에서 상기 제1 콘택홀(H1)을 채우게 될 장벽층 구성 물질과의 오믹 콘택을 위하여 형성하는 것으로서, 원하는 바에 따라 생략 가능하다.Referring to FIG. 2, an

도 3을 참조하면, 상기 제1 층간 절연막 패턴(12)의 상부에 상기 제1 콘택홀(H1) 내부를 채우기에 충분한 두께로 장벽 물질층(16), 예를 들면 TiN층을 형성한다. 상기 장벽 물질층(16)을 형성하는 물질로서 상기한 바와 같은 TiN 외에도 상기 반도체 기판(10)의 실리콘과 후속 공정에서 사용되는 하부 전극 물질 즉 Pt 사이에서의 상호 확산을 방지할 수 있는 물질, 예를 들면 TiAlN, TaSiN, TaAlN, TiSiN, TaSi, TiSi, Ta, TaN, CoSi, Co 등과 같은 물질을 사용할 수 있다.Referring to FIG. 3, a

도 4를 참조하면, 건식 식각 공정 또는 CMP(Chemical Mechanical Polishing) 공정을 이용하여 상기 제1 콘택홀(H1) 내부를 제외한 상기 제1 층간 절연막 패턴(12) 상부의 장벽 물질층(16)을 모두 제거하여 상기 제1 콘택홀(H1) 내부에 장벽층(16A)을 형성한다. 상기 오믹 콘택층(14)과 장벽층(16A)은 콘택 플러그를 구성한다. 그 결과, 상기 콘택 플러그는 그 측면이 노출되지 않으면서 상면이 수평 방향으로 편평한 기둥 형상의 구조를 갖는 장벽층을 포함하게 된다. 상기 장벽층(16A)을 포함하는 콘택 플러그는 커패시터 하부 전극을 트랜지스터의 소스/드레인 영역과 연결시키는 콘택의 일부를 구성하게 된다.Referring to FIG. 4, all of the

도 5를 참조하면, 상기 장벽층(16A)이 형성된 결과물상에 제2 층간 절연막을 형성하고 포토리소그래피 공정을 이용하여 상기 제2 층간 절연막을 패터닝하여 상기 장벽층(16A)의 상면을 노출시키는 제2 콘택홀(H2)을 포함하는 제2 층간 절연막 패턴(22)을 형성한다.Referring to FIG. 5, a second interlayer insulating film is formed on the resultant layer on which the

도 6을 참조하면, 상기 제2 층간 절연막 패턴(22)이 형성된 결과물 전면에 하부 전극을 형성하기 위한 도전 물질층(30), 예를 들면 백금(Pt)층을 형성한다. 상기 도전 물질층(30)은 상기 설명한 바와 같은 백금(Pt) 외에 이리듐(Ir), 이리듐 이산화물(IrO2), 루테늄(Ru), 루테늄 이산화물(RuO2) 또는 기타 산화물 전도체를 사용하여 형성할 수 있다. 상기 도전 물질층(30)은 PVD(Physical Vapor Deposition) 공정 또는 CVD(Chemical Vapor Deposition) 공정을 이용하여 형성한다. 또는, 상기 제2 층간 절연막 패턴(22)이 형성된 결과물 전면에 도전 물질, 예를 들면 Pt를 증착한 후 리플로우시켜서 상기 도전 물질층(30)을 형성하는 것도 가능하다.Referring to FIG. 6, a

도 7을 참조하면, 상기 제2 층간 절연막 패턴(22)이 노출되도록 상기 도전 물질층(30)을 패터닝함으로써, 상기 제2 콘택홀(H2) 내에 형성된 콘택을 통하여 상기 장벽층(16A)과 접촉되는 하부 전극(30A)을 형성한다.Referring to FIG. 7, the

도 8을 참조하면, 상기 하부 전극(30A)이 형성된 결과물상에 유전막(40)을 형성한다. 상기 유전막(40)은 예를 들면 STO(SrTiO3), BST, PZT 또는 PLZT 계열의 물질을 사용하여 형성한다. 그 후, 상기 유전막(40)상에 예를 들면 Pt로 이루어지는 상부 전극(50)을 형성함으로써 본 발명의 제1 실시예에 따른 커패시터를 완성한다.Referring to FIG. 8, a

상기한 바와 같이 본 발명의 제1 실시예에 따르면, 커패시터를 반도체 기판의 소스/드레인 영역에 연결시키기 위한 콘택 내부에 장벽층이 존재함으로써 상부로부터 하부 전극을 통해 유입되는 산소 확산의 경로가 길어져서 장벽층의 산화를 억제할 수 있을 뿐 만 아니라 장벽층의 측면이 층간 절연막에 의하여 완전히 차단되어 전혀 노출되지 않으므로 장벽층의 측면을 통한 산소 유입을 완전히 차단할 수 있다. 또한, 커패시터를 반도체 기판의 소스/드레인 영역에 연결시키기 위한 콘택을 2 단계에 걸쳐 형성함으로써 상기와 같이 측면이 노출되지 않는 구조를 가지는 장벽층을 용이하게 형성할 수 있다.As described above, according to the first embodiment of the present invention, a barrier layer is provided inside the contact for connecting the capacitor to the source / drain region of the semiconductor substrate, thereby increasing the path of oxygen diffusion flowing in from the top through the lower electrode. Not only can the oxidation of the barrier layer be suppressed, but the side of the barrier layer is completely blocked by the interlayer insulating film so that it is not exposed at all, thereby completely blocking the oxygen inflow through the side of the barrier layer. In addition, by forming a contact for connecting the capacitor to the source / drain region of the semiconductor substrate in two steps, a barrier layer having a structure in which the side surface is not exposed as described above can be easily formed.

도 9 및 도 10은 본 발명의 제2 실시예에 따른 반도체 메모리 장치의 커패시터를 제조하는 방법을 설명하기 위한 단면도들이다.9 and 10 are cross-sectional views illustrating a method of manufacturing a capacitor of a semiconductor memory device according to a second embodiment of the present invention.

도 9를 참조하면, 제1 실시예에서 도 1을 참조하여 설명한 바와 같은 방법으로 반도체 기판(110)상에 제1 층간 절연막을 형성하고, 그 위에 포토리소그래피 공정을 이용하여 상기 제1 층간 절연막을 일부 노출시키는 포토레지스트 패턴(도시 생략)을 형성한다. 그 후, 상기 포토레지스트 패턴을 식각 마스크로 하여 상기 노출된 제1 층간 절연막을 소정의 깊이 만큼 부분적으로 습식 식각하고, 다시 상기 포토레지스트 패턴을 식각 마스크로 하여 상기 노출된 제1 층간 절연막을 건식 식각함으로써, 도 9에 도시한 바와 같이 상부측 입구가 넓은 기둥 형상의 콘택홀(H3)을 포함하는 제1 층간 절연막 패턴(112)을 형성한다. 그 후, 상기 포토레지스트 패턴을 제거한다.Referring to FIG. 9, in the first embodiment, a first interlayer insulating film is formed on the

도 10을 참조하면, 제1 실시예에서 도 2, 도 3 및 도 4를 참조하여 설명한 바와 같은 방법으로 상기 콘택홀(H3) 내부에 금속 실리사이드로 이루어지는 오믹 콘택층(114)과 장벽층(116A)으로 이루어지는 콘택 플러그를 형성한다. 그 결과, 상기 콘택 플러그는 그 측면이 노출되지 않으면서 수평 방향으로 편평하고 저면보다 더 넓은 상면을 갖춘 장벽층을 포함하게 된다. 상기 장벽층은 측면에서 볼 때 단면의 형상이 대략 "T"자형의 구조를 갖는다.Referring to FIG. 10, in the first embodiment, the

그 후, 제1 실시예에서 도 5 내지 도 8을 참조하여 설명한 바와 같은 방법으로 제2 층간 절연막 패턴(122)을 형성하고, 하부 전극(130A), 유전막(140) 및 상부 전극(150)을 형성하여 본 발명의 제2 실시예에 따른 커패시터를 완성한다.Thereafter, in the first embodiment, the second interlayer insulating

상기한 바와 같이 본 발명의 제2 실시예에 따르면, 제1 실시예에서와 마찬가지로 커패시터를 반도체 기판의 소스/드레인 영역에 연결시키기 위한 콘택 내부에 장벽층이 존재함으로써 상부로부터 하부 전극을 통해 유입되는 산소 확산의 경로가 길어져서 장벽층의 산화를 억제할 수 있을 뿐 만 아니라 장벽층의 측면이 층간 절연막에 의하여 완전히 차단되어 전혀 노출되지 않으므로 장벽층의 측면을 통한 산소 유입을 완전히 차단할 수 있으며, 장벽층의 단면 형상이 측면에서 볼 때 대략 "T"자형의 구조를 가지도록 저면보다 더 넓은 상면을 갖추고 있으므로, 커패시터를 반도체 기판의 소스/드레인 영역에 연결시키기 위한 콘택을 2 단계로 형성하는 데 있어서, 장벽층을 구성하는 콘택 플러그의 상부에 제2 콘택홀을 포함하는 제2 층간 절연막 패턴을 형성할 때의 얼라인 마진을 증가시키는 효과를 제공함으로써 장벽층을 구성하는 콘택 플러그와 하부 전극이 형성되는 제2 콘택홀과의 미스얼라인을 줄일 수 있다.As described above, according to the second embodiment of the present invention, as in the first embodiment, a barrier layer is present inside the contact for connecting the capacitor to the source / drain region of the semiconductor substrate, thereby flowing through the lower electrode from the top. The long path of oxygen diffusion not only inhibits oxidation of the barrier layer, but also completely blocks the inflow of oxygen through the side of the barrier layer because the side of the barrier layer is completely blocked by the interlayer insulating film and is not exposed at all. Since the cross-sectional shape of the layer has a wider top surface than the bottom surface to have a substantially "T" shaped side view, in forming two stages of contacts for connecting the capacitor to the source / drain regions of the semiconductor substrate. And forming a second interlayer insulating film pattern including a second contact hole on the contact plug forming the barrier layer. The first contact plug and a lower electrode constituting the barrier layer by providing an effect to increase the alignment margin when formed can be reduced and miss alignment of the contact hole.

상기한 바와 같이 본 발명의 바람직한 실시예들에 따르면, 커패시터를 반도체 기판의 소스/드레인 영역에 연결시키기 위한 콘택 내부에 장벽층이 존재함으로써 상부로부터 하부 전극을 통해 유입되는 산소 확산의 경로가 길어져서 장벽층의 산화를 억제할 수 있을 뿐 만 아니라 장벽층의 측면이 전혀 노출되지 않으므로 장벽층의 측면을 통한 산소 유입을 완전히 차단할 수 있다. 또한, 커패시터를 반도체 기판의 소스/드레인 영역에 연결시키기 위한 콘택을 2 단계에 걸쳐 형성함으로써 상기와 같이 측면이 노출되지 않는 구조를 가지는 장벽층을 용이하게 형성할 수 있다.As described above, according to the preferred embodiments of the present invention, a barrier layer is provided inside the contact for connecting the capacitor to the source / drain region of the semiconductor substrate, thereby increasing the path of oxygen diffusion introduced from the top through the lower electrode. Not only can the oxidation of the barrier layer be suppressed, but the sides of the barrier layer are not exposed at all, thus completely blocking the oxygen inflow through the sides of the barrier layer. In addition, by forming a contact for connecting the capacitor to the source / drain region of the semiconductor substrate in two steps, a barrier layer having a structure in which the side surface is not exposed as described above can be easily formed.

이상, 본 발명을 바람직한 실시예를 들어 상세하게 설명하였으나, 본 발명은 상기 실시예에 한정되지 않고, 본 발명의 기술적 사상의 범위 내에서 당 분야에서 통상의 지식을 가진 자에 의하여 여러가지 변형이 가능하다.The present invention has been described in detail with reference to preferred embodiments, but the present invention is not limited to the above embodiments, and various modifications can be made by those skilled in the art within the scope of the technical idea of the present invention. Do.

Claims (17)

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1019970033246A KR100269301B1 (en) | 1997-07-16 | 1997-07-16 | Capacitor for preventing barrier layer from oxidizing and manufacturing method thereof |

| US08/969,803 US6130124A (en) | 1996-12-04 | 1997-11-13 | Methods of forming capacitor electrodes having reduced susceptibility to oxidation |

| JP9331819A JPH10173154A (en) | 1996-12-04 | 1997-12-02 | Capacitor of semiconductor storage device and its manufacturing method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1019970033246A KR100269301B1 (en) | 1997-07-16 | 1997-07-16 | Capacitor for preventing barrier layer from oxidizing and manufacturing method thereof |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR19990010450A KR19990010450A (en) | 1999-02-18 |

| KR100269301B1 true KR100269301B1 (en) | 2000-10-16 |

Family

ID=19514743

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019970033246A KR100269301B1 (en) | 1996-12-04 | 1997-07-16 | Capacitor for preventing barrier layer from oxidizing and manufacturing method thereof |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR100269301B1 (en) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001210803A (en) * | 1999-11-18 | 2001-08-03 | Mitsubishi Electric Corp | Stacked capacitor and manufacturing method therefor |

| KR100550763B1 (en) * | 1999-12-22 | 2006-02-08 | 주식회사 하이닉스반도체 | Method of manufacturing a capacitor in a semiconductor device |

| KR100702116B1 (en) * | 2001-01-04 | 2007-03-30 | 주식회사 하이닉스반도체 | Fabrication method for semiconductor device having high insulator capacitor |

| KR20030002863A (en) | 2001-06-30 | 2003-01-09 | 주식회사 하이닉스반도체 | Ferroelectric memory device over cored pulg and method for fabricating the same |

| KR100846384B1 (en) * | 2002-06-29 | 2008-07-15 | 주식회사 하이닉스반도체 | Method for fabricating semiconductor device |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5506166A (en) * | 1993-04-02 | 1996-04-09 | Micron Technology, Inc. | Method for forming capacitor compatible with high dielectric constant materials having a low contact resistance layer |

| KR970013305A (en) * | 1995-08-21 | 1997-03-29 | 김광호 | Capacitor of Semiconductor Memory Device and Manufacturing Method Thereof |

-

1997

- 1997-07-16 KR KR1019970033246A patent/KR100269301B1/en not_active IP Right Cessation

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5506166A (en) * | 1993-04-02 | 1996-04-09 | Micron Technology, Inc. | Method for forming capacitor compatible with high dielectric constant materials having a low contact resistance layer |

| KR970013305A (en) * | 1995-08-21 | 1997-03-29 | 김광호 | Capacitor of Semiconductor Memory Device and Manufacturing Method Thereof |

Also Published As

| Publication number | Publication date |

|---|---|

| KR19990010450A (en) | 1999-02-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3452800B2 (en) | Highly integrated memory element and method of manufacturing the same | |

| KR100272172B1 (en) | Capacitor of semiconductor device and mamufacturing method thereof | |

| KR0147640B1 (en) | Capacitor of semiconductor device & its fabrication method | |

| KR100190111B1 (en) | Fabricating method for capacitor in semiconductor device | |

| US6130124A (en) | Methods of forming capacitor electrodes having reduced susceptibility to oxidation | |

| KR100287187B1 (en) | capacitor of semiconductor device and manufacturing method thereof | |

| KR20010113324A (en) | Method of manufacturing a capacitor in a semiconductor device | |

| KR100500949B1 (en) | Semiconductor storage device and its manufacturing method | |

| KR20000017627A (en) | Dram having a stacked capacitor and a method for fabricating the same | |

| US6344965B1 (en) | Capacitor using high dielectric constant film for semiconductor memory device and fabrication method therefor | |

| US6180970B1 (en) | Microelectronic devices including ferroelectric capacitors with lower electrodes extending into contact holes | |

| KR100418586B1 (en) | Method of forming memory device | |

| KR100269301B1 (en) | Capacitor for preventing barrier layer from oxidizing and manufacturing method thereof | |

| JP4053702B2 (en) | Semiconductor memory device and manufacturing method thereof | |

| KR100346833B1 (en) | Method for manufacturing capacitor of semiconductor memory device using electroplating method | |

| KR100668881B1 (en) | Capacitor and method of its manufacture | |

| KR100247479B1 (en) | Large integrated memory element and manufacturing method thererof | |

| KR100533970B1 (en) | Highly Integrated Memory Device and Manufacturing Method Thereof | |

| KR20000023170A (en) | Capacitor arranged on a supporting frame in a semiconductor arrangement and method for producing the same | |

| JP2001053246A (en) | Semiconductor device and manufacture thereof | |

| KR100532383B1 (en) | Manufacturing method of capacitor using high dielectric layer for semiconductor device | |

| KR20020000048A (en) | Method of manufacturing a capacitor in a semiconductor device | |

| JP2003218235A (en) | Memory device with composite contact plug and method of manufacturing the same | |

| KR100331116B1 (en) | Capacitor and its manufacturing method | |

| KR100255660B1 (en) | Method for etching ir electrode |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20090714 Year of fee payment: 10 |

|

| LAPS | Lapse due to unpaid annual fee |