JP6677449B2 - 半導体装置の駆動方法 - Google Patents

半導体装置の駆動方法 Download PDFInfo

- Publication number

- JP6677449B2 JP6677449B2 JP2015045474A JP2015045474A JP6677449B2 JP 6677449 B2 JP6677449 B2 JP 6677449B2 JP 2015045474 A JP2015045474 A JP 2015045474A JP 2015045474 A JP2015045474 A JP 2015045474A JP 6677449 B2 JP6677449 B2 JP 6677449B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- circuit

- drain

- source

- logic element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/0175—Coupling arrangements; Interface arrangements

- H03K19/0185—Coupling arrangements; Interface arrangements using field effect transistors only

- H03K19/018507—Interface arrangements

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/08—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using semiconductor devices

- H03K19/094—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using semiconductor devices using field-effect transistors

- H03K19/0944—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using semiconductor devices using field-effect transistors using MOSFET or insulated gate field-effect transistors, i.e. IGFET

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Computing Systems (AREA)

- General Engineering & Computer Science (AREA)

- Mathematical Physics (AREA)

- Power Engineering (AREA)

- Logic Circuits (AREA)

- Semiconductor Integrated Circuits (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

- Dram (AREA)

- Thin Film Transistor (AREA)

Description

本発明の一態様に係る半導体装置及びその駆動方法について、図1乃至図4を用いて説明する。

本発明の一態様に係る半導体装置及びその駆動方法について、図2、図3、図5乃至図7を用いて説明する。

本発明の一態様に係る半導体装置及びその駆動方法について、図13乃至図16を用いて説明する。

本実施の形態では、本発明の一態様の半導体装置の構成の一例について、図面を参照しながら説明する。

本実施の形態では、本発明の一態様の半導体装置の構成の一例について、図面を参照しながら説明する。特に、実施の形態4で説明した半導体装置の構成と相違する点について詳細に説明する。

本発明の一態様に係る半導体装置は、表示機器、パーソナルコンピュータ、記録媒体を備えた画像再生装置(代表的にはDVD:Digital Versatile Disc等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置)に用いることができる。その他に、本発明の一態様に係る半導体装置を用いることができる電子機器として、携帯電話機、携帯型を含むゲーム機、携帯情報端末、電子書籍端末、ビデオカメラ、デジタルスチルカメラ等のカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、デジタルオーディオプレイヤー等)、複写機、ファクシミリ、プリンタ、プリンタ複合機、現金自動預け入れ払い機(ATM)、自動販売機、医療機器などが挙げられる。これら電子機器の具体例を図12に示す。

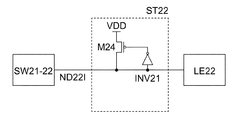

LE22 ロジックエレメント

LE2n ロジックエレメント

LE31 ロジックエレメント

LE32 ロジックエレメント

LE3n ロジックエレメント

SW21−21 回路

SW21−21a 回路

SW21−21b 回路

SW21−22 回路

SW21−22a 回路

SW21−22b 回路

SW21−2n 回路

SW22−21b 回路

SW22−22 回路

SW22−22b 回路

SW2n−21b 回路

SW2n−22 回路

SW2n−22b 回路

SW2n−2n 回路

SW2n−2nb 回路

SW31−31 回路

SW31−31a 回路

SW31−31b 回路

SW31−32 回路

SW31−32a 回路

SW31−32b 回路

SW3n−31b 回路

SW3n−32b 回路

SW3n−3n 回路

SW3n−3nb 回路

M21a トランジスタ

M21b トランジスタ

M22a トランジスタ

M22b トランジスタ

M23a トランジスタ

M23b トランジスタ

M24 トランジスタ

M31a トランジスタ

M31b トランジスタ

M32a トランジスタ

M32b トランジスタ

M33a トランジスタ

M33b トランジスタ

M34 トランジスタ

M35 トランジスタ

M36 トランジスタ

C21 容量素子

C22 容量素子

C31 容量素子

C32 容量素子

ST21 回路

ST22 回路

ST2n 回路

ST31 回路

ST32 回路

ST3n 回路

INV31 インバータ

21 インバータ

22 トランジスタ

23 トランジスタ

91 絶縁膜

92a 酸化物半導体膜

92b 酸化物半導体膜

92c 酸化物半導体膜

93 導電膜

94 導電膜

95 絶縁膜

96 導電膜

97 絶縁表面

201 ルックアップテーブル

202 記憶装置

203 レジスタ

204 AND回路

400 基板

401 素子分離領域

402 不純物領域

403 不純物領域

404 チャネル形成領域

405 絶縁膜

406 ゲート電極

411 絶縁膜

412 導電膜

413 導電膜

414 導電膜

416 導電膜

417 導電膜

418 導電膜

420 絶縁膜

421 絶縁膜

422 絶縁膜

430 半導体膜

430a 酸化物半導体膜

430c 酸化物半導体膜

431 ゲート絶縁膜

432 導電膜

433 導電膜

434 ゲート電極

601 半導体基板

610 素子分離領域

611 絶縁膜

612 絶縁膜

613 絶縁膜

625 導電膜

626 導電膜

627 導電膜

634 導電膜

635 導電膜

636 導電膜

637 導電膜

644 導電膜

651 導電膜

652 導電膜

653 導電膜

661 絶縁膜

662 ゲート絶縁膜

663 絶縁膜

701 半導体膜

710 領域

711 領域

721 導電膜

722 導電膜

731 ゲート電極

5001 筐体

5002 筐体

5003 表示部

5004 表示部

5005 マイクロホン

5006 スピーカー

5007 操作キー

5008 スタイラス

5101 車体

5102 車輪

5103 ダッシュボード

5104 ライト

5301 筐体

5302 扉

5303 扉

5401 筐体

5402 表示部

5403 キーボード

5404 ポインティングデバイス

5601 筐体

5602 筐体

5603 表示部

5604 表示部

5605 接続部

5606 操作キー

5801 筐体

5802 筐体

5803 表示部

5804 操作キー

5805 レンズ

5806 接続部

Claims (3)

- 第1のロジックエレメントと、第2のロジックエレメントと、第1の回路と、第1の配線と、を有し、

前記第1の回路は、第2の回路と、第3の回路と、を有し、

前記第2の回路は、第1乃至第3のトランジスタと、第1の容量素子と、を有し、

前記第3の回路は、第4乃至第6のトランジスタと、第2の容量素子と、を有し、

前記第1のトランジスタのソースまたはドレインの一方は、前記第1の配線と電気的に接続され、

前記第1のトランジスタのソースまたはドレインの他方は、前記第1の容量素子の一方の電極及び前記第2のトランジスタのゲートと電気的に接続され、

前記第2のトランジスタのソースまたはドレインの一方は、前記第1のロジックエレメントと電気的に接続され、

前記第2のトランジスタのソースまたはドレインの他方は、前記第3のトランジスタのソースまたはドレインの一方と電気的に接続され、

前記第3のトランジスタのソースまたはドレインの他方は、前記第2のロジックエレメントと電気的に接続され、

前記第4のトランジスタのソースまたはドレインの一方は、前記第1の配線と電気的に接続され、

前記第4のトランジスタのソースまたはドレインの他方は、前記第2の容量素子の一方の電極及び前記第5のトランジスタのゲートと電気的に接続され、

前記第5のトランジスタのソースまたはドレインの一方は、前記第1のロジックエレメントと電気的に接続され、

前記第5のトランジスタのソースまたはドレインの他方は、前記第6のトランジスタのソースまたはドレインの一方と電気的に接続され、

前記第6のトランジスタのソースまたはドレインの他方は、前記第2のロジックエレメントと電気的に接続され、

前記第1の回路は、前記第1のロジックエレメント及び前記第2のロジックエレメント間の導通状態を制御する機能を有し、

前記第2の回路は、前記第1のロジックエレメント及び前記第2のロジックエレメント間の導通状態を制御する第1のコンフィギュレーションデータを格納することができる機能を有し、

前記第3の回路は、前記第1のロジックエレメント及び前記第2のロジックエレメント間の導通状態を制御する第2のコンフィギュレーションデータを格納することができる機能を有する半導体装置の駆動方法であって、

前記第2の回路に格納されている前記第1のコンフィギュレーションデータに基づいて、前記第1のロジックエレメント及び前記第2のロジックエレメント間の導通状態を制御する第1の期間を有し、

前記第1の期間において、前記第3の回路に前記第2のコンフィギュレーションデータを書き込む第2の期間を有し、

前記第2の期間において、前記第6のトランジスタを非導通状態とするとともに、前記第4のトランジスタを導通状態とする第3の期間を有し、

前記第3の期間において、前記第5のトランジスタのソースまたはドレインの一方に低レベルの信号を入力するとともに、前記第1の配線を介して前記第4のトランジスタのソースまたはドレインの一方に高レベルの信号を入力し、

前記第3の期間において、前記第2のロジックエレメントに入力されるクロック信号の供給を止め、

前記第3の期間の後、前記第3の回路に前記第2のコンフィギュレーションデータの書き込みを行い、

前記第3の期間の後、クロック信号の供給を再開する半導体装置の駆動方法。 - 請求項1において、

前記第1のロジックエレメントは、ルックアップテーブルと、レジスタと、AND回路と、を有し、

前記AND回路は、第1の入力端子と、第2の入力端子と、を有し、

前記レジスタには、前記ルックアップテーブルからの出力信号が入力され、

前記第1の入力端子には、前記レジスタからの出力信号が入力され、

前記第3の期間において、前記第2の入力端子には、低レベルの信号が入力される半導体装置の駆動方法。 - 第1のロジックエレメントと、第2のロジックエレメントと、第1の回路と、第4の回路と、第1の配線と、第2の配線と、を有し、

前記第1の回路は、第2の回路と、第3の回路と、を有し、

前記第2の回路は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第1の容量素子と、を有し、

前記第3の回路は、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、第2の容量素子と、を有し、

前記第4の回路は、第7のトランジスタと、インバータと、を有し、

前記第1のトランジスタのソースまたはドレインの一方は、前記第1の配線と電気的に接続され、

前記第1のトランジスタのソースまたはドレインの他方は、前記第1の容量素子の一方の電極及び前記第2のトランジスタのゲートと電気的に接続され、

前記第2のトランジスタのソースまたはドレインの一方は、前記第1のロジックエレメントと電気的に接続され、

前記第2のトランジスタのソースまたはドレインの他方は、前記第3のトランジスタのソースまたはドレインの一方と電気的に接続され、

前記第3のトランジスタのソースまたはドレインの他方は、前記第4の回路と電気的に接続され、

前記第4のトランジスタのソースまたはドレインの一方は、前記第1の配線と電気的に接続され、

前記第4のトランジスタのソースまたはドレインの他方は、前記第2の容量素子の一方の電極及び前記第5のトランジスタのゲートと電気的に接続され、

前記第5のトランジスタのソースまたはドレインの一方は、前記第1のロジックエレメントと電気的に接続され、

前記第5のトランジスタのソースまたはドレインの他方は、前記第6のトランジスタのソースまたはドレインの一方と電気的に接続され、

前記第6のトランジスタのソースまたはドレインの他方は、前記第4の回路と電気的に接続され、

前記第4の回路は、前記第2のロジックエレメントと電気的に接続され、

前記第7のトランジスタのソースまたはドレインの一方は、前記第3のトランジスタのソースまたはドレインの他方、前記第6のトランジスタのソースまたはドレインの他方、及び前記インバータの入力端子と電気的に接続され、

前記第7のトランジスタのソースまたはドレインの他方は、前記第2の配線と電気的に接続され、

前記第7のトランジスタのゲートは、前記インバータの出力端子と電気的に接続され、

前記インバータの入力端子は、前記第2のロジックエレメントと電気的に接続され、

前記第1の回路は、前記第1のロジックエレメント及び前記第2のロジックエレメント間の導通状態を制御する機能を有し

前記第2の回路は、前記第1のロジックエレメント及び前記第2のロジックエレメント間の導通状態を制御する第1のコンフィギュレーションデータを格納することができる機能を有し、

前記第3の回路は、前記第1のロジックエレメント及び前記第2のロジックエレメント間の導通状態を制御する第2のコンフィギュレーションデータを格納することができる機能を有する半導体装置の駆動方法であって、

前記第2の回路に格納されている前記第1のコンフィギュレーションデータに基づいて、前記第1のロジックエレメント及び前記第2のロジックエレメント間の導通状態を制御する第1の期間を有し、

前記第1の期間において、前記第3の回路に前記第2のコンフィギュレーションデータを書き込む第2の期間を有し、

前記第2の期間において、前記第6のトランジスタを非導通状態とするとともに、前記第4のトランジスタを導通状態とする第3の期間を有し、

前記第3の期間において、前記第5のトランジスタのソースまたはドレインの一方に低レベルの信号を入力するとともに、前記第1の配線を介して前記第4のトランジスタのソースまたはドレインの一方に高レベルの信号を入力し、

前記第3の期間において、前記第2のロジックエレメントに入力されるクロック信号の供給を止め、

前記第3の期間の後、前記第3の回路に前記第2のコンフィギュレーションデータの書き込みを行い、

前記第3の期間の後、クロック信号の供給を再開する半導体装置の駆動方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015045474A JP6677449B2 (ja) | 2014-03-13 | 2015-03-09 | 半導体装置の駆動方法 |

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014050500 | 2014-03-13 | ||

| JP2014050500 | 2014-03-13 | ||

| JP2014051645 | 2014-03-14 | ||

| JP2014051645 | 2014-03-14 | ||

| JP2015045474A JP6677449B2 (ja) | 2014-03-13 | 2015-03-09 | 半導体装置の駆動方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015188213A JP2015188213A (ja) | 2015-10-29 |

| JP2015188213A5 JP2015188213A5 (ja) | 2018-04-19 |

| JP6677449B2 true JP6677449B2 (ja) | 2020-04-08 |

Family

ID=54070123

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015045474A Active JP6677449B2 (ja) | 2014-03-13 | 2015-03-09 | 半導体装置の駆動方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9385720B2 (ja) |

| JP (1) | JP6677449B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6541376B2 (ja) | 2014-03-13 | 2019-07-10 | 株式会社半導体エネルギー研究所 | プログラマブルロジックデバイスの動作方法 |

| CN108352837A (zh) | 2015-11-13 | 2018-07-31 | 株式会社半导体能源研究所 | 半导体装置、电子构件及电子设备 |

| JP6917168B2 (ja) | 2016-04-01 | 2021-08-11 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| WO2018069787A1 (en) | 2016-10-14 | 2018-04-19 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, broadcasting system, and electronic device |

Family Cites Families (120)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60198861A (ja) | 1984-03-23 | 1985-10-08 | Fujitsu Ltd | 薄膜トランジスタ |

| JPH0244256B2 (ja) | 1987-01-28 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn2o5deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPS63210023A (ja) | 1987-02-24 | 1988-08-31 | Natl Inst For Res In Inorg Mater | InGaZn↓4O↓7で示される六方晶系の層状構造を有する化合物およびその製造法 |

| JPH0244260B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn5o8deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244258B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn3o6deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244262B2 (ja) | 1987-02-27 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn6o9deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244263B2 (ja) | 1987-04-22 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn7o10deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH05251705A (ja) | 1992-03-04 | 1993-09-28 | Fuji Xerox Co Ltd | 薄膜トランジスタ |

| JP3479375B2 (ja) | 1995-03-27 | 2003-12-15 | 科学技術振興事業団 | 亜酸化銅等の金属酸化物半導体による薄膜トランジスタとpn接合を形成した金属酸化物半導体装置およびそれらの製造方法 |

| KR100394896B1 (ko) | 1995-08-03 | 2003-11-28 | 코닌클리케 필립스 일렉트로닉스 엔.브이. | 투명스위칭소자를포함하는반도체장치 |

| JP3625598B2 (ja) | 1995-12-30 | 2005-03-02 | 三星電子株式会社 | 液晶表示装置の製造方法 |

| US5859544A (en) * | 1996-09-05 | 1999-01-12 | Altera Corporation | Dynamic configurable elements for programmable logic devices |

| JP4170454B2 (ja) | 1998-07-24 | 2008-10-22 | Hoya株式会社 | 透明導電性酸化物薄膜を有する物品及びその製造方法 |

| JP2000150861A (ja) | 1998-11-16 | 2000-05-30 | Tdk Corp | 酸化物薄膜 |

| JP3276930B2 (ja) | 1998-11-17 | 2002-04-22 | 科学技術振興事業団 | トランジスタ及び半導体装置 |

| TW460731B (en) | 1999-09-03 | 2001-10-21 | Ind Tech Res Inst | Electrode structure and production method of wide viewing angle LCD |

| JP4089858B2 (ja) | 2000-09-01 | 2008-05-28 | 国立大学法人東北大学 | 半導体デバイス |

| KR20020038482A (ko) | 2000-11-15 | 2002-05-23 | 모리시타 요이찌 | 박막 트랜지스터 어레이, 그 제조방법 및 그것을 이용한표시패널 |

| US6978386B2 (en) * | 2000-12-28 | 2005-12-20 | Ge Fanuc Automation North America, Inc. | Method and apparatus for regulating current for programmable logic controllers |

| JP3997731B2 (ja) | 2001-03-19 | 2007-10-24 | 富士ゼロックス株式会社 | 基材上に結晶性半導体薄膜を形成する方法 |

| JP2002289859A (ja) | 2001-03-23 | 2002-10-04 | Minolta Co Ltd | 薄膜トランジスタ |

| JP4090716B2 (ja) | 2001-09-10 | 2008-05-28 | 雅司 川崎 | 薄膜トランジスタおよびマトリクス表示装置 |

| JP3925839B2 (ja) | 2001-09-10 | 2007-06-06 | シャープ株式会社 | 半導体記憶装置およびその試験方法 |

| WO2003040441A1 (en) | 2001-11-05 | 2003-05-15 | Japan Science And Technology Agency | Natural superlattice homologous single crystal thin film, method for preparation thereof, and device using said single crystal thin film |

| JP4164562B2 (ja) | 2002-09-11 | 2008-10-15 | 独立行政法人科学技術振興機構 | ホモロガス薄膜を活性層として用いる透明薄膜電界効果型トランジスタ |

| JP4083486B2 (ja) | 2002-02-21 | 2008-04-30 | 独立行政法人科学技術振興機構 | LnCuO(S,Se,Te)単結晶薄膜の製造方法 |

| CN1445821A (zh) | 2002-03-15 | 2003-10-01 | 三洋电机株式会社 | ZnO膜和ZnO半导体层的形成方法、半导体元件及其制造方法 |

| JP3933591B2 (ja) | 2002-03-26 | 2007-06-20 | 淳二 城戸 | 有機エレクトロルミネッセント素子 |

| US7339187B2 (en) | 2002-05-21 | 2008-03-04 | State Of Oregon Acting By And Through The Oregon State Board Of Higher Education On Behalf Of Oregon State University | Transistor structures |

| JP2004022625A (ja) | 2002-06-13 | 2004-01-22 | Murata Mfg Co Ltd | 半導体デバイス及び該半導体デバイスの製造方法 |

| US7105868B2 (en) | 2002-06-24 | 2006-09-12 | Cermet, Inc. | High-electron mobility transistor with zinc oxide |

| US7067843B2 (en) | 2002-10-11 | 2006-06-27 | E. I. Du Pont De Nemours And Company | Transparent oxide semiconductor thin film transistors |

| JP4166105B2 (ja) | 2003-03-06 | 2008-10-15 | シャープ株式会社 | 半導体装置およびその製造方法 |

| JP2004273732A (ja) | 2003-03-07 | 2004-09-30 | Sharp Corp | アクティブマトリクス基板およびその製造方法 |

| JP4108633B2 (ja) | 2003-06-20 | 2008-06-25 | シャープ株式会社 | 薄膜トランジスタおよびその製造方法ならびに電子デバイス |

| US7262463B2 (en) | 2003-07-25 | 2007-08-28 | Hewlett-Packard Development Company, L.P. | Transistor including a deposited channel region having a doped portion |

| US7145174B2 (en) | 2004-03-12 | 2006-12-05 | Hewlett-Packard Development Company, Lp. | Semiconductor device |

| US7297977B2 (en) | 2004-03-12 | 2007-11-20 | Hewlett-Packard Development Company, L.P. | Semiconductor device |

| US7282782B2 (en) | 2004-03-12 | 2007-10-16 | Hewlett-Packard Development Company, L.P. | Combined binary oxide semiconductor device |

| JP4620046B2 (ja) | 2004-03-12 | 2011-01-26 | 独立行政法人科学技術振興機構 | 薄膜トランジスタ及びその製造方法 |

| US7211825B2 (en) | 2004-06-14 | 2007-05-01 | Yi-Chi Shih | Indium oxide-based thin film transistors and circuits |

| ITMI20041675A1 (it) * | 2004-08-30 | 2004-11-30 | St Microelectronics Srl | Blocco di commutazione e relativa matrice di commutazione, in particolare per architetture fpga. |

| JP2006100760A (ja) | 2004-09-02 | 2006-04-13 | Casio Comput Co Ltd | 薄膜トランジスタおよびその製造方法 |

| US7285501B2 (en) | 2004-09-17 | 2007-10-23 | Hewlett-Packard Development Company, L.P. | Method of forming a solution processed device |

| US7129747B1 (en) * | 2004-10-15 | 2006-10-31 | Xilinx, Inc. | CPLD with fast logic sharing between function blocks |

| US7298084B2 (en) | 2004-11-02 | 2007-11-20 | 3M Innovative Properties Company | Methods and displays utilizing integrated zinc oxide row and column drivers in conjunction with organic light emitting diodes |

| US7453065B2 (en) | 2004-11-10 | 2008-11-18 | Canon Kabushiki Kaisha | Sensor and image pickup device |

| US7863611B2 (en) | 2004-11-10 | 2011-01-04 | Canon Kabushiki Kaisha | Integrated circuits utilizing amorphous oxides |

| CA2585063C (en) | 2004-11-10 | 2013-01-15 | Canon Kabushiki Kaisha | Light-emitting device |

| US7791072B2 (en) | 2004-11-10 | 2010-09-07 | Canon Kabushiki Kaisha | Display |

| EP1815530B1 (en) | 2004-11-10 | 2021-02-17 | Canon Kabushiki Kaisha | Field effect transistor employing an amorphous oxide |

| US7829444B2 (en) | 2004-11-10 | 2010-11-09 | Canon Kabushiki Kaisha | Field effect transistor manufacturing method |

| CN102938420B (zh) | 2004-11-10 | 2015-12-02 | 佳能株式会社 | 无定形氧化物和场效应晶体管 |

| US7579224B2 (en) | 2005-01-21 | 2009-08-25 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a thin film semiconductor device |

| US7608531B2 (en) | 2005-01-28 | 2009-10-27 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, electronic device, and method of manufacturing semiconductor device |

| TWI562380B (en) | 2005-01-28 | 2016-12-11 | Semiconductor Energy Lab Co Ltd | Semiconductor device, electronic device, and method of manufacturing semiconductor device |

| US7858451B2 (en) | 2005-02-03 | 2010-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Electronic device, semiconductor device and manufacturing method thereof |

| US7948171B2 (en) | 2005-02-18 | 2011-05-24 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device |

| US20060197092A1 (en) | 2005-03-03 | 2006-09-07 | Randy Hoffman | System and method for forming conductive material on a substrate |

| US8681077B2 (en) | 2005-03-18 | 2014-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, and display device, driving method and electronic apparatus thereof |

| US7544967B2 (en) | 2005-03-28 | 2009-06-09 | Massachusetts Institute Of Technology | Low voltage flexible organic/transparent transistor for selective gas sensing, photodetecting and CMOS device applications |

| US7645478B2 (en) | 2005-03-31 | 2010-01-12 | 3M Innovative Properties Company | Methods of making displays |

| US8300031B2 (en) | 2005-04-20 | 2012-10-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising transistor having gate and drain connected through a current-voltage conversion element |

| JP2006344849A (ja) | 2005-06-10 | 2006-12-21 | Casio Comput Co Ltd | 薄膜トランジスタ |

| US7402506B2 (en) | 2005-06-16 | 2008-07-22 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7691666B2 (en) | 2005-06-16 | 2010-04-06 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7507618B2 (en) | 2005-06-27 | 2009-03-24 | 3M Innovative Properties Company | Method for making electronic devices using metal oxide nanoparticles |

| KR100711890B1 (ko) | 2005-07-28 | 2007-04-25 | 삼성에스디아이 주식회사 | 유기 발광표시장치 및 그의 제조방법 |

| JP2007059128A (ja) | 2005-08-23 | 2007-03-08 | Canon Inc | 有機el表示装置およびその製造方法 |

| JP5116225B2 (ja) | 2005-09-06 | 2013-01-09 | キヤノン株式会社 | 酸化物半導体デバイスの製造方法 |

| JP2007073705A (ja) | 2005-09-06 | 2007-03-22 | Canon Inc | 酸化物半導体チャネル薄膜トランジスタおよびその製造方法 |

| JP4850457B2 (ja) | 2005-09-06 | 2012-01-11 | キヤノン株式会社 | 薄膜トランジスタ及び薄膜ダイオード |

| JP4280736B2 (ja) | 2005-09-06 | 2009-06-17 | キヤノン株式会社 | 半導体素子 |

| EP1995787A3 (en) | 2005-09-29 | 2012-01-18 | Semiconductor Energy Laboratory Co, Ltd. | Semiconductor device having oxide semiconductor layer and manufacturing method therof |

| JP5037808B2 (ja) | 2005-10-20 | 2012-10-03 | キヤノン株式会社 | アモルファス酸化物を用いた電界効果型トランジスタ、及び該トランジスタを用いた表示装置 |

| CN101577282A (zh) | 2005-11-15 | 2009-11-11 | 株式会社半导体能源研究所 | 半导体器件及其制造方法 |

| TWI292281B (en) | 2005-12-29 | 2008-01-01 | Ind Tech Res Inst | Pixel structure of active organic light emitting diode and method of fabricating the same |

| US7867636B2 (en) | 2006-01-11 | 2011-01-11 | Murata Manufacturing Co., Ltd. | Transparent conductive film and method for manufacturing the same |

| JP4977478B2 (ja) | 2006-01-21 | 2012-07-18 | 三星電子株式会社 | ZnOフィルム及びこれを用いたTFTの製造方法 |

| US7576394B2 (en) | 2006-02-02 | 2009-08-18 | Kochi Industrial Promotion Center | Thin film transistor including low resistance conductive thin films and manufacturing method thereof |

| US7977169B2 (en) | 2006-02-15 | 2011-07-12 | Kochi Industrial Promotion Center | Semiconductor device including active layer made of zinc oxide with controlled orientations and manufacturing method thereof |

| KR20070101595A (ko) | 2006-04-11 | 2007-10-17 | 삼성전자주식회사 | ZnO TFT |

| US20070252928A1 (en) | 2006-04-28 | 2007-11-01 | Toppan Printing Co., Ltd. | Structure, transmission type liquid crystal display, reflection type display and manufacturing method thereof |

| JP5028033B2 (ja) | 2006-06-13 | 2012-09-19 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4999400B2 (ja) | 2006-08-09 | 2012-08-15 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4609797B2 (ja) | 2006-08-09 | 2011-01-12 | Nec液晶テクノロジー株式会社 | 薄膜デバイス及びその製造方法 |

| JP4332545B2 (ja) | 2006-09-15 | 2009-09-16 | キヤノン株式会社 | 電界効果型トランジスタ及びその製造方法 |

| JP5164357B2 (ja) | 2006-09-27 | 2013-03-21 | キヤノン株式会社 | 半導体装置及び半導体装置の製造方法 |

| JP4274219B2 (ja) | 2006-09-27 | 2009-06-03 | セイコーエプソン株式会社 | 電子デバイス、有機エレクトロルミネッセンス装置、有機薄膜半導体装置 |

| US7622371B2 (en) | 2006-10-10 | 2009-11-24 | Hewlett-Packard Development Company, L.P. | Fused nanocrystal thin film semiconductor and method |

| US7772021B2 (en) | 2006-11-29 | 2010-08-10 | Samsung Electronics Co., Ltd. | Flat panel displays comprising a thin-film transistor having a semiconductive oxide in its channel and methods of fabricating the same for use in flat panel displays |

| JP2008140684A (ja) | 2006-12-04 | 2008-06-19 | Toppan Printing Co Ltd | カラーelディスプレイおよびその製造方法 |

| KR101303578B1 (ko) | 2007-01-05 | 2013-09-09 | 삼성전자주식회사 | 박막 식각 방법 |

| US8207063B2 (en) | 2007-01-26 | 2012-06-26 | Eastman Kodak Company | Process for atomic layer deposition |

| KR100851215B1 (ko) | 2007-03-14 | 2008-08-07 | 삼성에스디아이 주식회사 | 박막 트랜지스터 및 이를 이용한 유기 전계 발광표시장치 |

| US7795613B2 (en) | 2007-04-17 | 2010-09-14 | Toppan Printing Co., Ltd. | Structure with transistor |

| KR101325053B1 (ko) | 2007-04-18 | 2013-11-05 | 삼성디스플레이 주식회사 | 박막 트랜지스터 기판 및 이의 제조 방법 |

| KR20080094300A (ko) | 2007-04-19 | 2008-10-23 | 삼성전자주식회사 | 박막 트랜지스터 및 그 제조 방법과 박막 트랜지스터를포함하는 평판 디스플레이 |

| KR101334181B1 (ko) | 2007-04-20 | 2013-11-28 | 삼성전자주식회사 | 선택적으로 결정화된 채널층을 갖는 박막 트랜지스터 및 그제조 방법 |

| WO2008133345A1 (en) | 2007-04-25 | 2008-11-06 | Canon Kabushiki Kaisha | Oxynitride semiconductor |

| KR101345376B1 (ko) | 2007-05-29 | 2013-12-24 | 삼성전자주식회사 | ZnO 계 박막 트랜지스터 및 그 제조방법 |

| US8202365B2 (en) | 2007-12-17 | 2012-06-19 | Fujifilm Corporation | Process for producing oriented inorganic crystalline film, and semiconductor device using the oriented inorganic crystalline film |

| JP4623179B2 (ja) | 2008-09-18 | 2011-02-02 | ソニー株式会社 | 薄膜トランジスタおよびその製造方法 |

| JP5451280B2 (ja) | 2008-10-09 | 2014-03-26 | キヤノン株式会社 | ウルツ鉱型結晶成長用基板およびその製造方法ならびに半導体装置 |

| KR20240042253A (ko) | 2009-10-29 | 2024-04-01 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| SG182272A1 (en) | 2010-01-20 | 2012-08-30 | Semiconductor Energy Lab | Semiconductor device |

| TWI571058B (zh) | 2011-05-18 | 2017-02-11 | 半導體能源研究所股份有限公司 | 半導體裝置與驅動半導體裝置之方法 |

| JP5820336B2 (ja) | 2011-05-20 | 2015-11-24 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US9654107B2 (en) * | 2012-04-27 | 2017-05-16 | Semiconductor Energy Laboratory Co., Ltd. | Programmable LSI |

| SG10201608665WA (en) * | 2012-05-02 | 2016-12-29 | Semiconductor Energy Lab Co Ltd | Programmable logic device |

| WO2013176199A1 (en) | 2012-05-25 | 2013-11-28 | Semiconductor Energy Laboratory Co., Ltd. | Programmable logic device and semiconductor device |

| JP6377317B2 (ja) | 2012-05-30 | 2018-08-22 | 株式会社半導体エネルギー研究所 | プログラマブルロジックデバイス |

| KR102107591B1 (ko) * | 2012-07-18 | 2020-05-07 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 기억 소자 및 프로그래머블 로직 디바이스 |

| TWI591966B (zh) | 2012-10-17 | 2017-07-11 | 半導體能源研究所股份有限公司 | 可編程邏輯裝置及可編程邏輯裝置的驅動方法 |

| JP6254834B2 (ja) | 2012-12-06 | 2017-12-27 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| TWI611419B (zh) | 2012-12-24 | 2018-01-11 | 半導體能源研究所股份有限公司 | 可程式邏輯裝置及半導體裝置 |

| US8952723B2 (en) | 2013-02-13 | 2015-02-10 | Semiconductor Energy Laboratory Co., Ltd. | Programmable logic device and semiconductor device |

| JP6272713B2 (ja) * | 2013-03-25 | 2018-01-31 | 株式会社半導体エネルギー研究所 | プログラマブルロジックデバイス及び半導体装置 |

| TW201513128A (zh) | 2013-07-05 | 2015-04-01 | Semiconductor Energy Lab | 半導體裝置 |

| JP6625328B2 (ja) * | 2014-03-06 | 2019-12-25 | 株式会社半導体エネルギー研究所 | 半導体装置の駆動方法 |

-

2015

- 2015-03-09 JP JP2015045474A patent/JP6677449B2/ja active Active

- 2015-03-10 US US14/643,288 patent/US9385720B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20150263734A1 (en) | 2015-09-17 |

| US9385720B2 (en) | 2016-07-05 |

| JP2015188213A (ja) | 2015-10-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6445243B2 (ja) | 半導体装置 | |

| US9761736B2 (en) | Semiconductor device and method for manufacturing semiconductor device | |

| JP6661280B2 (ja) | 記憶装置、及び半導体装置 | |

| JP6625328B2 (ja) | 半導体装置の駆動方法 | |

| US9312349B2 (en) | Semiconductor device and method for manufacturing semiconductor device | |

| US9722615B2 (en) | Method for operating programmable logic device | |

| JP6498932B2 (ja) | 半導体装置 | |

| JP7384983B2 (ja) | 半導体装置 | |

| JP6677449B2 (ja) | 半導体装置の駆動方法 | |

| US9419622B2 (en) | Semiconductor device | |

| JP6298657B2 (ja) | 半導体装置 | |

| JP2014176041A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180306 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20180306 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20181031 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20181106 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20181226 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190228 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190723 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190920 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20200225 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20200313 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6677449 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |