JP5836024B2 - 駆動回路及び表示装置 - Google Patents

駆動回路及び表示装置 Download PDFInfo

- Publication number

- JP5836024B2 JP5836024B2 JP2011193730A JP2011193730A JP5836024B2 JP 5836024 B2 JP5836024 B2 JP 5836024B2 JP 2011193730 A JP2011193730 A JP 2011193730A JP 2011193730 A JP2011193730 A JP 2011193730A JP 5836024 B2 JP5836024 B2 JP 5836024B2

- Authority

- JP

- Japan

- Prior art keywords

- node

- transistor

- clock signal

- potential

- period

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000010586 diagram Methods 0.000 description 10

- 239000004973 liquid crystal related substance Substances 0.000 description 9

- 239000000758 substrate Substances 0.000 description 9

- 239000003990 capacitor Substances 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 230000001960 triggered effect Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3674—Details of drivers for scan electrodes

- G09G3/3677—Details of drivers for scan electrodes suitable for active matrices only

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0281—Arrangement of scan or data electrode driver circuits at the periphery of a panel not inherent to a split matrix structure

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Liquid Crystal Display Device Control (AREA)

- Control Of El Displays (AREA)

- Liquid Crystal (AREA)

- Shift Register Type Memory (AREA)

Description

図1には、本発明の一実施形態に係る表示装置100が概略的に示されている。この図に示されるように、表示装置100は、上フレーム110及び下フレーム120に挟まれるように固定された表示パネル200等から構成されている。なお、本実施形態では、表示パネル200は液晶表示パネルであることとする。

本発明の第2実施形態について説明する。第2実施形態に係る表示装置の構成は、第1実施形態の図1及び図2に示される構成と同様であるため、重複する説明を省略する。図6には、第2実施形態の表示装置に係る出力回路320の構成が示されている。第1実施形態における出力回路310と異なる点は、トランジスタT3に入力される信号が、クロック信号Vn+4ではなく、走査信号線Gn+4の出力を入力している点である。

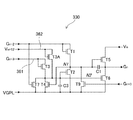

本発明の第3実施形態について説明する。第3実施形態に係る表示装置の構成は、第1実施形態の図1及び図2に示される構成と同様であるため、重複する説明を省略する。図8には、第3実施形態の表示装置に係る出力回路330の構成が示されている。第2実施形態における出力回路320と異なる点は、第1充電線361及びトランジスタT9のゲートに入力される信号が、走査信号線Gn+4の出力ではなく、走査信号線Gn+3の出力となっている点である。

第4実施形態に係る表示装置の構成は、第1実施形態の図1及び図2に示される構成と同様であるため、重複する説明を省略する。図10には、第4実施形態の表示装置に係る出力回路410の構成が示されている。また、図11には、出力回路410を用いた場合の動作のタイミングチャートが示されている。第1実施形態における出力回路310と異なる点は、ダイオード接続されたトランジスタT3Aを用いておらず、トランジスタT3には、8相のクロック信号Vm+2を入力している点である。このようにした場合であっても、図12に示されるように、ノードN2のHigh電位を維持することができるため、駆動回路はより安定的な走査信号を出力することができ、表示装置の表示品質を高めることができる。

Claims (4)

- 複数の走査信号線に対してトランジスタを導通させる電位であるアクティブ電位を順に出力する表示装置の駆動回路であって、

前記複数の走査信号線に、それぞれ電気的に接続された複数の出力回路を備え、

前記複数の出力回路は、

n番目(nは奇数または偶数)の前記走査信号線に前記アクティブ電位を出力するn番目の出力回路と、

(n−2)番目の前記走査信号線に前記アクティブ電位を出力する(n−2)番目の出力回路とを有し、

前記複数の出力回路のうち、一の出力回路は、

前記複数の走査信号線のうちの一の走査信号線とクロック信号線との電気的接続を制御する第1トランジスタと、

前記第1トランジスタのゲートに接続され、前記走査信号線に前記アクティブ電位が出力される期間を含む期間である第1期間にアクティブ電位となる第1ノードと、

トランジスタを導通させない電位である非アクティブ電位を保持する非アクティブ信号線と前記第1ノードとを、前記第1期間以外の期間である第2期間において電気的に接続するように制御する第2トランジスタと、

前記第2トランジスタのゲートに接続された第2ノードと、

前記非アクティブ信号線と前記第2ノードとを前記第1期間において電気的に接続する第3トランジスタと、を有し、

前記n番目の出力回路についての前記第1期間は、

前記(n−2)番目の出力回路が出力するアクティブ電位により、前記n番目の出力回路の前記第1ノードがアクティブ電位となると共に、前記第3トランジスタが導通して前記第2ノードが非アクティブ電位となることで開始し、

前記第2トランジスタが導通して前記第1のノードが非アクティブ電位となることで終了し、

前記第2ノードは、アクティブ電位を保持するために第1充電期間と第2充電期間とに充電され、

前記クロック信号線は第1クロック信号を供給し、

前記第2ノードに接続される第1充電線は第2クロック信号を供給し、

前記第2ノードに接続される第2充電線は第3クロック信号を供給し、

前記第1、第2、第3のクロック信号はそれぞれ8相のクロックのいずれかであり、前記第1、第2、第3のクロック信号は同一周期でありかつ位相が互いに異なり、

前記第2のクロック信号は前記第1充電期間に前記第2ノードを充電し、

前記第3のクロック信号は前記第2充電期間に前記第2ノードを充電する、

ことを特徴とする駆動回路。 - 請求項1に記載の駆動回路であって、

前記第2ノードのアクティブ電位を保持するために、

前記第1充電線は整流作用のある素子を介して前記第2ノードに接続され、

前記第2充電線は整流作用のある素子を介して前記第2ノードに接続される、ことを特徴とする駆動回路。 - 請求項1に記載の駆動回路であって、

前記第1クロック信号または前記第2クロック信号は、前記第1トランジスタに接続された前記クロック信号線に入力されるクロック信号がアクティブ電圧となるタイミングの前2分の1周期の間にアクティブ電圧となるクロック信号である、ことを特徴とする駆動回路。 - 画面に複数の画素を有する表示装置であって、

請求項1乃至3のいずれか一項に記載の駆動回路と、

前記複数の画素のそれぞれに配置され、階調値に基づく電圧を前記複数の画素の各々に保持するための画素トランジスタと、を備え、

前記駆動回路の走査信号線は、前記画面の一行分の前記画素の前記画素トランジスタのゲートに接続されている、ことを特徴とする表示装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011193730A JP5836024B2 (ja) | 2011-09-06 | 2011-09-06 | 駆動回路及び表示装置 |

| CN201210336321.XA CN102982774B (zh) | 2011-09-06 | 2012-09-05 | 驱动电路和显示装置 |

| US13/604,775 US8947338B2 (en) | 2011-09-06 | 2012-09-06 | Driving circuit and display device using multiple phase clock signals |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011193730A JP5836024B2 (ja) | 2011-09-06 | 2011-09-06 | 駆動回路及び表示装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2013054272A JP2013054272A (ja) | 2013-03-21 |

| JP2013054272A5 JP2013054272A5 (ja) | 2014-10-23 |

| JP5836024B2 true JP5836024B2 (ja) | 2015-12-24 |

Family

ID=47752780

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011193730A Active JP5836024B2 (ja) | 2011-09-06 | 2011-09-06 | 駆動回路及び表示装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8947338B2 (ja) |

| JP (1) | JP5836024B2 (ja) |

| CN (1) | CN102982774B (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103761949B (zh) * | 2013-12-31 | 2016-02-24 | 深圳市华星光电技术有限公司 | 栅极驱动电路以及驱动方法 |

| EP3951756A4 (en) * | 2019-03-28 | 2023-03-29 | BOE Technology Group Co., Ltd. | GRID DRIVER UNIT AND METHOD, GRID DRIVER CIRCUIT, DISPLAY BOARD AND DEVICE |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5859630A (en) * | 1996-12-09 | 1999-01-12 | Thomson Multimedia S.A. | Bi-directional shift register |

| KR101012972B1 (ko) * | 2003-12-30 | 2011-02-10 | 엘지디스플레이 주식회사 | 액티브 매트릭스 표시장치 |

| KR101056375B1 (ko) * | 2004-10-01 | 2011-08-11 | 삼성전자주식회사 | 쉬프트 레지스터와, 이를 이용한 게이트 구동 회로 및표시 패널 |

| KR101110133B1 (ko) * | 2004-12-28 | 2012-02-20 | 엘지디스플레이 주식회사 | 액정표시장치 게이트 구동용 쉬프트레지스터 |

| KR101066493B1 (ko) * | 2004-12-31 | 2011-09-21 | 엘지디스플레이 주식회사 | 쉬프트 레지스터 |

| KR101107703B1 (ko) * | 2005-05-26 | 2012-01-25 | 엘지디스플레이 주식회사 | 쉬프트 레지스터 |

| JP4644087B2 (ja) | 2005-09-29 | 2011-03-02 | 株式会社 日立ディスプレイズ | シフトレジスタ回路及びそれを用いた表示装置 |

| TWI511116B (zh) * | 2006-10-17 | 2015-12-01 | Semiconductor Energy Lab | 脈衝輸出電路、移位暫存器及顯示裝置 |

| BRPI0923245A2 (pt) * | 2008-12-10 | 2019-09-24 | Sharp Kk | circuito de excitacao de linha de sinal de varredura, registrador de deslocamente e metodo de excitacao de registrador de deslocamento |

| TWI410944B (zh) * | 2009-06-10 | 2013-10-01 | Au Optronics Corp | 顯示裝置之移位暫存器 |

| JP5719103B2 (ja) * | 2009-06-26 | 2015-05-13 | 株式会社ジャパンディスプレイ | 表示装置 |

| JP5404807B2 (ja) * | 2009-11-04 | 2014-02-05 | シャープ株式会社 | シフトレジスタならびにそれを備えた走査信号線駆動回路および表示装置 |

| JP5356208B2 (ja) * | 2009-12-25 | 2013-12-04 | 株式会社ジャパンディスプレイ | ゲート信号線駆動回路及び表示装置 |

| KR101308474B1 (ko) * | 2010-04-19 | 2013-09-16 | 엘지디스플레이 주식회사 | 쉬프트 레지스터 |

| JP5191522B2 (ja) * | 2010-10-29 | 2013-05-08 | 三菱電機株式会社 | シフトレジスタ回路 |

-

2011

- 2011-09-06 JP JP2011193730A patent/JP5836024B2/ja active Active

-

2012

- 2012-09-05 CN CN201210336321.XA patent/CN102982774B/zh active Active

- 2012-09-06 US US13/604,775 patent/US8947338B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US8947338B2 (en) | 2015-02-03 |

| CN102982774A (zh) | 2013-03-20 |

| US20130057525A1 (en) | 2013-03-07 |

| JP2013054272A (ja) | 2013-03-21 |

| CN102982774B (zh) | 2015-01-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7315469B2 (ja) | シフトレジスタユニットおよびその駆動方法、ゲート駆動回路および表示装置 | |

| JP4713246B2 (ja) | 液晶表示素子 | |

| US10283038B2 (en) | Shift register unit and method for driving the same, gate drive circuit and display device | |

| JP5774911B2 (ja) | 表示装置 | |

| US10950322B2 (en) | Shift register unit circuit, method of driving the same, gate drive circuit, and display apparatus | |

| US10453417B2 (en) | Driver circuit | |

| JP6009153B2 (ja) | 表示装置 | |

| CN112634812B (zh) | 显示面板和显示装置 | |

| US9886928B2 (en) | Gate signal line drive circuit | |

| JP5538765B2 (ja) | 液晶表示装置 | |

| JP2014142457A (ja) | 表示装置 | |

| JP5427495B2 (ja) | ゲート信号線駆動回路及び表示装置 | |

| JP5836024B2 (ja) | 駆動回路及び表示装置 | |

| US20100265243A1 (en) | Gate signal line driving circuit and dislay device | |

| KR20200089328A (ko) | 액정 표시 패널 및 그 eoa 모듈 | |

| JP2012225999A (ja) | 表示装置 | |

| KR102029749B1 (ko) | 게이트 구동부 및 이를 포함하는 평판표시장치 | |

| JP2014107001A (ja) | シフトレジスタ回路および画像表示装置 | |

| KR20140091399A (ko) | 액정표시장치 및 이의 구동회로 | |

| KR20160141346A (ko) | 게이트 드라이버 및 이를 포함하는 액정표시장치 | |

| JP2011232697A (ja) | 液晶表示装置 | |

| JP5342401B2 (ja) | 駆動回路及び表示装置 | |

| JP2011085663A (ja) | 駆動回路及び表示装置 | |

| JP4591664B2 (ja) | 液晶表示装置 | |

| JP2010117599A (ja) | 電気光学装置及び電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140905 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140905 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20150624 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150630 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150827 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20151006 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20151102 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5836024 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |