JP4301227B2 - 電気光学装置及びその製造方法、電子機器並びにコンデンサー - Google Patents

電気光学装置及びその製造方法、電子機器並びにコンデンサー Download PDFInfo

- Publication number

- JP4301227B2 JP4301227B2 JP2005268606A JP2005268606A JP4301227B2 JP 4301227 B2 JP4301227 B2 JP 4301227B2 JP 2005268606 A JP2005268606 A JP 2005268606A JP 2005268606 A JP2005268606 A JP 2005268606A JP 4301227 B2 JP4301227 B2 JP 4301227B2

- Authority

- JP

- Japan

- Prior art keywords

- pixel

- electrode

- contact hole

- capacitor

- film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136213—Storage capacitors associated with the pixel electrode

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136227—Through-hole connection of the pixel electrode to the active element through an insulation layer

Landscapes

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Mathematical Physics (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- General Physics & Mathematics (AREA)

- Optics & Photonics (AREA)

- Power Engineering (AREA)

- Liquid Crystal (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Description

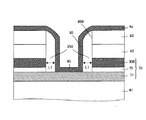

<第1実施形態>

第1実施形態に係る液晶装置について、図1から図8を参照して説明する。

<第2実施形態>

第2実施形態に係る電気光学装置について、図9及び図10を参照して説明する。ここに図9は、第2実施形態における図5と同趣旨の断面図であり、図10は、図9の破線円C2内を拡大して示す部分拡大図である。

<電子機器>

次に、上述した電気光学装置である液晶装置を各種の電子機器に適用する場合について説明する。

Claims (2)

- 基板上に、

相互に交差する複数の走査線及び複数のデータ線と、

前記複数の走査線と前記複数のデータ線との交差に対応して設けられた複数の画素電極と、

前記画素電極をスイッチング制御するための薄膜トランジスタと、

前記薄膜トランジスタより上層側に配置され、(i)一定電位に電気的に接続された固定電位側電極、(ii)誘電体膜及び(iii)前記画素電極に電気的に接続された画素電位側電極がこの順に積層されてなる蓄積容量と、

前記固定電位側電極及び前記誘電体膜を貫通して開口された開口部の内側壁上に設けられた第1の絶縁膜からなるサイドウォールと

を備え、

前記薄膜トランジスタを構成する半導体層と前記画素電位側電極とは、前記サイドウォールと同時に自己整合的に形成され前記サイドウォールに囲まれたセルフアラインコンタクトホールを介して互いに電気的に接続される

ことを特徴とする電気光学装置。 - 請求項1に記載の電気光学装置を具備してなる電子機器。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005268606A JP4301227B2 (ja) | 2005-09-15 | 2005-09-15 | 電気光学装置及びその製造方法、電子機器並びにコンデンサー |

| US11/482,425 US7561220B2 (en) | 2005-09-15 | 2006-07-07 | Electro-optical device and manufacturing method thereof, electronic apparatus, and capacitor |

| CNB2006101538784A CN100477237C (zh) | 2005-09-15 | 2006-09-14 | 电光装置、其制造方法、电子设备以及电容器 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005268606A JP4301227B2 (ja) | 2005-09-15 | 2005-09-15 | 電気光学装置及びその製造方法、電子機器並びにコンデンサー |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2007079257A JP2007079257A (ja) | 2007-03-29 |

| JP4301227B2 true JP4301227B2 (ja) | 2009-07-22 |

Family

ID=37854679

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005268606A Expired - Fee Related JP4301227B2 (ja) | 2005-09-15 | 2005-09-15 | 電気光学装置及びその製造方法、電子機器並びにコンデンサー |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7561220B2 (ja) |

| JP (1) | JP4301227B2 (ja) |

| CN (1) | CN100477237C (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4155317B2 (ja) * | 2006-07-11 | 2008-09-24 | セイコーエプソン株式会社 | 電気光学装置、及びこれを備えた電子機器 |

| US8284354B2 (en) * | 2008-02-04 | 2012-10-09 | Himax Display, Inc. | Liquid crystal on silicon display panel and electronic device using the same |

| CN101620347B (zh) * | 2008-07-03 | 2011-08-17 | 中芯国际集成电路制造(上海)有限公司 | 硅基液晶器件及其制造方法 |

| JP5724531B2 (ja) * | 2010-04-12 | 2015-05-27 | セイコーエプソン株式会社 | 電気光学装置及び電子機器 |

| JP2013195992A (ja) * | 2012-03-23 | 2013-09-30 | Japan Display Inc | 液晶表示装置およびその製造方法 |

| CN104020892B (zh) | 2014-05-30 | 2017-07-28 | 京东方科技集团股份有限公司 | 一种内嵌式触摸屏及显示装置 |

| CN105470267A (zh) * | 2016-01-11 | 2016-04-06 | 武汉华星光电技术有限公司 | 一种阵列基板及其制备方法 |

| JP6768394B2 (ja) * | 2016-07-29 | 2020-10-14 | 株式会社ジャパンディスプレイ | 電子機器 |

Family Cites Families (82)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4378630A (en) * | 1980-05-05 | 1983-04-05 | International Business Machines Corporation | Process for fabricating a high performance PNP and NPN structure |

| US4433470A (en) * | 1981-05-19 | 1984-02-28 | Tokyo Shibaura Denki Kabushiki Kaisha | Method for manufacturing semiconductor device utilizing selective etching and diffusion |

| US4826781A (en) * | 1986-03-04 | 1989-05-02 | Seiko Epson Corporation | Semiconductor device and method of preparation |

| JPS62274659A (ja) * | 1986-05-22 | 1987-11-28 | Mitsubishi Electric Corp | 半導体装置 |

| US4772569A (en) * | 1986-10-30 | 1988-09-20 | Mitsubishi Denki Kabushiki Kaisha | Method for forming oxide isolation films on french sidewalls |

| US4855953A (en) * | 1987-02-25 | 1989-08-08 | Mitsubishi Denki Kabushiki Kaisha | Semiconductor memory device having stacked memory capacitors and method for manufacturing the same |

| DE3809218C2 (de) * | 1987-03-20 | 1994-09-01 | Mitsubishi Electric Corp | Halbleitereinrichtung mit einem Graben und Verfahren zum Herstellen einer solchen Halbleitereinrichtung |

| JPH0620108B2 (ja) * | 1987-03-23 | 1994-03-16 | 三菱電機株式会社 | 半導体装置の製造方法 |

| JPH01143254A (ja) * | 1987-11-28 | 1989-06-05 | Mitsubishi Electric Corp | 半導体記憶装置 |

| US4849279A (en) * | 1988-02-22 | 1989-07-18 | Nissho & Co., Ltd. | Insect-repellent assembly |

| JP2682021B2 (ja) * | 1988-06-29 | 1997-11-26 | 富士通株式会社 | 半導体メモリ装置 |

| JPH0262073A (ja) * | 1988-08-26 | 1990-03-01 | Mitsubishi Electric Corp | 半導体記憶装置 |

| JP2624797B2 (ja) * | 1988-09-20 | 1997-06-25 | 株式会社日立製作所 | アクティブマトリクス基板の製造方法 |

| US5086322A (en) * | 1988-10-19 | 1992-02-04 | Mitsubishi Denki Kabushiki Kaisha | Input protection circuit and output driver circuit comprising mis semiconductor device |

| DE69030433T2 (de) * | 1989-12-29 | 1997-10-09 | Sharp Kk | Herstellungsmethode für Halbleiterspeicher |

| JP2573384B2 (ja) * | 1990-01-24 | 1997-01-22 | 株式会社東芝 | 半導体記憶装置とその製造方法 |

| JPH03278573A (ja) * | 1990-03-28 | 1991-12-10 | Mitsubishi Electric Corp | 半導体記憶装置 |

| JPH04188869A (ja) * | 1990-11-22 | 1992-07-07 | Mitsubishi Electric Corp | 接合型電界効果トランジスタとキャパシタとを含む半導体記憶装置およびその製造方法 |

| KR960001611B1 (ko) * | 1991-03-06 | 1996-02-02 | 가부시끼가이샤 한도다이 에네르기 겐뀨쇼 | 절연 게이트형 전계 효과 반도체 장치 및 그 제작방법 |

| US5053351A (en) * | 1991-03-19 | 1991-10-01 | Micron Technology, Inc. | Method of making stacked E-cell capacitor DRAM cell |

| JP2794499B2 (ja) * | 1991-03-26 | 1998-09-03 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JPH04348070A (ja) * | 1991-05-24 | 1992-12-03 | Texas Instr Japan Ltd | 半導体装置及びその製造方法 |

| US6778231B1 (en) * | 1991-06-14 | 2004-08-17 | Semiconductor Energy Laboratory Co., Ltd. | Electro-optical display device |

| US5334540A (en) * | 1991-11-14 | 1994-08-02 | Mitsubishi Denki Kabushiki Kaisha | OBIC observation method and apparatus therefor |

| JPH05340964A (ja) * | 1992-06-05 | 1993-12-24 | Mitsubishi Electric Corp | ウエハ及びチップの試験装置 |

| JP3435173B2 (ja) * | 1992-07-10 | 2003-08-11 | 株式会社日立製作所 | 半導体装置 |

| JPH0637269A (ja) * | 1992-07-17 | 1994-02-10 | Mitsubishi Electric Corp | 接合型電界効果トランジスタ、その接合型電界効果トランジスタを含む半導体記憶装置およびそれらの製造方法 |

| US5508541A (en) * | 1992-09-22 | 1996-04-16 | Kabushiki Kaisha Toshiba | Random access memory device with trench-type one-transistor memory cell structure |

| JPH0714898A (ja) * | 1993-06-23 | 1995-01-17 | Mitsubishi Electric Corp | 半導体ウエハの試験解析装置および解析方法 |

| JPH0737996A (ja) * | 1993-07-26 | 1995-02-07 | Mitsubishi Electric Corp | メモリセルにトランジスタを用いない半導体記憶装置およびその製造方法 |

| JP2974561B2 (ja) * | 1993-11-08 | 1999-11-10 | 株式会社東芝 | 半導体記憶装置及びその製造方法 |

| US6265249B1 (en) * | 1994-03-01 | 2001-07-24 | Industrial Technology Research Institute | Method of manufacturing thin film transistors |

| JPH07312423A (ja) * | 1994-05-17 | 1995-11-28 | Hitachi Ltd | Mis型半導体装置 |

| JPH08316430A (ja) * | 1995-05-15 | 1996-11-29 | Mitsubishi Electric Corp | 半導体メモリとその製造方法、スタックドキャパシタ |

| KR0147655B1 (ko) * | 1995-07-13 | 1998-08-01 | 김광호 | 반도체 장치의 캐패시터 제조방법 |

| US5747845A (en) * | 1995-08-22 | 1998-05-05 | Nippon Steel Corporation | Semiconductor memory device with memory cells each having transistor and capacitor and method of making the same |

| JPH09105952A (ja) * | 1995-10-11 | 1997-04-22 | Toshiba Electron Eng Corp | アクティブマトリクス型液晶表示装置 |

| JPH09127551A (ja) * | 1995-10-31 | 1997-05-16 | Sharp Corp | 半導体装置およびアクティブマトリクス基板 |

| US5914851A (en) * | 1995-12-22 | 1999-06-22 | International Business Machines Corporation | Isolated sidewall capacitor |

| US5633781A (en) * | 1995-12-22 | 1997-05-27 | International Business Machines Corporation | Isolated sidewall capacitor having a compound plate electrode |

| JP3976839B2 (ja) * | 1996-07-09 | 2007-09-19 | 株式会社ルネサステクノロジ | 不揮発性メモリシステムおよび不揮発性半導体メモリ |

| US6009016A (en) * | 1996-07-09 | 1999-12-28 | Hitachi, Ltd. | Nonvolatile memory system semiconductor memory and writing method |

| US5990507A (en) * | 1996-07-09 | 1999-11-23 | Kabushiki Kaisha Toshiba | Semiconductor device having ferroelectric capacitor structures |

| US6429473B1 (en) * | 1996-07-30 | 2002-08-06 | International Business Machines Corporation | DRAM cell with stacked capacitor self-aligned to bitline |

| US6262438B1 (en) * | 1996-11-04 | 2001-07-17 | Semiconductor Energy Laboratory Co., Ltd. | Active matrix type display circuit and method of manufacturing the same |

| KR100223832B1 (ko) * | 1996-12-27 | 1999-10-15 | 구본준 | 반도체 소자 및 그 제조방법 |

| JP3270821B2 (ja) * | 1997-03-12 | 2002-04-02 | シャープ株式会社 | 反射型液晶表示装置およびその製造方法 |

| TW407234B (en) * | 1997-03-31 | 2000-10-01 | Hitachi Ltd | Semiconductor memory device, non-volatile semiconductor memory device and data reading method thereof |

| JPH1116909A (ja) | 1997-06-24 | 1999-01-22 | Seiko Epson Corp | 半導体装置及びその製造方法 |

| KR100438346B1 (ko) * | 1997-07-25 | 2004-07-02 | 가부시키가이샤 오츠까 세이야꾸 고죠 | 환원당이 첨가된 지방유제, 그의 멸균방법 및 그의 포장체 |

| JP2000004269A (ja) * | 1998-06-12 | 2000-01-07 | Nec Corp | 受信装置および受信方法、並びに記録媒体 |

| US6767789B1 (en) * | 1998-06-26 | 2004-07-27 | International Business Machines Corporation | Method for interconnection between transfer devices and storage capacitors in memory cells and device formed thereby |

| JP2000031398A (ja) * | 1998-07-15 | 2000-01-28 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP2000036568A (ja) * | 1998-07-17 | 2000-02-02 | Toshiba Corp | 半導体記憶装置及びその製造方法 |

| JP3289777B2 (ja) * | 1999-04-27 | 2002-06-10 | 日本電気株式会社 | マルチステージ干渉キャンセラ |

| CN101221756A (zh) * | 1999-05-24 | 2008-07-16 | 石井达矢 | 音响发生装置及其制造方法 |

| GB9929615D0 (en) * | 1999-12-15 | 2000-02-09 | Koninkl Philips Electronics Nv | Method of manufacturing an active matrix device |

| JP3379501B2 (ja) * | 1999-12-28 | 2003-02-24 | 日本電気株式会社 | ゲイン可変型ディジタルフィルタ |

| JP4939689B2 (ja) | 2000-01-26 | 2012-05-30 | 株式会社半導体エネルギー研究所 | 半導体装置およびその作製方法 |

| US7262393B2 (en) * | 2000-05-11 | 2007-08-28 | The Procter & Gamble Company | Releasably sealable, air and liquid impermeable bags and methods for low temperature food preparation using the same |

| JP2002026254A (ja) * | 2000-07-03 | 2002-01-25 | Hitachi Ltd | 半導体集積回路および不揮発性メモリ |

| US6429069B1 (en) * | 2000-07-11 | 2002-08-06 | Micron Technology, Inc. | SOI DRAM with buried capacitor under the digit lines utilizing a self aligning penetrating storage node contact formation |

| JP3833887B2 (ja) * | 2000-10-30 | 2006-10-18 | 株式会社東芝 | 強誘電体メモリ及びその製造方法 |

| JP2002354449A (ja) * | 2001-05-28 | 2002-12-06 | Tatsuya Ishii | 広告配信方法及びテレビ放送受信機 |

| JP3809520B2 (ja) * | 2001-07-04 | 2006-08-16 | 独立行政法人 宇宙航空研究開発機構 | 微細噴流制御式吸音システム |

| JP3661633B2 (ja) * | 2001-08-27 | 2005-06-15 | セイコーエプソン株式会社 | 電子ビームテストシステム及び電子ビームテスト方法 |

| JP3633545B2 (ja) * | 2001-11-07 | 2005-03-30 | セイコーエプソン株式会社 | 電子ビームテストシステム及び電子ビームテスト方法 |

| US6858890B2 (en) * | 2002-06-04 | 2005-02-22 | Infineon Technologies Aktiengesellschaft | Ferroelectric memory integrated circuit with improved reliability |

| TWI302996B (en) * | 2002-07-25 | 2008-11-11 | Toppoly Optoelectronics Corp | Method for forming a self-aligned pixel electrode of lcd |

| US7175911B2 (en) * | 2002-09-18 | 2007-02-13 | Toshiba Ceramics Co., Ltd. | Titanium dioxide fine particles and method for producing the same, and method for producing visible light activatable photocatalyst |

| JP4129381B2 (ja) * | 2002-09-25 | 2008-08-06 | 株式会社ルネサステクノロジ | 不揮発性半導体記憶装置 |

| ES2443492T3 (es) * | 2002-10-02 | 2014-02-19 | Mitsubishi Electric Corporation | Reductor de pulsación de presión para un equipo de ciclo de refrigeración |

| TWI221340B (en) * | 2003-05-30 | 2004-09-21 | Ind Tech Res Inst | Thin film transistor and method for fabricating thereof |

| EP1511004A3 (en) * | 2003-08-19 | 2010-01-27 | Sony Corporation | Memory controller, memory control method, rate conversion apparatus, rate conversion method, image-signal-processing apparatus, image-signal-processing method, and program for executing these methods |

| JP3917964B2 (ja) * | 2003-08-22 | 2007-05-23 | 株式会社 工房Pda | 熱圧着用のヒーターチップ |

| JP2004109988A (ja) | 2003-08-29 | 2004-04-08 | Seiko Epson Corp | 電気光学装置及び電子機器 |

| JP4153457B2 (ja) * | 2004-03-30 | 2008-09-24 | 三菱電機株式会社 | 流路装置、冷凍サイクル装置 |

| JP2006086292A (ja) * | 2004-09-15 | 2006-03-30 | Toshiba Corp | 半導体記憶装置およびその製造方法 |

| JP4544413B2 (ja) * | 2004-10-26 | 2010-09-15 | 日本電気株式会社 | 無線基地局及び無線基地局におけるスケジューラアルゴリズム設定方法 |

| US20060217108A1 (en) * | 2005-03-25 | 2006-09-28 | Nec Corporation | Network authentication apparatus, network authentication method, network authentication system, and network authentication program |

| US20070085805A1 (en) * | 2005-10-18 | 2007-04-19 | Seiko Epson Corporation | Electro-optical device and electronic apparatus |

| JP4655943B2 (ja) * | 2006-01-18 | 2011-03-23 | セイコーエプソン株式会社 | 電気光学装置及びその製造方法、並びに導電層の接続構造 |

-

2005

- 2005-09-15 JP JP2005268606A patent/JP4301227B2/ja not_active Expired - Fee Related

-

2006

- 2006-07-07 US US11/482,425 patent/US7561220B2/en not_active Expired - Fee Related

- 2006-09-14 CN CNB2006101538784A patent/CN100477237C/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2007079257A (ja) | 2007-03-29 |

| US20070058100A1 (en) | 2007-03-15 |

| CN1933166A (zh) | 2007-03-21 |

| US7561220B2 (en) | 2009-07-14 |

| CN100477237C (zh) | 2009-04-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4442570B2 (ja) | 電気光学装置及びその製造方法、並びに電子機器 | |

| JP4225347B2 (ja) | 電気光学装置及び電子機器 | |

| JP4211644B2 (ja) | 電気光学装置の製造方法 | |

| JP2009047967A (ja) | 電気光学装置及び電子機器 | |

| JP2004004722A (ja) | 電気光学装置及び電子機器 | |

| US7561220B2 (en) | Electro-optical device and manufacturing method thereof, electronic apparatus, and capacitor | |

| JP3744521B2 (ja) | 電気光学装置及び電子機器 | |

| JP5018336B2 (ja) | 電気光学装置及び電子機器 | |

| JP4655943B2 (ja) | 電気光学装置及びその製造方法、並びに導電層の接続構造 | |

| JP2006276118A (ja) | 電気光学装置及びその製造方法、並びに電子機器 | |

| JP2008003380A (ja) | 電気光学装置及び電子機器 | |

| JP2005285976A (ja) | 半導体装置及びその製造方法、並びにこれを備えた電気光学装置及び電子機器 | |

| JP2010008635A (ja) | 電気光学装置用基板の製造方法、電気光学装置用基板、電気光学装置及び電子機器 | |

| JP4984911B2 (ja) | 電気光学装置及び電子機器 | |

| JP5343476B2 (ja) | 電気光学装置及び電子機器 | |

| JP4259528B2 (ja) | 電気光学装置及びこれを備えた電子機器 | |

| KR100830381B1 (ko) | 전기 광학 장치와 그 제조 방법, 전자 기기, 및 콘덴서 | |

| JP2011221119A (ja) | 電気光学装置及び電子機器、並びに電気光学装置の製造方法 | |

| JP5176852B2 (ja) | 電気光学装置及び電子機器 | |

| JP2008205248A (ja) | 半導体装置及びその製造方法、電気光学装置及びその製造方法、並びに電子機器 | |

| JP2007304352A (ja) | 電気光学装置用基板及び電気光学装置、並びに電子機器 | |

| JP2010145820A (ja) | 電気光学装置及びその製造方法並びに電子機器 | |

| JP4797453B2 (ja) | 電気光学装置の製造方法、電気光学装置、及び電子機器、並びに半導体基板の製造方法 | |

| JP2008039794A (ja) | 電気光学装置用基板及び電気光学装置、並びに電子機器 | |

| JP2010060686A (ja) | 電気光学装置及びその製造方法並びに電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080805 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080812 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080919 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090331 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120501 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 4301227 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090413 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130501 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140501 Year of fee payment: 5 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |