JP4105257B2 - 記憶装置および記憶方法 - Google Patents

記憶装置および記憶方法 Download PDFInfo

- Publication number

- JP4105257B2 JP4105257B2 JP20437297A JP20437297A JP4105257B2 JP 4105257 B2 JP4105257 B2 JP 4105257B2 JP 20437297 A JP20437297 A JP 20437297A JP 20437297 A JP20437297 A JP 20437297A JP 4105257 B2 JP4105257 B2 JP 4105257B2

- Authority

- JP

- Japan

- Prior art keywords

- image

- pixel

- pixels

- memory

- input image

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title claims description 34

- 230000015654 memory Effects 0.000 description 166

- 230000000875 corresponding effect Effects 0.000 description 32

- 238000004364 calculation method Methods 0.000 description 22

- 230000000903 blocking effect Effects 0.000 description 21

- 230000003044 adaptive effect Effects 0.000 description 18

- 238000010586 diagram Methods 0.000 description 11

- 230000003111 delayed effect Effects 0.000 description 6

- 230000006978 adaptation Effects 0.000 description 4

- 239000011159 matrix material Substances 0.000 description 4

- 230000000694 effects Effects 0.000 description 2

- 239000000284 extract Substances 0.000 description 2

- 238000013139 quantization Methods 0.000 description 2

- 230000001360 synchronised effect Effects 0.000 description 2

- 230000000295 complement effect Effects 0.000 description 1

- 230000002596 correlated effect Effects 0.000 description 1

- 230000001934 delay Effects 0.000 description 1

- 230000008030 elimination Effects 0.000 description 1

- 238000003379 elimination reaction Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06T—IMAGE DATA PROCESSING OR GENERATION, IN GENERAL

- G06T3/00—Geometric image transformations in the plane of the image

- G06T3/40—Scaling of whole images or parts thereof, e.g. expanding or contracting

Landscapes

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Image Processing (AREA)

- Memory System (AREA)

- Storing Facsimile Image Data (AREA)

- Compression Or Coding Systems Of Tv Signals (AREA)

- Editing Of Facsimile Originals (AREA)

Description

【発明の属する技術分野】

本発明は、記憶装置および記憶方法に関し、特に、例えば、画像を拡大する場合などに用いて好適な記憶装置および記憶方法に関する。

【0002】

【従来の技術】

例えば、高解像度の画像データを、最下位階層または第1階層の画像データとして、それより画素数の少ない第2階層の画像データを形成し、さらに、それより画素数の少ない第3階層の画像データを形成し、以下、同様にして、最上位階層までの画像データを形成する符号化手法がある。このような符号化は、階層符号化と呼ばれ、各階層の画像データは、その階層に対応した解像度(画素数)のモニタで表示される。従って、ユーザ側では、階層符号化された画像データのうち、自身が有するモニタの解像度に対応するものを選択することで、その画像データを視聴することができる。

【0003】

【発明が解決しようとする課題】

ところで、従来の階層符号化は、上述のように、元の画像データを第1階層の画像データとして、それより画素数の少ない上位階層の画像データを形成するだけであった。即ち、従来の階層符号化では、元の画像データの画素数より多い画素数の画像は形成されなかった。

【0004】

しかしながら、階層符号化において、元の画像データの画素数より多い画素数の画像(以下、適宜、多画素数画像)を形成しておくようにすれば、例えば、電子ズームを行うときなどに便利である。

【0005】

即ち、元の画像データの画素数より少ない画素数の画像を用意しておけば、画像の縮小を、即座に行うことができ、多画素数画像を用意しておけば、画像の拡大を、即座に行うことができる。

【0006】

また、一般に、電子ズームにおいて利用頻度が高いのは、画像の拡大または縮小のうちの拡大である。即ち、例えば、伝送されてきた画像や、記録媒体から再生された画像を、ユーザが視聴している場合において、その視聴している画像の一部または全部を拡大することの要請は高い。

【0007】

本発明は、このような状況に鑑みてなされたものであり、例えば、画像の拡大を即座にすることができるようにするものである。

【0008】

【課題を解決するための手段】

請求項1に記載の記憶装置は、少なくとも第1および第2のアドレス信号によってアドレス指定され、入力画像を記憶する第1の記憶手段と、入力画像から、その入力画像を構成する画素数よりも多い画素数で構成される画像である多画素数画像を生成する生成手段と、少なくとも第1および第2のアドレス信号によってアドレス指定され、多画素数画像を記憶する第2の記憶手段と、第1の記憶手段に記憶された入力画像、および第2の記憶手段に記憶された多画素数画像のうちのいずれを読み出すかを指示するフラグに基づいて、第1の記憶手段に記憶された入力画像、または第2の記憶手段に記憶された多画素数画像を出力する出力手段とを備え、生成手段は、入力画像を構成する画素から多画素数画像を構成する画素を生成する複数の画素生成手段であって、生成手段は、入力画像を構成する画素数に対する多画素数画像を構成する画素数に応じた個数の画素生成手段を用いて、多画素数画像を生成することを特徴とする。

【0009】

請求項5に記載の記憶方法は、少なくとも第1および第2のアドレス信号によってアドレス指定される第1の記憶手段に、入力画像を記憶させる第1の記憶ステップと、入力画像から、その入力画像を構成する画素数よりも多い画素数で構成される画像である多画素数画像を生成する生成ステップと、少なくとも第1および第2のアドレス信号によってアドレス指定される第2の記憶手段に、多画素数画像を記憶させる第2の記憶ステップと、第1の記憶手段に記憶された入力画像、および第2の記憶手段に記憶された多画素数画像のうちのいずれを読み出すかを指示するフラグに基づいて、第1の記憶手段に記憶された入力画像、または第2の記憶手段に記憶された多画素数画像が出力される出力ステップとを有し、生成ステップでは、入力画像を構成する画素から多画素数画像を構成する画素を生成する複数の画素生成手段であって、入力画像を構成する画素数に対する多画素数画像を構成する画素数に応じた個数の画素生成手段が用いられて、多画素数画像が生成されることを特徴とする。

【0010】

請求項1に記載の記憶装置においては、第1の記憶手段は、少なくとも第1および第2のアドレス信号によってアドレス指定され、入力画像を記憶するようになされている。生成手段は、入力画像から、その入力画像を構成する画素数よりも多い画素数で構成される画像である多画素数画像を生成するようになされている。第2の記憶手段は、少なくとも第1および第2のアドレス信号によってアドレス指定され、多画素数画像を記憶するようになされている。そして、出力手段は、第1の記憶手段に記憶された入力画像、および第2の記憶手段に記憶された多画素数画像のうちのいずれを読み出すかを指示するフラグに基づいて、第1の記憶手段に記憶された入力画像、または第2の記憶手段に記憶された多画素数画像を出力するようになされている。さらに、生成手段は、入力画像を構成する画素から多画素数画像を構成する画素を生成する複数の画素生成手段であって、入力画像を構成する画素数に対する多画素数画像を構成する画素数に応じた個数の画素生成手段を用いて、多画素数画像を生成するようになされている。

【0011】

請求項5に記載の記憶方法においては、少なくとも第1および第2のアドレス信号によってアドレス指定される第1の記憶手段に、入力画像を記憶させるとともに、入力画像から、その入力画像を構成する画素数よりも多い画素数で構成される画像である多画素数画像を生成し、少なくとも第1および第2のアドレス信号によってアドレス指定される第2の記憶手段に、多画素数画像を記憶させ、第1の記憶手段に記憶された入力画像、および第2の記憶手段に記憶された多画素数画像のうちのいずれを読み出すかを指示するフラグに基づいて、第1の記憶手段に記憶された入力画像、または第2の記憶手段に記憶された多画素数画像が出力されるようになされている。さらに、入力画像を構成する画素から多画素数画像を構成する画素を生成する複数の画素生成手段であって、入力画像を構成する画素数に対する多画素数画像を構成する画素数に応じた個数の画素生成手段が用いられて、多画素数画像が生成されるようになされている。

【0012】

【発明の実施の形態】

図1は、本発明を適用した記憶装置の一実施の形態の構成例を示している。

【0013】

この記憶装置は、例えば、1チップのCMOS(Complementary Metal Oxide Semiconductor)などで構成され、そこに入力される入力画像を記憶するとともに、その入力画像から、それよりも画素数の多い画像、即ち、多画素数画像を形成して記憶する階層符号化を行うようになされている。

【0014】

アドレス供給回路1には、記憶装置に入力される画像(入力画像)を構成する画素の水平方向または垂直方向の位置に対応したアドレスそれぞれとしての水平アドレスまたは垂直アドレスが供給されるようになされている。

【0015】

なお、本実施の形態では、例えば、図2に示すような、1画面が、水平方向が512画素で、垂直方向が512ラインで構成される画像が入力されるものとする。従って、水平アドレスおよび垂直アドレスは、いずれも9(=log2512)ビットで表される。

【0016】

アドレス供給回路1は、そこに供給される水平アドレスおよび垂直アドレスを必要に応じて処理して、入力画像メモリ2および多画素数メモリ4に供給するようになされている。なお、アドレス供給回路1には、水平アドレスおよび垂直アドレスの他、クロック(後述する図5乃至図7においては図示せず)、R/W(Read/Wright)信号、および選択フラグも供給されるようになされており、アドレス供給回路1は、そのクロックに同期して、入力画像メモリ2および多画素数画像メモリ4にアドレスを供給するようになされている。また、アドレス供給回路1は、R/W信号や選択フラグに対応して、そこに供給される水平アドレスおよび垂直アドレスを処理するようになされている。

【0017】

ここで、R/W信号は、記憶装置からの画像データの読み出し、または記憶装置への画像データの書き込みを指示する信号であり、選択フラグは、記憶装置に記憶された画像を読み出す場合に、入力画像メモリ2または多画素数画像メモリ4のうちのいずれに記憶された画像を読み出すかを指示するための、例えば1ビットのフラグである。従って、ここでは、選択フラグは、R/W信号が画像データの読み出しを指示している場合にのみ有効となる(意味を持つ)。即ち、入力画像メモリ2および多画素数画像メモリ4への画像データの書き込みは、後述するように並列に(ほぼ同時に)行われるため、書き込み時においては、選択フラグは無視される。

【0018】

入力画像メモリ2(第1の記憶手段)は、アドレス供給回路1からのアドレスに、RMW(Read Modify Write)回路5から供給される画像データを記憶し、また、そのアドレスに記憶されている画像データを読み出してRMW回路5に出力するようになされている。なお、入力画像メモリ2は、記憶装置に入力される画像(以下、適宜、原画像という)をそのまま記憶するようになされている。また、入力画像メモリ2は、例えば、少なくとも、1画面分の原画像、即ち、ここでは、図2に示したように、512×512画素の画像データを記憶することができるようになされている。さらに、入力画像メモリ2を構成するメモリセルは、例えば、少なくとも、原画像を構成する画素に割り当てられたビット数と同一のデータ長を有している。即ち、原画像を構成する1の画素が、例えば、8ビットで表されるとき、入力画像メモリ2を構成するメモリセルは、少なくとも8ビットのデータ長を有する。

【0019】

多画素数画像生成回路3(生成手段)は、入力画像メモリ2に記憶された原画像から、多画素数画像を生成し、多画素数画像メモリ4に供給するようになされている。即ち、多画素数画像生成回路3は、例えば、図3に示すように、原画像を構成する画素A1を注目画素とするとき、注目画素A1と、その右または下に隣接する画素A2またはA3との間に、新たに画素a12またはa13をそれぞれ形成するとともに、注目画素A1と、その右斜め下に隣接する画素A4との間(画素A2とA3との間)に、新たに画素a1234を形成する。多画素数画像生成回路3は、原画像を構成するすべての画素を順次、注目画素として、上述のような処理を行い、これにより、図4に示すような、横または縦の画素数それぞれが、原画像の2倍になっている多画素数画像、即ち、横×縦が1024×1024画素の画像を形成する。

【0020】

なお、多画素数画像生成回路3における多画素数画像の生成方法としては、例えば、多画素数画像を構成する1の画素を、その画素と相関のある、原画像を構成する複数の画素を用いて重み付け加算を行うことにより生成するものなどがある。即ち、この場合、図3において、多画素数画像の画素a12は、例えば、その左右に隣接する原画像の画素A1とA2との平均値(これは、A1およびA2に対する重みを、いずれも1とした重み付け加算により求められるものである)とすることができる。また、多画素数画像の画素a13は、例えば、その上下に隣接する原画像の画素A1とA3との平均値とすることができる。さらに、多画素数画像の画素a1234は、例えば、その左上、右上、左下、右下に隣接する原画像の画素A1,A2,A3,A4の平均値とすることができる。また、この場合、原画像の画素A1の位置における多画素数画像の画素は、例えば、その原画像の画素A1をそのまま採用することができる。

【0021】

多画素数画像メモリ4(第2の記憶手段)は、アドレス供給回路1からのアドレスに、多画素数画像生成回路3から供給される画像データ、即ち、本実施の形態では、多画素数画像を記憶し、また、そのアドレスに記憶されている画像データを読み出してRMW回路5に出力するようになされている。ここで、多画素数画像メモリ4は、少なくとも、1画面分の多画素数画像、即ち、ここでは、図4に示したように、1024×1024画素で構成される画像を記憶することのできる記憶容量を有している。また、多画素数画像メモリ4を構成するメモリセルは、少なくとも、多画素数画像生成回路3から供給される多画素数画像を構成する画素を、桁落ちが生じないように記憶することができるだけのデータ長を有している。なお、多画素数画像メモリ4を構成するメモリセルのデータ長は、例えば、入力画像メモリ2と同一の8ビットとすることも可能である。

【0022】

ここで、入力画像メモリ2、多画素数画像生成回路3、および多画素数画像メモリ4には、クロックが供給されるようになされており、このクロックに同期して、入力画像メモリ2および多画素数画像メモリ4では、データの読み書きが行われ、また、多画素数画像生成回路3では、多画素数画像の生成が行われるようになされている。

【0023】

RMW回路5は、記憶装置に供給される原画像としての画像データを、入力画像メモリ2に書き込むようになされている。また、また、RMW回路5は、入力画像メモリ2または多画素数画像メモリ4に記憶された画像データを読み出して出力するようにもなされている。なお、RMW回路5には、クロック、R/W信号、選択フラグが供給されるようになされており、RMW回路5は、クロックに同期し、R/W信号、選択フラグに基づいて各種の処理を行うようになされている。

【0024】

次に、図5は、図1の記憶装置の第1の詳細構成例を示している。

【0025】

なお、以下では、図2に示したように、512×512画素で構成される、各画素が8ビットで表される画像データが、原画像として記憶装置に供給されるものとする。また、画像データは、いわゆる順次走査されて供給されるものとする。

【0026】

さらに、原画像を構成する画素を、以下、適宜、その最も左上の画素をp(0,0)とし、以下、同様にして、左からx+1番目で、上からy+1番目にある画素をp(x,y)と表す。原画像は、上述したように、512×512画素で構成されるから、x,yは、いずれも0乃至511(=29−1)の範囲の整数値をとる。

【0027】

また、本実施の形態では、多画素数画像生成回路3では、原画像から、図4に示したような1024×1024画素で構成される多画素数画像が生成されるが、その多画素数画像を構成する画素を、以下、適宜、その最も左上の画素をq(0,0)とし、以下同様にして、左からm+1番目で、上からn+1番目にある画素をq(m,n)と表す。多画素数画像は、1024×1024画素で構成されるから、m,nは、いずれも、0乃至1023(=210−1)の範囲の整数値をとる。

【0028】

さらに、アドレス供給回路1には、データの書き込み時および読み出し時のいずれの場合も、水平アドレスHAおよび垂直アドレスVAの組合せ(HA,VA)が、

の順で、即ち、いわば順次走査に対応した順番で、クロックに同期して供給されるものとする。

【0029】

また、記憶装置への画像データの書き込み時には、RMW回路5には、原画像が、クロックに同期して順次走査されて供給され、これに伴い、アドレス供給回路1には、水平アドレスHAおよび垂直アドレスVAが、上述したように供給されるものとする。

【0030】

図5の実施の形態では、アドレス供給回路1は、遅延回路11a,11b,11c,11dを含んで構成されている。遅延回路11a,11b,11c,11dは、アドレス供給回路1に供給される水平アドレスHAおよび垂直アドレスVAを、必要な時間だけ遅延し、多画素数画像メモリ4を構成するメモリ13a,13b,13c,13dのアドレス端子(AD)にそれぞれ供給するようになされている。なお、アドレス供給回路1は、そこに供給される水平アドレスHAおよび垂直アドレスVAを、そのまま、入力画像メモリ2のアドレス端子(AD)に供給するようにもなされている。

【0031】

多画素数画像生成回路3は、画素生成回路12a,12b,12c,12dで構成されている。画素生成回路12a,12b,12c,12dは、いずれも、入力画像メモリ2に記憶された原画像を構成する1以上の画素を読み出し、その読み出した画素から、多画素数画像を構成する1以上の画素を順次生成し、多画素数画像メモリ4を構成するメモリ13a,13b,13c,13dにそれぞれ供給するようになされている。

【0032】

ここで、多画素数画像生成回路3が、4つの画素生成回路12a乃至12dで構成されているのは、次のような理由による。即ち、原画像は、1画面が512×512画素で構成されるのに対して、多画素数画像は、1画面が1024×1024で構成される。従って、単純に考えれば、原画像の1個の画素が、多画素数画像の4個の画素に対応する。そこで、原画像の1個の画素に対して、多画素数画像の4個の画素を生成するために、その4個の画素それぞれを生成する4つの画素生成回路12a乃至12dで、多画素数画像生成回路3が構成されている。

【0033】

なお、ここでは、原画像の1の画素p(x,y)に対して、多画素数画像の4の画素q(2x,2y),q(2x+1,2y),q(2x,2y+1),q(2x+1,2y+1)を対応させることとし(例えば、図3において、原画像の画素A1を注目画素とするときに、その画素A1の位置における多画素数画像の画素、およびそれに隣接する多画素数画像の画素a12,a13,a1234を生成することとし)、画素生成回路12a乃至12dでは、多画素数画像の画素q(2x,2y),q(2x+1,2y),q(2x,2y+1),q(2x+1,2y+1)がそれぞれ生成されるものとする。

【0034】

多画素数画像メモリ4は、上述したように、4つのメモリ13a乃至13dで構成されている。そして、メモリ13a乃至13dは、遅延回路11a乃至11dから供給されるアドレスに、画素生成回路12a乃至12dから供給される多画素数画像の画素q(2x,2y),q(2x+1,2y),q(2x,2y+1),q(2x+1,2y+1)をそれぞれ記憶するようになされている。従って、メモリ13a乃至13dは、いずれも、512×512画素を記憶することのできる記憶容量を有している。

【0035】

また、メモリ13a乃至13dは、遅延回路11a乃至11dから供給されるアドレスから、そこに記憶されている多画素数画像の画素q(2x,2y),q(2x+1,2y),q(2x,2y+1),q(2x+1,2y+1)を読み出し、RMW回路5に供給するようにもなされている。

【0036】

次に、その動作について説明する。

【0037】

まず、画像データの書き込み時においては、即ち、R/W信号が書き込みを表している場合においては、アドレス供給回路1は、そこに供給される水平アドレスHAおよび垂直アドレスVAを、そのまま、入力画像メモリ2に供給する。一方、RMW回路5は、そこに供給される原画像の画像データを、水平アドレスHAおよび垂直アドレスVAによって指定されている入力画像メモリ2のメモリセル(図示せず)に書き込む。以下、同様の処理が行われることで、512×512画素で構成される1画面分の原画像が、入力画像メモリ2に記憶される。即ち、これにより、入力画像メモリ2のアドレス

には、第1階層の画素(画素値)

がそれぞれ記憶される。

【0038】

また、多画素数画像生成回路3では、画素生成回路12a乃至12dにおいて、多画素数画像を構成する画素q(2x,2y),q(2x+1,2y),q(2x,2y+1),q(2x+1,2y+1)を生成するのに必要な原画像の画素が入力画像メモリ2に記憶されると、その原画像の画素(画素値)が読み出され、多画素数画像の画素q(2x,2y),q(2x+1,2y),q(2x,2y+1),q(2x+1,2y+1)がそれぞれ生成されて、メモリ13a乃至13dにそれぞれ供給される。

【0039】

即ち、上述したように、ここでは、例えば図3において、原画像の画素A1の位置における多画素数画像の画素は、画素A1とされるから、画素生成回路12aは、画素A1が入力画像メモリ2に記憶されると、それをそのまま読み出して、多画素数画像の画素q(2x,2y)としてメモリ13aに供給する。

【0040】

また、図3において、多画素数画像の画素a12は、原画像の画素A1とA2との平均値となるから、画素生成回路12bは、入力画像メモリ2に、画素A1が記憶され、さらに画素A2が記憶されるのを待って、画素A1およびA2を読み出す。そして、画素生成回路12bは、その画素A1とA2との平均値を計算し、多画素数画像の画素q(2x+1,2y)としてメモリ13bに供給する。

【0041】

さらに、図3において、多画素数画像の画素a13は、原画像の画素A1とA3との平均値とされるから、画素生成回路12Cは、入力画像メモリ2に、画素A1が記憶され、さらに、1ライン分の画素(原画像の1ライン分の画素)が記憶されることにより、画素A3が記憶されるのを待って、画素A1およびA3を読み出す。そして、画素生成回路12Cは、その画素A1とA2との平均値を計算し、多画素数画像の画素q(2x,2y+1)としてメモリ13Cに供給する。

【0042】

また、図3において、多画素数画像の画素a1234は、原画像の画素A1乃至A4の平均値とされるから、画素生成回路12dは、入力画像メモリ2に、これらの画素A1乃至A4が記憶されるのを待って読み出す。そして、画素生成回路12dは、画素A1乃至A4の平均値を計算し、多画素数画像の画素q(2x+1,2y+1)としてメモリ13dに供給する。

【0043】

一方、アドレス供給回路1では、遅延回路11a乃至11dにおいて、原画像の画素p(x,y)が入力画像メモリ2に記憶されてから、画素生成回路12a乃至12dが、多画素数画像の画素q(2x,2y),q(2x+1,2y),q(2x,2y+1),q(2x+1,2y+1)を生成するのに必要な時間だけ、水平アドレスHAおよび垂直アドレスVAがそれぞれ遅延され、メモリ13a乃至13dにそれぞれ供給される。

【0044】

その結果、メモリ13a乃至13dでは、同一のアドレス(x,y)に、画素生成回路12a乃至12dから供給される画素q(2x,2y),q(2x+1,2y),q(2x,2y+1),q(2x+1,2y+1)がそれぞれ記憶される。

【0045】

次に、読み出し時においては、即ち、R/W信号が読み出しを表している場合においては、選択フラグが原画像を表しているときには、アドレス供給回路1は、そこに供給される水平アドレスHAおよび垂直アドレスVAを、そのまま、入力画像メモリ2のアドレス端子に供給する。そして、RMW回路5において、水平アドレスHAおよび垂直アドレスVAによって指定されている入力画像メモリ2のメモリセルに記憶されている原画像の画素(画素値)が順次読み出される。

【0046】

以上のようにして、512×512画素で構成される1画面分の原画像が、入力画像メモリ2から読み出され、順次走査された原画像が出力される。

【0047】

一方、R/W信号が読み出しを表している場合において、選択フラグが多画素数画像を表しているときには、アドレス供給回路1は、そこに供給される水平アドレスHAおよび垂直アドレスVAを、遅延回路11a乃至11dにおいて、多画素数画像を、順次走査に対応する順に出力することができるように遅延して、メモリ13a乃至13dのアドレス端子に、それぞれ供給する。

【0048】

即ち、メモリ13a乃至13dでは、同一のアドレス(x,y)に、画素q(2x,2y),q(2x+1,2y),q(2x,2y+1),q(2x+1,2y+1)がそれぞれ記憶されている。従って、メモリ13a乃至13dそれぞれから、画素q(2x,2y),q(2x+1,2y),q(2x,2y+1),q(2x+1,2y+1)を順次走査に対応した順番で読み出すためには、画素q(2x,2y)を基準とすると、メモリ13bには、アドレス(x,y)を、メモリ13aに与えるタイミングよりも1画素分(多画素数画像の1画素分)だけ遅延して与える必要がある。また、メモリ13cには、アドレス(x,y)を、メモリ13aに与えるタイミングよりも1ライン分(ここでは、多画素数画素の1024画素分)だけ遅延して与える必要がある。さらに、メモリ13dには、アドレス(x,y)を、メモリ13aに与えるタイミングよりも1ラインと1画素分(ここでは、多画素数画素の1025画素分)だけ遅延して与える必要がある。

【0049】

そこで、遅延回路11a乃至11dでは、アドレス供給回路1に供給される水平アドレスHAおよび垂直アドレスVAの組(HA,VA)が、上述のような時間だけそれぞれ遅延され、メモリ13a乃至13dのアドレス端子に、それぞれ供給される。

【0050】

そして、RMW回路5においては、遅延回路11a乃至11dからのアドレスによって指定されているメモリ13a乃至13dのメモリセルに記憶されている多画素数画像の画素が順次読み出される。

【0051】

以上のようにして、1024×1024画素で構成される1画面分の多画素数画像が、多画素数画像メモリ4(メモリ13a乃至13d)から読み出され、順次走査された多画素数画像が出力される。

【0052】

なお、原画像および多画素数画像の1画面の周期を同一とする場合には、多画素数画像の1画面を構成する画素数は、原画像の1画面を構成する画素数の4倍であるから、多画素数画像の読み出し時においては、遅延回路11a乃至11dおよびRMW回路5を、通常のクロックの4倍の周波数のクロック(以下、適宜、4倍クロックという)に同期させて動作させる必要がある。この4倍クロックは、例えば、アドレス供給回路1やRMW回路5に、PLL(Phase Lock Loop)回路を内蔵させ、そのPLL回路に、通常のクロックに基づいて生成させるようにすることができる。

【0053】

以上のように、原画像と並列して、その原画像の画素数を多くした多画素数画像が生成されて記憶されるので、例えば、電子ズームなどにおいて、原画像の拡大が要求された場合に、多画素数画像メモリ4から多画素数画像を読み出すことで、即座に、原画像を拡大した画像としての多画素数画像を提供することが可能となる。

【0054】

次に、図6は、図1の記憶装置の第2の詳細構成例を示している。なお、図中、図5における場合と対応する部分については、同一の符号を付してある。

【0055】

この実施の形態では、アドレス供給回路1は、遅延回路11およびカウンタ21を含んで構成されている。遅延回路11は、そこに供給されるアドレスを必要な時間だけ遅延して、多画素数画像メモリ4を構成するメモリ22のアドレス端子(AD)に供給するようになされている。カウンタ21は、2ビットのカウンタなどで、例えば、4倍クロックをカウントし、2ビットのカウント値を出力するようになされている。

【0056】

また、アドレス供給回路1は、カウンタ21が出力する2ビットのカウント値のうちの最下位ビット(付加アドレス信号)を、そこに供給される9ビットの水平アドレスHAの最下位ビットとして付加し、これにより、10ビットの水平アドレスHA’を構成し、遅延回路11を介して、メモリ22のアドレス端子(AD)に供給するようになされている。さらに、アドレス供給回路1は、カウンタ21が出力する2ビットのカウント値のうちの最上位ビット(付加アドレス信号)を、そこに供給される9ビットの垂直アドレスVAの最下位ビットとして付加し、これにより、10ビットの垂直アドレスVA’を構成し、遅延回路11を介して、メモリ22のアドレス端子(AD)に供給するようになされている。

【0057】

従って、図6の実施の形態では、アドレス供給回路1において、入力画像メモリ2に対して、アドレス(x,y)が供給されると、メモリ22に対しては、遅延回路11を介して、アドレス(2x,2y),(2x+1,2y),(2x,2y+1),(2x+1,2y+1)が供給される。

【0058】

多画素数画像メモリ4は、上述したように、1のメモリ22で構成されている。そして、メモリ22は、遅延回路11から供給されるアドレス(2x,2y),(2x+1,2y),(2x,2y+1),(2x+1,2y+1)に、画素生成回路12a乃至12dから供給される多画素数画像の画素q(2x,2y),q(2x+1,2y),q(2x,2y+1),q(2x+1,2y+1)をそれぞれ記憶するようになされている。従って、メモリ22は、1画面の多画素数画像を構成する1024×1024画素を記憶することのできる記憶容量を有している。

【0059】

また、メモリ22は、遅延回路11から供給されるアドレス(2x,2y),(2x+1,2y),(2x,2y+1),(2x+1,2y+1)から、それぞれに記憶されている多画素数画像の画素q(2x,2y),q(2x+1,2y),q(2x,2y+1),q(2x+1,2y+1)を読み出し、RMW回路5に供給するようにもなされている。

【0060】

次に、その動作について説明する。

【0061】

まず、画像データの書き込み時においては、即ち、R/W信号が書き込みを表している場合においては、入力画像メモリ2には、図5における場合と同様にして、原画像が書き込まれる。

【0062】

また、多画素数画像生成回路3では、画素生成回路12a乃至12dにおいて、多画素数画像を構成する画素q(2x,2y),q(2x+1,2y),q(2x,2y+1),q(2x+1,2y+1)を生成するのに必要な原画像の画素が入力画像メモリ2に記憶されると、図5における場合と同様に、多画素数画像の画素q(2x,2y),q(2x+1,2y),q(2x,2y+1),q(2x+1,2y+1)がそれぞれ生成され、メモリ22に順次供給される。

【0063】

一方、アドレス供給回路1では、カウンタ21が出力する2ビットのカウント値のうちの最下位ビットまたは最上位ビットが、そこに供給される9ビットの水平アドレスHAまたは垂直アドレスVAの最下位ビットとしてそれぞれ付加され、10ビットの水平アドレスHA’および垂直アドレスVA’が構成される。即ち、これにより、水平アドレスHAと垂直アドレスVAとの組(HA,VA)として、(x,y)が、アドレス供給回路1に供給された場合、4つのアドレス(2x,2y),(2x+1,2y),(2x,2y+1),(2x+1,2y+1)が構成される。これらのアドレス(2x,2y),(2x+1,2y),(2x,2y+1),(2x+1,2y+1)それぞれは、遅延回路11において、原画像の画素p(x,y)が入力画像メモリ2に記憶されてから、画素生成回路12a乃至12dが、多画素数画像の画素q(2x,2y),q(2x+1,2y),q(2x,2y+1),q(2x+1,2y+1)を生成するのに必要な時間だけそれぞれ遅延され、メモリ22に供給される。

【0064】

その結果、メモリ22では、アドレス(2x,2y),(2x+1,2y),(2x,2y+1),(2x+1,2y+1)に、画素生成回路12a乃至12dから供給される画素q(2x,2y),q(2x+1,2y),q(2x,2y+1),q(2x+1,2y+1)がそれぞれ記憶される。

【0065】

次に、読み出し時においては、即ち、R/W信号が読み出しを表している場合においては、選択フラグが原画像を表しているときには、図5における場合と同様にして、原画像が、入力画像メモリ2から読み出され、RMW回路5から、順次走査された原画像が出力される。

【0066】

また、R/W信号が読み出しを表している場合において、選択フラグが多画素数画像を表しているときには、アドレス供給回路1は、上述したようにして、10ビットの水平アドレスHA’および垂直アドレスVA’、即ち、アドレス(2x,2y),(2x+1,2y),(2x,2y+1),(2x+1,2y+1)を構成し、遅延回路11に出力する。遅延回路11では、アドレス(2x,2y),(2x+1,2y),(2x,2y+1),(2x+1,2y+1)が、多画素数画像を、順次走査に対応する順に出力することができるように遅延され、メモリ22のアドレス端子に、それぞれ供給される。

【0067】

即ち、メモリ22に、アドレス(2x,2y),(2x+1,2y),(2x,2y+1),(2x+1,2y+1)を与えると、画素q(2x,2y),q(2x+1,2y),q(2x,2y+1),q(2x+1,2y+1)がそれぞれ読み出されるが、これらの画素q(2x,2y),q(2x+1,2y),q(2x,2y+1),q(2x+1,2y+1)を順次走査に対応した順番で読み出すためには、アドレス(2x,2y)に記憶されている画素q(2x,2y)を基準とすると、アドレス(2x+1,2y)は、アドレス(2x,2y)をタイミングよりも1画素分(多画素数画像の1画素分)だけ遅延して与える必要がある。また、アドレス(2x,2y+1)は、アドレス(2x,2y)を与えるタイミングよりも1ライン分(ここでは、多画素数画素の1024画素分)だけ遅延して与える必要がある。さらに、アドレス(2x+1,2y+1)は、アドレス(2x,2y)を与えるタイミングよりも1ラインと1画素分(ここでは、多画素数画素の1025画素分)だけ遅延して与える必要がある。

【0068】

そこで、遅延回路11では、アドレス(2x+1,2y),(2x,2y+1),(2x+1,2y+1)が、アドレス(2x,2y)が出力される時刻を基準として、上述のような時間だけそれぞれ遅延され、メモリ22のアドレス端子に供給される。

【0069】

そして、RMW回路5においては、遅延回路11からのアドレスによって指定されているメモリ22のメモリセルに記憶されている多画素数画像の画素が読み出される。

【0070】

以上のようにして、1024×1024画素で構成される1画面分の多画素数画像が、多画素数画像メモリ4(メモリ22)から読み出され、順次走査された多画素数画像が出力される。

【0071】

なお、図6の実施の形態においても、原画像および多画素数画像の1画面の周期を同一とする場合には、多画素数画像の読み出し時において、遅延回路11およびRMW回路5を、4倍クロックに同期させて動作させる必要がある。

【0072】

以上のように、図6の実施の形態でも、原画像と並列して、その原画像の画素数を多くした多画素数画像が生成されて記憶されるので、例えば、電子ズームなどにおいて、原画像の拡大が要求された場合に、多画素数画像メモリ4から多画素数画像を読み出すことで、即座に、原画像を拡大した画像としての多画素数画像を提供することが可能となる。

【0073】

次に、上述の場合においては、多画素数画像生成回路3において、多画素数画像を、原画像を用いた重み付け加算を行うことによって生成するようにしたが、多画素数画像は、その他、例えば、クラス分類適応処理などを行うことによっても生成することができる。

【0074】

図7は、クラス分類適応処理によって多画素数画像を生成する場合の多画素数画像生成回路3(画素生成回路12a乃至12dそれぞれ)の構成例を示している。

【0075】

クラス分類用ブロック化回路41および予測値計算用ブロック化回路42には、入力画像メモリ2に記憶された原画像の画像データ(原画像データ)が供給されるようになされている。クラス分類用ブロック化回路41は、原画像データを、その性質に応じて所定のクラスに分類するための単位である、注目している原画像データ(注目原画像データ)を中心としたクラス分類用ブロックにブロック化するようになされている。

【0076】

即ち、いま、図8において、上からi番目で、左からj番目の原画像データ(原画像を構成する画素(画素値))(図中、○印で示す部分)をXijと表すとすると、クラス分類用ブロック化回路41は、例えば、注目原画像データXijの左上、上、右上、左、右、左下、下、右下に隣接する8つの画素X(i-1)(j-1),X(i-1)j,X(i-1)(j+1),Xi(j-1),Xi(j+1),X(i-1)(j-1),X(i-1)j,X(i+1)(j+1)に、自身を含め、合計9画素で構成されるクラス分類用ブロックを構成するようになされている。このクラス分類用ブロックは、クラス分類適応処理回路43に供給されるようになされている。

【0077】

なお、この場合、クラス分類用ブロックは、3×3画素(横×縦)でなる正方形状のブロックで構成されることとなるが、クラス分類用ブロックの形状は、正方形である必要はなく、その他、例えば、長方形や、十文字形、その他の任意な形とすることが可能である。また、クラス分類用ブロックを構成する画素数も、3×3の9画素に限定されるものではない。

【0078】

予測値計算用ブロック化回路42は、原画像データを、多画素数画像を構成する画素(画素値)の予測値を計算するための単位である、注目原画像データを中心とした予測値計算用ブロックにブロック化するようになされている。即ち、いま、図8において、原画像データXij(図中、○印で示す部分)を中心とする、多画素数画像における3×3の9画素(図中、×印で示す部分)を、その最も左から右方向、かつ上から下方向に、Yij(1),Yij(2),Yij(3),Yij(4),Yij(5),Yij(6),Yij(7),Yij(8),Yij(9)と表すとすると、画素Yij(1)乃至Yij(9)の予測値の計算のために、予測値計算用ブロック化回路42は、例えば、注目原画像データXijを中心とする5×5の25画素X(i-2)(j-2),X(i-2)(j-1),X(i-2)j,X(i-2)(j+1),X(i-2)(j+2),X(i-1)(j-2),X(i-1)(j-1),X(i-1)j,X(i-1)(j+1),X(i-1)(j+2),Xi(j-2),Xi(j-1),Xij,Xi(j+1),Xi(j+2),X(i+1)(j-2),X(i+1)(j-1),X(i+1)j,X(i+1)(j+1),X(i+1)(j+2),X(i+2)(j-2),X(i+2)(j-1),X(i+2)j,X(i+2)(j+1),X(i+2)(j+2)で構成される正方形状の予測値計算用ブロックを構成するようになされている。

【0079】

具体的には、例えば、図8において四角形で囲む、多画素数画像における画素Y33(1)乃至Y33(9)の9画素の予測値の計算のためには、画素X11,X12,X13,X14,X15,X21,X22,X23,X24,X25,X31,X32,X33,X34,X35,X41,X42,X43,X44,X45,X51,X52,X53,X54,X55により、予測値計算用ブロックが構成される(この場合の注目原画像データは、X33となる)。

【0080】

予測値計算用ブロック化回路42において得られた予測値計算用ブロックは、クラス分類適応処理回路43に供給されるようになされている。

【0081】

なお、予測値計算用ブロックについても、クラス分類用ブロックにおける場合と同様に、その画素数および形状は、上述したものに限定されるものではない。但し、予測値計算用ブロックを構成する画素数は、クラス分類用ブロックを構成する画素数よりも多くするのが望ましい。

【0082】

また、上述のようなブロック化を行う場合において(ブロック化以外の処理についても同様)、画像の画枠付近では、対応する画素が存在しないことがあるが、この場合には、例えば、画枠を構成する画素と同一の画素が、その外側に存在するものとして処理を行う。

【0083】

クラス分類適応処理回路43は、ADRC(Adaptive Dynamic Range Coding)処理回路、クラス分類回路45、予測係数ROM46、および予測回路47で構成され、クラス分類適応処理を行うようになされている。

【0084】

クラス分類適応処理とは、入力信号を、その特徴に基づいて幾つかのクラスに分類し、各クラスの入力信号に、そのクラスに適切な適応処理を施すもので、大きく、クラス分類処理と適応処理とに分かれている。

【0085】

ここで、クラス分類処理および適応処理について簡単に説明する。

【0086】

まず、クラス分類処理について説明する。

【0087】

いま、例えば、図9(A)に示すように、ある注目画素と、それに隣接する3つの画素により、2×2画素でなるブロック(クラス分類用ブロック)を構成し、また、各画素は、1ビットで表現される(0または1のうちのいずれかのレベルをとる)ものとする。この場合、注目画素を含む2×2の4画素のブロックは、各画素のレベル分布により、図9(B)に示すように、16(=(21)4)パターンに分類することができる。従って、いまの場合、注目画素は、16のパターンに分類することができ、このようなパターン分けが、クラス分類処理であり、クラス分類回路45において行われる。

【0088】

なお、クラス分類処理は、画像(ブロック内の画像)のアクティビティ(画像の複雑さ)(変化の激しさ)などをも考慮して行うようにすることが可能である。

【0089】

ここで、本実施の形態では、原画像を構成する各画素に、8ビットが割り当てられる。また、本実施の形態においては、上述したように、クラス分類用ブロックは、3×3の9画素で構成される。従って、このようなクラス分類用ブロックを対象にクラス分類処理を行ったのでは、(28)9という膨大な数のクラスに分類されることになる。

【0090】

そこで、本実施の形態においては、ADRC処理回路44において、クラス分類用ブロックに対して、ADRC処理が施されるようになされており、これにより、クラス分類用ブロックを構成する画素のビット数を小さくすることで、クラス数を削減するようになされている。

【0091】

即ち、例えば、いま、説明を簡単にするため、図10(A)に示すように、直線上に並んだ4画素で構成されるブロックを考えると、ADRC処理においては、その画素値の最大値MAXと最小値MINが検出される。そして、DR=MAX−MINを、ブロックの局所的なダイナミックレンジとし、このダイナミックレンジDRに基づいて、ブロックを構成する画素の画素値がKビットに再量子化される。

【0092】

即ち、ブロック内の各画素値から、最小値MINを減算し、その減算値をDR/2Kで除算する。そして、その結果得られる除算値に対応するコード(ADRCコード)に変換される。具体的には、例えば、K=2とした場合、図10(B)に示すように、除算値が、ダイナミックレンジDRを4(=22)等分して得られるいずれの範囲に属するかが判定され、除算値が、最も下のレベルの範囲、下から2番目のレベルの範囲、下から3番目のレベルの範囲、または最も上のレベルの範囲に属する場合には、それぞれ、例えば、00B,01B,10B、または11Bなどの2ビットにコード化される(Bは2進数であることを表す)。なお、その復号は、ADRCコード00B,01B,10B、または11Bを、ダイナミックレンジDRを4等分して得られる最も下のレベルの範囲の中心値L00、下から2番目のレベルの範囲の中心値L01、下から3番目のレベルの範囲の中心値L10、または最も上のレベルの範囲の中心値L11に変換し、その値に、最小値MINを加算することで行われる。

【0093】

ここで、このようなADRC処理はノンエッジマッチングと呼ばれ、また、ADRC処理については、本件出願人が先に出願した、例えば、特開平3−53778号公報などに、その詳細が開示されている。

【0094】

ブロックを構成する画素に割り当てられているビット数より少ないビット数で再量子化を行うADRC処理を施すことにより、上述したように、クラス数を削減することができ、このようなADRC処理が、ADRC処理回路44において行われるようになされている。

【0095】

なお、本実施の形態では、クラス分類回路45において、ADRC処理回路44から出力されるADRCコードに基づいて、クラス分類処理が行われるが、クラス分類処理は、その他、例えば、DPCM(予測符号化)や、BTC(Block Truncation Coding)、VQ(ベクトル量子化)、DCT(離散コサイン変換)、アダマール変換などを施したデータを対象に行うようにすることも可能である。

【0096】

次に、適応処理について説明する。

【0097】

例えば、いま、ある画像(上述の多画素数画像に相当する画像)の画素(画素値)yの予測値E[y]を、その画像の画素を間引いて得られる画像(画素数の少ない画像)(上述の原画像に相当する画像)を構成する幾つかの画素(画素値)(以下、適宜、学習データという)x1,x2,・・・と、所定の予測係数w1,w2,・・・の線形結合により規定される線形1次結合モデルにより求めることを考える。この場合、予測値E[y]は、次式で表すことができる。

【0098】

【0099】

そこで、一般化するために、予測係数wの集合でなる行列W、学習データの集合でなる行列X、および予測値E[y]の集合でなる行列Y’を、

【数1】

で定義すると、次のような観測方程式が成立する。

【0100】

XW=Y’

・・・(2)

【0101】

そして、この観測方程式に最小自乗法を適用して、元の画像の画素値yに近い予測値E[y]を求めることを考える。この場合、元の画像の画素値(以下、適宜、教師データという)yの集合でなる行列Y、および元の画像の画素値yに対する予測値E[y]の残差eの集合でなる行列Eを、

【数2】

で定義すると、式(2)から、次のような残差方程式が成立する。

【0102】

XW=Y+E・・・(3)

【0103】

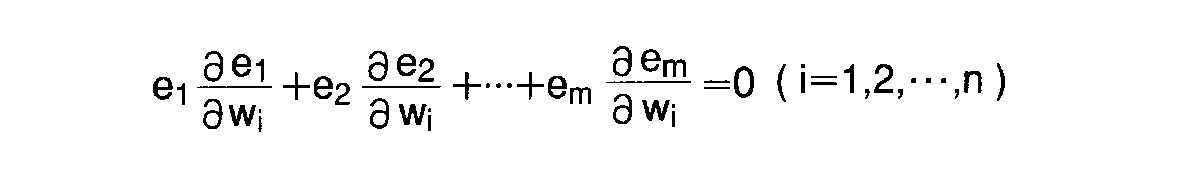

この場合、元の画像の画素値yに近い予測値E[y]を求めるための予測係数wiは、自乗誤差

【数3】

を最小にすることで求めることができる。

【0104】

従って、上述の自乗誤差を予測係数wiで微分したものが0になる場合、即ち、次式を満たす予測係数wiが、元の画像の画素値yに近い予測値E[y]を求めるため最適値ということになる。

【0105】

【数4】

・・・(4)

【0106】

そこで、まず、式(3)を、予測係数wiで微分することにより、次式が成立する。

【0107】

【数5】

・・・(5)

【0108】

式(4)および(5)より、式(6)が得られる。

【0109】

【数6】

・・・(6)

【0110】

さらに、式(3)の残差方程式における学習データx、予測係数w、教師データy、および残差eの関係を考慮すると、式(6)から、次のような正規方程式を得ることができる。

【0111】

【数7】

・・・(7)

【0112】

式(7)の正規方程式は、求めるべき予測係数wの数と同じ数だけたてることができ、従って、式(7)を解くことで、最適な予測係数wを求めることができる。なお、式(7)を解くにあたっては、例えば、掃き出し法(Gauss-Jordanの消去法)などを適用することが可能である。

【0113】

以上のように、クラスごとに最適な予測係数wを求め、その予測係数wを用い、式(1)により、元の画像の画素値yに近い予測値E[y]を求めるのが適応処理であり、この適応処理が、予測係数ROM46および予測回路47において行われるようになされている。

【0114】

即ち、予測係数ROM46は、あらかじめ学習(後述する)を行うことにより求められたクラスごとの予測係数を記憶しており、クラス分類回路45が出力するクラス情報を受信し、そのクラス情報に対応するアドレスに記憶されている予測係数(クラス情報に対応する予測係数)を読み出して、予測回路47に供給するようになされている。

【0115】

予測回路47は、予測値計算用ブロック化回路42からの5×5画素の予測値計算用ブロックと、予測係数ROM46からの予測係数とを用いて、式(1)に示した線形1次式を計算し、これにより、多画素数画像の3×3画素の予測値を算出するようになされている。

【0116】

なお、適応処理は、間引かれた画像には含まれていない、元の画像に含まれる成分が再現される点で、上述したような重み付け加算のような補間処理とは異なる。即ち、適応処理は、式(1)だけを見る限りは、いわゆる補間フィルタを用いての補間処理と同一であるが、その補間フィルタのタップ係数に相当する予測係数wが、教師データyを用いての、いわば学習により求められるため、元の画像に含まれる成分を再現することができる。このことから、適応処理は、いわば画像の創造作用がある処理ということができる。

【0117】

次に、図7の多画素数画像生成回路3の処理について説明する。

【0118】

多画素数画像生成回路3においては、まず最初に、原画像データがブロック化される。即ち、クラス分類用ブロック化回路41において、原画像データが、注目原画像データを中心とする3×3画素のクラス分類用ブロックにブロック化され、クラス分類適応処理回路43に供給されるとともに、予測値計算用ブロック化回路42において、原画像データが、注目原画像データを中心とする5×5画素の予測値計算用ブロックにブロック化され、クラス分類適応処理回路43に供給される。

【0119】

クラス分類適応処理回路43においては、クラス分類用ブロックはADRC処理部44に、予測値計算用ブロックは適応処理回路46に、それぞれ供給される。

【0120】

ADRC処理回路44は、クラス分類用ブロックを受信すると、そのクラス分類用ブロックに対して、例えば、1ビットのADRC(1ビットで再量子化を行うADRC)処理を施し、これにより、原画像データを、1ビットに変換(符号化)して、クラス分類回路45に出力する。クラス分類回路45では、ADRC処理が施されたクラス分類用ブロックに対して、クラス分類処理が施される。即ち、ADRC処理が施されたクラス分類用ブロックを構成する各画素のレベル分布の状態が検出され、そのクラス分類用ブロックが属するクラスが判定される。このクラスの判定結果は、クラス情報として、予測係数ROM46に供給される。

【0121】

なお、本実施の形態においては、1ビットのADRC処理が施された3×3の9画素で構成されるクラス分類用ブロックに対して、クラス分類処理が施されるので、各クラス分類用ブロックは、512(=(21)9)のクラスのうちのいずれかに分類されることになる。

【0122】

予測係数ROM46は、クラス情報を受信すると、そのクラス情報に対応する予測係数を、記憶しているクラスごとの予測係数の中から読み出し、予測回路47に供給する。予測回路47では、予測係数ROM46からの予測係数と、予測値計算用ブロック化回路42からの予測値計算用ブロックとを用いて適応処理が行われることにより、即ち、式(1)にしたがった演算が行われることにより、多画素数画像の画素の予測値が求められる。

【0123】

次に、図11は、図7の予測係数ROM46に記憶されている予測係数を得るための学習を行う画像処理装置の構成例を示している。

【0124】

学習用ブロック化回路91および教師用ブロック化回路92には、予測係数を得るための学習用の画像データ(学習用の多画素数画像)が供給されるようになされている。

【0125】

学習用ブロック化回路91は、そこに入力される画像データから、例えば、図8に○印で示した位置関係の5×5画素(原画像を構成する画素に相当する)を抽出し、この25画素で構成されるブロックを、学習用ブロックとして、ADRC処理93および学習データメモリ96に供給する。

【0126】

また、教師用ブロック化回路92では、入力される画像データから、例えば、3×3の9画素で構成されるブロックが生成され、この9画素で構成されるブロックが、教師用ブロックとして、教師データメモリ98に供給される。

【0127】

なお、学習用ブロック化回路91において、例えば、図8に○印で示した位置関係の25画素X11,X12,X13,X14,X15,X21,X22,X23,X24,X25,X31,X32,X33,X34,X35,X41,X42,X43,X44,X45,X51,X52,X53,X54,X55で構成される学習用ブロックが生成されるとき、教師用ブロック化回路92では、同図に四角形で囲んで示す3×3画素の教師用ブロックが生成されるようになされている。

【0128】

ADRC処理回路93は、学習用ブロックを構成する25画素から、例えば、その中心の9画素(3×3画素)を抽出し、この9画素でなるブロックに対して、図7のADRC処理回路44における場合と同様に、1ビットのADRC処理を施す。ADRC処理の施された3×3画素のブロックは、クラス分類回路94に供給される。クラス分類回路94では、図7のクラス分類回路45における場合と同様に、ADRC処理回路93からのブロックがクラス分類処理され、それにより得られるクラス情報が、スイッチ95の端子aを介して、学習データメモリ96および教師データメモリ98に供給される。

【0129】

学習データメモリ96または教師データメモリ98では、そこに供給されるクラス情報に対応するアドレスに、学習用ブロック化回路91からの学習用ブロックまたは教師用ブロック化回路92からの教師用ブロックが、それぞれ記憶される。

【0130】

従って、学習データメモリ96において、例えば、図8に○印で示した5×5画素X11,X12,X13,X14,X15,X21,X22,X23,X24,X25,X31,X32,X33,X34,X35,X41,X42,X43,X44,X45,X51,X52,X53,X54,X55でなるブロックが学習用ブロックとして、あるアドレスに記憶されたとすると、教師データメモリ98においては、そのアドレスと同一のアドレスに、同図において、四角形で囲んで示す3×3画素(同図において×印で示す)のブロックが、教師用ブロックとして記憶される。

【0131】

以下、同様の処理が、あらかじめ用意されたすべての学習用の画像について繰り返され、これにより、学習用ブロックと、図7の多画素数画像生成回路3において、その学習用ブロックを構成する25画素と同一の位置関係を有する25の原画像データで構成される予測値計算用ブロックを用いて予測値が求められる9画素で構成される教師用ブロックとが、学習用データメモリ96と、教師用データメモリ98とにおいて、同一のアドレスに記憶される。

【0132】

なお、学習用データメモリ96と教師用データメモリ98においては、同一アドレスに複数の情報を記憶することができるようになされており、これにより、同一アドレスには、複数の学習用ブロックと教師用ブロックを記憶することができるようになされている。

【0133】

学習用画像すべてについての学習用ブロックと教師用ブロックとが、学習データメモリ96と教師データメモリ98に記憶されると、端子aを選択していたスイッチ95が、端子bに切り替わり、これにより、カウンタ97の出力が、アドレスとして、学習データメモリ96および教師データメモリ98に供給される。カウンタ97は、所定のクロックをカウントし、そのカウント値を出力しており、学習データメモリ96または教師データメモリ98では、そのカウント値に対応するアドレスに記憶された学習用ブロックまたは教師用ブロックが読み出され、演算回路99に供給される。

【0134】

従って、演算回路99には、カウンタ97のカウント値に対応するクラスの学習用ブロックのセットと、教師用ブロックのセットとが供給される。

【0135】

演算回路99は、あるクラスについての学習用ブロックのセットと、教師用ブロックのセットとを受信すると、それらを用いて、最小自乗法により、誤差を最小とする予測係数を算出する。

【0136】

即ち、例えば、いま、学習用ブロックを構成する画素の画素値を、x1,x2,x3,・・・とし、求めるべき予測係数をw1,w2,w3,・・・とするとき、これらの線形1次結合により、教師用ブロックを構成する、ある画素の画素値yを求めるには、予測係数w1,w2,w3,・・・は、次式を満たす必要がある。

【0137】

y=w1x1+w2x2+w3x3+・・・

【0138】

そこで、演算回路99では、同一クラスの学習用ブロックと、対応する教師用ブロックとから、真値yに対する、予測値w1x1+w2x2+w3x3+・・・の自乗誤差を最小とする予測係数w1,w2,w3,・・・が、上述した式(7)に示す正規方程式をたてて解くことにより求められる。従って、この処理をクラスごとに行うことにより、各クラスごとに、予測係数が生成される。

【0139】

演算回路99において求められた、クラスごとの予測係数は、メモリ100に供給される。メモリ100には、演算回路99からの予測係数の他、カウンタ97からカウント値が供給されており、これにより、メモリ100においては、演算回路99からの予測係数が、カウンタ97からのカウント値に対応するアドレスに記憶される。

【0140】

以上のようにして、メモリ100には、各クラスに対応するアドレスに、そのクラスのブロックの3×3画素を予測するのに最適な予測係数が記憶される。

【0141】

図7の予測係数ROM46には、以上のようにしてメモリ100に記憶されたクラスごとの予測係数が記憶されている。

【0142】

なお、本実施の形態では、多画素数画像メモリ4に、原画像の横または縦の画素数を、それぞれ2倍にした多画素数画像を記憶させるようにしたが、多画素数画像メモリ4に記憶させる多画素数画像を構成する画素数は、これに限定されるものではない。

【0143】

また、多画素数画像メモリ4は複数設けるようにすることができ、これにより、原画像よりも画素数が多い、異なる画素数の多画素数画像を記憶させるようにすることができる。

【0144】

さらに、本実施の形態では、多画素数画像メモリ4に対しては、入力画像メモリ2に与える水平アドレスHAおよび垂直アドレスVAを処理して得られるアドレスを与えるようにしたが、多画素数メモリ4には、入力画像メモリ2に与える水平アドレスHAおよび垂直アドレスVAとは別に生成した、独立のアドレスを与えてアクセスするようにすることも可能である。

【0145】

また、本実施の形態では、入力画像メモリ2および多画素数画像メモリ4に対して、画像を構成する画素の水平または垂直方向の位置にそれぞれ対応する水平アドレスまたは垂直アドレスを与えてアクセスするようにしたが、入力画像メモリ2および多画素数画像メモリ4には、その他、例えば、時間方向に対応するアドレスをさらに与えてアクセスするようにすることなども可能である。この場合、多画素数画像は、横および縦の空間方向に散らばる原画像の画素の他、時間方向に散らばる原画像の画素も用いて形成されることになる。

【0146】

さらに、入力画像メモリ2、多画素数画像メモリ4は、それぞれ物理的に別のメモリである必要はなく、両者を、1のメモリで構成することも可能である。この場合、1のメモリの記憶領域を、入力画像メモリ2、多画素数画像メモリ4のそれぞれに割り当てるようにすれば良い。

【0147】

また、本実施の形態では、アドレス供給回路1、入力画像メモリ2、多画素数画像生成回路3、多画素数画像メモリ4、およびRMW回路5のすべてを、1チップ上に形成するようにしたが、これらは、必ずしも1チップ上に形成する必要はない。

【0148】

さらに、本実施の形態では、原画像の画素数を多くした多画素数画像だけを形成するようにしたが、多画素数画像の他、原画像の画素数を少なくした画像も、同時に形成して記憶するようにすることも可能である。

【0149】

また、本発明は、ノンインターレース走査される画像およびインターレース走査される画像のいずれにも適用可能である。

【0150】

さらに、本実施の形態では、記憶装置をハードウェアで実現するようにしたが、記憶装置は、上述のような処理を行うためのプログラムをコンピュータに実行させることによっても実現可能である。

【0151】

また、図6の実施の形態では、多画素数画像メモリ4を、1のメモリ22で構成するようにしたが、図6においても、多画素数メモリ4は、図5における場合と同様に、4つのメモリ13a乃至13dで構成することも可能である。この場合、カウンタ21の出力は、水平アドレスHAおよび垂直アドレスVAの最下位ビットとして付加するのではなく、4つのメモリ13a乃至13dのうちのいずれか1つを選択するための、いわゆるチップセレクト信号として用いるようにすれば良い。

【0152】

さらに、本実施の形態では、画素(画素値)を、例えば、RAM(Random Access Memory)などに代表されるメモリに記憶させるようにしたが、画素は、その他、例えば、磁気ディスクや、光磁気ディスク、磁気テープ、光カードなどの記録媒体に記憶(記録)させるようにすることも可能である。

【0153】

【発明の効果】

請求項1に記載の記憶装置および請求項5に記載の記憶方法によれば、少なくとも第1および第2のアドレス信号によってアドレス指定される第1の記憶手段に、入力画像が記憶されるとともに、入力画像から、その入力画像を構成する画素数よりも多い画素数で構成される画像である多画素数画像が生成され、少なくとも第1および第2のアドレス信号によってアドレス指定される第2の記憶手段に、多画素数画像が記憶される。そして、第1の記憶手段に記憶された入力画像、および第2の記憶手段に記憶された多画素数画像のうちのいずれを読み出すかを指示するフラグに基づいて、第1の記憶手段に記憶された入力画像、または第2の記憶手段に記憶された多画素数画像が出力される。さらに、入力画像を構成する画素から多画素数画像を構成する画素を生成する複数の画素生成手段であって、入力画像を構成する画素数に対する多画素数画像を構成する画素数に応じた個数の画素生成手段が用いられて、多画素数画像が生成される。従って、例えば、入力画像を拡大したものを、即座に提供することが可能となる。

【図面の簡単な説明】

【図1】本発明を適用した記憶装置の一実施の形態の構成例を示すブロック図である。

【図2】図1の記憶装置に入力される入力画像を示す図である。

【図3】図1の多画素数画像生成回路3の処理を説明するための図である。

【図4】多画素数画像を示す図である。

【図5】図1の記憶装置の第1の詳細構成例を示すブロック図である。

【図6】図1の記憶装置の第2の詳細構成例を示すブロック図である。

【図7】図1の多画素数画像生成回路3の詳細構成例を示すブロック図である。

【図8】図7のクラス分類用ブロック化回路41および予測値計算用ブロック化回路42の処理を説明するための図である。

【図9】クラス分類処理を説明するための図である。

【図10】ADRC処理を説明するための図である。

【図11】予測係数を求める学習処理を行う画像処理装置の構成例を示すブロック図である。

【符号の説明】

1 アドレス供給回路, 2 入力画像メモリ(第1の記憶手段), 3 多画素数画像生成回路(生成手段), 4 多画素数画像メモリ(第2の記憶手段), 5 RMW回路, 11,11a乃至11d 遅延回路, 12a乃至12d 画素生成回路, 13a乃至13d メモリ, 21 カウンタ, 22メモリ, 41 クラス分類用ブロック化回路, 42 予測値計算用ブロック化回路, 43 クラス分類適応処理回路, 44 ADRC処理回路, 45 クラス分類回路, 46 予測係数ROM, 47 予測回路, 91 学習用ブロック化回路, 92 教師用ブロック化回路, 93 ADRC処理回路, 94 クラス分類回路, 95 スイッチ, 96 学習データメモリ,97 カウンタ, 98 教師データメモリ, 99 演算回路, 100 メモリ

Claims (5)

- 画像を記憶する記憶装置であって、

少なくとも第1および第2のアドレス信号によってアドレス指定され、入力画像を記憶する第1の記憶手段と、

前記入力画像から、その入力画像を構成する画素数よりも多い画素数で構成される画像である多画素数画像を生成する生成手段と、

少なくとも前記第1および第2のアドレス信号によってアドレス指定され、前記多画素数画像を記憶する第2の記憶手段と、

前記第1の記憶手段に記憶された入力画像、および前記第2の記憶手段に記憶された多画素数画像のうちのいずれを読み出すかを指示するフラグに基づいて、前記第1の記憶手段に記憶された入力画像、または前記第2の記憶手段に記憶された多画素数画像を出力する出力手段と

を備え、

前記生成手段は、前記入力画像を構成する画素から前記多画素数画像を構成する画素を生成する複数の画素生成手段であって、前記入力画像を構成する画素数に対する前記多画素数画像を構成する画素数に応じた個数の前記画素生成手段を用いて、前記多画素数画像を生成する

ことを特徴とする記憶装置。 - 前記第2の記憶手段は、少なくとも前記第1および第2のアドレス信号と、それに付加される付加アドレス信号とによってアドレス指定される

ことを特徴とする請求項1に記載の記憶装置。 - 前記生成手段は、前記入力画像を構成する複数の画素を用いて重み付け加算を行うことにより、前記多画素数画像を構成する1の画素を生成する

ことを特徴とする請求項1に記載の記憶装置。 - 前記生成手段は、前記入力画像を構成する画素との線形結合により前記多画素数画像を構成する画素の予測値を算出するための予測係数を用いて、前記多画素数画像を生成する

ことを特徴とする請求項1に記載の記憶装置。 - 少なくとも第1および第2のアドレス信号によってアドレス指定される第1の記憶手段に、入力画像を記憶させる第1の記憶ステップと、

前記入力画像から、その入力画像を構成する画素数よりも多い画素数で構成される画像である多画素数画像を生成する生成ステップと、

少なくとも前記第1および第2のアドレス信号によってアドレス指定される第2の記憶手段に、前記多画素数画像を記憶させる第2の記憶ステップと、

前記第1の記憶手段に記憶された入力画像、および前記第2の記憶手段に記憶された多画素数画像のうちのいずれを読み出すかを指示するフラグに基づいて、前記第1の記憶手段に記憶された入力画像、または前記第2の記憶手段に記憶された多画素数画像が出力される出力ステップと

を有し、

前記生成ステップでは、前記入力画像を構成する画素から前記多画素数画像を構成する画素を生成する複数の画素生成手段であって、前記入力画像を構成する画素数に対する前記多画素数画像を構成する画素数に応じた個数の前記画素生成手段が用いられて、前記多画素数画像が生成される

ことを特徴とする記憶方法。

Priority Applications (10)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP20437297A JP4105257B2 (ja) | 1997-07-30 | 1997-07-30 | 記憶装置および記憶方法 |

| US09/121,417 US6278806B1 (en) | 1997-07-30 | 1998-07-23 | Storage apparatus and storage method |

| SG9802661A SG87004A1 (en) | 1997-07-30 | 1998-07-24 | Storage apparatus and storage method |

| DE1998633836 DE69833836T2 (de) | 1997-07-30 | 1998-07-29 | Verfahren und Gerät zur massstäblichen Umformung von Bildern |

| ES98306041T ES2256921T3 (es) | 1997-07-30 | 1998-07-29 | Metodo y aparato para ampliar imagenes. |

| EP19980306041 EP0895188B1 (en) | 1997-07-30 | 1998-07-29 | Method and apparatus for image scaling |

| AU78587/98A AU749662B2 (en) | 1997-07-30 | 1998-07-29 | Storage apparatus and storage method |

| KR1019980030780A KR100591867B1 (ko) | 1997-07-30 | 1998-07-30 | 기억장치및기억방법 |

| CNB981203256A CN1139897C (zh) | 1997-07-30 | 1998-07-30 | 存储装置和存储方法 |

| HK99103529A HK1019254A1 (en) | 1997-07-30 | 1999-08-13 | Storage device and storage method. |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP20437297A JP4105257B2 (ja) | 1997-07-30 | 1997-07-30 | 記憶装置および記憶方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH1153529A JPH1153529A (ja) | 1999-02-26 |

| JP4105257B2 true JP4105257B2 (ja) | 2008-06-25 |

Family

ID=16489434

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP20437297A Expired - Fee Related JP4105257B2 (ja) | 1997-07-30 | 1997-07-30 | 記憶装置および記憶方法 |

Country Status (10)

| Country | Link |

|---|---|

| US (1) | US6278806B1 (ja) |

| EP (1) | EP0895188B1 (ja) |

| JP (1) | JP4105257B2 (ja) |

| KR (1) | KR100591867B1 (ja) |

| CN (1) | CN1139897C (ja) |

| AU (1) | AU749662B2 (ja) |

| DE (1) | DE69833836T2 (ja) |

| ES (1) | ES2256921T3 (ja) |

| HK (1) | HK1019254A1 (ja) |

| SG (1) | SG87004A1 (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2000016260A1 (fr) | 1998-09-11 | 2000-03-23 | Sony Corporation | Processeur de donnees et procede de conversion de sequences de donnees |

| CN1190063C (zh) * | 1999-03-24 | 2005-02-16 | 松下电器产业株式会社 | 图像处理装置及处理方法 |

| JP4055203B2 (ja) | 2002-09-12 | 2008-03-05 | ソニー株式会社 | データ処理装置およびデータ処理方法、記録媒体、並びにプログラム |

| US20070195887A1 (en) * | 2004-09-29 | 2007-08-23 | Comer Mary L | Method and apparatus for reduced resolution update video coding and decoding |

| JP4417230B2 (ja) | 2004-11-24 | 2010-02-17 | 本田技研工業株式会社 | 車両用灯火装置 |

| CN103596011B (zh) * | 2013-11-20 | 2017-07-04 | 北京中星微电子有限公司 | 图像数据的存储处理方法和装置 |

| US10636336B2 (en) * | 2015-04-17 | 2020-04-28 | Nvidia Corporation | Mixed primary display with spatially modulated backlight |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62200976A (ja) | 1986-02-28 | 1987-09-04 | Dainippon Screen Mfg Co Ltd | 高分解能2値化画像出力装置 |

| JPS6381688A (ja) * | 1986-09-26 | 1988-04-12 | Hitachi Ltd | 半導体記憶装置 |

| US5070465A (en) * | 1987-02-25 | 1991-12-03 | Sony Corporation | Video image transforming method and apparatus |

| JPH02253765A (ja) | 1989-03-28 | 1990-10-12 | Toshiba Corp | 画像処理装置 |

| US5325189A (en) * | 1989-05-23 | 1994-06-28 | Canon Kabushiki Kaisha | Image processing with a multiple-memory apparatus |

| WO1994014138A1 (en) | 1992-06-10 | 1994-06-23 | Guissin, David | Apparatus and methods for smoothing images |

| JPH06167966A (ja) * | 1992-06-15 | 1994-06-14 | Seiko Epson Corp | 表示回路 |

| US5585864A (en) | 1992-06-24 | 1996-12-17 | Seiko Epson Corporation | Apparatus for effecting high speed transfer of video data into a video memory using direct memory access |

| US5270813A (en) | 1992-07-02 | 1993-12-14 | At&T Bell Laboratories | Spatially scalable video coding facilitating the derivation of variable-resolution images |

| JP3362463B2 (ja) * | 1993-07-09 | 2003-01-07 | ソニー株式会社 | フレーム補間装置 |

| EP0671852B1 (en) | 1993-08-30 | 2001-11-07 | Sony Corporation | Device and method for encoding image data |

| JP3227931B2 (ja) * | 1993-09-10 | 2001-11-12 | ソニー株式会社 | 符号化装置および復号化装置 |

| JP3590996B2 (ja) | 1993-09-30 | 2004-11-17 | ソニー株式会社 | ディジタル画像信号の階層符号化および復号装置 |

| US5473342A (en) | 1993-10-19 | 1995-12-05 | Chrontel, Inc. | Method and apparatus for on-the-fly multiple display mode switching in high-resolution bitmapped graphics system |

| US5517612A (en) | 1993-11-12 | 1996-05-14 | International Business Machines Corporation | Device for scaling real-time image frames in multi-media workstations |

| JP3336544B2 (ja) * | 1994-04-25 | 2002-10-21 | 富士写真フイルム株式会社 | デジタル画像処理装置 |

| JPH0837662A (ja) * | 1994-07-22 | 1996-02-06 | Hitachi Ltd | 画像符号化復号化装置 |

| JP2956527B2 (ja) * | 1995-04-28 | 1999-10-04 | 松下電器産業株式会社 | 画像メモリ機能付き映像装置 |

| JP3870428B2 (ja) * | 1995-05-10 | 2007-01-17 | ソニー株式会社 | 画像情報変換装置および方法並びに係数データ生成装置および方法 |

| JP3724008B2 (ja) * | 1995-05-23 | 2005-12-07 | ソニー株式会社 | 画像情報変換装置および係数データ作成装置 |

| US5959676A (en) | 1995-12-27 | 1999-09-28 | Sony Corporation | Video signal encoding method, video signal encoding apparatus, video signal transmitting method, and recording medium |

| US5950223A (en) * | 1997-06-19 | 1999-09-07 | Silicon Magic Corporation | Dual-edge extended data out memory |

-

1997

- 1997-07-30 JP JP20437297A patent/JP4105257B2/ja not_active Expired - Fee Related

-

1998

- 1998-07-23 US US09/121,417 patent/US6278806B1/en not_active Expired - Fee Related

- 1998-07-24 SG SG9802661A patent/SG87004A1/en unknown

- 1998-07-29 ES ES98306041T patent/ES2256921T3/es not_active Expired - Lifetime

- 1998-07-29 AU AU78587/98A patent/AU749662B2/en not_active Ceased

- 1998-07-29 DE DE1998633836 patent/DE69833836T2/de not_active Expired - Lifetime

- 1998-07-29 EP EP19980306041 patent/EP0895188B1/en not_active Expired - Lifetime

- 1998-07-30 CN CNB981203256A patent/CN1139897C/zh not_active Expired - Fee Related

- 1998-07-30 KR KR1019980030780A patent/KR100591867B1/ko not_active IP Right Cessation

-

1999

- 1999-08-13 HK HK99103529A patent/HK1019254A1/xx not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| DE69833836D1 (de) | 2006-05-11 |

| EP0895188A2 (en) | 1999-02-03 |

| AU7858798A (en) | 1999-02-11 |

| EP0895188B1 (en) | 2006-03-15 |

| US6278806B1 (en) | 2001-08-21 |

| DE69833836T2 (de) | 2007-01-11 |

| SG87004A1 (en) | 2002-03-19 |

| JPH1153529A (ja) | 1999-02-26 |

| HK1019254A1 (en) | 2000-03-31 |

| KR100591867B1 (ko) | 2007-04-25 |

| KR19990014287A (ko) | 1999-02-25 |

| CN1208906A (zh) | 1999-02-24 |

| EP0895188A3 (en) | 2000-01-12 |

| ES2256921T3 (es) | 2006-07-16 |

| AU749662B2 (en) | 2002-07-04 |

| CN1139897C (zh) | 2004-02-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US5517588A (en) | Digital data conversion equipment and a method for the same | |

| JP4126709B2 (ja) | 画像処理装置および画像処理方法 | |

| JPH11191880A (ja) | 画像変換装置および画像変換方法、並びに学習装置および学習方法 | |

| JP3912627B2 (ja) | 画像符号化装置および画像符号化方法、並びに伝送方法 | |

| JP4147632B2 (ja) | 画像情報変換装置、画像情報変換方法、およびテレビジョン受像機 | |

| JP4224876B2 (ja) | 記憶装置、並びに書き込み方法および読み出し方法 | |

| JP3787823B2 (ja) | 画像処理装置および画像処理方法 | |

| JP4105257B2 (ja) | 記憶装置および記憶方法 | |

| JPH0779418A (ja) | 画像信号変換装置 | |

| EP0972270B1 (en) | A storage apparatus and writing and/or reading methods for use in hierarchical coding | |

| US6873738B2 (en) | Hierarchical image processor for encoding or decoding, and memory on the same chip | |

| JP2001222702A (ja) | 画像処理装置および画像処理方法、並びに記録媒体 | |

| JP3723995B2 (ja) | 画像情報変換装置および方法 | |

| JP3912558B2 (ja) | 画像符号化装置および画像符号化方法、並びに記録媒体 | |

| JP3784086B2 (ja) | 映像信号符号化・復号化装置及び符号化・復号化方法 | |

| JP3702508B2 (ja) | ディジタル画像信号用のメモリ装置 | |

| JP4166292B2 (ja) | ディジタル画像信号用のメモリ装置、書込み方法および読出し方法 | |

| JP3907623B2 (ja) | 映像信号符号化・復号化装置及び符号化・復号化方法 | |

| JP4534951B2 (ja) | 画像符号化装置および画像符号化方法、画像処理システムおよび画像処理方法、伝送方法、並びに記録媒体 | |

| JP4062326B2 (ja) | 係数生成装置および方法 | |

| JP4487900B2 (ja) | 画像処理システム | |

| JP3988738B2 (ja) | 画像変換装置および画像変換方法 | |

| JPH1093981A (ja) | 画像符号化装置および画像符号化方法、画像復号化装置および画像復号化方法、伝送方法、並びに記録媒体 | |

| JP4042121B2 (ja) | 画像情報処理装置及び画像情報処理方法 | |

| JP2000004436A (ja) | 画像処理装置および画像処理方法、並びに伝送媒体および伝送方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20050913 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20050916 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20051111 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20060307 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060502 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20060524 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20060616 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080327 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110404 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120404 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120404 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130404 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130404 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140404 Year of fee payment: 6 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |