JP4073176B2 - 半導体装置およびその製造方法 - Google Patents

半導体装置およびその製造方法 Download PDFInfo

- Publication number

- JP4073176B2 JP4073176B2 JP2001103197A JP2001103197A JP4073176B2 JP 4073176 B2 JP4073176 B2 JP 4073176B2 JP 2001103197 A JP2001103197 A JP 2001103197A JP 2001103197 A JP2001103197 A JP 2001103197A JP 4073176 B2 JP4073176 B2 JP 4073176B2

- Authority

- JP

- Japan

- Prior art keywords

- groove

- film

- silicon oxide

- electrode film

- inner peripheral

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 104

- 238000004519 manufacturing process Methods 0.000 title claims description 32

- 230000002093 peripheral effect Effects 0.000 claims description 60

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 54

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 54

- 239000000758 substrate Substances 0.000 claims description 33

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 14

- 229920005591 polysilicon Polymers 0.000 claims description 14

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 13

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 13

- 238000000151 deposition Methods 0.000 claims description 3

- 230000001590 oxidative effect Effects 0.000 claims 1

- 239000010408 film Substances 0.000 description 267

- 239000010410 layer Substances 0.000 description 91

- 229920002120 photoresistant polymer Polymers 0.000 description 18

- 238000009792 diffusion process Methods 0.000 description 13

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 11

- 229910052710 silicon Inorganic materials 0.000 description 11

- 239000010703 silicon Substances 0.000 description 11

- 239000011229 interlayer Substances 0.000 description 8

- 238000010586 diagram Methods 0.000 description 7

- 238000001312 dry etching Methods 0.000 description 6

- -1 boron ions Chemical class 0.000 description 4

- 238000002474 experimental method Methods 0.000 description 4

- 238000000034 method Methods 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- 229910052796 boron Inorganic materials 0.000 description 3

- 238000009413 insulation Methods 0.000 description 3

- 230000003647 oxidation Effects 0.000 description 3

- 238000007254 oxidation reaction Methods 0.000 description 3

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000005684 electric field Effects 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- 239000012141 concentrate Substances 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 239000005368 silicate glass Substances 0.000 description 1

- GECHUMIMRBOMGK-UHFFFAOYSA-N sulfapyridine Chemical compound C1=CC(N)=CC=C1S(=O)(=O)NC1=CC=CC=N1 GECHUMIMRBOMGK-UHFFFAOYSA-N 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/7813—Vertical DMOS transistors, i.e. VDMOS transistors with trench gate electrode, e.g. UMOS transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/739—Transistor-type devices, i.e. able to continuously respond to applied control signals controlled by field-effect, e.g. bipolar static induction transistors [BSIT]

- H01L29/7393—Insulated gate bipolar mode transistors, i.e. IGBT; IGT; COMFET

- H01L29/7395—Vertical transistors, e.g. vertical IGBT

- H01L29/7396—Vertical transistors, e.g. vertical IGBT with a non planar surface, e.g. with a non planar gate or with a trench or recess or pillar in the surface of the emitter, base or collector region for improving current density or short circuiting the emitter and base regions

- H01L29/7397—Vertical transistors, e.g. vertical IGBT with a non planar surface, e.g. with a non planar gate or with a trench or recess or pillar in the surface of the emitter, base or collector region for improving current density or short circuiting the emitter and base regions and a gate structure lying on a slanted or vertical surface or formed in a groove, e.g. trench gate IGBT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42364—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the insulating layer, e.g. thickness or uniformity

- H01L29/42368—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the insulating layer, e.g. thickness or uniformity the thickness being non-uniform

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42372—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the conducting layer, e.g. the length, the sectional shape or the lay-out

- H01L29/4238—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the conducting layer, e.g. the length, the sectional shape or the lay-out characterised by the surface lay-out

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Electrodes Of Semiconductors (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Description

【発明の属する分野】

本発明は、半導体装置とその製造法に係り、特に電源回路等に利用されるトレンチゲート型パワーMOSFETの構成を有する半導体装置およびその製造方法に関するものである。

【0002】

【従来の技術】

トレンチゲート型パワーMOSFETは、近年、DC−DCコンバータなど各種電源装置に幅広く応用されている。図34は、従来技術に係るトレンチゲート型パワーMOSFETの構成を有する半導体装置の一例を示す説明図であり、(a)は半導体装置の平面図であり、(b)はA−A線断面図である。図中、100a〜100eはセル、110は溝、111はゲート電極膜、117はN+型シリコン基板、118はN−エピタキシャル層、119はP型ボディ層、120はP+型拡散領域、121はN+型ソース領域、122は層間絶縁膜、124はソース電極膜、125はドレイン電極膜、127はゲート絶縁膜、141は上部絶縁膜である。

【0003】

この半導体装置は、図34(a)のセル100a〜100eに示すように、表面側に多数のセルを千鳥格子状に配置形成している。さらに、各セルは、例えばセル100aに示したように、P+型拡散領域120の周辺にN+型ソース領域121を形成している。

【0004】

また、この半導体装置の断面の構成は、図34(b)に示すように、N+型シリコン基板117上に、ドレイン層としてN−エピタキシャル層118を形成し、さらにN−エピタキシャル層118上にP型ボディ層119を形成している。P型ボディ層119の内部には、P+型拡散領域120およびN+型ソース領域121を形成している。さらに、セル100a〜100eの間は、P型ボディ層119を貫通してN−エピタキシャル層118内まで達する溝110を形成している。

【0005】

溝110は、P型ボディ層119を開口させて、N−エピタキシャル層118内部にまで到達するように形成されている。この溝110の内周面および底面には、ゲート絶縁膜127を密着形成しており、さらにゲート絶縁膜127に囲まれる空間内にゲート電極膜111を形成している。くわえて、ゲート絶縁膜127およびゲート電極膜111上には上部絶縁膜141を形成している。さらに、上部絶縁膜141およびN+型ソース領域121の一部の上には、層間絶縁膜122を形成している。

【0006】

さらに、上述のP+型拡散領域120、N+型ソース領域121および層間絶縁膜122上には、ソース電極膜124を形成している。くわえて、N+型シリコン基板117のもう一方の面にはドレイン電極膜125を形成している。

【0007】

上述の半導体装置において、ソース電極膜124とドレイン電極膜125との間に電圧を印加するとともに、ゲート電極膜111とソース電極膜124との間に所定閾値以上の電圧を印加すると、P型ボディ層119のゲート絶縁膜127との境界領域に反転層が形成されてチャネルとなる。そして、ドレイン電極膜125からソース電極124へこのチャネルを通って電流が流れる。

【0008】

ところで、このような構成を有する半導体装置においては、ゲート絶縁膜127の底部の膜厚を他の部分よりも厚く形成してゲート絶縁膜127の絶縁耐圧を確保するために、溝110を深く掘り下げることによって図28(b)に示した溝110の深さDを大きくし、ゲート絶縁膜127の底部の膜厚を確保するためのスペースを作るようにしている。また、溝110を深く掘り下げれば、ゲート絶縁膜127の外周面の面積を増やすことができるので、オン抵抗Ronを下げることもできる。

【0009】

しかし、ゲート絶縁膜127の外周面の面積を大きくすると、ゲート電極膜111とN−エピタキシャル層118との間の静電容量Crssも大きくなり、半導体装置のスイッチング特性が悪化することになる。また、深さDを大きくして行くと、ソース電極膜124とドレイン電極膜125との間に電圧を印加したときに、ゲート絶縁膜127の特定の部分に電界が集中するなどの悪影響を招くことになる。

【0010】

【発明が解決しようとする課題】

本発明は、上述の課題を解決するために、オン抵抗を低くしつつゲート電極膜とドレイン層との間の静電容量を小さくでき、かつゲート絶縁膜の絶縁耐圧を確保することが可能な半導体装置を提供することを目的とするものである。

【0013】

【課題を解決するための手段】

また、本発明は、半導体装置において、第1導電型のドレイン層と、該ドレイン層上に配置される該第1導電型とは反対型の第2導電型の導電領域とを形成してなる半導体基板と、前記導電領域を開口し、前記ドレイン層に達して形成してなる溝と、前記導電領域内に配置されるとともに、少なくとも一部を前記溝の内周面に露出させて形成してなる第1導電型のソース領域と、前記溝の内周面に形成されるとともに、所定深さより深い部分の膜厚を他の部分より厚く形成してなるゲート絶縁膜と、前記ゲート絶縁膜の内周面に形成してなるゲート電極膜と、前記ゲート電極膜とは絶縁されるとともに、前記ソース領域と接して形成してなるソース電極膜と、を有し、前記所定深さは、前記ソース領域よりも深くかつ前記ドレイン層と前記導電領域との境界面よりも浅い範囲内であることを特徴とした。

【0014】

したがって、本発明に係る半導体装置は、所定深さより深い部分のゲート電極膜の膜厚が他の部分、すなわち所定深さより浅い部分よりも薄くなるので、当該部分周辺の静電容量を低く押さえるとともに、オン抵抗を一定程度低減することができる。

【0016】

また、本発明は、半導体装置において、第1導電型のドレイン層と、該ドレイン層上に配置される該第1導電型とは反対型の第2導電型の導電領域とを形成してなる半導体基板と、前記導電領域を開口し、前記ドレイン層に達して形成してなる溝と、前記導電領域内に配置されるとともに、少なくとも一部を前記溝の内周面に露出して形成させてなる第1導電型のソース領域と、前記溝の内周面に形成されてなるとともに、前記導電領域の開口側に行くに従って膜厚が薄くなるように形成してなるゲート絶縁膜と、前記ゲート絶縁膜の内周面に形成してなるゲート電極膜と、前記ゲート電極膜とは絶縁されるとともに、前記ソース領域と接して形成してなるソース電極膜とを有することを特徴とするものとした。

【0017】

したがって、本発明に係る半導体装置は、所定深さより深い部分のゲート電極膜の膜厚が他の部分、すなわち所定深さより浅い部分よりも薄くなるので、当該部分周辺の静電容量を低く押さえるとともに、オン抵抗を一定程度低減することができる。

【0018】

また、半導体装置の製造方法において、第1導電型のドレイン層を形成した半導体基板の表面上に第1のシリコン酸化膜を形成し、前記シリコン酸化膜の所定部位を開口させて前記ドレイン層を露出させ、露出した前記ドレイン層を開口させて前記ドレイン層に第1の溝を形成し、前記半導体基板の表面および前記第1の溝の内周面に第2のシリコン酸化膜を形成し、前記半導体基板の表面および前記第1の溝の内周面を覆うシリコン窒化膜を形成し、前記半導体基板の表面および前記第1の溝の底面の前記シリコン窒化膜を除去し、前記半導体基板の表面および前記第1の溝の底面の前記第2のシリコン酸化膜を露出させ、前記第1のシリコン酸化膜および前記第2のシリコン酸化膜の少なくとも一部、ならびに前記第1の溝の底面に露出した前記シリコン酸化膜を除去し、前記第1の溝の底面の前記ドレイン層を露出させ、前記第1の溝の底面に露出した前記ドレイン層を開口して第2の溝を形成し、前記第2の溝周辺の前記ドレイン層を酸化し、前記第1の溝の周側面の前記シリコン窒化膜および前記第2のシリコン酸化膜を除去し、前記半導体基板の表面ならびに前記第1の溝および前記第2の溝の内周面に第3のシリコン酸化膜を形成し、前記半導体基板の表面および前記第1の溝ならびに前記第2の溝の内周面にポリシリコン膜を堆積形成し、前記第1の溝ならびに前記第2の溝を埋め、前記半導体基板の表面の前記ポリシリコン膜および前記第1の溝の一部の前記ポリシリコン膜を除去し、前記半導体基板の表面および前記第1の溝の内周面の一部の前記第3のシリコン酸化膜を除去し、前記半導体基板の表面ならびに前記第1の溝の内周面に第4のシリコン酸化膜を形成することを特徴とするものとした。

【0019】

したがって、第1の溝の底部に第2の溝を形成することが可能になり、上部と下部とで膜厚のことなるゲート電極膜を形成することが可能になる。

【0020】

【発明の実施の形態】

以下に本発明の第1の実施の形態に係る半導体装置を図面に基づいて詳細に説明する。図1は、本発明の第1の実施の形態に係る半導体装置を示す説明図であり、(a)は半導体装置のセルの配置を示す平面図であり、(b)はB−B線断面図である。図中、1a〜1eはセル、10は溝、11はゲート電極膜、15は周側面部、16は底面部、17はN+型シリコン基板、18はN−エピタキシャル層、19はP型ボディ層、20はP+型拡散領域、21はN+型ソース領域、22は層間絶縁膜、24はソース電極膜、25はドレイン電極膜、27はゲート絶縁膜、41は上部絶縁膜である。

【0021】

本発明の第1の実施の形態に係る半導体装置の構造は、図1(a)に示すように、平面構成においてセル1a〜1eなどの各セルを千鳥格子状に配置している。さらに、セル1aなど各セルは、P+型拡散領域20の周辺にN+型ソース領域21を形成している。なお、セル1a〜1eの配置は、図1(a)のパターンに限られるものではなく、例えば図27に示すようにしてもよい。図27は、セルの別の配置の一例を示す平面図である。セル1a,1bなどの各セルは、P+型拡散領域20およびN+型ソース領域21をそれぞれ短冊状に形成し、これらを平行に配置した例である。本実施の形態においては、セルを円形などさらに別の形状とし、また配置についても格子状など他の配置にしてもよい。

【0022】

また、図1(b)に示すように、この半導体装置の断面構造においては、N+型シリコン基板17上に、ドレイン層であるN−エピタキシャル層18を形成している。さらに、N−エピタキシャル層18上に、P型ボディ層19を形成している。また、P型ボディ層19の内部には、P+型拡散領域20およびN+型ソース領域21を形成してセル1aを設けている。

【0023】

さらに、P型ボディ層19を開口させて、N−エピタキシャル層18内部の比較的浅い部位に到達するように溝10を形成している。溝10の周側面および底面には、ゲート絶縁膜27を密着形成されている。このゲート絶縁膜27は、その底面部16の膜厚を周側面部15のそれよりも厚く形成している。また、ゲート絶縁膜27の底面部16の上面が、N−エピタキシャル層18とP型ボディ層19との境界面より浅くなるように形成している。さらに、ゲート絶縁膜27の内部空間には、この内部空間を充填するようにゲート電極膜11を堆積形成している。よって、ゲート電極膜11は、N−エピタキシャル層18とP型ボディ層19との境界面より浅い部位に形成される。くわえて、ゲート電極膜11の上には、上部絶縁膜41を形成している。

【0024】

また、ゲート絶縁膜27上には、層間絶縁膜22を形成している。くわえて、P+型拡散領域20およびN+型ソース領域21ならびに層間絶縁膜22上には、ソース電極膜24を形成している。さらに、N+型シリコン基板17のもう一方の面には、ドレイン電極膜25を形成している。

【0025】

そして、この半導体装置において、ソース電極膜24とドレイン電極膜25との間に電圧を印加するとともに、ゲート電極膜11とソース電極膜24との間に所定閾値以上の電圧を印加すると、P型ボディ層19のゲート絶縁膜27との境界領域に反転層が形成されてチャネルとなる。そして、ドレイン電極膜25からソース電極膜24へこのチャネルを通って電流が流れる。また、ゲート電極膜11とソース電極膜24との間の電圧を所定閾値より低くすれば、この反転層が消滅して、ドレイン電極膜25とソース電極膜24との間に電流は流れない。

【0026】

また、本発明の第1の実施の形態に係る半導体装置においては、ゲート電極膜11をN−エピタキシャル層18とP型ボディ層19との境界面より浅く、すなわちゲート電極膜11の下端部がN−エピタキシャル層18とP型ボディ層19との境界面よりも上方に位置するように形成している。したがって、溝10をN−エピタキシャル層18の比較的浅い部位に達する程度に形成しても、ゲート絶縁膜27の底面部16の膜厚を厚くして、ゲート絶縁膜27の絶縁耐圧を十分に確保することが可能である。さらに、溝10を浅く形成できるので、ゲート絶縁膜27の特定の部分に電界が集中するような事態を回避することができる。

【0027】

また、ゲート電極膜11の下端部をN−エピタキシャル層18とP型ボディ層19との境界面よりも上方に位置させても、オン抵抗Ronを十分に引き下げることが可能である。図28は、本発明の第1の実施の形態に係る半導体装置の実験例を示す説明図である。図中、Aは溝10の幅、BはP型ボディ層19の厚さ、Cは溝10の深さ、Dはゲート絶縁膜27の周側面部15の厚さ、Xは半導体装置の表面からゲート電極膜11の下端部までの深さを示す変数である。なお、他の符号は、図1のものと同じである。図28に示した実験例においては、Aを0.8μm、Bを1.3μm、Cを1.6μm、Dを50nmとした。そして、オン抵抗Ronの測定においては、ソース電極膜24とドレイン電極膜25との間に10V印加するとともに、ゲート電極膜11とソース電極膜24との間にも10V印加し、静電容量Cissの測定においては、それぞれ0V、10Vずつ印加するものとした。

【0028】

図31は、本発明の第1の実施の形態に係る半導体装置の実験例におけるオン抵抗Ronと静電容量Cissとの関係を示す説明図である。この図においては、Xを1.55μmとしたときのオン抵抗Ronと静電容量Cissとの積を1.0としている。なお、上記の実験および以下に述べる実験においては、Crs sではなくCissを測定対象としているが、これらの実験条件ではCGSはほぼ一定となり、Ciss=CGS+CGD、Crss=CGDの関係にあることを勘案すれば、X、Y、Zの各変数に対するCissの変化をCrssの変化と見なせるのでCissを用いた。

【0029】

図31に示すように、図28の構成において、オン抵抗Ronと静電容量Cissとの積は、Xをほぼ1.0μmないし1.2μmの範囲とした場合が最も小さくなる。したがって、ゲート電極膜11の深さは、この範囲、すなわちゲート電極膜11の下端部がN−エピタキシャル層18とP型ボディ層19との境界面よりも上方に位置させることが有利と言える。

【0030】

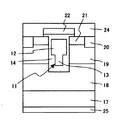

さらに、本発明の第2の実施の形態に係る半導体装置を図面に基づいて詳細に説明する。図2は、本発明の第2の実施の形態に係る半導体装置を示す断面図である。図中、12はゲート電極膜上部、13はゲート電極膜下部、14は下側周側面部、29は上側周側面部である。その他の符号は、図1のものと同じである。

【0031】

本発明の第2の実施の形態に係る半導体装置の断面構造は、図2に示すように、ゲート絶縁膜27において下側周側面部14の膜厚を上側周側面部29の膜厚よりも厚くしている。したがって、ゲート電極膜上部12の膜厚は、ゲート電極膜下部13の膜厚よりも厚くなっている。その他の部分の構造は、上述の第1の実施の形態のものと同じである。

【0032】

したがって、本発明の第2の実施の形態においては、ゲート絶縁膜27の底面部16の膜厚に加えて、下側周側面部14の膜厚も他の部分より厚く形成することにより、本発明の第1の実施の形態よりもオン抵抗Ronの低減させている。なお、本発明の第2の実施の形態においては、ゲート電極膜上部12をN−エピタキシャル層18とP型ボディ層19との境界面よりも上方に位置させるとともに、ゲート電極膜下部13の下端部がこの境界面よりも下方に位置するように形成してもよい。また、ゲート電極膜下部13は、例えば中間部分の膜厚を上下端部よりも厚くしたり、漏斗状やドーム状に形成するなど他の形態にしても良い。

【0033】

以下に、本発明の第2の実施の形態に係る半導体装置の2つの実験例について説明する。図29は、本発明の第2の実施の形態に係る半導体装置の第1の実験例を示す説明図である。図中、Dはゲート電極膜上部12に接するゲート絶縁膜27の上側周側面部29の厚さ、Eはゲート電極膜下部13の下端部と溝10の底面との距離、Fはゲート電極膜下部13の周側面と溝10の周側面との距離、Yは半導体装置の表面からゲート電極膜上部12の下端部までの深さを示す変数である。なお、他の符号は、図28のものと同じである。図29に示した実験例においては、Aを0.8μm、Bを1.3μm、Cを1.6μm、Dを50nm、EおよびFを0.25μmとした。この構成において、ソース電極膜24とドレイン電極膜25との間、およびゲート電極膜11とソース電極膜24との間に、図28に示した実験と同様の電圧を印加した。

【0034】

図32は、本発明の第2の実施の形態に係る半導体装置の第1の実験例におけるオン抵抗Ronと静電容量Cissとの関係を示す説明図である。この図においては、オン抵抗Ronと静電容量Cissとの積を示す指標値は、図28における実験例と同じ数値を示すものである。図32に示すように、図29の構成において、オン抵抗Ronと静電容量Cissとの積は、Yをほぼ0.8μmないし1.0μmの範囲とした場合が最も小さくなる。また、この値は、第1の実施の形態に係る実験例における値よりもわずかに小さい。したがって、ゲート電極膜11の中段近傍に段差を設け、ゲート電極膜上部12の下端部の深さを溝10の深さに対して概ね50%〜60%程度にした場合には、製造工程が複雑にはなるが、図31に示した例よりもさらに好適なものが得られる。

【0035】

図30は、本発明の第2の実施の形態に係る半導体装置の第2の実験例を示す説明図である。図中、Gはゲート電極膜11の長さ、Zはゲート電極膜上部12とゲート電極膜下部13との水平方向の膜厚差を示す変数である。なお、他の符号は、図29のものと同じである。図30に示した実験例においては、Aを0.8μm、Bを1.3μm、Cを1.6μm、Dを50nm、Eを0.25μmとした。したがって、この実験例では、ゲート電極膜上部12の下端部は、N−エピタキシャル層18とP型ボディ層19との境界面よりも上方に位置しているが、ゲート電極膜下部13の下端部はこの境界面よりも下方に位置している。この構成において、ソース電極膜24とドレイン電極膜25との間、およびゲート電極膜11とソース電極膜24との間に、図28に示した実験と同様の電圧を印加した。

【0036】

図33は、本発明の第2の実施の形態に係る半導体装置の第2の実験例におけるオン抵抗Ronと静電容量Cissとの関係を示す説明図である。図33に示すように、図30の構成において、オン抵抗Ronと静電容量Cissとの積は、Zをほぼ0.1μmないし0.3μmの範囲とした場合が最も小さくなる。したがって、ゲート電極膜上部12の膜厚に対してゲート電極膜下部13の膜厚を概ね30〜85%程度とすることが最も好ましいと言える。また、この実験例においては、ゲート電極膜下部13の下端部がN−エピタキシャル層18とP型ボディ層19との境界面よりも下方に位置しているが、オン抵抗Ronと静電容量Cissとの積から判断する限り、実験例1に対して特段不利になることはなかった。したがって、ゲート電極膜11は、オン抵抗Ronと静電容量Cissの双方を勘案する場合、その長さを溝10の深さに対して概ね50%〜60%程度とし、中段付近に段差を設け、ゲート電極膜上部12の膜厚に対してゲート電極膜下部13の膜厚を概ね30〜85%程度とすることが最も好ましいと言える。

【0037】

さらに、本発明の第2の実施の形態に係る半導体装置の製造工程について説明する。図5〜図26は、本発明の第2の実施の形態に係る半導体装置の製造工程を説明する断面図(a)〜本発明の第2の実施の形態に係る半導体装置の製造工程を説明する断面図(v)である。これらの図中、31,36,41,42はシリコン酸化膜、32,45はフォトレジスト膜、33,34は開口部、35は溝、37はシリコン窒化膜、38,39,40は溝内周面、43はポリシリコン膜、44は段差部である。

【0038】

まず、図5に示すように、抵抗率を3×10−3Ω・cmとしたN+型シリコン基板17の表面上に、エピタキシャル成長によって、ドレイン層として厚さ4〜5μmで抵抗率を0.3Ω・cmのN−エピタキシャル層18を形成する。なお、これらの抵抗率を適宜変更してもよい。

【0039】

さらに、図6に示すように、熱酸化処理を行なって、N−エピタキシャル層18の表面全体にシリコン酸化膜31を形成する。次に、図7に示すように、シリコン酸化膜31の表面全体にフォトレジストを塗布してフォトレジスト膜32を形成する。そして、フォトレジスト膜32の露光、現像を行なって溝10を形成する部位に開口部33を設け、溝10を形成する部位のシリコン酸化膜31を露出させる。

【0040】

次に、図8に示すように、フォトレジスト膜32をマスクとしてシリコン酸化膜31をドライエッチングし、開口部34を形成して溝10を形成する部位のN−エピタキシャル層18を露出させる。そして、図9に示すように、シリコン酸化膜31をマスクとして溝35を形成する。

【0041】

さらに、図10に示すように、熱酸化処理を行なって、シリコン酸化膜31の表面全体および溝35の内周面にシリコン酸化膜を形成する。この処理によって、溝35の内周面に露出していたN−エピタキシャル層18は、シリコン酸化膜36によって覆われる。続けて、図11に示すように、CVD法によって、シリコン酸化膜31および溝35の内周面のシリコン酸化膜36の表面全体にシリコン窒化膜37を堆積形成する。

【0042】

次に、図12に示すように、シリコン窒化膜37に対する異方性エッチングによって、シリコン酸化膜31の表面および溝35の底面のシリコン窒化膜37を除去する。この処理によって、シリコン窒化膜37は、溝35の周側面にのみ残る。さらに、図13に示すように、ドライエッチングによって、シリコン酸化膜31の上部および溝35の底面のシリコン酸化膜36の全部を除去する。この処理によって、溝35の底面にN−エピタキシャル層18が露出する。

【0043】

続けて、図14に示すように、溝35の底面に露出したN−エピタキシャル層18に対する異方性エッチングによって、溝35をN−エピタキシャル層18の内部にまで掘り下げる。この段階において、溝の掘り下げが完了し、溝10が形成された状態になる。さらに、図15に示すように、熱酸化処理を行なって、溝10の下部に露出しているN−エピタキシャル層18を酸化する。

【0044】

次に、図16に示すように、溝10の周側面に残ったシリコン窒化膜37をドライエッチングによって除去し、溝内周面38のシリコン酸化膜36を露出させる。この状態において、溝10の内周面は、その全体にわたってシリコン酸化膜が露出した状態になり、段差部44を境にして幅の異なる上下2段の溝が形成された状態となる。そして、図17に示すように、ウェットエッチングによって、N−エピタキシャル層18状のシリコン酸化膜31の一部および溝10の上段の内周面のシリコン酸化膜36のすべてを除去し、溝内周面39を露出させる。この処理によって、表面が荒れたシリコン酸化膜が除去される。

【0045】

続けて、図18に示すように、再び熱酸化処理を行なって、シリコン酸化膜31および溝10の内周面にシリコン酸化膜42を形成する。この処理によって、溝10の上段の内周面に再びシリコン酸化膜が形成されて、溝内周面40がシリコン酸化膜で覆われる。次に、図19に示すように、CVD法によって、リンをドープしたポリシリコンを溝10の内部空間およびシリコン酸化膜31上に堆積してポリシリコン膜43を形成する。

【0046】

続けて、図20に示すようにドライエッチングによって、シリコン酸化膜31上のすべてのポリシリコン膜43を除去するとともに、溝10の内部のポリシリコン膜43のうちN−エピタキシャル層18の表面よりわずかに深い部位から上方のものを除去する。この処理によって、溝10の内部にゲート電極膜11が形成される。また、溝10の段差部44によって、ゲート電極膜上部12の膜厚は、ゲート電極膜下部13の膜厚よりも厚くなる。次に、図21に示すように、ドライエッチングによって、N−エピタキシャル層18上のすべてのシリコン酸化膜31を除去するとともに、ゲート絶縁膜42のうちゲート電極膜11の表面よりわずかに深い部位から上方のものを除去する。

【0047】

そして、図22に示すように、熱酸化処理によって、N−エピタキシャル層18、ゲート電極膜11およびゲート絶縁膜42上にシリコン酸化膜41を形成する。さらに、ホウ素イオン(B+)をN−エピタキシャル層18に注入し、N−エピタキシャル層18の内部で拡散させてP型ボディ層19を形成する。この際、P型ボディ層19とN−エピタキシャル層18との境界面が溝10の段差部44よりも深くなるようにする。次に、図23に示すように、シリコン酸化膜41の表面全体にフォトレジストを塗布して露光、現像し、フォトレジスト膜45を形成する。そして、フォトレジスト膜45をマスクとしてホウ素イオン(B+)をP型ボディ層19に注入する。さらに、フォトレジスト膜45を除去後に加熱処理を行ない、ホウ素イオン(B+)をP型ボディ層19の内部で拡散させてP+型拡散領域20を形成する。

【0048】

続けて、新たにフォトレジストを塗布してフォトレジスト膜を形成し、露光、現像後に、これをマスクとして砒素イオン(As+)をP型ボディ層19に注入する。そして、フォトレジスト膜を除去後に加熱処理を行ない、拡散させてN+型ソース領域21を形成する。次に、図24に示すように、CVD法によって、シリコン酸化膜41の表面全体にPSG(Phoso−Silicate Glass)膜を堆積する。そして、再びフォトレジストを塗布してフォトレジスト膜を形成し、露光、現像する。次に、図25に示すように、このフォトレジスト膜をマスクとして、上部絶縁膜41およびこのPSG膜の溝10を覆う部分とその近傍部分が残るようにドライエッチングを行なう。残ったPSG膜は、層間絶縁膜22となる。

【0049】

最後に、図26に示すように、層間絶縁膜22およびP型ボディ層19の表面にアルミニウムをスパッタしてアルミニウム膜を形成し、フォトレジストを塗布して露光、現像する。そして、図示しない不要部分をドライエッチングによって除去し、ソース電極膜24を形成する。さらに、N+型シリコン基板17の裏面側に、金属薄膜を蒸着することによってドレイン電極膜25を形成する。

【0050】

以上の製造工程によれば、上下で膜厚の異なるゲート電極膜11を容易に形成することができる。なお、上述の工程においては、N−エピタキシャル層18をエピタキシャル成長によって形成するものとしたが、表面拡散法で形成してもよい。また、ソース電極膜24をアルミニウムで形成するものとしたが、銅など他の金属を用いて形成しても良い。

【0051】

また、ゲート電極膜11は、膜厚を上下2段で異なる構成としたが、さらに多段階で膜厚が異なるものとしても良い。図3は、本発明の第3の実施の形態に係る半導体装置を示す断面図である。図中の符号は、図1に用いたものと同じである。図3に示すように、本発明の第3の実施の形態に係る半導体装置においては、ゲート電極膜11の膜厚を上下3段階で変化させている。

【0052】

さらに、本発明の第4の実施の形態を図面に基づいて詳細に説明する。図4は、本発明の第4の実施の形態に係る半導体装置を示す断面図である。図中、23はゲート電極膜の表面と溝の内周面との距離、26はゲート電極膜の表面である。その他の符号は、図1に用いたものと同じである。図4に示すように、本発明の第4の実施の形態に係る半導体装置においては、ゲート電極膜の表面26を曲面として形成し、ゲート電極膜の表面と溝の内周面との距離23を連続的に変化するものとしている。

【0053】

ゲート電極膜の形態については、以上のほかにも、例えば上部の膜厚一定にし、下部の膜厚を徐々に薄くする、あるいは上部の膜厚を徐々に薄くし、下部の膜厚を一定にするなど他の形態に形成しても良い。また、以上説明した本発明の各実施の形態においては、Nチャネルトレンチゲート型パワーMOSFETの構成を例として取り上げたが、Pチャネルトレンチゲート型パワーMOSFETの場合においても同様に適用できる。さらに、トレンチゲート型パワーMOSFETの構成を有する半導体装置ばかりでなく、IGBTの構成を有する半導体装置にも好ましく適用できるものである。

【0054】

【発明の効果】

以上のように、本発明は、ゲート電極膜の下端部をソース領域よりも深くかつドレイン層と導電領域との境界面よりも浅い範囲内に位置するようにしたことによって、オン抵抗を低くしつつゲート電極膜とドレイン層との間の静電容量を小さくでき、かつゲート絶縁膜の絶縁耐圧を確保することが可能になる。

【図面の簡単な説明】

【図1】本発明の第1の実施の半導体装置を示す説明図であり、(a)は半導体装置のセルの配置を示す平面図であり、(b)はB−B線断面図である。

【図2】本発明の第2の実施の形態に係る半導体装置を示す断面図である。

【図3】本発明の第3の実施の形態に係る半導体装置を示す断面図である。

【図4】本発明の第4の実施の形態に係る半導体装置を示す断面図である。

【図5】本発明の第2の実施の形態に係る半導体装置の製造工程を説明する断面図(a)である。

【図6】本発明の第2の実施の形態に係る半導体装置の製造工程を説明する断面図(b)である。

【図7】本発明の第2の実施の形態に係る半導体装置の製造工程を説明する断面図(c)である。

【図8】本発明の第2の実施の形態に係る半導体装置の製造工程を説明する断面図(d)である。

【図9】本発明の第2の実施の形態に係る半導体装置の製造工程を説明する断面図(e)である。

【図10】本発明の第2の実施の形態に係る半導体装置の製造工程を説明する断面図(f)である。

【図11】本発明の第2の実施の形態に係る半導体装置の製造工程を説明する断面図(g)である。

【図12】本発明の第2の実施の形態に係る半導体装置の製造工程を説明する断面図(h)である。

【図13】本発明の第2の実施の形態に係る半導体装置の製造工程を説明する断面図(i)である。

【図14】本発明の第2の実施の形態に係る半導体装置の製造工程を説明する断面図(j)である。

【図15】本発明の第2の実施の形態に係る半導体装置の製造工程を説明する断面図(k)である。

【図16】本発明の第2の実施の形態に係る半導体装置の製造工程を説明する断面図(l)である。

【図17】本発明の第2の実施の形態に係る半導体装置の製造工程を説明する断面図(m)である。

【図18】本発明の第2の実施の形態に係る半導体装置の製造工程を説明する断面図(n)である。

【図19】本発明の第2の実施の形態に係る半導体装置の製造工程を説明する断面図(o)である。

【図20】本発明の第2の実施の形態に係る半導体装置の製造工程を説明する断面図(p)である。

【図21】本発明の第2の実施の形態に係る半導体装置の製造工程を説明する断面図(q)である。

【図22】本発明の第2の実施の形態に係る半導体装置の製造工程を説明する断面図(r)である。

【図23】本発明の第2の実施の形態に係る半導体装置の製造工程を説明する断面図(s)である。

【図24】本発明の第2の実施の形態に係る半導体装置の製造工程を説明する断面図(t)である。

【図25】本発明の第2の実施の形態に係る半導体装置の製造工程を説明する断面図(u)である。

【図26】本発明の第2の実施の形態に係る半導体装置の製造工程を説明する断面図(v)である。

【図27】図27は、セルの別の配置の一例を示す平面図である。

【図28】図28は、本発明の第1の実施の形態に係る半導体装置の実験例を示す説明図である。

【図29】本発明の第2の実施の形態に係る半導体装置の第1の実験例を示す説明図である。

【図30】本発明の第2の実施の形態に係る半導体装置の第2の実験例を示す説明図である。

【図31】図31は、本発明の第1の実施の形態に係る半導体装置の実験例におけるオン抵抗Ronと静電容量Cissとの関係を示す説明図である。

【図32】本発明の第2の実施の形態に係る半導体装置の第1の実験例におけるオン抵抗Ronと静電容量Cissとの関係を示す説明図である。

【図33】本発明の第2の実施の形態に係る半導体装置の第2の実験例におけるオン抵抗Ronと静電容量Cissとの関係を示す説明図である。

【図34】従来技術に係るトレンチゲート型パワーMOSFET型の半導体装置の一例を示す説明図であり、(a)は半導体装置の平面図であり、(b)はA−A線断面図である。

【符号の簡単な説明】

1a〜1e セル

10 溝

11 ゲート電極膜

12 ゲート電極膜上部

13 ゲート電極膜下部

14 下側周側面部

15 周側面部

16 底面部

17 N+型シリコン基板

18 N−エピタキシャル層

19 P型ボディ層

20 P+型拡散領域

21 N+型ソース領域

22 ポリシリコン絶縁膜

23 ゲート電極膜の表面

24 ソース電極膜

25 ドレイン電極膜

26 ゲート電極膜の表面と溝の内周面との距離

27 ゲート絶縁膜

29 上側周側面部

31 シリコン酸化膜

32 フォトレジスト膜

33 開口部

34 開口部

35 溝

36 シリコン酸化膜

37 シリコン窒化膜

38 溝内周面

39 溝内周面

40 溝内周面

41 シリコン酸化膜

42 シリコン酸化膜

43 ポリシリコン膜

44 段差部

45 フォトレジスト膜

100a〜100e セル

110 溝

111 ゲート電極膜

117 N+型シリコン基板

118 N−エピタキシャル層

119 P型ボディ層

120 P+型拡散領域

121 N+型ソース領域

122 ポリシリコン絶縁膜

124 ソース電極膜

125 ドレイン電極膜

127 ゲート絶縁膜

Claims (3)

- 第1導電型のドレイン層と、該ドレイン層上に配置される該第1導電型とは反対型の第2導電型の導電領域とを形成してなる半導体基板と、

前記導電領域を開口し、前記ドレイン層に達して形成してなる溝と、

前記導電領域内に配置されるとともに、少なくとも一部を前記溝の内周面に露出させて形成してなる第1導電型のソース領域と、

前記溝の内周面に形成されるとともに、所定深さより深い部分の膜厚を他の部分より厚く形成してなるゲート絶縁膜と、

前記ゲート絶縁膜の内周面に形成してなるゲート電極膜と、

前記ゲート電極膜とは絶縁されるとともに、前記ソース領域と接して形成してなるソース電極膜と、を有し、

前記所定深さは、前記ソース領域よりも深くかつ前記ドレイン層と前記導電領域との境界面よりも浅い範囲内であることを特徴とする半導体装置。 - 第1導電型のドレイン層と、該ドレイン層上に配置される該第1導電型とは反対型の第2導電型の導電領域とを形成してなる半導体基板と、

前記導電領域を開口し、前記ドレイン層に達して形成してなる溝と、

前記導電領域内に配置されるとともに、少なくとも一部を前記溝の内周面に露出して形成させてなる第1導電型のソース領域と、

前記溝の内周面に形成されてなるとともに、前記導電領域の開口側に行くに従って膜厚が薄くなるように形成してなるゲート絶縁膜と、

前記ゲート絶縁膜の内周面に形成してなるゲート電極膜と、

前記ゲート電極膜とは絶縁されるとともに、前記ソース領域と接して形成してなるソース電極膜とを有することを特徴とする半導体装置。 - 第1導電型のドレイン層を形成した半導体基板の表面上に第1のシリコン酸化膜を形成し、

前記シリコン酸化膜の所定部位を開口させて前記ドレイン層を露出させ、

露出した前記ドレイン層を開口させて前記ドレイン層に第1の溝を形成し、

前記半導体基板の表面および前記第1の溝の内周面に第2のシリコン酸化膜を形成し、

前記半導体基板の表面および前記第1の溝の内周面を覆うシリコン窒化膜を形成し、前記半導体基板の表面および前記第1の溝の底面の前記シリコン窒化膜を除去し、前記半導体基板の表面および前記第1の溝の底面の前記第2のシリコン酸化膜を露出させ、

前記第1のシリコン酸化膜および前記第2のシリコン酸化膜の少なくとも一部、ならびに前記第1の溝の底面に露出した前記シリコン酸化膜を除去し、前記第1の溝の底面の前記ドレイン層を露出させ、

前記第1の溝の底面に露出した前記ドレイン層を開口して第2の溝を形成し、

前記第2の溝周辺の前記ドレイン層を酸化し、

前記第1の溝の周側面の前記シリコン窒化膜および前記第2のシリコン酸化膜を除去し、

前記半導体基板の表面ならびに前記第1の溝および前記第2の溝の内周面に第3のシリコン酸化膜を形成し、

前記半導体基板の表面および前記第1の溝ならびに前記第2の溝の内周面にポリシリコン膜を堆積形成し、前記第1の溝ならびに前記第2の溝を埋め、

前記半導体基板の表面の前記ポリシリコン膜および前記第1の溝の一部の前記ポリシリコン膜を除去し、

前記半導体基板の表面および前記第1の溝の内周面の一部の前記第3のシリコン酸化膜を除去し、

前記半導体基板の表面ならびに前記第1の溝の内周面に第4のシリコン酸化膜を形成することを特徴とする半導体装置の製造方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001103197A JP4073176B2 (ja) | 2001-04-02 | 2001-04-02 | 半導体装置およびその製造方法 |

| EP02006955A EP1248300A3 (en) | 2001-04-02 | 2002-03-26 | Power MOSFET having a trench gate electrode and method of making the same |

| US10/112,056 US6809375B2 (en) | 2001-04-02 | 2002-04-01 | Semiconductor device having shallow trenches and method for manufacturing the same |

| US10/924,808 US7397082B2 (en) | 2001-04-02 | 2004-08-25 | Semiconductor device having shallow trenches and method for manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001103197A JP4073176B2 (ja) | 2001-04-02 | 2001-04-02 | 半導体装置およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2002299619A JP2002299619A (ja) | 2002-10-11 |

| JP4073176B2 true JP4073176B2 (ja) | 2008-04-09 |

Family

ID=18956285

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001103197A Expired - Fee Related JP4073176B2 (ja) | 2001-04-02 | 2001-04-02 | 半導体装置およびその製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US6809375B2 (ja) |

| EP (1) | EP1248300A3 (ja) |

| JP (1) | JP4073176B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102119483B1 (ko) * | 2018-12-06 | 2020-06-05 | 현대오트론 주식회사 | 전력 반도체 소자 및 그 제조방법 |

Families Citing this family (60)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4073176B2 (ja) * | 2001-04-02 | 2008-04-09 | 新電元工業株式会社 | 半導体装置およびその製造方法 |

| CN100437942C (zh) * | 2002-05-31 | 2008-11-26 | Nxp股份有限公司 | 沟槽栅半导体器件及制造方法 |

| GB0229212D0 (en) * | 2002-12-14 | 2003-01-22 | Koninkl Philips Electronics Nv | Method of manufacture of a trench semiconductor device |

| US7638841B2 (en) | 2003-05-20 | 2009-12-29 | Fairchild Semiconductor Corporation | Power semiconductor devices and methods of manufacture |

| JP2005019668A (ja) * | 2003-06-26 | 2005-01-20 | Shindengen Electric Mfg Co Ltd | 半導体装置 |

| US7235842B2 (en) * | 2003-07-12 | 2007-06-26 | Nxp B.V. | Insulated gate power semiconductor devices |

| JP2005302925A (ja) * | 2004-04-09 | 2005-10-27 | Toshiba Corp | 半導体装置 |

| US7417266B1 (en) * | 2004-06-10 | 2008-08-26 | Qspeed Semiconductor Inc. | MOSFET having a JFET embedded as a body diode |

| JP2006128506A (ja) * | 2004-10-29 | 2006-05-18 | Sharp Corp | トレンチ型mosfet及びその製造方法 |

| US7371641B2 (en) * | 2004-10-29 | 2008-05-13 | International Rectifier Corporation | Method of making a trench MOSFET with deposited oxide |

| JP2006324644A (ja) * | 2005-04-18 | 2006-11-30 | Nec Electronics Corp | 半導体装置の製造方法 |

| US7382019B2 (en) * | 2005-04-26 | 2008-06-03 | Fairchild Semiconductor Corporation | Trench gate FETs with reduced gate to drain charge |

| JP2006344760A (ja) * | 2005-06-08 | 2006-12-21 | Sharp Corp | トレンチ型mosfet及びその製造方法 |

| DE112006001516T5 (de) | 2005-06-10 | 2008-04-17 | Fairchild Semiconductor Corp. | Feldeffekttransistor mit Ladungsgleichgewicht |

| TWI400757B (zh) * | 2005-06-29 | 2013-07-01 | Fairchild Semiconductor | 形成遮蔽閘極場效應電晶體之方法 |

| ITMI20052140A1 (it) * | 2005-11-10 | 2007-05-11 | St Microelectronics Srl | Metodo di realizzazione di un trasnsitor mos a gate verticale con incavo con incavo di gate svasato |

| EP1883116B1 (en) | 2006-07-26 | 2020-03-11 | Semiconductor Components Industries, LLC | Semiconductor device with high breakdown voltage and manufacturing method thereof |

| KR100824205B1 (ko) * | 2006-12-26 | 2008-04-21 | 매그나칩 반도체 유한회사 | Dmos 트랜지스터 및 그 제조방법 |

| JP5767430B2 (ja) * | 2007-08-10 | 2015-08-19 | ローム株式会社 | 半導体装置および半導体装置の製造方法 |

| JP5385567B2 (ja) * | 2007-09-03 | 2014-01-08 | ローム株式会社 | 半導体装置および半導体装置の製造方法 |

| US8129779B2 (en) * | 2007-09-03 | 2012-03-06 | Rohm Co., Ltd. | Trench gate type VDMOSFET device with thicker gate insulation layer portion for reducing gate to source capacitance |

| KR100970282B1 (ko) * | 2007-11-19 | 2010-07-15 | 매그나칩 반도체 유한회사 | 트렌치 mosfet 및 그 제조방법 |

| US20100013009A1 (en) * | 2007-12-14 | 2010-01-21 | James Pan | Structure and Method for Forming Trench Gate Transistors with Low Gate Resistance |

| US7807576B2 (en) * | 2008-06-20 | 2010-10-05 | Fairchild Semiconductor Corporation | Structure and method for forming a thick bottom dielectric (TBD) for trench-gate devices |

| EP2308095A1 (en) * | 2008-07-25 | 2011-04-13 | Nxp B.V. | A trench-gate semiconductor device |

| US8304829B2 (en) | 2008-12-08 | 2012-11-06 | Fairchild Semiconductor Corporation | Trench-based power semiconductor devices with increased breakdown voltage characteristics |

| US8174067B2 (en) | 2008-12-08 | 2012-05-08 | Fairchild Semiconductor Corporation | Trench-based power semiconductor devices with increased breakdown voltage characteristics |

| US8227855B2 (en) | 2009-02-09 | 2012-07-24 | Fairchild Semiconductor Corporation | Semiconductor devices with stable and controlled avalanche characteristics and methods of fabricating the same |

| US8148749B2 (en) | 2009-02-19 | 2012-04-03 | Fairchild Semiconductor Corporation | Trench-shielded semiconductor device |

| IT1396561B1 (it) | 2009-03-13 | 2012-12-14 | St Microelectronics Srl | Metodo per realizzare un dispositivo di potenza con struttura trench-gate e relativo dispositivo |

| WO2010119789A1 (ja) * | 2009-04-13 | 2010-10-21 | ローム株式会社 | 半導体装置および半導体装置の製造方法 |

| JP5350878B2 (ja) * | 2009-05-12 | 2013-11-27 | 新電元工業株式会社 | トレンチゲートパワー半導体装置及びその製造方法 |

| US8049276B2 (en) | 2009-06-12 | 2011-11-01 | Fairchild Semiconductor Corporation | Reduced process sensitivity of electrode-semiconductor rectifiers |

| CN101777514B (zh) * | 2010-02-03 | 2012-12-05 | 香港商莫斯飞特半导体有限公司 | 一种沟槽型半导体功率器件及其制备方法 |

| US20110218295A1 (en) * | 2010-03-02 | 2011-09-08 | Basf Se | Anionic associative rheology modifiers |

| JP5594276B2 (ja) * | 2010-12-08 | 2014-09-24 | 株式会社デンソー | 絶縁ゲート型半導体装置 |

| US8610205B2 (en) | 2011-03-16 | 2013-12-17 | Fairchild Semiconductor Corporation | Inter-poly dielectric in a shielded gate MOSFET device |

| US8598654B2 (en) | 2011-03-16 | 2013-12-03 | Fairchild Semiconductor Corporation | MOSFET device with thick trench bottom oxide |

| JP2012204377A (ja) * | 2011-03-23 | 2012-10-22 | Toshiba Corp | 電力用半導体装置 |

| JP5637916B2 (ja) * | 2011-03-31 | 2014-12-10 | トヨタ自動車株式会社 | 半導体装置及びその製造方法 |

| US20120256255A1 (en) * | 2011-04-07 | 2012-10-11 | Tieh-Chiang Wu | Recessed trench gate structure and method of fabricating the same |

| US8633094B2 (en) | 2011-12-01 | 2014-01-21 | Power Integrations, Inc. | GaN high voltage HFET with passivation plus gate dielectric multilayer structure |

| US8940620B2 (en) | 2011-12-15 | 2015-01-27 | Power Integrations, Inc. | Composite wafer for fabrication of semiconductor devices |

| JP5848619B2 (ja) * | 2012-01-25 | 2016-01-27 | ルネサスエレクトロニクス株式会社 | 半導体装置および半導体装置の製造方法 |

| JP6022777B2 (ja) | 2012-02-28 | 2016-11-09 | エスアイアイ・セミコンダクタ株式会社 | 半導体装置の製造方法 |

| JP6185062B2 (ja) * | 2012-07-25 | 2017-08-23 | パワー・インテグレーションズ・インコーポレーテッド | テーパ付けされた酸化物の堆積/エッチング |

| JP5838176B2 (ja) * | 2013-02-12 | 2016-01-06 | サンケン電気株式会社 | 半導体装置 |

| US8928037B2 (en) | 2013-02-28 | 2015-01-06 | Power Integrations, Inc. | Heterostructure power transistor with AlSiN passivation layer |

| JP6131689B2 (ja) * | 2013-04-16 | 2017-05-24 | 住友電気工業株式会社 | 炭化珪素半導体装置の製造方法 |

| JP2014207403A (ja) | 2013-04-16 | 2014-10-30 | 住友電気工業株式会社 | 炭化珪素半導体装置の製造方法 |

| JP6020488B2 (ja) * | 2014-02-27 | 2016-11-02 | サンケン電気株式会社 | 半導体装置 |

| CN106158631A (zh) * | 2015-03-25 | 2016-11-23 | 北大方正集团有限公司 | 带埋层沟槽功率器件及其制作方法 |

| US9299830B1 (en) * | 2015-05-07 | 2016-03-29 | Texas Instruments Incorporated | Multiple shielding trench gate fet |

| JP6514035B2 (ja) * | 2015-05-27 | 2019-05-15 | 株式会社豊田中央研究所 | 半導体装置 |

| JP6830390B2 (ja) * | 2017-03-28 | 2021-02-17 | エイブリック株式会社 | 半導体装置 |

| CN109473474A (zh) * | 2018-11-09 | 2019-03-15 | 上海擎茂微电子科技有限公司 | 沟槽绝缘栅双极型晶体管器件及其生成方法 |

| CN110854191A (zh) * | 2019-11-15 | 2020-02-28 | 合肥中恒微半导体有限公司 | 一种沟槽型绝缘栅双极晶体管及其制备方法 |

| EP4120361A1 (en) | 2021-07-16 | 2023-01-18 | Hitachi Energy Switzerland AG | Power semiconductor device |

| EP4120360A1 (en) | 2021-07-16 | 2023-01-18 | Hitachi Energy Switzerland AG | Power semiconductor device |

| EP4120362A1 (en) * | 2021-07-16 | 2023-01-18 | Hitachi Energy Switzerland AG | Power semiconductor device |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4914058A (en) | 1987-12-29 | 1990-04-03 | Siliconix Incorporated | Grooved DMOS process with varying gate dielectric thickness |

| US5448083A (en) | 1991-08-08 | 1995-09-05 | Kabushiki Kaisha Toshiba | Insulated-gate semiconductor device |

| US5910669A (en) * | 1992-07-24 | 1999-06-08 | Siliconix Incorporated | Field effect Trench transistor having lightly doped epitaxial region on the surface portion thereof |

| US5637898A (en) * | 1995-12-22 | 1997-06-10 | North Carolina State University | Vertical field effect transistors having improved breakdown voltage capability and low on-state resistance |

| US5770878A (en) | 1996-04-10 | 1998-06-23 | Harris Corporation | Trench MOS gate device |

| US6236099B1 (en) * | 1996-04-22 | 2001-05-22 | International Rectifier Corp. | Trench MOS device and process for radhard device |

| US5998833A (en) | 1998-10-26 | 1999-12-07 | North Carolina State University | Power semiconductor devices having improved high frequency switching and breakdown characteristics |

| US6198127B1 (en) * | 1999-05-19 | 2001-03-06 | Intersil Corporation | MOS-gated power device having extended trench and doping zone and process for forming same |

| US6291298B1 (en) | 1999-05-25 | 2001-09-18 | Advanced Analogic Technologies, Inc. | Process of manufacturing Trench gate semiconductor device having gate oxide layer with multiple thicknesses |

| US6191447B1 (en) | 1999-05-28 | 2001-02-20 | Micro-Ohm Corporation | Power semiconductor devices that utilize tapered trench-based insulating regions to improve electric field profiles in highly doped drift region mesas and methods of forming same |

| CN101800243B (zh) * | 2000-03-17 | 2012-11-07 | 通用半导体公司 | 双栅极结构沟槽型dmos晶体管制造方法 |

| JP4073176B2 (ja) * | 2001-04-02 | 2008-04-09 | 新電元工業株式会社 | 半導体装置およびその製造方法 |

| US6674124B2 (en) * | 2001-11-15 | 2004-01-06 | General Semiconductor, Inc. | Trench MOSFET having low gate charge |

-

2001

- 2001-04-02 JP JP2001103197A patent/JP4073176B2/ja not_active Expired - Fee Related

-

2002

- 2002-03-26 EP EP02006955A patent/EP1248300A3/en not_active Withdrawn

- 2002-04-01 US US10/112,056 patent/US6809375B2/en not_active Expired - Lifetime

-

2004

- 2004-08-25 US US10/924,808 patent/US7397082B2/en not_active Expired - Fee Related

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102119483B1 (ko) * | 2018-12-06 | 2020-06-05 | 현대오트론 주식회사 | 전력 반도체 소자 및 그 제조방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20020153558A1 (en) | 2002-10-24 |

| JP2002299619A (ja) | 2002-10-11 |

| US20050017294A1 (en) | 2005-01-27 |

| US6809375B2 (en) | 2004-10-26 |

| EP1248300A3 (en) | 2005-01-12 |

| EP1248300A2 (en) | 2002-10-09 |

| US7397082B2 (en) | 2008-07-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4073176B2 (ja) | 半導体装置およびその製造方法 | |

| US6872611B2 (en) | Method of manufacturing transistor | |

| KR100271721B1 (ko) | 6 단계의 마스킹 공정을 이용한 이중 확산형 금속 산화물 실리콘(dmos) 트랜지스터 제조방법 | |

| TWI491044B (zh) | 在溝槽dmos中製備帶有階梯厚度的閘極氧化物的方法 | |

| US7579650B2 (en) | Termination design for deep source electrode MOSFET | |

| US8193579B2 (en) | Trench type semiconductor device and fabrication method for the same | |

| JP4188234B2 (ja) | トレンチ・ゲート半導体デバイス及びその製造 | |

| US9978860B2 (en) | Semiconductor device and method of manufacturing semiconductor device | |

| JP4183620B2 (ja) | 半導体装置およびその製造方法 | |

| US9614073B2 (en) | Semiconductor device, and manufacturing method for same | |

| JP3915180B2 (ja) | トレンチ型mos半導体装置およびその製造方法 | |

| US7687352B2 (en) | Trench MOSFET and method of manufacture utilizing four masks | |

| KR100850689B1 (ko) | 파워 mosfet 및 이러한 파워 mosfet을 제조하는 방법 | |

| TWI696288B (zh) | 遮蔽閘金氧半場效電晶體及其製造方法 | |

| JP3965027B2 (ja) | トレンチ底部に厚いポリシリコン絶縁層を有するトレンチゲート型misデバイスの製造方法 | |

| JP2004158680A (ja) | 半導体装置およびその製造方法 | |

| TWI601295B (zh) | 斷閘極金氧半場效電晶體 | |

| JPH05275691A (ja) | 半導体装置及びその製造方法 | |

| EP1450411A1 (en) | MOS power device with high integration density and manufacturing process thereof | |

| JP2002505811A (ja) | 電界効果半導体装置の製造方法 | |

| CN108321206B (zh) | Ldmos器件及其制造方法 | |

| JP4179811B2 (ja) | 縦型mosfetの製造方法 | |

| JP2006332232A (ja) | 半導体装置およびその製造方法 | |

| JP2004039885A (ja) | トレンチゲート型半導体装置とその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040826 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20050912 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20071113 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071213 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080122 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080122 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110201 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 4073176 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110201 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120201 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120201 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130201 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130201 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140201 Year of fee payment: 6 |

|

| LAPS | Cancellation because of no payment of annual fees |