JP4004277B2 - Manufacturing method of semiconductor device - Google Patents

Manufacturing method of semiconductor device Download PDFInfo

- Publication number

- JP4004277B2 JP4004277B2 JP2001357123A JP2001357123A JP4004277B2 JP 4004277 B2 JP4004277 B2 JP 4004277B2 JP 2001357123 A JP2001357123 A JP 2001357123A JP 2001357123 A JP2001357123 A JP 2001357123A JP 4004277 B2 JP4004277 B2 JP 4004277B2

- Authority

- JP

- Japan

- Prior art keywords

- silicon

- film

- gas

- silicon film

- groove

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Insulated Gate Type Field-Effect Transistor (AREA)

- Electrodes Of Semiconductors (AREA)

Description

【0001】

【発明の属する分野】

本発明は、溝部を利用したMOSFETやIGBTの溝部にボロンを添加したゲート電極用シリコン膜を埋め込む場合に有効な半導体装置の製造方法である。

【0002】

【従来の技術】

最近のMOSFETやIGBTはオン特性向上のために溝型構造を有する集積度の高いものが多くなっている。溝部にチャネルを形成するため、溝部側壁にゲート酸化膜を形成し、残りの溝部にゲート電極用のシリコン膜を埋め込む必要がある。素子の歩留まりおよび信頼度を確保するためにはシリコン膜を溝部に均一に付ける必要がある。即ち、段差被覆性のよい膜が必要となる。また、MOSFETやIGBTを各セル部分に対して均一にしかも高速に動作させるためには、ゲート電極とするシリコン膜はできるかぎり低抵抗にする必要がある。このため、シリコン膜に不純物を添加して抵抗を下げている。この段差被覆性、低抵抗の要求は、集積度が高くなり微細化が進むにつれてますます強くなっている。

【0003】

pチャネルMOSFETやIGBTでは、製造工程上ボロン添加のシリコン膜を製造することが要求される。このボロン添加のシリコン膜の形成はnチャネルMOSFETやIGBTに要求される燐添加のシリコン膜の形成に比べて難しい工程である。

【0004】

図7、図8、図9は従来の半導体装置の製造工程を説明するための図である。シリコン基板の溝部にシリコン膜を形成する工程を示している。以下、従来の実施例について説明する。

【0005】

第7図に示すシリコン基板30の表面に付着させたシリコン酸化膜32をマスクにとして、異方性ドライエッチングによりこのシリコン基板30の表面に溝部34を形成し、溝部34の側壁にMOSFETやIGBTのゲート酸化膜となるシリコン酸化膜31を形成する。次にこのシリコン基板30をCVD装置の反応室内に設置し、このシリコン基板を550℃に保ち、モノシランガスとジボランガスの混合ガスをCVD装置内に導入し、モノシランガスを分解させ、少量ボロンを含んだ段差被覆性のよいシリコン膜33を堆積する。

【0006】

しかる後に第8図に示すように、CVD装置内においてこのシリコン基板の温度を550℃に保ったまま、モノシランガスとジボランガスの混合ガスにより、堆積したシリコン膜33より多くのボロンを含んだボロン不純物濃度の高いシリコン膜35をこのシリコン基板表面が平坦化するまで堆積する。

【0007】

次に非酸化性の雰囲気中でこのシリコン基板30を900℃に保ち30分間の熱処理を行ない、シリコン膜35からシリコン膜33へボロンを拡散させ、溝部34内のシリコン膜33、35のボロンの濃度を均一にする。

【0008】

その後、異方性ドライエッチング装置を用い、第9図に示すように、上記シリコン基板に堆積したシリコン膜33、35をエッチングして溝部34内にのみシリコン膜33、35を残し、MOSFETの埋め込みシリコン電極を作製する。

【0009】

このように、段差被覆性のよい比較的ボロン濃度の低いシリコン膜33を堆積し、さらにゲート電極の抵抗を下げるため、比較的ボロン濃度の高いシリコン膜35を堆積し、その後、熱処理することにより、溝部34を空隙なく埋め込み、ある程度低抵抗のシリコン膜33、35を得ることができる。しかしながら、最近の高性能なより集積度の高いMOSFETやIGBTのゲート電極にはさらに低い抵抗が要求されている。

モノシランガスは500℃以上の高温にしないと熱分解が起こらず、ジボランガスはこれよりかなり低温でないと分解しないため、これ以上シリコン膜中のボロン濃度をあげるのは困難である。モノシランガスの反応を500℃以下の低温にすることは、ボロン濃度をあげることにあまり効果がないばかりか、膜の付着速度を落とし、段差被覆性を悪くすることになるため、とても生産には使えない。

【0010】

図10は従来の製造方法の問題点を説明するための半導体装置の断面図である。シリコン膜33、35を堆積するときにジシランガスとジボランガスの混合ガスを用いることもできる。ジシランガスとジボランガスの混合ガスは比較的低温でしかも熱分解温度の差が少ないため、十分ボロン濃度をあげることができ、ボロンの分布の均一性、即ち抵抗の均一性もよい。しかしながら、溝部24にシリコン膜33,35を堆積し埋め込むときにジシランガスを含む高次シランガスを用いると空隙を作りやすい。空隙が残ると溝部24内のみにシリコン膜33、35を残すためにこれらのシリコン膜33、35をエッチングする際に、エッチングガスが空隙に入り込んで溝部34内の空隙が大きくなり信頼性や、特性に悪い影響を与える。

【0011】

このように、従来の方法では、最近の高性能なより集積度の高いMOSFETやIGBTのゲート電極に要求されるより低抵抗な空隙の少ないシリコン膜を作ることには対応できない。また、溝部34を段差被覆性のよい膜と段差被覆性の悪い低抵抗のシリコン膜とで埋め込む方法では空隙の発生を完全に押さえることは困難である。

【0012】

【発明が解決しようとする課題】

本発明は、上記従来技術の問題点を鑑みてなされたもので、その目的は、溝部を埋めるシリコン膜の抵抗率を小さくし併せて、抵抗率のばらつきをなくし、空隙の発生をなくすことである。

【0013】

【課題を解決しようとする手段】

シランガスとジボランガスの混合ガスによるシリコン膜とジシランガスあるいは高次シランガスとジボランガスの混合ガスによるシリコン膜との組み合わせにより低抵抗でそのばらつきも少なく空隙の発生もない半導体装置の製造方法を見つけた。

【0014】

上記課題を解決するための手段として、本発明の半導体装置の製造方法は、溝部を有する半導体基板上にシリコン酸化膜を形成する第一の工程と、前記シリコン酸化膜上に、モノシランガスとジボランガスを混入した反応ガスの熱分解によりボロン不純物を含有する第一のシリコン膜を堆積する第二の工程と、前記第一のシリコン膜上にジシランガスとジボランガスを混入した反応ガスの熱分解により前記第一のシリコン膜より高濃度のボロン不純物を含有する第二のシリコン膜を堆積する第三の工程と、前記第一のシリコン膜と前記第二のシリコン膜のボロン不純物濃度を均一にする非酸化性雰囲気で熱処理を行う第四の工程とを含む半導体装置の製造方法において、前記第二の工程は、前記溝部を空隙なく充填するように前記第一のシリコン膜を堆積することを特徴とする。

【0015】

【発明の実施の形態】

図1、図2、図3は本発明の第1の実施の形態に係る半導体装置の製造工程を説明するための断面図である。図4、図5、図6は本発明の第2の実施の形態に係る半導体装置の製造工程を説明するための断面図である。

【0016】

第1の実施例について説明する。

第1図に示すように、シリコン基板10を酸化雰囲気中で熱処理することにより、シリコン基板10の表面にシリコン酸化膜12を成長させる。次に、このシリコン酸化膜12を写真処理することにより、溝部14を形成する部分に対応するシリコン酸化膜12を除去する。残されたシリコン酸化膜12をマスクとし、異方性ドライエッチにより、幅0.6μm、深さ5μmの溝部14を形成する。次にこのシリコン基板を酸化雰囲気中で熱処理をすることにより、溝部14の側壁に厚さ0.05μmのシリコン酸化膜11を形成する。

【0017】

次にこのシリコン基板10を減圧CVD装置の反応室内に設置し、このシリコン基板を500℃に保ち、減圧CVD装置の反応室内を真空度0.1Paまで排気する。その後、シリコン膜13の成膜用ガスであるモノシランガスと不純物添加用ガスであるジボランガスをそれぞれ90sccm、14sccmの流量の割合とする混合ガスを導入し、減圧CVD装置の反応室内の真空度を13Paに保った状態で、モノシランガスとジボランガスの混合ガスを分解させ、少量のボロンを含んだシリコン膜13をこのシリコン基板の表面に厚さ0.125μm堆積する。

【0018】

次に、減圧CVD装置の反応室内に窒素ガスを導入し、反応室内の真空度を30Paに調整しながら反応室内のガスを置換し、窒素ガスを流したままこのシリコン基板の温度を380℃まで下降させる。

このシリコン基板を380℃に保ち、減圧CVD装置の反応室内を真空度0.1Paまで排気する。その後、シリコン膜13の成膜用ガスであるジシランガスと不純物添加用ガスであるジボランガスをそれぞれ150sccm、25sccmの流量の割合とする混合ガスを導入し、減圧CVD装置の反応室内の真空度を30Paに保った状態で、ジシランガスとジボランガスの混合ガスを分解させ、多量のボロンを含んだシリコン膜15をこのシリコン基板10の表面に厚さ0.125μm堆積し溝部24にシリコンを埋め込み、このシリコン基板10の表面を平坦化する。

【0019】

この加工されたシリコン基板10をアニール炉に設置し、このシリコン基板10を850℃に保ち、非酸化性雰囲気中にて30分間の熱処理を行ない、シリコン膜15からシリコン膜13へボロンを拡散させ、溝部14内のシリコン膜13、15のボロンの濃度を均一にする。

【0020】

その後、異方性ドライエッチング装置を用い、第3図に示すように、上記シリコン基板10に堆積したシリコン膜13、15をエッチングして溝部14内にのみシリコン膜13、15を残す。このようにMOSFETの埋め込みシリコン電極を作成する。

【0021】

次に第2の実施例について説明する。第1の実施例と異なる特徴は、堆積するシリコン膜の厚さにある。

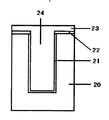

第1の実施例と同様、第4図に示すようにシリコン基板20の表面にシリコン酸化膜22を成長させる。これをマスクとして利用し、異方性ドライエッチング技術を用いて幅0.6μm、深さ5μmの溝部14を形成し、溝部24の側壁に厚さ0.05μmの酸化膜21を形成する。

【0022】

次にこのシリコン基板20を減圧CVD装置の反応室内に設置し、第1の実施例と同様、少量のボロンを含んだシリコン膜23をシリコン基板20の表面に厚さ0.25μm以上堆積する。図4に示されるように、シリコン膜23は溝24を充填し、シリコン基板20の表面は平滑化されている。

【0023】

次に、このシリコン基板20を減圧CVD装置の反応室内に設置し、第1の実施例と同様にして、図5に見られるように多量のボロンを含んだシリコン膜25をこのシリコン基板20の表面に厚さ0.25μm堆積する。

【0024】

このシリコン基板20をアニール炉に設置し、第1の実施例と同じ、非酸化性雰囲気中、850℃、30分間の熱処理を行ない、シリコン膜25からシリコン膜23へボロンを拡散させ、溝部24内のシリコン膜23のボロンの濃度を均一にする。

【0025】

第2の実施例では、溝部24に埋め込まれるシリコン膜は段差被覆性のよいシリコン膜23だけであり、第1の実施例のように、段差被覆性の悪い膜を埋め込まないので、空隙はまったくできない。また、シリコン膜25に添加されたボロンはシリコン膜23全体、深さ約5μmにわたり十分拡散される必要があるが、シリコン膜23、25は多結晶または非晶質であるため、不純物は非常に拡散しやすく、溝部24の中のシリコン膜23に十分拡散され、シリコン膜23の比抵抗が十分下がっていることが確認された。

【0026】

なお、半導体基板としてシリコン基板について説明したがn型のシリコンであってもp型のシリコンであってもであってもよい。また、炭化珪素その他の半導体基板であってもよい。溝部形成用のマスクに利用した酸化膜は、シリコン酸化膜でなくても半導体基板の溝部形成用のマスクになり、ボロンが半導体基板に拡散するのを防止できる窒化シリコン等の膜であってもよい。また、溝部内側に形成するシリコン酸化膜は、溝部内側がシリコン酸化膜であればよく、埋め込まれるシリコン側が窒化シリコン膜であって溝内側がシリコン酸化膜である2層の膜等であってもよい。

【0027】

本発明の半導体装置の製造方法の利用について、溝部を利用したMOSFETやIGBTの溝部にボロンを添加したゲート電極用シリコン膜を埋め込むのに有効であることを述べたが、記憶素子に利用することもできる。

【0028】

【発明の効果】

本発明によれば、溝を埋めるシリコン膜の抵抗率を低くすることができ、低効率のばらつきを少なくすることができる。また、段差被覆性のよい膜を用いることにより空隙のない膜を作製でき、信頼性のよい半導体装置の製造方法を提供できる。MOSFETやIGBTに適用することにより、オン抵抗や高速性の特性を改善できる。また、溝を利用した記憶素子に適用するにより、高速応答を達成することができる。

【図面の簡単な説明】

【図1】 本発明の第1の実施の形態に係る半導体装置の製造工程を説明するための断面図である。

【図2】本発明の第1の実施の形態に係る半導体装置の製造工程を説明するための断面図である。

【図3】本発明の第1の実施の形態に係る半導体装置の製造工程を説明するための断面図である。

【図4】 本発明の第2の実施の形態に係る半導体装置の製造工程を説明するための断面図である。

【図5】 本発明の第2の実施の形態に係る半導体装置の製造工程を説明するための断面図である。

【図6】 本発明の第2の実施の形態に係る半導体装置の製造工程を説明するための断面図である。

【図7】 従来の半導体装置の製造工程を説明するための断面図である。

【図8】 従来の半導体装置の製造工程を説明するための断面図である。

【図9】 従来の半導体装置の製造工程を説明するための断面図である。

【図10】 従来の半導体装置の製造方法の問題点を説明するための半導体装置の断面図である。

【符号の説明】

10 シリコン基板

11、12 シリコン酸化膜

13、15 シリコン膜

14 溝部

20 シリコン基板

21、22 シリコン酸化膜

23、25 シリコン膜

24 溝部

30 シリコン基板

31、32 シリコン酸化膜

33、35 シリコン膜

34 溝部[0001]

[Field of the Invention]

The present invention is a method of manufacturing a semiconductor device that is effective when a silicon film for a gate electrode to which boron is added is buried in a trench portion of a MOSFET or IGBT using the trench portion.

[0002]

[Prior art]

Recently, many MOSFETs and IGBTs have a high degree of integration having a groove-type structure in order to improve on-characteristics. In order to form a channel in the trench, it is necessary to form a gate oxide film on the sidewall of the trench and bury a silicon film for the gate electrode in the remaining trench. In order to ensure the yield and reliability of the element, it is necessary to uniformly apply the silicon film to the groove. That is, a film with good step coverage is required. Further, in order to make the MOSFET and IGBT operate uniformly with respect to each cell portion and at high speed, it is necessary to make the silicon film as the gate electrode as low resistance as possible. For this reason, the resistance is lowered by adding impurities to the silicon film. The demand for step coverage and low resistance is increasing as the degree of integration increases and miniaturization progresses.

[0003]

In the p-channel MOSFET and IGBT, it is required to manufacture a boron-added silicon film in the manufacturing process. The formation of the boron-added silicon film is a difficult process compared to the formation of the phosphorus-added silicon film required for n-channel MOSFETs and IGBTs.

[0004]

7, 8, and 9 are views for explaining a manufacturing process of a conventional semiconductor device. The process of forming a silicon film in the groove of the silicon substrate is shown. Hereinafter, conventional examples will be described.

[0005]

Using the

[0006]

Thereafter, as shown in FIG. 8, the boron impurity concentration containing more boron than the deposited

[0007]

Next, this

[0008]

Thereafter, using an anisotropic dry etching apparatus, as shown in FIG. 9, the

[0009]

In this way, a

The monosilane gas does not undergo thermal decomposition unless the temperature is higher than 500 ° C., and the diborane gas does not decompose unless the temperature is much lower than this, so that it is difficult to increase the boron concentration in the silicon film. Lowering the reaction of the monosilane gas to 500 ° C or less is not very effective in increasing the boron concentration, but also reduces the film deposition rate and deteriorates the step coverage, so it can be used for production. Absent.

[0010]

FIG. 10 is a cross-sectional view of a semiconductor device for explaining problems of a conventional manufacturing method. A mixed gas of disilane gas and diborane gas can also be used when depositing the

[0011]

As described above, the conventional method cannot cope with the production of a silicon film having a low resistance and a small gap, which is required for a gate electrode of a recent high-performance MOSFET with higher integration and IGBT. Also, it is difficult to completely suppress the generation of voids by the method of filling the

[0012]

[Problems to be solved by the invention]

The present invention has been made in view of the above-described problems of the prior art, and its purpose is to reduce the resistivity of the silicon film filling the trench, eliminate the variation in resistivity, and eliminate the generation of voids. is there.

[0013]

[Means to solve the problem]

We have found a method of manufacturing a semiconductor device that has low resistance, little variation, and no voids by combining a silicon film with a mixed gas of silane gas and diborane gas and a silicon film with a mixed gas of disilane gas or higher order silane gas and diborane gas.

[0014]

As a means for solving the above-described problems, a method of manufacturing a semiconductor device according to the present invention includes a first step of forming a silicon oxide film on a semiconductor substrate having a groove, and monosilane gas and diborane gas on the silicon oxide film. A second step of depositing a first silicon film containing boron impurities by thermal decomposition of the mixed reaction gas; and the first step by thermal decomposition of the reaction gas mixed with disilane gas and diborane gas on the first silicon film. A third step of depositing a second silicon film containing a higher concentration of boron impurities than the silicon film, and a non-oxidizing property for making the boron impurity concentrations of the first silicon film and the second silicon film uniform And a fourth step of performing a heat treatment in an atmosphere, wherein the second step includes the first silicidation so as to fill the groove without gaps. Characterized by depositing the emission layer.

[0015]

DETAILED DESCRIPTION OF THE INVENTION

1, 2, and 3 are cross-sectional views for explaining a manufacturing process of a semiconductor device according to the first embodiment of the present invention. 4, 5, and 6 are cross-sectional views for explaining a manufacturing process of a semiconductor device according to the second embodiment of the present invention.

[0016]

A first embodiment will be described.

As shown in FIG. 1, a

[0017]

Next, the

[0018]

Next, nitrogen gas is introduced into the reaction chamber of the low pressure CVD apparatus, the gas in the reaction chamber is replaced while adjusting the degree of vacuum in the reaction chamber to 30 Pa, and the temperature of the silicon substrate is increased to 380 ° C. while the nitrogen gas is flowing. Lower.

This silicon substrate is kept at 380 ° C., and the reaction chamber of the low pressure CVD apparatus is evacuated to a vacuum degree of 0.1 Pa. Thereafter, a mixed gas having a flow rate of 150 sccm and 25 sccm of disilane gas, which is a film forming gas for the

[0019]

The processed

[0020]

Thereafter, using an anisotropic dry etching apparatus, as shown in FIG. 3, the

[0021]

Next, a second embodiment will be described. A feature different from the first embodiment is the thickness of the deposited silicon film.

As in the first embodiment, a

[0022]

Next, this

[0023]

Next, the

[0024]

This

[0025]

In the second embodiment, the silicon film embedded in the

[0026]

Although the silicon substrate has been described as the semiconductor substrate, it may be n-type silicon or p-type silicon. Further, it may be a silicon carbide or other semiconductor substrate. Even if the oxide film used for the groove forming mask is not a silicon oxide film, it may be a mask for forming the groove of the semiconductor substrate and may be a film of silicon nitride or the like that can prevent boron from diffusing into the semiconductor substrate. Good. The silicon oxide film formed inside the groove may be a silicon oxide film inside the groove, and may be a two-layer film or the like in which the silicon side to be embedded is a silicon nitride film and the inside of the groove is a silicon oxide film. Good.

[0027]

Regarding the use of the semiconductor device manufacturing method of the present invention, it has been described that it is effective for embedding a silicon film for a gate electrode to which boron is added in the trench portion of a MOSFET or IGBT using the trench portion. You can also.

[0028]

【The invention's effect】

According to the present invention, the resistivity of the silicon film filling the trench can be lowered, and variation in low efficiency can be reduced. Further, by using a film with good step coverage, a film without voids can be manufactured, and a reliable method for manufacturing a semiconductor device can be provided. By applying to a MOSFET or IGBT, on-resistance and high-speed characteristics can be improved. In addition, a high-speed response can be achieved by applying to a memory element using a groove.

[Brief description of the drawings]

FIG. 1 is a cross-sectional view for illustrating a manufacturing step of a semiconductor device according to a first embodiment of the invention.

FIG. 2 is a cross-sectional view for illustrating a manufacturing step of the semiconductor device according to the first embodiment of the invention.

FIG. 3 is a cross-sectional view for illustrating a manufacturing step of the semiconductor device according to the first embodiment of the invention.

FIG. 4 is a cross-sectional view for illustrating a manufacturing step of the semiconductor device according to the second embodiment of the present invention.

FIG. 5 is a cross-sectional view for illustrating a manufacturing step of the semiconductor device according to the second embodiment of the present invention.

FIG. 6 is a cross-sectional view for illustrating a manufacturing step of the semiconductor device according to the second embodiment of the present invention.

FIG. 7 is a cross-sectional view for explaining a manufacturing process of a conventional semiconductor device.

FIG. 8 is a cross-sectional view for explaining a manufacturing process of a conventional semiconductor device.

FIG. 9 is a cross-sectional view for explaining a manufacturing process of a conventional semiconductor device.

FIG. 10 is a cross-sectional view of a semiconductor device for illustrating problems in a conventional method for manufacturing a semiconductor device.

[Explanation of symbols]

DESCRIPTION OF

Claims (1)

前記シリコン酸化膜上に、モノシランガスとジボランガスを混入した反応ガスの熱分解によりボロン不純物を含有する第一のシリコン膜を堆積する第二の工程と、

前記第一のシリコン膜上にジシランガスとジボランガスを混入した反応ガスの熱分解により前記第一のシリコン膜より高濃度のボロン不純物を含有する第二のシリコン膜を堆積する第三の工程と、

前記第一のシリコン膜と前記第二のシリコン膜のボロン不純物濃度を均一にする非酸化性雰囲気で熱処理を行う第四の工程とを含む半導体装置の製造方法において、

前記第二の工程は、前記溝部を空隙なく充填するように前記第一のシリコン膜を堆積することを特徴とする半導体装置の製造方法。A first step of forming a silicon oxide film on a semiconductor substrate having a groove;

A second step of depositing a first silicon film containing boron impurities on the silicon oxide film by thermal decomposition of a reaction gas mixed with monosilane gas and diborane gas;

A third step of depositing a second silicon film containing a higher concentration of boron impurities than the first silicon film by thermal decomposition of a reaction gas mixed with disilane gas and diborane gas on the first silicon film;

In a method for manufacturing a semiconductor device, comprising: a fourth step of performing a heat treatment in a non-oxidizing atmosphere that makes the boron impurity concentration of the first silicon film and the second silicon film uniform.

In the second step, the first silicon film is deposited so as to fill the groove portion without a gap.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001357123A JP4004277B2 (en) | 2001-11-22 | 2001-11-22 | Manufacturing method of semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001357123A JP4004277B2 (en) | 2001-11-22 | 2001-11-22 | Manufacturing method of semiconductor device |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2003158092A JP2003158092A (en) | 2003-05-30 |

| JP4004277B2 true JP4004277B2 (en) | 2007-11-07 |

Family

ID=19168512

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001357123A Expired - Fee Related JP4004277B2 (en) | 2001-11-22 | 2001-11-22 | Manufacturing method of semiconductor device |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4004277B2 (en) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4627974B2 (en) * | 2003-08-01 | 2011-02-09 | セイコーインスツル株式会社 | Manufacturing method of semiconductor device |

| JP4751023B2 (en) * | 2004-01-13 | 2011-08-17 | セイコーインスツル株式会社 | Manufacturing method of semiconductor device |

| JP4560820B2 (en) * | 2006-06-20 | 2010-10-13 | エルピーダメモリ株式会社 | Manufacturing method of semiconductor device |

| KR101570044B1 (en) | 2009-03-17 | 2015-11-20 | 삼성전자주식회사 | Semiconductor device having low resistance buried metal gate electrode structure and method of manufacturing the same |

-

2001

- 2001-11-22 JP JP2001357123A patent/JP4004277B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2003158092A (en) | 2003-05-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100403540C (en) | Integrated circuit component and forming method thereof | |

| US7456087B2 (en) | Semiconductor device and method of fabricating the same | |

| KR101023208B1 (en) | Mosfet device with tensile strained substrate and method of making the same | |

| JP3840198B2 (en) | Semiconductor device and manufacturing method thereof | |

| JP2002198526A (en) | Method of manufacturing semiconductor device | |

| US6812073B2 (en) | Source drain and extension dopant concentration | |

| CN106653751A (en) | Semiconductor device and manufacturing method thereof | |

| JP2877104B2 (en) | Method for manufacturing semiconductor device | |

| JP2009266871A (en) | Silicon carbide semiconductor device and method of manufacturing same | |

| JP2004095639A (en) | Semiconductor device and its manufacturing method | |

| CN105047539B (en) | The method for improving SiC MOSFET channel mobilities | |

| JP2004119980A (en) | Sidewall forming method using alkylsilane precursol for manufacturing mos transistor | |

| KR100603588B1 (en) | Semiconductor device with low contact resistance and method for fabricating the same | |

| CN103000499B (en) | A kind of germanium silicon boron outer layer growth method | |

| US20050121704A1 (en) | Semiconductor device and method of manufacturing the same | |

| JP4004277B2 (en) | Manufacturing method of semiconductor device | |

| US20040180509A1 (en) | Shallow trench isolation for strained silicon processes | |

| US20150279694A1 (en) | DRAM Cells and Methods of Forming Silicon Dioxide | |

| CN110444473A (en) | The manufacturing method of embedded SiGe device and embedded SiGe device structure | |

| JP2005064032A (en) | Semiconductor device and its manufacturing method | |

| US6555425B2 (en) | Method for manufacturing transistor | |

| CN105161526B (en) | The method for improving vertical conductive structure SiC MOSFET channel mobilities | |

| JP2685033B2 (en) | MIS type FET and manufacturing method thereof | |

| JP2004039946A (en) | Manufacturing method of semiconductor device | |

| CN108074870A (en) | Transistor and forming method thereof |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20050610 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070619 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070720 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20070821 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20070821 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100831 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |