JP2005064523A - 半導体装置のキャパシタとその製造方法、およびそのキャパシタを備えるメモリ装置 - Google Patents

半導体装置のキャパシタとその製造方法、およびそのキャパシタを備えるメモリ装置 Download PDFInfo

- Publication number

- JP2005064523A JP2005064523A JP2004237223A JP2004237223A JP2005064523A JP 2005064523 A JP2005064523 A JP 2005064523A JP 2004237223 A JP2004237223 A JP 2004237223A JP 2004237223 A JP2004237223 A JP 2004237223A JP 2005064523 A JP2005064523 A JP 2005064523A

- Authority

- JP

- Japan

- Prior art keywords

- film

- oxide film

- capacitor

- manufacturing

- dielectric film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 239000003990 capacitor Substances 0.000 title claims abstract description 87

- 239000004065 semiconductor Substances 0.000 title claims abstract description 33

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 29

- 238000006243 chemical reaction Methods 0.000 claims abstract description 47

- 238000000034 method Methods 0.000 claims abstract description 35

- 230000002265 prevention Effects 0.000 claims abstract description 3

- 239000002243 precursor Substances 0.000 claims description 25

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 claims description 18

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 17

- 229910052747 lanthanoid Inorganic materials 0.000 claims description 17

- 150000002602 lanthanoids Chemical class 0.000 claims description 17

- 229910052710 silicon Inorganic materials 0.000 claims description 17

- 239000010703 silicon Substances 0.000 claims description 17

- 239000012535 impurity Substances 0.000 claims description 16

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 claims description 12

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 claims description 11

- 229910000449 hafnium oxide Inorganic materials 0.000 claims description 11

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 claims description 11

- 229910052751 metal Inorganic materials 0.000 claims description 11

- 239000002184 metal Substances 0.000 claims description 11

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 claims description 11

- 150000001768 cations Chemical class 0.000 claims description 10

- 230000001590 oxidative effect Effects 0.000 claims description 8

- 230000003647 oxidation Effects 0.000 claims description 7

- 238000007254 oxidation reaction Methods 0.000 claims description 7

- 229910021193 La 2 O 3 Inorganic materials 0.000 claims description 6

- 238000001035 drying Methods 0.000 claims description 5

- 230000006866 deterioration Effects 0.000 abstract description 2

- 238000010521 absorption reaction Methods 0.000 abstract 1

- 239000010408 film Substances 0.000 description 159

- MRELNEQAGSRDBK-UHFFFAOYSA-N lanthanum(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[La+3].[La+3] MRELNEQAGSRDBK-UHFFFAOYSA-N 0.000 description 26

- 239000010410 layer Substances 0.000 description 20

- 238000000231 atomic layer deposition Methods 0.000 description 14

- 239000011229 interlayer Substances 0.000 description 8

- 239000004020 conductor Substances 0.000 description 5

- BPQQTUXANYXVAA-UHFFFAOYSA-N Orthosilicate Chemical compound [O-][Si]([O-])([O-])[O-] BPQQTUXANYXVAA-UHFFFAOYSA-N 0.000 description 4

- 239000000758 substrate Substances 0.000 description 4

- 238000005229 chemical vapour deposition Methods 0.000 description 3

- 239000010409 thin film Substances 0.000 description 3

- 238000007736 thin film deposition technique Methods 0.000 description 3

- 238000010586 diagram Methods 0.000 description 2

- 238000005755 formation reaction Methods 0.000 description 2

- 229910052746 lanthanum Inorganic materials 0.000 description 2

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 230000002542 deteriorative effect Effects 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 150000004760 silicates Chemical class 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

- 230000008016 vaporization Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L28/00—Passive two-terminal components without a potential-jump or surface barrier for integrated circuits; Details thereof; Multistep manufacturing processes therefor

- H01L28/40—Capacitors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/018—Dielectrics

- H01G4/06—Solid dielectrics

- H01G4/08—Inorganic dielectrics

- H01G4/10—Metal-oxide dielectrics

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/018—Dielectrics

- H01G4/06—Solid dielectrics

- H01G4/08—Inorganic dielectrics

- H01G4/12—Ceramic dielectrics

- H01G4/1272—Semiconductive ceramic capacitors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B51/00—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory transistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B51/00—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory transistors

- H10B51/30—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory transistors characterised by the memory core region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B53/00—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/022—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being a laminate, i.e. composed of sublayers, e.g. stacks of alternating high-k metal oxides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/0226—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process

- H01L21/02263—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/0226—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process

- H01L21/02263—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase

- H01L21/02271—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/0226—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process

- H01L21/02263—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase

- H01L21/02271—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition

- H01L21/0228—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition deposition by cyclic CVD, e.g. ALD, ALE, pulsed CVD

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/314—Inorganic layers

- H01L21/316—Inorganic layers composed of oxides or glassy oxides or oxide based glass

- H01L21/31604—Deposition from a gas or vapour

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L28/00—Passive two-terminal components without a potential-jump or surface barrier for integrated circuits; Details thereof; Multistep manufacturing processes therefor

- H01L28/40—Capacitors

- H01L28/55—Capacitors with a dielectric comprising a perovskite structure material

- H01L28/56—Capacitors with a dielectric comprising a perovskite structure material the dielectric comprising two or more layers, e.g. comprising buffer layers, seed layers, gradient layers

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Chemical & Material Sciences (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Inorganic Chemistry (AREA)

- Manufacturing & Machinery (AREA)

- Ceramic Engineering (AREA)

- Computer Hardware Design (AREA)

- Semiconductor Memories (AREA)

- Formation Of Insulating Films (AREA)

- Fixed Capacitors And Capacitor Manufacturing Machines (AREA)

- Semiconductor Integrated Circuits (AREA)

Abstract

【課題】 誘電膜とその誘電膜が蒸着される下部電極の間の望ましくない反応を防止でき、ALD法を利用した誘電膜の形成過程で誘電膜に多量の水蒸気が吸収されることを防止して、誘電膜の電気的な特性の低下を防止できる。

【解決手段】 下部電極と、誘電膜と、上部電極とを含む半導体装置のキャパシタにおいて、前記下部電極と前記誘電膜の間に、前記下部電極と前記誘電膜の反応を防止する第1反応防止膜を備える半導体装置のキャパシタとその製造方法および前記キャパシタを備えるメモリ装置。

【選択図】 図2

【解決手段】 下部電極と、誘電膜と、上部電極とを含む半導体装置のキャパシタにおいて、前記下部電極と前記誘電膜の間に、前記下部電極と前記誘電膜の反応を防止する第1反応防止膜を備える半導体装置のキャパシタとその製造方法および前記キャパシタを備えるメモリ装置。

【選択図】 図2

Description

本発明は、半導体装置およびその製造方法に係り、さらに詳細には半導体装置のキャパシタとその製造方法、および前記キャパシタを備えるメモリ装置に関する。

半導体装置のキャパシタに使われる誘電膜として、ランタン酸化膜(La203)が使われている。

シリコン層上にランタン酸化膜が蒸着される場合、ランタン酸化膜がシリコンと反応し、その結果、キャパシタにシリケートが形成される。このシリケートの形成によって、キャパシタの特性が低下する。

シリコン層上にランタン酸化膜が蒸着される場合、ランタン酸化膜がシリコンと反応し、その結果、キャパシタにシリケートが形成される。このシリケートの形成によって、キャパシタの特性が低下する。

半導体装置の集積度が高くなるにつれて、狭い領域に高静電容量を有するキャパシタを形成することが求められている。キャパシタの静電容量は電極の表面積に比例する。したがって、キャパシタの電極を立体的に形成することによって、キャパシタの静電容量を増加させることができる。

一方、キャパシタの電極が複雑な構造を有していても誘電膜の厚さおよび成分は均一であることが望ましい。

しかし、化学気相蒸着(Chemical Vapor Deposition:CVD)方法のような既存の薄膜蒸着方法は、工程の特性上、複雑な構造を有する電極上に均一な厚さおよび成分を有する誘電膜を形成し難い。

そこで、最近では、原子層堆積(Atomic Layer Deposition:ALD)を利用して複雑な構造を有する下部構造物に薄膜を形成する方法が紹介されている。

ALD法を利用する場合、形成しようとする薄膜の成分を複雑な構造を有する下部構造物の深い所まで到達させることができる。したがって、薄膜の厚さの均一性および成分の均一性をある程度確保できる。

したがって、ALD法を利用する場合、複雑な構造を有するキャパシタ電極の上に均一な厚さおよび成分を有する誘電膜を形成できる。

前記ランタン酸化膜もALD法を利用して形成できる。しかし、問題は、ランタニド系列の物質が吸湿性を有しているため、ランタニド系列の物質が空気中に露出される場合、水蒸気(H2O)を吸収してその特性が変わることである。

すなわち、ランタン酸化膜をALD法を利用して形成する場合、ランタン前駆体層を蒸着した後、水蒸気を使用して前記ランタン前駆体層を酸化させる過程で水蒸気がランタン酸化膜内に多量に吸収される。この場合、ランタン酸化膜の電気的な特性、例えば、漏れ電流特性が低下する。

図1は、ALD法を利用してランタン酸化膜等の幾つかの酸化膜を形成する過程で酸化ガスとして水蒸気を使用した時の問題点、すなわち漏れ電流密度が増加することを表す。B1は40Åの厚さに形成されたアルミニウム酸化膜における漏れ電流密度を表し、B2は45Åの厚さに形成されたハフニウム酸化膜における漏れ電流密度を表す。そして、B3は前駆体、La(tmhd)3における漏れ電流密度を表し、B4はLa(N(Si(Me)3)2)3における漏れ電流密度を表す。また、B5は、La(iPrCp)3における漏れ電流密度を表す。

本発明が解決しようとする技術的課題は、前記従来の技術の問題点を改善するためのものであって、誘電膜とその誘電膜が蒸着される下部電極の間の望ましくない反応を防止でき、ALD法を利用した誘電膜の形成過程で誘電膜に多量の水蒸気が吸収されることを防止して、誘電膜の電気的な特性の低下を防止できる半導体装置のキャパシタを提供することである。

本発明が解決しようとする他の技術的課題は、前記キャパシタの製造方法を提供することである。

本発明が解決しようとするさらに他の技術的課題は、前記キャパシタを備える半導体メモリ装置を提供することである。

前記課題を達成するために、本発明は、下部電極と、誘電膜と、上部電極とを含む半導体装置のキャパシタにおいて、前記下部電極と前記誘電膜の間に、前記下部電極と前記誘電膜の反応を防止する第1反応防止膜を備えることを特徴とする半導体装置のキャパシタを提供する。

前記誘電膜は、ランタニド系列の元素を含む酸化膜である。

前記上部電極と前記誘電膜の間に、さらに第2反応防止膜が設けられていてもよい。

前記第1反応防止膜および第2反応防止膜は、La2O3よりイオン半径の小さいハフニウム酸化膜またはアルミニウム酸化膜である。

前記上部電極と前記誘電膜の間に、さらに第2反応防止膜が設けられていてもよい。

前記第1反応防止膜および第2反応防止膜は、La2O3よりイオン半径の小さいハフニウム酸化膜またはアルミニウム酸化膜である。

前記他の課題を達成するために、本発明は、下部電極を形成する段階と、前記下部電極の上に第1反応防止膜を形成する段階と、前記第1反応防止膜の上に金属元素を含む前駆体層を形成する段階と、前記金属元素を酸化させて前記第1反応防止膜の上に前記金属元素を含む酸化膜を形成する段階と、前記金属元素を含む酸化膜を乾燥させる段階と、前記乾燥された酸化膜の上に上部電極を形成する段階とを含むことを特徴とするキャパシタの製造方法を提供する。

前記下部電極は、導電性不純物がドーピングされたシリコン電極で形成し、前記上部電極はチタンナイトライド膜で形成できる。

前記乾燥された酸化膜と前記上部電極の間に第2反応防止膜をさらに形成できるが、この時、前記下部電極および前記上部電極は全て導電性不純物がドーピングされたシリコン電極またはチタンナイトライド膜で形成する。

前記上部電極および前記下部電極は全てチタンナイトライド膜で形成できる。

前記前駆体層を形成した後、前記金属元素を含む酸化膜を形成した後、および前記酸化膜を乾燥した後に、それぞれ排気工程を実施できる。

前記酸化膜を形成する段階で、前記前駆体層は、前記前駆体層の上に水蒸気を流して1次酸化させる。

前記前駆体層を1次酸化させた後、前記前駆体層上にオゾンを流して前記1次酸化された前駆体層を2次酸化させる。この時、前記1次および2次酸化工程は数回繰返して行なうことができる。

前記酸化膜は、その酸化膜の上にオゾンを流して乾燥させる。

前記第1反応防止膜および第2反応防止膜は、前記誘電膜が含むものよりも半径の小さい陽イオンを含むハフニウム酸化膜またはアルミニウム酸化膜で形成できる。

さらに他の課題を解決するため、本発明は、トランジスタとそれに連結されたキャパシタとを備える半導体メモリ装置において、前記キャパシタが、下部電極と、誘電膜と、上部電極とを含み、前記下部電極と前記誘電膜の間に、前記下部電極と前記誘電膜の反応を防止する第1反応防止膜を備えることを特徴とする半導体メモリ装置を提供する。

本発明によるキャパシタは、誘電膜として使われるランタニド系列の元素を含む酸化膜と、シリコンを含む下部電極または/および上部電極の間に両者の反応を防止するための反応防止膜を備える。これにより、ランタニド系列の元素を含む酸化膜とシリコンの反応に起因するシリケートが形成されないため、キャパシタの電気的特性の劣化を防止することができる。また、ALDを利用したランタニド系列の元素を含む酸化膜形成過程で、酸化工程後にオゾンを利用して酸化された結果物から水蒸気を完全に除去する。すなわち、酸化された結果物を乾燥する。これにより、ランタニド系列の元素を含む酸化膜に水蒸気が多量に含まれることに起因するキャパシタの電気的特性の劣化も防止することができる。さらに、このようなキャパシタを半導体メモリ装置に備える場合、メモリ装置に保存されたデータを長期間正常な状態で維持できるので、メモリ装置の信頼性も高くなる。

以下、本発明の実施形態による半導体装置のキャパシタとその製造方法、およびキャパシタを備えるメモリ装置について、添付図面を参照して詳細に説明する。なお、図面に示された層や領域の厚さは、明細書の明確性のために誇張して示した。

まず、本発明の実施形態によるキャパシタ(以下、本発明のキャパシタという)について説明する。

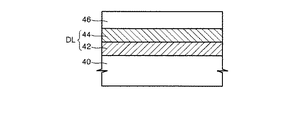

図2は、本発明の実施形態によるキャパシタの断面図である。

図2に示すとおり、本発明のキャパシタは、下部電極40と、誘電膜DLと、上部電極46とを備える。下部電極40は、導電性不純物がドーピングされたシリコン電極である。下部電極40は、チタンナイトライド(TiN)で形成されていてもよい。誘電膜DLは、第1誘電膜42と第2誘電膜44とを含む。第1誘電膜42は、下部電極40と第2誘電膜44との望ましくない反応、例えば、シリケート形成反応を防止するためのものである。第1誘電膜42は、第2誘電膜44におけるよりも半径が小さい陽イオンを含む誘電膜、例えば、ハフニウム酸化膜(HfO2)またはアルミニウム酸化膜(Al2O3)であることが望ましい。第1誘電膜42の厚さは2nm程度が望ましいが、多少厚いか、または薄くても良い。しかし、第1誘電膜42の厚さは、第2誘電膜44より薄いことが望ましい。第2誘電膜44は、ランタニド系列の元素を含む酸化膜、例えば、ランタン酸化膜(La2O3)であることが望ましい。第2誘電膜44の厚さは、2nm〜10nm程度が望ましいが、多少厚いか、または薄くても良い。上部電極46は、チタンナイトライド(TiN)電極が望ましいが、導電性不純物がドーピングされたシリコン電極であってもよい。但し、後者の場合、上部電極46と第2誘電膜44の間のシリケート反応を防止するために、上部電極46と第2誘電膜44の間に、第1誘電膜42と同等な役割を有する反応防止膜をさらに形成してもよい。上部電極46と下部電極40とは、同じ素材で形成されていてもよい。

図2は、本発明の実施形態によるキャパシタの断面図である。

図2に示すとおり、本発明のキャパシタは、下部電極40と、誘電膜DLと、上部電極46とを備える。下部電極40は、導電性不純物がドーピングされたシリコン電極である。下部電極40は、チタンナイトライド(TiN)で形成されていてもよい。誘電膜DLは、第1誘電膜42と第2誘電膜44とを含む。第1誘電膜42は、下部電極40と第2誘電膜44との望ましくない反応、例えば、シリケート形成反応を防止するためのものである。第1誘電膜42は、第2誘電膜44におけるよりも半径が小さい陽イオンを含む誘電膜、例えば、ハフニウム酸化膜(HfO2)またはアルミニウム酸化膜(Al2O3)であることが望ましい。第1誘電膜42の厚さは2nm程度が望ましいが、多少厚いか、または薄くても良い。しかし、第1誘電膜42の厚さは、第2誘電膜44より薄いことが望ましい。第2誘電膜44は、ランタニド系列の元素を含む酸化膜、例えば、ランタン酸化膜(La2O3)であることが望ましい。第2誘電膜44の厚さは、2nm〜10nm程度が望ましいが、多少厚いか、または薄くても良い。上部電極46は、チタンナイトライド(TiN)電極が望ましいが、導電性不純物がドーピングされたシリコン電極であってもよい。但し、後者の場合、上部電極46と第2誘電膜44の間のシリケート反応を防止するために、上部電極46と第2誘電膜44の間に、第1誘電膜42と同等な役割を有する反応防止膜をさらに形成してもよい。上部電極46と下部電極40とは、同じ素材で形成されていてもよい。

図3は、前記本発明のキャパシタの電気的特性、すなわち、印加電圧に対する漏れ電流特性を表すグラフである。図3において、T、BおよびCは、それぞれ、図2に示したキャパシタの形成されたウェーハを垂直に立てた時、前記ウェーハの上側、下側および中央に形成されたキャパシタを対象として印加電圧による漏れ電流密度を測定した結果を表す第1グラフないし第3グラフである。

第1グラフT、第2グラフBおよび第3グラフCから、前記ウェーハの上側、下側および中央に形成されたキャパシタの漏れ電流密度は大きい差がなく、動作電圧の範囲では全て漏れ電流密度は1×10-7A/cm2以下と低いことが分かる。

また、第1グラフT、第2グラフBおよび第3グラフCから、前記ウェーハの全領域に形成されたキャパシタに対する漏れ電流特性も、前記ウェーハの上側、下側および中央に形成されたキャパシタの漏れ電流特性と同様に優秀であることが分かる。

次いで、図2に示した本発明のキャパシタの製造方法(以下、「本発明の製造方法」という)を説明する。

図4に示すとおり、本発明の製造方法は、第1段階60、第2段階62および第3段階64を含む。

第1段階60では、下部電極の上に第1酸化膜を形成する。前記下部電極は、導電性不純物がドーピングされたシリコン電極で形成することが望ましいが、他の導電性電極、例えば、チタンナイトライド電極で形成できる。前記第1酸化膜は、前述した本発明のキャパシタの第1誘電膜42と同等なものである。すなわち、前記第1酸化膜は、キャパシタの誘電膜の一部として利用されるが、主に、後述する第2酸化膜と前記下部電極の間の望ましくない反応を防止するための反応防止膜の役割を有する。したがって、前記第1酸化膜は、前記下部電極を構成する物質、例えば、シリコン(Si)と反応しない成分で形成することが望ましい。前記第1酸化膜は、後述する第2酸化膜より薄く、例えば、2nm程度の厚さに形成することが望ましいが、これより厚いか、または薄く形成できる。このように、前記第1酸化膜は、数nmの厚さに形成されるため、CVD方法のように既存の広く使われている薄膜蒸着方法を使用するよりは厚さの均一性および成分の均一性に優れ、厚さを微細に調節できるALDで形成することが望ましい。前記第1酸化膜は、単一膜に形成することが望ましいが、二重膜に形成しても良い。したがって、前記第1酸化膜は、ハフニウム酸化膜および/またはアルミニウム酸化膜で形成できる。

第2段階62において、前記第1酸化膜の上に第2酸化膜を形成する。前記第2酸化膜は、前記本発明のキャパシタの第2誘電膜44と同等のものである。したがって、前記第2酸化膜は、前記第1酸化膜が含むものよりも半径の大きい陽イオンを含む酸化膜で形成することが望ましい。例えば、前記第2酸化膜は、ランタン酸化膜(La2O3)等のランタニド系列の元素を含む酸化膜で形成することが望ましい。前記第2酸化膜は、前記第1酸化膜と同様に数nmの厚さに形成することが望ましい。しかし、前記第2酸化膜は、前記第1酸化膜と同じ厚さであるか、または前記第1酸化膜よりも厚く形成される。このように、前記第2酸化膜も数nmの厚さに形成するため、既存の薄膜蒸着方法よりもALD法で形成することが望ましい。ALD法を利用した前記第2酸化膜形成過程については後述する。

第3段階64では、前記第2酸化膜の上に上部電極を形成する。前記上部電極は、チタンナイトライド電極で形成される。前記上部電極は、導電性不純物がドーピングされたシリコン電極でもよい。

図5に示すとおり、前記第2段階62は、さらに3つの下位段階62a,62b,62cに細分できる。3つの下位段階62a,62b,62cにおいて、ALDを利用した前記第2酸化膜の形成方法をさらに詳細に説明する。ここで、前記第2酸化膜は、ランタン酸化膜(La2O3)とする。

具体的には、第1の下位段階62aにおいて、前記第1酸化膜の上に、前記第2酸化膜の金属性分(La)を含む前駆体、例えばLa(tmhd)3,La(N(Si(Me)3)2)3,またはLa(iPrCp)3を蒸着する。次いで、第1排気工程を実施して前記前駆体層を形成し、残りの前駆体を反応チャンバーから除去する。

第2の下位段階62bでは、前記前駆体層が酸化される。

具体的には、前記第1排気工程が実施された以後、前記反応チャンバーに、酸化ガス、例えば、水蒸気(H2O)を供給する。前記酸化ガスと前記前駆体層との間の置換反応を通じて前記前駆体層が酸化されて、前記下部電極の上に前記第2酸化膜、すなわち、ランタン酸化膜が形成される。次いで、第2排気工程を実施して、前記反応チャンバー内に存在する残りの酸化ガスを除去する。

具体的には、前記第1排気工程が実施された以後、前記反応チャンバーに、酸化ガス、例えば、水蒸気(H2O)を供給する。前記酸化ガスと前記前駆体層との間の置換反応を通じて前記前駆体層が酸化されて、前記下部電極の上に前記第2酸化膜、すなわち、ランタン酸化膜が形成される。次いで、第2排気工程を実施して、前記反応チャンバー内に存在する残りの酸化ガスを除去する。

第3の下位段階62cでは、前記第2酸化膜から不純物が除去される。

具体的には、前記第2排気工程後に前記反応チャンバーにオゾン(O3)を供給して前記第2酸化膜に過度に含まれている水蒸気を除去する。次に、前記反応チャンバーに残留するオゾンを除去するための第3排気工程を実施する。

具体的には、前記第2排気工程後に前記反応チャンバーにオゾン(O3)を供給して前記第2酸化膜に過度に含まれている水蒸気を除去する。次に、前記反応チャンバーに残留するオゾンを除去するための第3排気工程を実施する。

前記第2酸化膜に含まれた水蒸気が除去されるという点で、第3の下位段階62cは、前記第2酸化膜を乾燥する段階と見なすことができる。

また、前記第3の下位段階62cでは、前記不純物が除去されると同時に、流入された前記オゾンによって前記前駆体層が2次酸化される。したがって、前記第3の下位段階62cは、前記前駆体に対する2次酸化段階とも見なすことができる。

表1に示すとおり、オゾンを酸化ガスとして使用した時、およびオゾンをまず供給した後に水蒸気を供給した時には、下部電極の上に第2酸化膜が形成されない。

そして、水蒸気を酸化ガスとして使用した時は、下部電極の上に第2酸化膜が形成されるが、形成された第2酸化膜に水蒸気が含まれており、漏れ電流密度は1×10-1A/cm2と高い。

これに対して、本発明の製造方法によって、水蒸気をまず供給した後にオゾンを供給した場合には、下部電極の上に第2酸化膜が形成されるだけでなく、形成された第2酸化膜に水蒸気が残存せず、漏れ電流密度は1×10-7A/cm2と非常に低い。

次いで、図2に示したキャパシタを備える本発明の実施形態による半導体メモリ装置(以下、「本発明のメモリ装置」という)について説明する。

図6に示すとおり、本発明のメモリ装置は、基板70に導電性不純物がドープされて形成された第1領域74および第2領域76を有する。第1領域74および第2領域76は、所定の間隔だけ離れている。第1領域74はソース領域であり、第2領域76はドレーン領域である。基板70における第1領域74と第2領域76の間にチャンネル領域が形成され、前記チャンネル領域の上にゲート積層物72が配置される。ゲート積層物72は、印加される電圧によって第1領域74と第2領域76の間に形成されたチャンネル領域をスイッチングする役割を有する。ゲート積層物72は、ゲート絶縁膜(図示せず)とゲート導電層(図示せず)とを含む。基板70と、第1領域74および第2領域76と、ゲート積層物72とは、MOSFETを構成する。基板70上に、ゲート積層物72を覆う第1層間絶縁膜78が形成されており、第1層間絶縁膜78に第2領域76を露出する第1コンタクトホール80が形成されている。第1コンタクトホール80には、第1導電性プラグ82、例えば、導電性不純物がドーピングされたポリシリコンが充填されている。第1層間絶縁膜78の上に、第1導電性プラグ82の全面を覆うキャパシタCが形成されている。キャパシタCは、図2に示したキャパシタと同じであることが望ましい。したがって、キャパシタCの構成および作用に関する具体的な説明は省略する。下部電極40と第1導電性プラグ82とは同じ導電性物質で形成されていることが望ましいが、相異なる導電性物質で形成されていてもよい。第1層間絶縁膜78の上に、キャパシタCを覆う第2層間絶縁膜84が形成されている。第1層間絶縁膜78および第2層間絶縁膜84に、第1領域74を露出する第2コンタクトホール86が形成されている。第2コンタクトホール86には、第2導電性プラグ88が充填されている。第2導電性プラグ88は、例えば、導電性不純物がドーピングされたポリシリコンで形成されていることが望ましいが、他の導電性物質で形成されていていもよい。第2層間絶縁膜84の上に、第2導電性プラグ88の全面を覆う導電層90が形成されている。導電層90はビットラインであり、ゲート積層物72に垂直に交差する。導電層90と第2導電性プラグ88とは、同じ導電性物質で形成されていることが望ましいが、相異なる導電性物質で形成されていてもよい。

前述したメモリ装置の場合、図2に示したキャパシタを備えるため、キャパシタに保存されたデータは正常な状態で長期間保存できる。これは、保存されたデータを長時間経過後も正常に読み出せることを意味し、前述したメモリ装置の信頼性は高くなる。

前記説明で多くの事項が具体的に記載されているが、それらは本発明の範囲を限定するものではなく、望ましい実施形態の例示として解釈されなければならない。例えば、当業者ならば、反応防止膜として使われた第1誘電膜42として非酸化膜を使用できる。また、上部電極および下部電極を全てシリコンを含まない電極に代え、誘電膜DLをランタン酸化膜に代えることができる。したがって、本発明の範囲は、前述した実施形態に限定されず、特許請求の範囲に記載された技術的思想によって決定されなければならない。

本発明のキャパシタおよびそれを用いたメモリ装置は、メモリチップが使われる全ての機器に使用され、特に、各種のコンピュータ、カムコーダ、デジタルカメラ、携帯電話、計算機、メモリスチックやカード、信用カードをはじめとする各種のカードなどに使用することができる。

40 下部電極

42 第1誘電膜

44 第2誘電膜

46 上部電極

DL 誘電膜

42 第1誘電膜

44 第2誘電膜

46 上部電極

DL 誘電膜

Claims (33)

- 下部電極と、

前記下部電極の上に形成された誘電膜と、

前記誘電膜の上に形成された上部電極と、

前記下部電極と前記誘電膜の間に設けられた、前記下部電極と前記誘電膜の反応を防止する第1反応防止膜と、を含むことを特徴とする半導体装置のキャパシタ。 - 前記下部電極は、導電性不純物がドーピングされたシリコン電極であることを特徴とする請求項1に記載の半導体装置のキャパシタ。

- 前記第1反応防止膜は、前記誘電膜が含む陽イオンよりも半径が小さい陽イオンを含む、ハフニウム酸化膜またはアルミニウム酸化膜であることを特徴とする請求項1に記載の半導体装置のキャパシタ。

- 前記誘電膜は、ランタニド系列の元素を含む酸化膜であることを特徴とする請求項1に記載の半導体装置のキャパシタ。

- 前記ランタニド系列の元素を含む酸化膜が、La2O3膜であることを特徴とする請求項4に記載の半導体装置のキャパシタ。

- 前記上部電極は、チタンナイトライド膜であることを特徴とする請求項1に記載の半導体装置のキャパシタ。

- 前記上部電極は、導電性不純物がドーピングされたシリコン電極であり、前記上部電極と前記誘電膜の間に、さらに第2反応防止膜が設けられていることを特徴とする請求項1に記載の半導体装置のキャパシタ。

- 前記第2反応防止膜は、前記誘電膜が含むものよりも半径の小さい陽イオンを含むハフニウム酸化膜またはアルミニウム酸化膜であることを特徴とする請求項7に記載の半導体装置のキャパシタ。

- 前記誘電膜は、ランタニド系列の元素を含む酸化膜であることを特徴とする請求項3に記載の半導体装置のキャパシタ。

- 下部電極を形成する段階と、

前記下部電極の上に第1反応防止膜を形成する段階と、

前記第1反応防止膜の上に金属元素を含む前駆体層を形成する段階と、

前記前駆体層を酸化させて前記第1反応防止膜の上に前記金属元素を含む酸化膜を形成する段階と、

前記酸化膜を乾燥させる段階と、

前記乾燥された酸化膜の上に上部電極を形成する段階と、を含むことを特徴とするキャパシタの製造方法。 - 前記上部電極を形成する前に、前記乾燥された酸化膜の上に第2反応防止膜をさらに形成することを特徴とする請求項10に記載のキャパシタの製造方法。

- 前記下部電極は導電性不純物がドーピングされたシリコン電極で形成し、前記上部電極はチタンナイトライド膜で形成することを特徴とする請求項10に記載のキャパシタの製造方法。

- 前記下部電極および上部電極は、導電性不純物がドーピングされたシリコン電極またはチタンナイトライド膜で形成することを特徴とする請求項11に記載のキャパシタの製造方法。

- 前記上部電極および下部電極は、チタンナイトライド膜で形成することを特徴とする請求項10に記載のキャパシタの製造方法。

- 前記前駆体層を形成した後、排気工程を実施することを特徴とする請求項10に記載のキャパシタの製造方法。

- 前記酸化膜を形成した後、排気工程を実施することを特徴とする請求項10に記載のキャパシタの製造方法。

- 前記酸化膜を乾燥した後、排気工程を実施することを特徴とする請求項10に記載のキャパシタの製造方法。

- 前記酸化膜を形成する段階において、前記前駆体層の上に水蒸気を流して前記前駆体層を1次酸化させることを特徴とする請求項10に記載のキャパシタの製造方法。

- 前記1次酸化された前駆体層の上にオゾンを供給して、前記1次酸化された前駆体層を2次酸化させることを特徴とする請求項18に記載のキャパシタの製造方法。

- 前記酸化膜を形成する段階において、前記1次酸化および2次酸化を繰返して行なうことを特徴とする請求項19に記載のキャパシタの製造方法。

- 前記金属元素は、ランタニド系列の元素であることを特徴とする請求項10に記載のキャパシタの製造方法。

- 前記酸化膜を乾燥させる段階において、前記酸化膜はその上にオゾンを流して乾燥させることを特徴とする請求項10に記載のキャパシタの製造方法。

- 前記第1反応防止膜は、前記誘電膜が含むものよりも半径の小さい陽イオンを含むハフニウム酸化膜またはアルミニウム酸化膜で形成することを特徴とする請求項10に記載のキャパシタの製造方法。

- 前記第2反応防止膜は、前記誘電膜が含むものよりも半径の小さい陽イオンを含むハフニウム酸化膜またはアルミニウム酸化膜で形成することを特徴とする請求項11に記載のキャパシタの製造方法。

- 前記金属元素は、ランタニド系列の元素であることを特徴とする請求項18に記載のキャパシタの製造方法。

- 前記金属元素は、ランタニド系列の元素であることを特徴とする請求項19に記載のキャパシタの製造方法。

- トランジスタとそれに連結されたキャパシタとを備える半導体メモリ装置において、

前記キャパシタは、

下部電極と、

前記下部電極の上に形成された誘電膜と、

前記誘電膜の上に形成された上部電極と、

前記下部電極と前記誘電膜の間に設けられた、前記下部電極と前記誘電膜の反応を防止する第1反応防止膜と、を含むことを特徴とする半導体メモリ装置。 - 前記下部電極は導電性不純物がドーピングされたシリコン電極であり、前記上部電極はチタンナイトライド電極であることを特徴とする請求項27に記載の半導体メモリ装置。

- 前記第1反応防止膜は、前記誘電膜が含むものよりも半径の小さい陽イオンを含むハフニウム酸化膜またはアルミニウム酸化膜であることを特徴とする請求項27に記載の半導体メモリ装置。

- 前記上部電極と前記誘電膜の間に、さらに第2反応防止膜が設けられていることを特徴とする請求項27に記載の半導体メモリ装置。

- 前記誘電膜は、ランタニド系列の元素を含む酸化膜であることを特徴とする請求項27に記載の半導体メモリ装置。

- 前記第2反応防止膜は、前記誘電膜が含むものよりも半径の小さい陽イオンを含むハフニウム酸化膜またはアルミニウム酸化膜であることを特徴とする請求項30に記載の半導体メモリ装置。

- 前記誘電膜は、ランタニド系列の元素を含む酸化膜であることを特徴とする請求項30に記載の半導体メモリ装置。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020030056857A KR101001741B1 (ko) | 2003-08-18 | 2003-08-18 | 반도체 장치의 커패시터 및 그 제조 방법과 커패시터를구비하는 메모리 장치 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005064523A true JP2005064523A (ja) | 2005-03-10 |

Family

ID=34056926

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004237223A Withdrawn JP2005064523A (ja) | 2003-08-18 | 2004-08-17 | 半導体装置のキャパシタとその製造方法、およびそのキャパシタを備えるメモリ装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US20050082593A1 (ja) |

| EP (1) | EP1508906A3 (ja) |

| JP (1) | JP2005064523A (ja) |

| KR (1) | KR101001741B1 (ja) |

| CN (1) | CN1610120A (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007266474A (ja) * | 2006-03-29 | 2007-10-11 | Hitachi Ltd | 半導体記憶装置 |

| JP6529675B1 (ja) * | 2018-01-19 | 2019-06-12 | 三菱電機株式会社 | 薄層キャパシタおよび薄層キャパシタの製造方法 |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7217615B1 (en) | 2000-08-31 | 2007-05-15 | Micron Technology, Inc. | Capacitor fabrication methods including forming a conductive layer |

| US7112503B1 (en) | 2000-08-31 | 2006-09-26 | Micron Technology, Inc. | Enhanced surface area capacitor fabrication methods |

| US6420230B1 (en) * | 2000-08-31 | 2002-07-16 | Micron Technology, Inc. | Capacitor fabrication methods and capacitor constructions |

| US7105065B2 (en) | 2002-04-25 | 2006-09-12 | Micron Technology, Inc. | Metal layer forming methods and capacitor electrode forming methods |

| US7440255B2 (en) | 2003-07-21 | 2008-10-21 | Micron Technology, Inc. | Capacitor constructions and methods of forming |

| KR100590592B1 (ko) * | 2004-08-20 | 2006-06-19 | 삼성전자주식회사 | 누설 전류를 감소시킨 유전체층을 포함하는 캐패시터 및그 제조 방법 |

| KR100693890B1 (ko) * | 2005-04-21 | 2007-03-12 | 삼성전자주식회사 | 반응 장벽막을 갖는 반도체 장치의 제조 방법 |

| US7611972B2 (en) * | 2006-11-29 | 2009-11-03 | Qimonda North America Corp. | Semiconductor devices and methods of manufacture thereof |

| JP2008166360A (ja) * | 2006-12-27 | 2008-07-17 | Hitachi Ltd | 半導体集積回路装置 |

| US7662693B2 (en) | 2007-09-26 | 2010-02-16 | Micron Technology, Inc. | Lanthanide dielectric with controlled interfaces |

| WO2010144092A1 (en) | 2009-06-12 | 2010-12-16 | Hewlett-Packard Development Company, L.P. | Capacitive crossbar arrays |

| WO2010147588A1 (en) * | 2009-06-18 | 2010-12-23 | Hewlett-Packard Development Company, L.P. | Memcapacitor |

| US20110298089A1 (en) * | 2010-06-03 | 2011-12-08 | International Business Machines Corporation | Trench capacitor and method of fabrication |

| KR101977271B1 (ko) * | 2013-04-05 | 2019-05-10 | 에스케이하이닉스 주식회사 | 반도체 장치의 제조 방법 |

| KR102665567B1 (ko) | 2018-04-12 | 2024-05-14 | 엘에스엠트론 주식회사 | 견인부하조절장치가 구비된 농작업차량 |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3351856B2 (ja) * | 1992-04-20 | 2002-12-03 | テキサス インスツルメンツ インコーポレイテツド | 構造体およびコンデンサの製造方法 |

| US6194751B1 (en) * | 1994-11-15 | 2001-02-27 | Radiant Technologies, Inc | Ferroelectric based memory devices utilizing low Curie point ferroelectrics and encapsulation |

| JPH0969509A (ja) * | 1995-09-01 | 1997-03-11 | Matsushita Electron Corp | 半導体ウェーハの洗浄・エッチング・乾燥装置及びその使用方法 |

| US6218260B1 (en) * | 1997-04-22 | 2001-04-17 | Samsung Electronics Co., Ltd. | Methods of forming integrated circuit capacitors having improved electrode and dielectric layer characteristics and capacitors formed thereby |

| US5841186A (en) * | 1997-08-19 | 1998-11-24 | United Microelectronics Corp. | Composite dielectric films |

| KR100293713B1 (ko) * | 1998-12-22 | 2001-07-12 | 박종섭 | 메모리소자의 커패시터 제조방법 |

| US6576053B1 (en) * | 1999-10-06 | 2003-06-10 | Samsung Electronics Co., Ltd. | Method of forming thin film using atomic layer deposition method |

| US6607950B2 (en) * | 2000-03-30 | 2003-08-19 | Interuniversitair Microelektronic Centrum (Imec) | MIS transistors with a metal gate and high-k dielectric and method of forming |

| US6503314B1 (en) * | 2000-08-28 | 2003-01-07 | Sharp Laboratories Of America, Inc. | MOCVD ferroelectric and dielectric thin films depositions using mixed solvents |

| US6660660B2 (en) * | 2000-10-10 | 2003-12-09 | Asm International, Nv. | Methods for making a dielectric stack in an integrated circuit |

| US6794694B2 (en) * | 2000-12-21 | 2004-09-21 | Agere Systems Inc. | Inter-wiring-layer capacitors |

| US6511873B2 (en) * | 2001-06-15 | 2003-01-28 | International Business Machines Corporation | High-dielectric constant insulators for FEOL capacitors |

| US6642131B2 (en) * | 2001-06-21 | 2003-11-04 | Matsushita Electric Industrial Co., Ltd. | Method of forming a silicon-containing metal-oxide gate dielectric by depositing a high dielectric constant film on a silicon substrate and diffusing silicon from the substrate into the high dielectric constant film |

| US6734477B2 (en) * | 2001-08-08 | 2004-05-11 | Agilent Technologies, Inc. | Fabricating an embedded ferroelectric memory cell |

| US7087481B2 (en) * | 2002-08-28 | 2006-08-08 | Micron Technology, Inc. | Systems and methods for forming metal oxides using metal compounds containing aminosilane ligands |

| US6858524B2 (en) * | 2002-12-03 | 2005-02-22 | Asm International, Nv | Method of depositing barrier layer for metal gates |

| KR100546324B1 (ko) * | 2003-04-22 | 2006-01-26 | 삼성전자주식회사 | Ald에 의한 금속 산화물 박막 형성 방법, 란탄 산화막 형성 방법 및 반도체 소자의 고유전막 형성 방법 |

| KR20050007496A (ko) * | 2003-07-08 | 2005-01-19 | 삼성전자주식회사 | 원자층 적층 방식의 복합막 형성방법 및 이를 이용한반도체 소자의 커패시터 형성방법 |

-

2003

- 2003-08-18 KR KR1020030056857A patent/KR101001741B1/ko not_active IP Right Cessation

-

2004

- 2004-08-17 EP EP04254930A patent/EP1508906A3/en not_active Withdrawn

- 2004-08-17 JP JP2004237223A patent/JP2005064523A/ja not_active Withdrawn

- 2004-08-18 US US10/920,455 patent/US20050082593A1/en not_active Abandoned

- 2004-08-18 CN CNA2004100959626A patent/CN1610120A/zh active Pending

-

2008

- 2008-12-10 US US12/314,427 patent/US20090126173A1/en not_active Abandoned

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007266474A (ja) * | 2006-03-29 | 2007-10-11 | Hitachi Ltd | 半導体記憶装置 |

| JP6529675B1 (ja) * | 2018-01-19 | 2019-06-12 | 三菱電機株式会社 | 薄層キャパシタおよび薄層キャパシタの製造方法 |

| WO2019142317A1 (ja) * | 2018-01-19 | 2019-07-25 | 三菱電機株式会社 | 薄層キャパシタおよび薄層キャパシタの製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20090126173A1 (en) | 2009-05-21 |

| KR20050019218A (ko) | 2005-03-03 |

| EP1508906A3 (en) | 2006-12-06 |

| US20050082593A1 (en) | 2005-04-21 |

| EP1508906A2 (en) | 2005-02-23 |

| KR101001741B1 (ko) | 2010-12-15 |

| CN1610120A (zh) | 2005-04-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4722501B2 (ja) | 半導体素子の多層誘電体構造物、半導体及びその製造方法 | |

| US7465982B2 (en) | Capacitor structures | |

| US7323422B2 (en) | Dielectric layers and methods of forming the same | |

| US20090126173A1 (en) | Method of manufacturing a capacitor and memory device including the same | |

| US9418999B2 (en) | MIM capacitors with improved reliability | |

| US20090011608A1 (en) | Manufacturing method of semiconductor device | |

| JP2002534818A (ja) | 半導体構造素子およびその製造方法 | |

| JP2009059882A (ja) | 半導体装置 | |

| JP2004214661A (ja) | トランジスタゲートの製造及び高誘電率ゲート誘電体の粗さを減少する方法 | |

| JP2004134579A (ja) | キャパシタ及びその製造方法 | |

| JP3822378B2 (ja) | 半導体装置の製造方法 | |

| US6548854B1 (en) | Compound, high-K, gate and capacitor insulator layer | |

| JP2007150285A (ja) | 半導体装置のデュアルゲート構造物及びその形成方法 | |

| JP2004079931A (ja) | 半導体装置の製造方法 | |

| JP2006120848A (ja) | 半導体装置及びその製造方法 | |

| US20060063290A1 (en) | Method of fabricating metal-insulator-metal capacitor | |

| JP2007329286A (ja) | 半導体装置、およびその製造方法 | |

| US20060079075A1 (en) | Gate structures with silicide sidewall barriers and methods of manufacturing the same | |

| EP1020896A1 (en) | Integrated circuit device with composite oxide dielectric | |

| JP2004193176A (ja) | 半導体装置およびその製造方法 | |

| JP2000307069A (ja) | 半導体装置の製造方法 | |

| KR100546151B1 (ko) | 반도체소자의 캐패시터 제조방법 | |

| KR100790567B1 (ko) | 고유전율의 복합 게이트절연막을 갖는 반도체소자 및 그제조방법 | |

| JP2003188374A (ja) | 半導体装置およびその製造方法 | |

| KR100376987B1 (ko) | 반도체소자의 캐패시터 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20061102 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20061106 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070418 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20090525 |