JP2004061985A - Drive circuit for liquid crystal display - Google Patents

Drive circuit for liquid crystal display Download PDFInfo

- Publication number

- JP2004061985A JP2004061985A JP2002222236A JP2002222236A JP2004061985A JP 2004061985 A JP2004061985 A JP 2004061985A JP 2002222236 A JP2002222236 A JP 2002222236A JP 2002222236 A JP2002222236 A JP 2002222236A JP 2004061985 A JP2004061985 A JP 2004061985A

- Authority

- JP

- Japan

- Prior art keywords

- operational amplifier

- data

- phase compensation

- liquid crystal

- well

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Liquid Crystal (AREA)

- Liquid Crystal Display Device Control (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

Abstract

Description

【0001】

【発明の属する技術分野】

本発明は、液晶表示装置の駆動回路に関し、特に演算増幅器に接続された位相補償容量素子がNウェル容量素子からなる液晶表示装置の駆動回路に関する。

【0002】

【従来の技術】

アクティブマトリックス方式の液晶表示装置の液晶表示モジュールは、図3に示すように、液晶パネル(LCDパネル)1と、半導体集積回路装置(以下、ICという)からなる制御回路(以下、コントローラという)2と、ICからなる複数個の走査側駆動回路(以下、走査側ドライバという)3およびデータ側駆動回路(以下、データ側ドライバという)4とを具備している。液晶パネル1は、詳細を図示しないが、透明な画素電極および薄膜トランジスタ(TFT)を配置した半導体基板と、面全体に1つの透明な電極を形成した対向基板と、これら2枚の基板を対向させて間に液晶を封入した構造からなり、対向基板電極に所定の電圧(以下、コモン電圧Vcomという)を供給するとともに、スイッチング機能を持つTFTを制御することにより各画素電極に所定の電圧を印加し、各画素電極と対向基板電極との間の電位差により液晶の透過率を変化させて画像を表示するものである。ここで、画像を中間調表示(階調表示)するために各画素電極には所定の電圧として可変の電圧(以下、階調電圧という)が印加される。半導体基板上には、各画素電極へ印加する階調電圧を送るデータ線と、TFTのスイッチング制御信号(走査信号)を送る走査線とが配線されている。

【0003】

コントローラ2は、入力側がPC(パソコン)5に接続され、出力側が走査側ドライバ3およびデータ側ドライバ4に接続されている。走査側ドライバ3およびデータ側ドライバ4の出力側は、液晶パネル1の走査線およびデータ線にそれぞれ接続されている。走査側ドライバ3およびデータ側ドライバ4は、製造上の制限よりチップサイズが制限され、従って、IC1個で出力できる走査線およびデータ線に対応する出力数も制限され、液晶パネル1のサイズが大きい場合、それぞれ複数個を液晶パネル1の外周に配置する必要がある。例えばXGA(1024×768画素)カラー表示の液晶パネルの場合の各ドライバ3,4のモジュールへの実装は、

▲1▼走査側ドライバ3は、768本のゲート線を駆動する必要があり、例えば192本分の駆動能力を有する場合、4個必要とし、液晶パネル1の左側外周にカスケード接続で片側配置される。

▲2▼データ側ドライバ4は、1画素をカラー表示するためにデータ線はR(赤)、G(緑)、B(青)用の3本が必要なため、1024×3=3072本のデータ線を駆動する必要があり、例えば、384本分の駆動能力を有する場合、8個を必要とし、液晶パネル1の上側外周にカスケード接続で片側配置される。

尚、図示しないが、対向基板電極には、コモン電圧Vcomを供給するための電源回路が接続されている。

【0004】

PC5から画像データが液晶表示モジュールのコントローラ2に送られ、コントローラ2から走査側ドライバ3には、クロック信号等が各走査側ドライバ3に並列に送られ、垂直同期用のスタート信号STVが初段の走査側ドライバ3に送られ、カスケード接続された次段以降の走査側ドライバ3に順次転送されていく。また、コントローラ2からデータ側ドライバ4には、クロック信号等のタイミング信号やデータ信号が各データ側ドライバ4に並列に送られ、水平同期用のスタート信号STHが初段のデータ側ドライバ4に送られ、カスケード接続された次段以降のデータ側ドライバ4に順次転送されていく。そして、走査側ドライバ3から各走査線にはパルス状の走査信号が送られ、走査線に印加された走査信号がハイレベルのとき、その走査線につながるTFTが全てオンとなり、そのときデータ側ドライバ4からデータ線に送られた階調電圧が、オンとなったTFTを介して画素電極に印加される。このとき、図示しない電源回路から対向基板電極にコモン電圧Vcomが供給される。そして、走査信号がローレベルとなり、TFTがオフ状態に変化すると、画素電極と対向基板電極との電位差は、次の階調電圧が画素電極に印加されるまでの間保持される。そして、各走査線に順次走査信号を送ることにより、全ての画素電極に所定の階調電圧が印加され、フレーム周期で階調電圧の書き替えを行うことにより画像を表示することができる。

【0005】

データ側ドライバ4により各画素電極を駆動するとき、液晶固有の特性から対向基板電極の電位に対して交流駆動する必要がある。代表的な交流駆動方法として、データ側ドライバ4からの階調電圧を1走査線を駆動する期間(以下、1水平期間という)ごとにコモン電圧Vcomに対して正電圧と負電圧を、1走査線単位で切り換えるライン反転駆動法や、1画素電極単位で切り換えるドット反転駆動法がある。ライン反転駆動法は、データ側ドライバ4からの階調電圧を、例えば、+5V以下の低電圧に設定し、コモン電圧Vcomを1水平期間ごとに変化させることにより極性反転して交流駆動する方法である。これに対して、ドット反転駆動法は、コモン電圧Vcomを一定電圧に固定し、データ側ドライバ4からの階調電圧としてコモン電圧Vcomに対して、極性が正の電圧(以下、正極性階調電圧という)と、極性が負の電圧(以下、負極性階調電圧という)をそれぞれ対称となるように設定して、正極性階調電圧と負極性階調電圧を1水平期間ごとに交互に供給する方法である。例えば、64階調表示の場合、正極性階調電圧VP1〜VP64としてVcom<VP64<…<VP1、および負極性階調電圧VN1〜VN64としてVcom>VN64>…>VN1で、正極性階調電圧VP1〜VP64と負極性階調電圧VN1〜VN64とがコモン電圧Vcomに対してそれぞれ対称に設定される。そして、正極性階調電圧VP1〜VP64のうちのひとつの階調電圧VPxと、負極性階調電圧VN1〜VN64のうちのひとつの階調電圧VNxとが1水平期間ごとに交互に供給される。

【0006】

以下に、データ側ドライバ4の従来例として、ドット反転駆動法を用いたデータ側ドライバ100について、液晶パネルのデータ線384本分を駆動し、64階調表示する能力を有するものとして、図4を参照して説明する。データ側ドライバ100は、384本の各データ線に対応して、画像データとしてm=6ビットのデータ信号DATAを供給することにより、2のm乗=64階調の正極性および負極性階調電圧VP1〜VP64、VN1〜VN64のうちデータ信号DATAの論理に対応した1つの階調電圧VPx、VNxを1水平期間ごとに極性が交互にかつ2n−1(奇数)番目(n=1〜192)のデータ線と2n(偶数)番目のデータ線とで互い違いとなるようにして出力するもので、384本の各データ線に対応して、データ信号DATAをシリアル/パラレル変換し、さらに1水平期間ごとに極性が交互にかつ2n−1番目のデータ線と2n番目のデータ線とで互い違いの階調電圧VPx、VNxにデジタル/アナログ変換して出力する前段回路部10と、データ線384本に対応して前段回路部10からの階調電圧VPx,VNxを駆動能力を上げて出力する384個のボルテージホロワ接続の演算増幅器20と、演算増幅器20の発振を防止するための位相補償容量素子30とを備えている。

【0007】

次にデータ側ドライバ100を液晶パネルに接続したときの動作を図5を参照して説明する。ある1水平期間において、前段回路部10に極性制御信号POLが“ハイ”レベルで供給され、384本の各データ線に対応するm=6ビットのデータ信号DATAがシリアルに取り込まれ、内部で、パラレルに変換され、ストローブ信号STBに同期して、2n−1番目のデータ線に対応して64階調の階調電圧VP1〜VP64のうちのひとつの階調電圧VPxにアナログ変換されるとともに、2n番目のデータ線に対応して64階調の階調電圧VN1〜VN64のうちのひとつの階調電圧VNxにアナログ変換され、各演算増幅器20で各階調電圧VPx、VNxの駆動能力を上げて出力S1、S2、…、S384として液晶パネルの対応する各データ線に供給される。

【0008】

次の1水平期間において、前段回路部10に極性制御信号POLが“ロウ”レベルで供給され、384本の各データ線に対応するm=6ビットのデータ信号DATAがシリアルに取り込まれ、内部で、パラレルに変換され、ストローブ信号STBに同期して、2n−1番目のデータ線に対応して64階調の階調電圧VN1〜VN64のうちのひとつの階調電圧VNxにアナログ変換されるとともに、2n番目のデータ線に対応して64階調の階調電圧VP1〜VP64のうちのひとつの階調電圧VPxにアナログ変換され、各演算増幅器20で各階調電圧VPx、VNxの駆動能力を上げて出力S1、S2、…、S384として液晶パネルの対応する各データ線に供給される。

【0009】

【発明が解決しようとする課題】

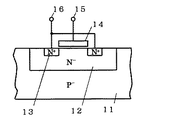

ところで、上述したように演算増幅器20の発振防止のための位相補償容量素子30が用いられているが、位相補償容量素子30としてNウェル容量素子を用いた場合について、以下、説明する。Nウェル容量素子は、図6に示すように、P型半導体基板11に形成されたNウェル層12にN+拡散層13が形成され、N+拡散層13間のNウェル層12上にゲート酸化膜を介してゲート電極14が形成されるとともに、ゲート電極14にゲート側端子15が接続され、N+拡散層にウェル側端子16が接続されて構成されている。このNウェル容量素子は、図7に示すような電圧依存性を有する。すなわち、ゲート側端子15とウェル側端子16に電圧を印加した場合、ウェル側端子16を基準電位として閾値電圧以上の正電圧で容量が最大となり、閾値電圧より低くなると容量が減少し、ある電圧以下の負電圧になると容量が最小となる。

【0010】

一方、データ側ドライバ100に用いられる演算増幅器20は、各出力S1、S2、…、S384から正極性階調電圧VPxと負極性階調電圧VNxを1水平期間ごとに交互に出力するために、立ち上がり波形および立ち下がり波形の両出力を高速にできるものが用いられ、具体的回路の一例として、例えば、図8に示す演算増幅器20が用いられる。この図8に示す演算増幅器20は、特開平9−93055号公報に記載されている。そして、図8において、位相補償容量素子30は、演算増幅器20の差動段出力、すなわち、MOSトランジスタM14のゲートと出力端子Vout間に接続されるが、MOSトランジスタM14のゲートと出力端子Vout間の電位差は、図9に示すように、出力端子Voutを基準電位として立ち下がり波形の出力時に正側で大となり、立ち上がり波形の出力時に負側で小となる。従って、位相補償容量素子30として、図6に示すNウェル容量素子を用いる場合、立ち下がり波形の出力時に、MOSトランジスタM14のゲートと出力端子Vout間の大きな正側の電位差が、Nウェル容量素子のゲート側端子15とウェル側端子16間にウェル側端子16を基準電位として正電圧で印加され、立ち上がり波形の出力時に、MOSトランジスタM14のゲートと出力端子Vout間の小さな負側の電位差が、Nウェル容量素子のゲート側端子15とウェル側端子16間にウェル側端子16を基準電位として負電圧で印加されるようにするため、ゲート側端子15がMOSトランジスタM14のゲートに接続され、ウェル側端子16が出力端子Voutに接続されて構成される。尚、図8では、位相補償容量素子30をゲート側が太線、ウェル側が細線で表示されたNウェル容量素子として表示している。

【0011】

上述のようにNウェル容量素子を位相補償容量素子として用いた場合において、位相補償容量素子の容量値を立ち下がり波形の出力時に必要とする容量値に合わせて決めた場合、立ち上がり波形の出力時の容量が必要とする容量値より小さくなる虞があり、最悪の場合、演算増幅器20が発振する。また、逆に立ち上がり波形の出力時に必要とする容量値に合わせて決めた場合、立ち下がり波形の出力時の容量値が必要とする容量値より大きくなる虞がある。この場合、演算増幅器20の立ち下がり波形の出力時のスルーレートを小さくするという不都合が生じることになる。また、容量値は、ドライバICのチップ面積を小さくするいう観点から、できる限り小さくする必要があり、容量値が必要とする容量値より大きくなるということは、これに反する。

【0012】

従って、本発明は上記の問題点を解決するためになされたもので、演算増幅器に接続されるNウェル容量素子からなる位相補償容量素子の容量値を立ち上がり波形の出力時と立ち下がり波形の出力時のそれぞれにおいて、必要とする適切な容量値とすることができる液晶表示装置の駆動回路を提供することを目的とする。

【0013】

【課題を解決するための手段】

(1)本発明の液晶表示装置の駆動回路は、液晶パネルのデータ線に接続される演算増幅器と、演算増幅器に接続されるNウェル容量素子からなる位相補償容量素子とを備えた液晶表示装置の駆動回路において、容量値の相異なる2個1組の位相補償容量素子を有し、演算増幅器が立ち下がり波形を出力するとき、2個1組の位相補償容量素子のうち容量値が大きい位相補償容量素子が接続されるとともに、演算増幅器が立ち上がり波形を出力するとき、2個1組の位相補償容量素子のうち容量値が小さい位相補償容量素子が、容量値が大きい位相補償容量素子に対しNウェル容量素子の端子を逆方向にして接続されることを特徴とする。

(2)本発明の液晶表示装置の駆動回路は、上記(1)項において、演算増幅器が、立ち上がり波形と立ち下がり波形を交互に出力することを特徴とする。

(3)本発明の液晶表示装置の駆動回路は、上記(2)項において、立ち上がり波形と立ち下がり波形を奇数データ線と偶数データ線とで互い違いに出力する2個1組の演算増幅器に上記2個1組の位相補償容量素子が互い違いに接続されることを特徴とする。

(4)本発明の液晶表示装置の駆動回路は、上記(2)項において、立ち上がり波形と立ち下がり波形を出力するデータ線1本に対応して1個の演算増幅器に上記2個1組の位相補償容量素子が交互に接続されることを特徴とする。

【0014】

【発明の実施の形態】

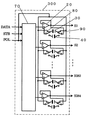

以下に、本発明に基づき、第1実施例のドット反転駆動法を用いたデータ側ドライバ200について、液晶パネルのデータ線384本分を駆動し、64階調表示する能力を有するものとして、図1を参照して説明する。尚、図4に示したデータ側ドライバ100と同一部分は同一符号を付して、重複する説明を省略する。

データ側ドライバ200は、384本の各データ線に対応して、画像データとしてm=6ビットのデータ信号DATAを供給することにより、2のm乗=64階調の正極性および負極性階調電圧VP1〜VP64、VN1〜VN64のうちデータ信号DATAの論理に対応した1つの階調電圧VPx、VNxを1水平期間ごとに極性が交互にかつ2n−1(奇数)番目(n=1〜192)のデータ線と2n(偶数)番目のデータ線とで互い違いとなるようにして出力するもので、前段回路部10と、384個のボルテージホロワ接続の演算増幅器20と、各192個の位相補償容量素子30,40と、各192個の切替えスイッチ50,60とを備えている。位相補償容量素子30,40は、それぞれ図6に示すNウェル容量素子で構成される。位相補償容量素子30は、2n−1番目と2n番目のデータ線に対応した2個の演算増幅器20のうち、立ち下がり波形の出力時の演算増幅器20のMOSトランジスタM14のゲートにゲート側端子15が、および出力端子Voutにウェル側端子16が、切替えスイッチ50,60を介して接続され、その容量値は、立ち下がり波形の出力時の演算増幅器20が発振しないレベルに設定される。位相補償容量素子40は、2n−1番目と2n番目のデータ線に対応した2個の演算増幅器20のうち、立ち上がり波形の出力時の演算増幅器20のMOSトランジスタM14のゲートにウェル側端子16が、および出力端子Voutにゲート側端子15が、切替えスイッチ50,60を介して接続され、その容量値は、立ち上がり波形の出力時の演算増幅器20が発振しないレベルに設定される。このとき、位相補償容量素子の容量値は、立ち下がり波形を出力するときよりも立ち上がり波形を出力するときの方が小さくて済むので、ゲート側端子15とウェル側端子16間にウェル側端子16を基準電位として正電圧を印加したときの容量値は、位相補償容量素子30より位相補償容量素子40の方が小さく設定される。切替えスイッチ50,60は、外部から供給される極性制御信号POLにより切替えられる。

【0015】

次にデータ側ドライバ200を液晶パネルに接続したときの動作を図5を参照して説明する。ある1水平期間において、前段回路部10に極性制御信号POLが“ハイ”レベルで供給され、384本の各データ線に対応するm=6ビットのデータ信号DATAがシリアルに取り込まれ、内部で、パラレルに変換され、ストローブ信号STBに同期して、2n−1番目のデータ線に対応して64階調の階調電圧VP1〜VP64のうちのひとつの階調電圧VPxにアナログ変換されるとともに、2n番目のデータ線に対応して64階調の階調電圧VN1〜VN64のうちのひとつの階調電圧VNxにアナログ変換され、各演算増幅器20で各階調電圧VPx、VNxの駆動能力を上げて出力S1、S2、…、S384として液晶パネルの対応する各データ線に供給される。このとき、各切替えスイッチ50,60に極性制御信号POLが“ハイ”レベルで供給され、2n−1番目のデータ線に対応する演算増幅器20に位相補償容量素子40が接続されるとともに2n番目のデータ線に対応する演算増幅器20に位相補償容量素子30が接続される。

【0016】

次の1水平期間において、前段回路部10に極性制御信号POLが“ロウ”レベルで供給され、384本の各データ線に対応するm=6ビットのデータ信号DATAがシリアルに取り込まれ、内部で、パラレルに変換され、ストローブ信号STBに同期して、2n−1番目のデータ線に対応して64階調の階調電圧VN1〜VN64のうちのひとつの階調電圧VNxにアナログ変換されるとともに、2n番目のデータ線に対応して64階調の階調電圧VP1〜VP64のうちのひとつの階調電圧VPxにアナログ変換され、各演算増幅器20で各階調電圧VPx、VNxの駆動能力を上げて出力S1、S2、…、S384として液晶パネルの対応する各データ線に供給される。このとき、各切替えスイッチ50,60に極性制御信号POLが“ロウ”レベルで供給され、2n−1番目のデータ線に対応する演算増幅器20に位相補償容量素子30が接続されるとともに2n番目のデータ線に対応する演算増幅器20に位相補償容量素子40が接続される。

【0017】

以上、第1実施例で説明したように、立ち下がり波形の出力時用に容量値を設定したNウェル容量素子からなる位相補償容量素子30と立ち上がり波形の出力時用に容量値を設定したNウェル容量素子からなる位相補償容量素子40とを切替えスイッチ50,60を介してNウェル容量素子のゲート側端子とウェル側端子とを逆並列に接続している。そして、2n−1番目と2n番目のデータ線に対応した2個の演算増幅器20のうち、立ち上がり波形の出力時の演算増幅器20に位相補償容量素子40を接続するとともに、立ち下がり波形の出力時の演算増幅器20に位相補償容量素子30を接続するようにしている。その結果、立ち上がり波形および立ち下がり波形のそれぞれの出力時に適合したNウェル容量素子の容量値を設定でき、容量値が小さ過ぎることにより演算増幅器が発振することや、逆に必要以上に大き過ぎてスルレートが小さくなるという不都合を防止でき、また、データ側ドライバのチップ面積を小さくすることができる。

【0018】

次に、第2実施例のライン反転駆動法を用いたデータ側ドライバ300について、液晶パネルのデータ線384本分を駆動し、64階調表示する能力を有するものとして、図2を参照して説明する。尚、図1に示したデータ側ドライバ200と同一部分は同一符号を付して、重複する説明を省略する。データ側ドライバ300は、コモン電圧Vcomを1水平期間ごとに変化させることにより極性反転して交流駆動するコモン反転駆動法に用いられるため、正極性および負極性の2種類の階調電圧が不要で、384本の各データ線に対応して、画像データとしてm=6ビットのデータ信号DATAを供給することにより、2のm乗=64階調の階調電圧V1〜V64のうちデータ信号DATAの論理に対応した1つの階調電圧Vxを各データ線に1水平期間ごとに出力するもので、384本の各データ線に対応して、データ信号DATAをシリアル/パラレル変換し、1水平期間ごとに階調電圧Vxにデジタル/アナログ変換して出力する前段回路部70と、384個のボルテージホロワ接続の演算増幅器20と、各384個の位相補償容量素子30,40と、各384個の切替えスイッチ80,90とを備えている。位相補償容量素子30,40は、それぞれ図6に示すNウェル容量素子で構成される。各位相補償容量素子30は、各演算増幅器20の立ち下がり波形の出力時にゲート側端子15がMOSトランジスタM14のゲートに、およびウェル側端子16が出力端子Voutに、切替えスイッチ80,90を介して接続され、その容量値は、各演算増幅器20が立ち下がり波形の出力時に発振しないレベルに設定される。各位相補償容量素子40は、各演算増幅器20の立ち上がり波形の出力時にゲート側端子15が出力端子Voutに、およびウェル側端子16がMOSトランジスタM14のゲートに、切替えスイッチ80,90を介して接続され、その容量値は、各演算増幅器20が立ち上がり波形の出力時に発振しないレベルに設定される。このとき、位相補償容量素子の容量値は、立ち下がり波形を出力するときよりも立ち上がり波形を出力するときの方が小さくて済むので、ゲート側端子15とウェル側端子16間にウェル側端子16を基準電位として正電圧を印加したときの容量値は、位相補償容量素子30より位相補償容量素子40の方が小さく設定される。切替えスイッチ80,90は、外部から供給される極性制御信号POLにより切替えられる。

【0019】

次にデータ側ドライバ300を液晶パネルに接続したときの動作を説明する。ある1水平期間において、前段回路部70に極性制御信号POLが“ハイ”レベルで供給され、384本の各データ線に対応するm=6ビットのデータ信号DATAがシリアルに取り込まれ、内部で、パラレルに変換され、ストローブ信号STBに同期して、各データ線に対応して64階調の階調電圧V1〜V64のうちのひとつの階調電圧Vxにアナログ変換され、各演算増幅器20で各階調電圧Vxの駆動能力を上げて出力S1、S2、…、S384として液晶パネルの対応する各データ線に供給される。このとき、コモン電圧Vcomは、負電圧が供給され、各演算増幅器20は立ち上がり波形を出力することになる。このとき、各切替えスイッチ80,90に極性制御信号POLが“ハイ”レベルで供給され、各演算増幅器20に位相補償容量素子40が接続される。

【0020】

次の1水平期間において、前段回路部70に極性制御信号POLが“ロウ”レベルで供給され、384本の各データ線に対応するm=6ビットのデータ信号DATAがシリアルに取り込まれ、内部で、パラレルに変換され、ストローブ信号STBに同期して、各データ線に対応して64階調の階調電圧V1〜V64のうちのひとつの階調電圧Vxにアナログ変換され、各演算増幅器20で各階調電圧Vxの駆動能力を上げて出力S1、S2、…、S384として液晶パネルの対応する各データ線に供給される。このとき、コモン電圧Vcomは、正電圧が供給され、各演算増幅器20は立ち下がり波形を出力することになる。このとき、各切替えスイッチ80,90に極性制御信号POLが“ロウ”レベルで供給され、演算増幅器20に位相補償容量素子30が接続される。

【0021】

以上、第2実施例で説明したように、立ち下がり波形の出力時用に容量値を設定したNウェル容量素子からなる位相補償容量素子30と立ち上がり波形の出力時用に容量値を設定したNウェル容量素子からなる位相補償容量素子40とを切替えスイッチ80,90を介してNウェル容量素子のゲート側端子とウェル側端子とを逆並列に接続している。そして、各データ線に対応した演算増幅器20に、立ち上がり波形の出力時に位相補償容量素子40を接続するとともに、立ち下がり波形の出力時に位相補償容量素子30を接続するようにしている。その結果、立ち上がり波形および立ち下がり波形のそれぞれの出力時に適合したNウェルの容量値を設定でき、容量値が小さ過ぎることにより演算増幅器が発振することや、逆に必要以上に大き過ぎてスルレートが小さくなるという不都合を防止できる。

【0022】

【発明の効果】

本発明に係わる液晶表示装置の駆動回路によれば、演算増幅器に接続されるNウェル容量素子からなる位相補償容量素子を、容量値の相異なる2個1組の位相補償容量素子で構成し、演算増幅器が立ち下がり波形を出力するとき、2個1組の位相補償容量素子のうち容量値が大きい位相補償容量素子を接続するとともに、演算増幅器が立ち上がり波形を出力するとき、2個1組の位相補償容量素子のうち容量値が小さい位相補償容量素子を、容量値が大きい位相補償容量素子に対しNウェル容量素子の端子を逆方向にして接続するので、容量値が小さ過ぎることにより演算増幅器が発振することや、逆に必要以上に大き過ぎてスルレートが小さくなるという不都合を防止できる。さらに、立ち上がり波形と立ち下がり波形を奇数データ線と偶数データ線とで互い違いに出力する2個1組の演算増幅器に2個1組の位相補償容量素子が互い違いに接続される液晶表示装置の駆動回路では、チップ面積を小さくすることができる。

【図面の簡単な説明】

【図1】本発明の第1実施例であるデータ側ドライバの要部回路図。

【図2】本発明の第2実施例であるデータ側ドライバの要部回路図。

【図3】液晶表示装置の概略構成図。

【図4】従来のデータ側ドライバの要部回路図。

【図5】図4のデータ側ドライバの回路動作を示すタイミング図。

【図6】Nウェル容量素子の概略断面を示す図。

【図7】図6のNウェル容量素子のバイアス電圧依存特性を示す図。

【図8】図1、2および図5のデータ側ドライバに用いられる演算増幅器の一例の回路図。

【図9】図8に示す演算増幅器のNウェル容量素子の接続点における電位の変化を示す図。

【符号の説明】

200、300 データ側ドライバ

10、70 前段回路部

20 演算増幅器

30、40 位相補償容量素子

50、60、80、90 切替えスイッチ[0001]

TECHNICAL FIELD OF THE INVENTION

The present invention relates to a drive circuit for a liquid crystal display device, and more particularly to a drive circuit for a liquid crystal display device in which a phase compensation capacitor connected to an operational amplifier is an N-well capacitor.

[0002]

[Prior art]

As shown in FIG. 3, a liquid crystal display module of an active matrix type liquid crystal display device includes a liquid crystal panel (LCD panel) 1 and a control circuit (hereinafter, referred to as a controller) 2 composed of a semiconductor integrated circuit device (hereinafter, referred to as an IC). And a plurality of scan-side drive circuits (hereinafter, referred to as scan-side drivers) 3 and data-side drive circuits (hereinafter, referred to as data-side drivers) 4 comprising ICs. Although not shown in detail, the

[0003]

The

{Circle around (1)} The scanning driver 3 needs to drive 768 gate lines. For example, if it has a driving capability of 192 gates, it requires four, and is arranged on one side of the

{Circle around (2)} The data side driver 4 needs three data lines for R (red), G (green), and B (blue) in order to display one pixel in color, so that 1024 × 3 = 3072 lines It is necessary to drive the data lines. For example, in the case of having a driving capability for 384 lines, eight lines are required, and one side is arranged in a cascade connection on the upper outer periphery of the

Although not shown, a power supply circuit for supplying the common voltage Vcom is connected to the counter substrate electrode.

[0004]

Image data is sent from the PC 5 to the

[0005]

When each pixel electrode is driven by the data-side driver 4, it is necessary to perform AC driving with respect to the potential of the counter substrate electrode due to the characteristics unique to the liquid crystal. As a typical AC driving method, the gray scale voltage from the data driver 4 is applied to the common voltage Vcom by a positive voltage and a negative voltage for one scan period (hereinafter, referred to as one horizontal period) for one scan line. There are a line inversion driving method for switching on a line basis and a dot inversion driving method for switching on a pixel electrode basis. The line inversion driving method is a method in which the grayscale voltage from the data side driver 4 is set to a low voltage of, for example, +5 V or less, and the polarity is inverted by changing the common voltage Vcom every one horizontal period to perform AC driving. is there. On the other hand, in the dot inversion driving method, the common voltage Vcom is fixed to a constant voltage, and a voltage having a positive polarity (hereinafter referred to as a positive gradation) is applied to the common voltage Vcom as a gradation voltage from the data driver 4. Voltage and a voltage having a negative polarity (hereinafter referred to as a negative gradation voltage) are set so as to be symmetrical, and the positive gradation voltage and the negative gradation voltage are alternately changed every one horizontal period. It is a method of supplying. For example, in the case of a 64-gradation display, Vcom <VP64 <... <VP1 as the positive gradation voltages VP1 to VP64, and Vcom>VN64> ... VN1 as the negative gradation voltages VN1 to VN64, and the positive gradation voltage VP1 to VP64 and the negative gradation voltages VN1 to VN64 are set symmetrically with respect to the common voltage Vcom. Then, one gray scale voltage VPx of the positive gray scale voltages VP1 to VP64 and one gray scale voltage VNx of the negative gray scale voltages VN1 to VN64 are alternately supplied every one horizontal period. .

[0006]

In the following, as a conventional example of the data-side driver 4, the data-

[0007]

Next, the operation when the

[0008]

In the next one horizontal period, the polarity control signal POL is supplied at a “low” level to the preceding-

[0009]

[Problems to be solved by the invention]

By the way, as described above, the phase

[0010]

On the other hand, the

[0011]

When the N-well capacitance element is used as the phase compensation capacitance element as described above, when the capacitance value of the phase compensation capacitance element is determined in accordance with the capacitance value required at the time of output of the falling waveform, when the rising waveform is output May be smaller than the required capacitance value. In the worst case, the

[0012]

SUMMARY OF THE INVENTION Accordingly, the present invention has been made to solve the above-mentioned problems, and it is desirable to change the capacitance value of a phase compensation capacitance element composed of an N-well capacitance element connected to an operational amplifier when a rising waveform is output and when a falling waveform is output. It is an object of the present invention to provide a driving circuit of a liquid crystal display device which can provide a necessary and appropriate capacitance value at each time.

[0013]

[Means for Solving the Problems]

(1) A driving circuit for a liquid crystal display device according to the present invention includes a liquid crystal display device including an operational amplifier connected to a data line of a liquid crystal panel, and a phase compensation capacitive element including an N-well capacitive element connected to the operational amplifier. The driving circuit of the above has two sets of phase compensation capacitance elements having different capacitance values, and when the operational amplifier outputs a falling waveform, the phase of the two phase compensation capacitance elements having the larger capacitance value is output. When the compensating capacitive element is connected and the operational amplifier outputs a rising waveform, the phase compensating capacitive element having a small capacitance value of the pair of phase compensating capacitive elements corresponds to the phase compensating capacitive element having a large capacitive value. It is characterized in that the terminals of the N-well capacitance element are connected in the opposite direction.

(2) In the driving circuit for a liquid crystal display device according to the present invention, in the above item (1), the operational amplifier outputs a rising waveform and a falling waveform alternately.

(3) The driving circuit for a liquid crystal display device according to the above item (2), wherein the set of two operational amplifiers that alternately output a rising waveform and a falling waveform between an odd data line and an even data line are provided. A pair of phase compensation capacitive elements are connected alternately.

(4) The driving circuit for a liquid crystal display device according to the above item (2), wherein in the operational amplifier corresponding to one data line for outputting a rising waveform and a falling waveform, one pair of the two operational amplifiers is provided. The phase compensation capacitance element is connected alternately.

[0014]

BEST MODE FOR CARRYING OUT THE INVENTION

Hereinafter, the

The data-

[0015]

Next, an operation when the

[0016]

In the next one horizontal period, the polarity control signal POL is supplied at a “low” level to the preceding-

[0017]

As described above, as described in the first embodiment, the phase

[0018]

Next, the data-

[0019]

Next, the operation when the

[0020]

In the next one horizontal period, the polarity control signal POL is supplied at the “low” level to the preceding-

[0021]

As described above, as described in the second embodiment, the phase

[0022]

【The invention's effect】

According to the drive circuit of the liquid crystal display device according to the present invention, the phase compensation capacitance element composed of the N-well capacitance element connected to the operational amplifier is constituted by a pair of phase compensation capacitance elements having different capacitance values, When the operational amplifier outputs a falling waveform, a phase compensating capacitive element having a larger capacitance value is connected among the pair of phase compensating capacitive elements, and when the operational amplifier outputs a rising waveform, a pair of phase compensating capacitive elements is output. Since the phase compensation capacitance element having a small capacitance value among the phase compensation capacitance elements is connected to the phase compensation capacitance element having a large capacitance value with the terminal of the N-well capacitance element being in the opposite direction, the operational amplifier may be connected because the capacitance value is too small. Can be prevented from oscillating, and conversely, the inconvenience that the sullate is too small to be too large can be prevented. Further, a drive of a liquid crystal display device in which a pair of phase compensation capacitive elements are alternately connected to a pair of operational amplifiers that alternately output a rising waveform and a falling waveform between an odd data line and an even data line. In the circuit, the chip area can be reduced.

[Brief description of the drawings]

FIG. 1 is a main part circuit diagram of a data side driver according to a first embodiment of the present invention.

FIG. 2 is a main part circuit diagram of a data side driver according to a second embodiment of the present invention.

FIG. 3 is a schematic configuration diagram of a liquid crystal display device.

FIG. 4 is a main part circuit diagram of a conventional data side driver.

FIG. 5 is a timing chart showing a circuit operation of the data side driver of FIG. 4;

FIG. 6 is a diagram showing a schematic cross section of an N-well capacitance element.

FIG. 7 is a view showing a bias voltage dependence characteristic of the N-well capacitance element shown in FIG. 6;

FIG. 8 is a circuit diagram of an example of an operational amplifier used in the data side driver of FIGS. 1, 2 and 5;

9 is a diagram showing a change in potential at a connection point of an N-well capacitance element of the operational amplifier shown in FIG. 8;

[Explanation of symbols]

200, 300

Claims (4)

容量値の相異なる2個1組の前記位相補償容量素子を有し、

前記演算増幅器が立ち下がり波形を出力するとき、前記2個1組の位相補償容量素子のうち容量値が大きい位相補償容量素子が接続されるとともに、前記演算増幅器が立ち上がり波形を出力するとき、前記2個1組の位相補償容量素子のうち容量値が小さい位相補償容量素子が、前記容量値が大きい位相補償容量素子に対しNウェル容量素子の端子を逆方向にして接続されることを特徴とする液晶表示装置の駆動回路。In a drive circuit of a liquid crystal display device including an operational amplifier connected to a data line of a liquid crystal panel, and a phase compensation capacitive element including an N-well capacitive element connected to the operational amplifier,

A pair of phase compensation capacitance elements having different capacitance values,

When the operational amplifier outputs a falling waveform, a phase compensating capacitive element having a large capacitance value among the pair of phase compensating capacitive elements is connected, and when the operational amplifier outputs a rising waveform, A phase compensating capacitance element having a small capacitance value among a pair of phase compensating capacitance elements is connected to the phase compensating capacitance element having a large capacitance value with the terminal of the N-well capacitance element in a reverse direction. Circuit for driving a liquid crystal display device.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002222236A JP2004061985A (en) | 2002-07-31 | 2002-07-31 | Drive circuit for liquid crystal display |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002222236A JP2004061985A (en) | 2002-07-31 | 2002-07-31 | Drive circuit for liquid crystal display |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2004061985A true JP2004061985A (en) | 2004-02-26 |

Family

ID=31942302

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002222236A Pending JP2004061985A (en) | 2002-07-31 | 2002-07-31 | Drive circuit for liquid crystal display |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2004061985A (en) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009278518A (en) * | 2008-05-16 | 2009-11-26 | Oki Semiconductor Co Ltd | Driving device |

| JP2010134110A (en) * | 2008-12-03 | 2010-06-17 | Seiko Epson Corp | Reference voltage generating circuit, integrated circuit device, electrooptical device, and electronic device |

-

2002

- 2002-07-31 JP JP2002222236A patent/JP2004061985A/en active Pending

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009278518A (en) * | 2008-05-16 | 2009-11-26 | Oki Semiconductor Co Ltd | Driving device |

| JP2010134110A (en) * | 2008-12-03 | 2010-06-17 | Seiko Epson Corp | Reference voltage generating circuit, integrated circuit device, electrooptical device, and electronic device |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7002568B2 (en) | Signal drive circuit, display device, electro-optical device, and signal drive method | |

| US7030869B2 (en) | Signal drive circuit, display device, electro-optical device, and signal drive method | |

| US7079103B2 (en) | Scan-driving circuit, display device, electro-optical device, and scan-driving method | |

| US7696970B2 (en) | Driving circuit, display device, and driving method for the display device | |

| JP2004309669A (en) | Active matrix type display device and its driving method | |

| US6433768B1 (en) | Liquid crystal display device having a gray-scale voltage producing circuit | |

| KR20090002994A (en) | Driving apparatus and method for display device and display device including the same | |

| KR100659621B1 (en) | Active matrix type liquid crystal display device | |

| US20080062027A1 (en) | Source driving circuit and liquid crystal display apparatus including the same | |

| JP4810840B2 (en) | Reference voltage generation circuit, display driver, electro-optical device, and electronic apparatus | |

| JP3726910B2 (en) | Display driver and electro-optical device | |

| JP2006227272A (en) | Reference voltage generation circuit, display driver, electrooptical apparatus and electronic equipment | |

| KR20070070928A (en) | Driving apparatus and liquid crystal display comprising the same | |

| JP2001343944A (en) | Driving method and driving device for liquid crystal display device | |

| JP4442455B2 (en) | Reference voltage selection circuit, reference voltage generation circuit, display driver, electro-optical device, and electronic apparatus | |

| JP2006243232A (en) | Reference voltage generation circuit, display driver, electro-optic device and electronic device | |

| JP2001272655A (en) | Method and device for driving liquid crystal device | |

| US7898516B2 (en) | Liquid crystal display device and mobile terminal | |

| JP2004061985A (en) | Drive circuit for liquid crystal display | |

| JP3443059B2 (en) | Afterimage erasing method and display device using the afterimage erasing method | |

| JP2004029409A (en) | Liquid crystal display device and its drive circuit | |

| JP2004029316A (en) | Liquid crystal display device and its drive circuit | |

| JP2006243233A (en) | Reference voltage generation circuit, display driver, electro-optic device and electronic device | |

| JP2007219091A (en) | Driving circuit, electrooptical device, and electronic equipment | |

| KR101298402B1 (en) | Liquid Crystal Panel and Liquid Crystal Display Device having the same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20050119 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20050511 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050615 |

|

| RD01 | Notification of change of attorney |

Effective date: 20070703 Free format text: JAPANESE INTERMEDIATE CODE: A7421 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080805 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20090113 |