CN1221027C - Semiconductor package with heat sink structure - Google Patents

Semiconductor package with heat sink structure Download PDFInfo

- Publication number

- CN1221027C CN1221027C CN 01116163 CN01116163A CN1221027C CN 1221027 C CN1221027 C CN 1221027C CN 01116163 CN01116163 CN 01116163 CN 01116163 A CN01116163 A CN 01116163A CN 1221027 C CN1221027 C CN 1221027C

- Authority

- CN

- China

- Prior art keywords

- semiconductor package

- package part

- radiator structure

- chip

- substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32245—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73253—Bump and layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

Landscapes

- Cooling Or The Like Of Semiconductors Or Solid State Devices (AREA)

Abstract

The present invention relates to a semiconductor package member with a heat radiation structure, which comprises a chip bearing member, wherein a plurality of welding pad are arranged on the surface for a chip to be connected, and thus, a heat radiation member is connected by a plurality of soft metal supporting blocks so that the heat radiation member is supported on the chip by the supporting blocks. The heat radiation member is formed with a plurality of positioning parts in the positions connected with the supporting blocks; thus, the heat radiation member is stably positioned without the worry of offset after being connected to the chip bearing member. Then, the heat radiation structure formed from the heat radiation member and the supporting blocks is welded back to the chip bearing member together with the semiconductor chip; the top surface of the heat radiation member is exposed to the package member for increasing heat radiation efficiency.

Description

Technical field

The invention relates to a kind of semiconductor package part, refer to a kind of flip chip type ball grid array (Flip Chip Ball Grid Array, FCBGA) semiconductor package part especially with embedded heat sink with the lifting radiating efficiency.

Background technology

Ball grid array (BGA) semiconductor package part (Ball Grid Array SemiconductorPackage) have the input of comparatively high amts/go out link (I/O Connection) be able in response to the semiconductor chip institute of high density electronic building brick (Electronic Components) and electronic circuit (ElectronicCircuits) must, become for the demand of electrical functionality and processing speed and encapsulate main flow today to meet electronic product.Yet along with electronic circuit on the semiconductor chip and electronic building brick layout density increase day by day, the heat that produces during the chip running just the more; If, will influence the performance and the useful life of semiconductor chip not with the effective loss of heat energy of semiconductor chip generation.Other is the person, the high performance chips of BGA semiconductor package part is coated by packing colloid (Encapsulant) traditionally, the potting resin that only constitutes this packing colloid is the bad thermal conductor that a conductive coefficient only is about 0.8w/m ° of K, so the action face (Active Surface) that makes semiconductor chip be laid with electronic circuit and electronic building brick is difficult to efficiently radiates heat; How effectively to get rid of heat that semiconductor chip produces and satisfy into the big problem that industry institute must solution.

United States Patent (USP) the 5th, 726, No. 079 case promptly discloses a kind of flip chip type ball grid array (Flip ChipBall Grid Array, FCBGA) encapsulating structure (shown in the 1st figure), it is placed in semiconductor chip 12 tops with a heat sink 11, by heat sink 11 surfaces that expose to packaging part 1 heat that chip 12 produces is spilt in the atmosphere fast.If yet that the disappearance of this technology is that heat sink 11 is provided with the position is too high, clamping pressure was urged to this heat sink 11 when molding operation was implemented, and then the chip 12 that is urged to heat sink 11 belows causes chip 12 impaired; If heat sink 11 is provided with the position too near chip 12, the upper surface 110 that then easily makes heat sink 11 expose produces excessive glue and its heat sinking benefit and cause product appearance bad of detracting in the colloid encapsulation procedure.Therefore carry out this technology and need ask high operation precision side to make this heat sink 11 correctly to be placed in predetermined altitude, this measure will promote the processing procedure degree of difficulty and not meet cost benefit.

In addition, United States Patent (USP) the 5th, 977, No. 626 case also discloses a kind of semiconductor package 1 with special shape heat sink 11.Shown in the 2nd figure, this kind semiconductor package 1 comprises that a heat sink 11 gluings to are equipped with on the substrate 14 of semiconductor chip 12; Wherein this heat sink 11 has a par 111 and in order to this par 111 is supported in the support portion 112 of chip top, insert for this chip 12 and gold thread 13 in order to do making this par 111 form an accommodation space with support portion 112, simultaneously, this support portion 112 is formed with a plurality of salient points 113, makes this heat sink 11 get these salient points 113 stable connecing of mat and places on this substrate 14.

Though be that kind of encapsulating structure 1 can promote chip cooling efficient by heat sink 11 designs of special shape, this packaging body still has aforementioned patent (United States Patent (USP) the 5th, 726, No. 079) and is difficult for the appropriate problem of settling heat sink 11 positions of cutting.In addition, must use punching press processing procedure (Stamping) in order to do to form reclinate support portion 112 when making the heat sink 11 of this special shape, except that increasing packaging cost, after punching press the flatness (Planarity) of these heat sink 11 pars 111 often be affected and cause potting resin overflow glue in the par 111 upper surface 110 (being the exposed surface 110 of heat sink 11); Especially now semiconductor package part power is towards thinning trend exploitation, even that used heat sink 11 thickness often are as thin as 0.2mm is thinner, the flatness that will make this par 111 is more difficult to be kept heat sink 11 structural strengths because of thinning reduces, and the glue phenomenon of overflowing can't be avoided then.

Summary of the invention

Purpose of the present invention is promptly at the semiconductor package part that the embedded radiator structure of a kind of tool is provided, this radiator structure is provided with a plurality of matter soft metal back-up block and uses the compressing power that and even molding die produces for the heat sink chip in the matched moulds operation of sharing equally that allays, in order to do to avoid semiconductor chip impaired and heat sink is accurately located and steadily adhere on above the chip, except that the good flatness (Planarity) of keeping this heat sink, and must make the unlikely excessive glue of the exposed surface that makes radiator structure so promote the integral heat sink efficient of packaging part.

Another object of the present invention is promptly planted the size that connects welding pad opening so that control the spacing of this radiator structure and substrate by adjusting on the substrate providing a kind of, in order to do the semiconductor package part with the embedded radiator structure of tool of reduction packaging cost and process complexity.

In view of on take off and other purpose, the semiconductor package part of the embedded radiator structure of tool of the present invention comprises: a substrate, it has a positive and opposing backside surface, connects respectively to establish a bond pads weld pad and one group and plant ball pad on this substrate front side, and lays a plurality of conductive welding pad at this substrate back; The semiconductor chip has an action face that is equipped with electronic circuit and electronic building brick, plants on it to be connected to a plurality of soldering projections in order to do being connected with substrate conducting for this chip; One radiator structure, its mat one heat sink and a plurality of matter soft metal back-up block institute constitutor, wherein this heat sink lower surface offers a plurality of location divisions and establishes for these back-up blocks are glutinous; A plurality of soldered balls are planted to place on those conductive welding pad in order to do carrying out electrical lotus root for this chip and external device (ED) and are connect; And one in order to coating this semiconductor chip, radiator structure and part substrate, and order packing colloid that this heat sink upper surface is exposed.

Location division on this heat sink must be for being formed at the depression on this lower surface or being through to the through hole of lower surface by this heat sink upper surface, treat that these matter soft metal back-up blocks are (promptly by tin, plumbous, soft metal such as lead/ashbury metal and similar alloy material makes) glutinous put in order to do to constitute a radiator structure with the soldering projection reflow simultaneously of this chip when substrate is implemented molding operation, this heat sink is slightly larger than the die cavity end face of the encapsulating mould that forms packing colloid and the spacing of substrate apart from the height of substrate front side, the matched moulds compressing power that mould provided when matched moulds was carried out must allay and reduce via these matter soft metals back-up block crumple (Collapse), and share out equally on heat sink in order to do to avoid chip impaired to reduce pressure that semiconductor chip bears, can make entirely attached this chip top that is against of this heat sink use the excellent planar of keeping heat sink again.

On the other hand, offering of these location divisions has the pressure buffer space when a space is provided in order to do the back-up block crumple of sharp matter soft metal, the anxiety of not having off normal by these back-up block reflows also make to the solder pad of substrate this heat sink precisely inerrably be positioned on the substrate, the die cavity end face of this heat sink end face and upper mould is able to fluid-tight engagement can prevent from then the to overflow generation of glue phenomenon when then carrying out the mold pressing processing procedure.

Description of drawings

Below cooperate appended graphic characteristics of the present invention and the effect of being described in further detail with preferred embodiment:

The 1st figure is a United States Patent (USP) the 5th, 726, the cutaway view of the semiconductor package part of No. 079 case;

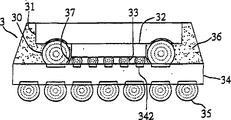

The 2nd figure is a United States Patent (USP) the 5th, 977, the cutaway view of the semiconductor package part of No. 626 cases;

The 3rd figure is the cutaway view of the semiconductor package part of first embodiment of the invention;

4A to 4D figure is the detailed processing procedure figure of semiconductor package part first embodiment of the present invention;

The 5th figure is the comparison cutaway view that semiconductor package part of the present invention is implemented mold pressing processing procedure front and back;

The 6th figure is the cutaway view of the semiconductor package part of second embodiment of the invention; And,

The 7th figure is the cutaway view of the semiconductor package part of third embodiment of the invention.

The symbolic label explanation

1,2,3 semiconductor package parts, 20,30 tin balls

11,21,31 embedded fin 110,210 heatsink upper surface

211,311 fin lower surfaces, 212 depressions

312 through holes, 213,313 gluing layers

112 support portions, 111 pars

113 salient points, 12,22,32 semiconductor chips

220 action face, 221 non-action face

13 gold threads, 23,33 soldering projections

14,24,34 substrates, 240 substrate front side

241 substrate backs, 242,342 solder pad

243 plant ball pad 243a plants the ball pad opening

244 conductive welding pad, 245 chip connecting areas

15,25,35 soldered balls, 16,26,36 packing colloids

17,37 bottom fillers, 28 molding dies

280 die cavity end faces, 29 radiator structures

Embodiment

Below promptly cooperate each embodiment of appended graphic detailed description flip chip type ball grid array of the present invention (FCBGA) semiconductor package part.

First embodiment:

The 3rd figure is the embedded heat sink FCBGA of the tool of a first embodiment of the invention semiconductor package part 2, this encapsulating structure is to provide a plurality of weld pads 242 by a surface, 243,244 connect the substrate of putting 24, the semiconductor chip 22 of one tool, one action face 220, one glutinous embedded fin 21 (the Embedded Heat Sink that is equipped with a plurality of first soldered balls 20, EDHS), a plurality of soldering projections 23 that are connected to these chip 22 action face 220 of planting, a plurality of planting on this substrate 24 in order to do second soldered ball 25 for semiconductor chip 12 and external device (ED) (not icon) electrically connect, and one in order to coating this chip 22 and fin 21, and 26 constitutors of packing colloid that these fin 21 upper surfaces 210 are exposed.

4A to 4D figure is the detailed making flow process of the embedded heat sink FCBGA of the tool semiconductor package part 2 of first embodiment of the invention, below promptly with regard to this packaging part its each processing procedure is described.

Put a substrate 24 earlier, shown in 4A figure, this substrate 24 has positive 240 and one opposing backside surface 241; Wherein, be formed with a bond pads weld pad 242 (Bonding Pads) and plant ball pad 243 (Ball Pads) with one group on these substrate 24 fronts 240, substrate then is provided with a plurality of conductive welding pad 244 on 24 back sides 241 in addition.Being preset with a chip connecting area 245 on substrate 24 fronts 240 provides these solder pad 242 to form to connect and put in order to do the soldering projection (not icon) with semiconductor chip (not icon), these solder pad 242 respectively by a plurality of conductive traces (not icon) pass through conductive through hole (not icon) electrically connect to a plurality of conductive welding pad 244 at these substrate 24 back sides 241; In addition in the appropriate location of these chip connecting area 245 peripheries on the substrate 24 form a plurality of plant ball pad 243 in case with this heat sink (not icon) on first soldered ball (not icon) welding, simultaneously, this plants ball pad 243 also must have grounding function (Grounding), decapacitation promotes outside the integral heat sink efficient of semiconductor package part 2, can improve again that it is electrical.Use on this formation of planting ball pad 243 and the existing BGA substrate that to plant the conductive welding pad 244 that connects on it for soldered ball (not icon) identical, satisfy and give unnecessary details for literary composition in addition.

This semiconductor chip 22 has an action face 220 and a relative non-action face 221, sees also 4B figure.Be laid with a plurality of electronic circuits and electronic building brick (not icon) on this action face 220, and a plurality of I/O weld pads (not icon) connect in order to do a plurality of soldering projections 23 (SolderBump) being connect put and must carry out electrical lotus root with substrate 24 (shown in 4A figure), these soldering projections 23 are planted through bottom metalization processing procedure modes such as (Under Bump Metallization) and are connect, and these cover brilliant formation method knows not inking in addition of the known event of genus.

Moreover, the embedded fin 21 that is equipped with metal materials such as a bronze medal, aluminium in addition, shown in 4C figure, this fin 21 has a upper surface 210 and an opposing lower surface 211, offers a plurality of depressions 212 in these fin 21 lower surfaces 211 appropriate locations in order to do for being coated with on it just like epoxy resin (Epoxy) the gluing layer of etc.ing 213 by existing half erosion (Half Etching) or punching out (Stamping) technology (all for existing so will not give unnecessary details); Then, with a plurality of first soldered balls 20 insert one by one cause in these depressions that are covered with gluing layer 213 212 this first soldered ball 20 firmly connect and place on this fin 21 constituting a radiator structure 29, and the vertical height H of this first soldered ball 20 must be more than or equal to semiconductor chip 22 thickness and soldering projection 23 summation highly.This first soldered ball 20 is outside material is made divided by tin, and other soft metals such as lead, tin/lead alloy and similar alloy also are suitable for it.

This semiconductor chip 22 and embedded fin 21 are used soldering projection 23 and these first soldered ball, 20 reflows simultaneously (Solder Reflow) respectively to substrate 24 corresponding pad 242, on 243, shown in 4D figure, when planting ball, can plant the anxiety of exempting off normal on the ball pad 243 because of its automatic contraposition (Self-Alignment) is precisely planted first soldered ball 20 and is connected to the reflow operation; And, plant the size that ball pad 243 opening 243a offer by substrate 24 surfaces, (it is bigger to plant ball pad 243 opening 243a to be able to adjust more expediently the height of embedded fin 21 in packaging part 2, then first soldered ball, 20 pressurizeds and sink deeplyer cause the height of this fin 21 in packaging part 2 less and comparatively press close to chip 22; Vice versa).First soldered ball, 20 reflows simultaneously on semiconductor chip 22, soldering projection 23 and the fin 21 can impose the mold pressing processing procedure behind substrate.

This packing colloid 26 is to form with materials such as existing epoxy resin, in order to do to coat this semiconductor chip 22, soldering projection 23 and radiator structure 29.Shown in the 5th figure, for the radiating efficiency that makes this semiconductor package part 2 is able to effective lifting, the upper surface 210 of this fin 21 exposes outside this packing colloid 26 directly to contact with atmosphere.Because this first soldered ball, 20 tools, one matter software feature, and the gluing layer 213 of being separated by between first soldered ball 20 and the fin 21 also is the buffer medium of an absorption pressure, so make this radiator structure 29 be slightly larger than in order to the die cavity end face 280 of the encapsulating mould 28 that forms packing colloid 26 and the spacing in these substrate 24 fronts 240 apart from the height H 1 in substrate 24 fronts 240, when then carrying out the matched moulds operation, the die cavity end face 280 of this encapsulating mould 28 promptly can provide one to be out of shape sagging to lower compression power in order to do making first soldered ball, 20 pressurizeds that join with this fin 21, the upper surface 210 of this fin 21 connects airtight in die cavity end face 280 causes unlikely formation gap between the two, so the generation of the glue phenomenon of avoiding overflowing and must guarantee the outward appearance and the thermal diffusivity of packaged article; Other is the person, because of this first soldered ball 20 and the glutinous gluing layer of putting on it 213 have the characteristic that absorbs deflection, and even effectively allayed and reduced encapsulating mould 28, rhegma is taken place in mold process so can prevent semiconductor chip 22 for the compressing power that fin 21 chips 22 produce.

Second embodiment:

The 6th figure those shown is the semiconductor package part cutaway view of second embodiment of the invention, those disclosed herein are roughly the same among the semiconductor package part 3 of this second embodiment and first embodiment, and its difference is in offers a plurality of through holes 312 in order to do to replace depression as connecing the location hole of putting tin ball 30 on this fin 31.By existing punching technology a plurality of through holes 312 of the pre-subdrilling system in appropriate location on this fin 31, multiple through hole 312 openings coating adhesive 313 in fin 31 lower surfaces 311 is with gluing tin ball 30 and carry out follow-up packaging operation, wait when carrying out the matched moulds operation, because molding die (not icon) is bestowed the compressing power of fin 31 and is forced first soldered ball, 30 compressive deformations, these through holes 312 were formed a cushion space and were beneficial to compressing power and allay this moment, make the pressure that is passed to chip reduce, then more help to keep the structural intergrity of semiconductor chip 32.

The 3rd embodiment:

The 7th figure is the semiconductor package part cutaway view of third embodiment of the invention, the semiconductor package part of the 3rd embodiment and aforementioned two embodiment are roughly the same, its difference be in this embodiment be the soldering projection 33 of keeping chip 32 with substrate 34 on the welding quality of solder pad 342, then after finishing, the reflow operation imposes colloid bottom filling (Underfill) (shown in Figure 37) again as the 7th, solder joint is unlikely frailly suffers the compressing power that molding die (not icon) bestows and destroy for 342 of soldering projection 33 and solder pad when then carrying out the mold pressing processing procedure, can guarantee to cover the quality reliability of brilliant welding then.

The above is preferred embodiment of the present invention only, is not in order to limit essence technology contents scope of the present invention.Essence technology contents of the present invention broadly is defined in the claim scope of the present invention, any technology entity or method that other people are finished, if with the claim scope definien of institute of the present invention be identical, also or be a kind of equivalent change, all treat as and be covered by in this claim.

Claims (18)

1. semiconductor package part with radiator structure, it is characterized in that: described semiconductor package part comprises:

One substrate, it has a positive and opposing backside surface, respectively is laid with one group of first weld pad and second weld pad in this substrate front side, and connects in this substrate back and to be equipped with the 3rd a plurality of weld pads;

The semiconductor chip has an action face and connects for a plurality of soldering projections and put on it so that this chip and this substrate first weld pad are electrically conducted;

One radiator structure, it has a heat sink and a plurality of matter soft metal back-up block, wherein this heat sink has a upper surface and an opposing lower surface, and puts and being arranged on this substrate second weld pad of mat for these back-up blocks are glutinous in offering a plurality of location divisions on this lower surface;

A plurality of conductive components in order to be connected to mutually on substrate the 3rd weld pad, connect for this chip and the electrical lotus root of external device; And

One packing colloid is in order to coat this semiconductor chip and radiator structure and the upper surface of this heat sink is exposed.

2. the semiconductor package part with radiator structure as claimed in claim 1 is characterized in that: this semiconductor package part is flip chip type ball grid array (FCBGA) semiconductor package part.

3. the semiconductor package part with radiator structure as claimed in claim 1 is characterized in that: this first weld pad is a solder pad.

4. the semiconductor package part with radiator structure as claimed in claim 1 is characterized in that: this second weld pad is for planting ball pad.

5. the semiconductor package part with radiator structure as claimed in claim 1 is characterized in that: the size of offering of this second welding pad opening depends on that this radiator structure is apart from the height of this substrate front side and adjust it.

6. the semiconductor package part with radiator structure as claimed in claim 1 is characterized in that: the 3rd weld pad is a conductive welding pad.

7. the semiconductor package part with radiator structure as claimed in claim 1 is characterized in that: this action face is the chip surface that is equipped with a plurality of electronic circuits and electronic building brick.

8. the semiconductor package part with radiator structure as claimed in claim 1 is characterized in that: the soldering projection between this chip and substrate must impose colloid bottom filling (Underfill) in order to the soldering projection between coating chip and substrate.

9. the semiconductor package part with radiator structure as claimed in claim 1 is characterized in that: this heat sink is the embedded fin of a metal material.

10. the semiconductor package part with radiator structure as claimed in claim 1 is characterized in that: the material of this back-up block is selected from one of them of tin, lead, tin/lead alloy cohort.

11. the semiconductor package part with radiator structure as claimed in claim 1 is characterized in that: this back-up block is selected from welding rod (Solder Column), one of them of soldered ball (Solder Balls) cohort.

12. the semiconductor package part with radiator structure as claimed in claim 1 is characterized in that: the vertical height of this back-up block is more than or equal to the summation of this semiconductor chip thickness and this soldering bump height.

13. the semiconductor package part with radiator structure as claimed in claim 1 is characterized in that: this back-up block is used a gluing layer gluing on the location division of this heat sink.

14. the semiconductor package part with radiator structure as claimed in claim 13 is characterized in that: this gluing layer is constituted by the elastic material of an epoxy resin.

15. the semiconductor package part with radiator structure as claimed in claim 1 is characterized in that: this location division is the depression that is formed on this heat sink lower surface.

16. the semiconductor package part with radiator structure as claimed in claim 1 is characterized in that: this location division is a plurality of through holes that are opened on this heat sink.

17. the semiconductor package part with radiator structure as claimed in claim 1 is characterized in that: this soldering projection and these back-up blocks are used the reflow mode simultaneously and are planted and be connected on the set many assembly weldings pad of this substrate.

18. the semiconductor package part with radiator structure as claimed in claim 1 is characterized in that: this conductive component is a soldered ball.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN 01116163 CN1221027C (en) | 2001-05-21 | 2001-05-21 | Semiconductor package with heat sink structure |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN 01116163 CN1221027C (en) | 2001-05-21 | 2001-05-21 | Semiconductor package with heat sink structure |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1387252A CN1387252A (en) | 2002-12-25 |

| CN1221027C true CN1221027C (en) | 2005-09-28 |

Family

ID=4662428

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN 01116163 Expired - Fee Related CN1221027C (en) | 2001-05-21 | 2001-05-21 | Semiconductor package with heat sink structure |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN1221027C (en) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2009006761A1 (en) * | 2007-07-12 | 2009-01-15 | Princo Corp. | Multi-layer baseboard and manufacturing method thereof |

| US7656679B2 (en) | 2007-06-20 | 2010-02-02 | Princo Corp. | Multi-layer substrate and manufacture method thereof |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN100411218C (en) * | 2003-03-07 | 2008-08-13 | 铼宝科技股份有限公司 | Package process of organic electroluminescence panel |

| CN1319159C (en) * | 2003-03-26 | 2007-05-30 | 矽品精密工业股份有限公司 | Semiconductor package part with radiation fin |

| CN1316607C (en) * | 2003-06-10 | 2007-05-16 | 矽品精密工业股份有限公司 | Semiconductor package with high heat radiation performance and making method thereof |

| CN100416806C (en) * | 2003-08-20 | 2008-09-03 | 日月光半导体制造股份有限公司 | Packaging structure with projected zone carrying crystals, crystals carried substrate and crystals carried assembly |

| CN1319163C (en) * | 2003-08-29 | 2007-05-30 | 矽品精密工业股份有限公司 | Semiconductor package with radiating fins |

| TWI253154B (en) | 2005-05-06 | 2006-04-11 | Neobulb Technologies Inc | Integrated circuit packaging and method of making the same |

| CN100447989C (en) * | 2005-05-18 | 2008-12-31 | 新灯源科技有限公司 | Integrated circuit packaging and manufacturing method |

| KR100764682B1 (en) * | 2006-02-14 | 2007-10-08 | 인티그런트 테크놀로지즈(주) | Ic chip and package |

| CN101221929B (en) * | 2007-01-12 | 2010-05-19 | 日月光半导体制造股份有限公司 | Packaging structure and its radiating module |

| TWI451539B (en) | 2010-08-05 | 2014-09-01 | Advanced Semiconductor Eng | Semiconductor package and manufacturing method thereof |

| CN101937885B (en) * | 2010-08-12 | 2013-03-20 | 日月光半导体制造股份有限公司 | Semiconductor packaging piece and manufacture method thereof |

| CN102347290A (en) * | 2011-09-30 | 2012-02-08 | 常熟市广大电器有限公司 | Chip packaging structure with good heat dispersion property |

| TWI453881B (en) * | 2012-01-04 | 2014-09-21 | 矽品精密工業股份有限公司 | Package structure and method of forming same |

| US8674509B2 (en) * | 2012-05-31 | 2014-03-18 | Freescale Semiconductor, Inc. | Integrated circuit die assembly with heat spreader |

| CN106935516B (en) * | 2015-12-30 | 2019-05-03 | 欣兴电子股份有限公司 | The production method of the encapsulating structure of built-in type electronic building brick |

| CN116134613A (en) * | 2020-09-25 | 2023-05-16 | 华为技术有限公司 | Chip packaging structure, electronic equipment and preparation method of chip packaging structure |

| CN112437555B (en) * | 2020-11-25 | 2021-11-09 | 江苏汇成光电有限公司 | Mechanism capable of reducing jitter in Tape Bonding technological process |

-

2001

- 2001-05-21 CN CN 01116163 patent/CN1221027C/en not_active Expired - Fee Related

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7656679B2 (en) | 2007-06-20 | 2010-02-02 | Princo Corp. | Multi-layer substrate and manufacture method thereof |

| WO2009006761A1 (en) * | 2007-07-12 | 2009-01-15 | Princo Corp. | Multi-layer baseboard and manufacturing method thereof |

Also Published As

| Publication number | Publication date |

|---|---|

| CN1387252A (en) | 2002-12-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1221027C (en) | Semiconductor package with heat sink structure | |

| US11705413B2 (en) | Semiconductor package having improved thermal interface between semiconductor die and heat spreading structure | |

| US8546183B2 (en) | Method for fabricating heat dissipating semiconductor package | |

| CN1543675A (en) | Microelectronic package having a bumpless laminated interconnection layer | |

| TWI242869B (en) | High density substrate for multi-chip package | |

| CN101887885B (en) | Stacking structure of semiconductor packages | |

| US20150014031A1 (en) | Compound carrier board structure of flip-chip chip-scale package and manufacturing method thereof | |

| CN1174484C (en) | Semiconductor package with radiating structure | |

| CN116093046A (en) | Preparation method of single chip and chip structure | |

| TW200423337A (en) | Chip package structure | |

| CN1855450A (en) | High-heat loss rate semiconductor sealer and its production | |

| US6770513B1 (en) | Thermally enhanced flip chip packaging arrangement | |

| TW200423342A (en) | Chip package structure and process for fabricating the same | |

| CN116093044B (en) | Multi-chip integration method and structure | |

| CN1172369C (en) | Semiconductor package with heat radiator | |

| CN100362639C (en) | Semiconductor packer and production for godown chip | |

| CN1153285C (en) | Semiconductor package with heat dissipating structure | |

| CN100446200C (en) | Heat radiation type packaging structure and its making method | |

| CN2662455Y (en) | Electric packaging body | |

| CN1779931A (en) | Radiating pack structure and production thereof | |

| TW200423349A (en) | Chip package structure | |

| TW200408088A (en) | Process for fabricating semiconductor package having heat spreader and the same thereof | |

| KR20050031599A (en) | Semiconductor package having thermal interface material | |

| WO2019127264A1 (en) | Three-dimensional chip stacking chip size packaging structure and manufacturing method therefor | |

| CN116487344A (en) | Three-dimensional packaging structure and packaging method |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20050928 |