CN113035732A - Three-dimensional memory and method for forming step area of three-dimensional memory - Google Patents

Three-dimensional memory and method for forming step area of three-dimensional memory Download PDFInfo

- Publication number

- CN113035732A CN113035732A CN202110209757.1A CN202110209757A CN113035732A CN 113035732 A CN113035732 A CN 113035732A CN 202110209757 A CN202110209757 A CN 202110209757A CN 113035732 A CN113035732 A CN 113035732A

- Authority

- CN

- China

- Prior art keywords

- dimensional memory

- forming

- stacked structure

- region

- mask layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 230000015654 memory Effects 0.000 title claims abstract description 83

- 238000000034 method Methods 0.000 title claims abstract description 47

- 238000005259 measurement Methods 0.000 claims abstract description 50

- 238000005530 etching Methods 0.000 claims abstract description 35

- 239000000758 substrate Substances 0.000 claims abstract description 25

- 238000009966 trimming Methods 0.000 description 18

- 230000015572 biosynthetic process Effects 0.000 description 10

- 229920002120 photoresistant polymer Polymers 0.000 description 8

- 239000000463 material Substances 0.000 description 7

- 239000004065 semiconductor Substances 0.000 description 6

- 238000004519 manufacturing process Methods 0.000 description 3

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 150000001875 compounds Chemical class 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 239000007787 solid Substances 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- 229910052681 coesite Inorganic materials 0.000 description 1

- 229910052906 cristobalite Inorganic materials 0.000 description 1

- 238000013500 data storage Methods 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000001259 photo etching Methods 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 229910052682 stishovite Inorganic materials 0.000 description 1

- 229910052905 tridymite Inorganic materials 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L22/00—Testing or measuring during manufacture or treatment; Reliability measurements, i.e. testing of parts without further processing to modify the parts as such; Structural arrangements therefor

- H01L22/20—Sequence of activities consisting of a plurality of measurements, corrections, marking or sorting steps

- H01L22/26—Acting in response to an ongoing measurement without interruption of processing, e.g. endpoint detection, in-situ thickness measurement

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L22/00—Testing or measuring during manufacture or treatment; Reliability measurements, i.e. testing of parts without further processing to modify the parts as such; Structural arrangements therefor

- H01L22/10—Measuring as part of the manufacturing process

- H01L22/12—Measuring as part of the manufacturing process for structural parameters, e.g. thickness, line width, refractive index, temperature, warp, bond strength, defects, optical inspection, electrical measurement of structural dimensions, metallurgic measurement of diffusions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L22/00—Testing or measuring during manufacture or treatment; Reliability measurements, i.e. testing of parts without further processing to modify the parts as such; Structural arrangements therefor

- H01L22/30—Structural arrangements specially adapted for testing or measuring during manufacture or treatment, or specially adapted for reliability measurements

- H01L22/34—Circuits for electrically characterising or monitoring manufacturing processes, e. g. whole test die, wafers filled with test structures, on-board-devices incorporated on each die, process control monitors or pad structures thereof, devices in scribe line

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Automation & Control Theory (AREA)

- Semiconductor Memories (AREA)

Abstract

The invention discloses a three-dimensional memory and a method for forming a step area of the three-dimensional memory, wherein the three-dimensional memory comprises the following components: a substrate and a stacked structure on the substrate; wherein the stacked structure includes a step region in which a measurement mark is formed at a first position on a surface of a step; the measurement mark is formed by etching the stack structure.

Description

Technical Field

The invention relates to the technical field of semiconductors, in particular to a three-dimensional memory and a method for forming a step area of the three-dimensional memory.

Background

Memory (Memory) is a Memory device used in modern information technology to store information. With the increasing demands of various electronic devices for integration and data storage density, it is increasingly difficult for a common two-dimensional memory device to meet the demands, and in such a situation, a three-dimensional (3D) memory has come into play.

Currently, three-dimensional memories mainly include a vertical channel layer, and a horizontally stacked gate structure disposed outside the channel layer. The horizontally stacked gate structures generally have stepped regions (SS) so that each layer of gates is electrically connected to a vertical Contact hole (CT) through a corresponding stepped surface, thereby implementing an addressing operation of a corresponding memory cell of each layer of gates. In the actual manufacturing process, if the formation position of the step is shifted, the CT formed in the subsequent process cannot accurately correspond to the corresponding step, which may cause the memory cell in the corresponding gate to fail to operate normally. Therefore, the deviation of the actual forming position of each step in the step region from the preset forming position is important for judging whether the device is successfully prepared at the process stage.

However, since each step in the step region needs to be formed through multiple etching steps, the size and position of the mask layer in each etching process affect the final forming position of the step. It is difficult to calculate the actual step shift by the Overlay (OVL) measurement and the etch trim (ETCH TRIM CD) measurement of the photoresist layer. How to conveniently and accurately determine the actual offset condition of the step becomes one of the technical problems to be solved urgently in the field.

Disclosure of Invention

In view of the above, the present invention provides a three-dimensional memory and a method for forming a step region of the three-dimensional memory.

In order to achieve the purpose, the technical scheme of the invention is realized as follows:

according to a first aspect of embodiments of the present invention, an embodiment of the present invention provides a three-dimensional memory, including: a substrate and a stacked structure on the substrate; wherein,

the stacked structure includes a step region in which a measurement mark is formed at a first position on a surface of a step; the measurement mark is formed by etching the stack structure.

According to a second aspect of the embodiments of the present invention, there is provided a three-dimensional memory including: a substrate and a stacked structure on the substrate; wherein,

the stacked structure includes a step region in which a measurement mark is formed at a first position on a surface of a step;

the first position corresponds to a preset forming position of the step; the step is positioned at the actual forming position of the step;

and the position of the measuring mark and the actual forming position of the step in the step area are used for determining the offset of the step.

In some embodiments, the measurement mark is formed within a dummy region of the three-dimensional memory.

In some embodiments, the measurement mark is formed on a surface of a partial step within the step region.

In some embodiments, the first position is equidistant from the preset forming positions of two adjacent steps.

In some embodiments, the measurement marks are arranged in at least two directions corresponding to a forming direction of at least two step regions on the three-dimensional memory.

According to a third aspect of the embodiments of the present invention, an embodiment of the present invention provides a method for forming a step region of a three-dimensional memory, the method including the steps of:

providing a substrate and a stacked structure on the substrate;

etching the stacked structure, and forming a measurement mark at a first position in preset forming positions of a plurality of steps in the step area of the three-dimensional memory;

etching the stacked structure to form a plurality of steps; the measurement mark is transferred to the surface of the step.

In some embodiments, the first location is within a dummy region of the three-dimensional memory.

In some embodiments, the first position is equidistant from the preset forming positions of two adjacent steps.

In some embodiments, the method further comprises:

and forming a top step in the step area at the same time of forming the measuring mark.

In some embodiments, the method further comprises:

and determining the offset of the step according to the position of the measuring mark and the actual forming position of the step in the step area.

According to the three-dimensional memory and the method for forming the step area of the three-dimensional memory provided by the embodiment of the invention, the measuring mark is formed at the first position on the surface of the step in the step area; thereby, the deviation of the actual forming position of the step in the step area relative to the preset forming position can be determined based on the measuring mark.

Drawings

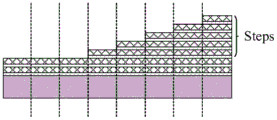

FIGS. 1a to 1c are schematic cross-sectional views of device structures in a process of etching the stacked structure by using a first mask layer as a mask in the related art;

FIGS. 2a-2i are schematic cross-sectional views of device structures in a process of etching the stacked structure by using a second mask layer as a mask in the related art;

FIG. 3 is a schematic diagram illustrating several steps formed in the related art;

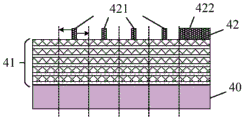

fig. 4a is a schematic structural diagram of a mask according to an embodiment of the present invention;

fig. 4b is an enlarged schematic view of a structure of a portion of the mask corresponding to the dummy region according to another embodiment of the present invention;

FIG. 5 is a flowchart illustrating a method for forming a step region of a three-dimensional memory according to an embodiment of the present invention;

6a-6b are schematic cross-sectional views of device structures in the process of etching the stacked structure by using the first mask layer as a mask in the embodiment of the invention;

fig. 7a to 7i are schematic cross-sectional views of device structures in the process of etching the stacked structure by using the second mask layer as a mask in the embodiment of the present invention.

Detailed Description

Exemplary embodiments of the present disclosure will be described in more detail below with reference to the accompanying drawings. While exemplary embodiments of the invention are shown in the drawings, it should be understood that the invention may be embodied in various forms and should not be limited to the specific embodiments set forth herein. Rather, these embodiments are provided so that this disclosure will be thorough and complete, and will fully convey the scope of the disclosure to those skilled in the art.

In the following description, numerous specific details are set forth in order to provide a more thorough understanding of the present invention. It will be apparent, however, to one skilled in the art, that the present invention may be practiced without one or more of these specific details. In other instances, well-known features have not been described in order to avoid obscuring the present invention; that is, not all features of an actual embodiment are described herein, and well-known functions and structures are not described in detail.

In the drawings, the size of layers, regions, elements, and relative sizes may be exaggerated for clarity. Like reference numerals refer to like elements throughout.

It will be understood that when an element or layer is referred to as being "on" … …, "adjacent to … …," "connected to" or "coupled to" other elements or layers, it can be directly on, adjacent to, connected to or coupled to the other elements or layers or intervening elements or layers may be present. In contrast, when an element is referred to as being "directly on … …," "directly adjacent to … …," "directly connected to" or "directly coupled to" other elements or layers, there are no intervening elements or layers present. It will be understood that, although the terms first, second, third, etc. may be used to describe various elements, components, regions, layers and/or sections, these elements, components, regions, layers and/or sections should not be limited by these terms. These terms are only used to distinguish one element, component, region, layer or section from another element, component, region, layer or section. Thus, a first element, component, region, layer or section discussed below could be termed a second element, component, region, layer or section without departing from the teachings of the present invention. And the discussion of a second element, component, region, layer or section does not necessarily imply that a first element, component, region, layer or section is present in the invention.

Spatial relationship terms such as "under … …", "under … …", "below", "under … …", "above … …", "above", and the like, may be used herein for ease of description to describe the relationship of one element or feature to another element or feature as illustrated in the figures. It will be understood that the spatially relative terms are intended to encompass different orientations of the device in use or operation in addition to the orientation depicted in the figures. For example, if the device in the figures is turned over, then elements or features described as "below" or "beneath" other elements or features would then be oriented "above" the other elements or features. Thus, the exemplary terms "below … …" and "below … …" can encompass both an orientation of up and down. The device may be otherwise oriented (rotated 90 degrees or at other orientations) and the spatial descriptors used herein interpreted accordingly.

The terminology used herein is for the purpose of describing particular embodiments only and is not intended to be limiting of the invention. As used herein, the singular forms "a", "an" and "the" are intended to include the plural forms as well, unless the context clearly indicates otherwise. It will be further understood that the terms "comprises" and/or "comprising," when used in this specification, specify the presence of stated features, integers, steps, operations, elements, and/or components, but do not preclude the presence or addition of one or more other features, integers, steps, operations, elements, components, and/or groups thereof. As used herein, the term "and/or" includes any and all combinations of the associated listed items.

In the following description, for the purposes of explanation, numerous specific details are set forth in order to provide a thorough understanding of the present invention. The following detailed description of the preferred embodiments of the invention, however, the invention is capable of other embodiments in addition to those detailed.

FIGS. 1 and 2 are schematic cross-sectional views illustrating a device structure during a process of forming a step region of a three-dimensional memory in the related art; fig. 1a to 1c are schematic cross-sectional views of a device structure in a process of etching the stacked structure by using a first mask layer as a mask in the related art; fig. 2a-2i are schematic cross-sectional views of device structures in the process of etching the stacked structure by using the second mask layer as a mask in the related art.

First, please refer to fig. 1 a. Providing a three-dimensional memory structure to be etched to form a step area, wherein the three-dimensional memory structure comprises: a substrate 10 and a stacked structure 11 on the substrate 10; the vertical dotted lines in the drawing show the preset forming positions of the respective steps in the step areas.

Next, please refer to fig. 1 b. A first mask layer 12 is formed on the stacked structure 11, and the first mask layer 12 is patterned based on a mask plate, so as to finally form the first mask layer 12 at least covering a storage region (not shown) of the three-dimensional memory and a preset formation position of a top step in a step region as shown in the figure.

Next, please refer to fig. 1 c. Etching the stacked structure 11 by using the first mask layer 12 as a mask, and forming the top step 111 in the step region; the first mask layer 12 is removed.

Next, please refer to fig. 2 a. And forming a second mask layer 13 on the stacked structure 11, wherein the second mask layer 13 is also subjected to patterning processing, and forms a shape corresponding to a pattern to be etched.

Next, please refer to fig. 2 b. Performing a first etch (1) with the second mask layer 13stETCH) that the etching is terminated at a position of a thickness of the sub-top step 112 in the stack structure 11, but at this time, a position of the sub-top step 112 in the step direction has not reached its preset formation position S112。

Here, it is understood that the horizontal direction in the drawing shows the step direction of the step region.

Next, please refer to fig. 2 c. Performing a step (1) of first trimming the dimension of the second mask layer 13stTRIM) to expose more of a surface of the stacked structure after trimming than before trimming; in one embodiment, the TRIM dimension (TRIM CD) in the trimming step is equal to the distance between the boundaries of two adjacent steps along the step direction.

Next, please refer to fig. 2 d. Performing a second etch (2) using the trimmed second mask layer 13 as a maskstETCH), the area of the stacked structure not covered by the second mask layer 13 is entirely lowered by the thickness of one step.

Please refer to fig. 2e-2 h. Repeating the steps of trimming the second mask layer size and etching with the trimmed second mask layer as mask, e.g. performing step 2st TRIM—3st ETCH—3st TRIM—4stETCH (here, the number of trimming and etching are merely examples) to form Steps (Steps).

Finally, please refer to fig. 2 i. The second mask layer 13 is removed.

Therefore, the boundary position of the stacked structure 11 covered by the first mask layer 12 (reflected by the photoresist dimension PH CD), the alignment condition of the second mask layer 13 and the first mask layer 12 (reflected by the photoresist overlay PH OVL measurement), and the trim dimension of each trimming of the first mask layer 12 (reflected by the etch trim dimension ETCH TRIM CD measurement) all affect whether the finally formed step can be located at the preset forming position; if any one of the above-mentioned influencing factors does not meet the preset condition, the actual forming position of the step will be influenced. For example, FIG. 3 illustrates several step formation scenarios; as shown in the figure, for the case (1), the PH OVL is measured to be shifted to the left, that is, the boundary of the second mask layer 13 is shifted to the left in comparison with the preset case, and at this time, even if the subsequent trim size meets the preset case, the step formed by etching is shifted to the left as a whole; for the case (2), the measured PH OVL is shifted to the left, but the step corresponding to the case (2) is ETCH TRIM CD larger before etching, and finally the step is just formed at the preset forming position, and the gate corresponding to the step is conducted without problems; in case (3), ETCH TRIM CD in the previous trimming of the steps corresponding to PH OVL and case (3) are shifted, so that the step corresponding to case (3) is formed at the preset forming position of another step, and at this time, although the gate corresponding to the step can be turned on, the memory cell in the gate cannot normally operate. Therefore, in the etching process of the three-dimensional memory, the actual forming condition of the steps is very complicated; at present, there is no good method for determining the deviation of the actual forming position of each step in the step region from the preset forming position, and the actual deviation of the step is often difficult to be reflected only by PH OVL measurement and ETCH TRIM CD measurement.

Based on the above, the embodiment of the invention provides a mask plate, which is applied to an etching process of a step region of a three-dimensional memory; specifically referring to fig. 4a, the mask 200 includes: the first patterns 210 correspond to preset forming positions of steps in the step area of the three-dimensional memory one to one, and are used for forming a measuring mark at a first position in the preset forming positions of the steps.

Here, the first pattern may be a solid pattern or a blank pattern, which depends on whether the photoresist to be etched is a positive photoresist or a negative photoresist. The shape of the first pattern may include a circle, square, polygon, ring, or other shape; in a preferred embodiment, the first pattern is an axisymmetric pattern so as to facilitate measurement of a distance between a left boundary of the measurement mark and a left boundary forming the step, and a distance between a right boundary of the measurement mark and a right boundary forming the step after the measurement mark is formed on the step.

In a specific embodiment, the first location is within a dummy area (dummy area) of the three-dimensional memory. Here, the dummy area is a non-operating area of the three-dimensional memory, and the measurement mark is formed on a portion of the step located within the dummy area, thereby avoiding affecting the normal operation of the three-dimensional memory.

In a specific embodiment, the first position is located at a middle of the step in the step direction.

In this embodiment, the plurality of steps may be all or part of the steps in the step region of the three-dimensional memory, or at least one of the steps in the different step forming directions.

It is to be understood that the three-dimensional memory includes, but is not limited to, forming a step region in one face or one direction, for example, fig. 4a shows a case where the three-dimensional memory is provided with steps in an arrow direction only at a left side edge in the drawing, and fig. 4b shows a case where the three-dimensional memory is provided with steps in a plurality of directions.

Specifically, fig. 4b is an enlarged schematic structural view of a portion of the mask 200' corresponding to the dummy region according to another embodiment of the present invention; as shown, the plurality of first patterns 210 are arranged in at least two directions corresponding to a predetermined forming direction of at least two step regions on the three-dimensional memory.

Three sets of arrows in the figure respectively show the preset forming directions of three step regions, namely, the three directions are respectively etched on corresponding positions in the three-dimensional memory to form the step regions.

In this embodiment, the first location may also be located within a dummy region of the three-dimensional memory. The offset of the steps in the other areas (working areas) of the three-dimensional memory can be fed back through the dummy area.

In a specific embodiment, the mask further includes a second pattern 220, and the second pattern 220 corresponds to a storage region of the three-dimensional memory and a preset formation position of a top step in a step region, and is used for forming the top step in the step region.

It will be appreciated that the second pattern is used to form a mask layer covering the storage region and the top step in the step region (i.e. defining the top step formation location). The first pattern provided by the embodiment can be formed in an existing mask plate for forming a top-layer step pattern in the prior art, so that the mask plate does not need to be added, and a step region forming process does not need to be added.

The embodiment of the invention also provides a method for forming the step area of the three-dimensional memory; please refer to fig. 5. As shown, the method comprises the steps of:

305, etching the stacked structure by using the second mask layer as a mask to form a plurality of steps; the measurement mark is transferred to the surface of the step.

Next, the method for forming a three-dimensional memory step region according to the embodiment of the present invention will be further described in detail with reference to the schematic cross-sectional views of the device structures in the process of forming the three-dimensional memory step region in fig. 6 and 7.

First, please refer to fig. 6 a.

Step 301 is performed to provide a substrate 40 and a stacked structure 41 on the substrate 40.

Here, the substrate 40 may include at least one elemental semiconductor material (e.g., a silicon (Si) substrate, a germanium (Ge) substrate), at least one III-V compound semiconductor material, at least one II-VI compound semiconductor material, at least one organic semiconductor material, or other semiconductor materials known in the art.

The stack structure 41 may include alternately stacked dielectric layers and gate layers (or dummy gate layers); wherein the material of the dielectric layer includes but is not limited to silicon oxide, silicon nitride layer, silicon oxynitride and other high dielectric constant (high-k) dielectric layers; in one embodiment, the dielectric layer may be made of SiO2Forming; the material of the gate layer may comprise metal tungsten.

Step 302 is executed to form a first mask layer 42 on the stacked structure 41, where the first mask layer 42 includes a plurality of first patterns 421, and the plurality of first patterns 421 correspond to preset forming positions of a plurality of steps in the step region of the three-dimensional memory one-to-one.

In this embodiment, the first pattern of the first mask layer may be formed based on the mask provided in one of the foregoing embodiments of the present invention. Specifically, the pattern in the mask may be transferred onto the first mask layer by a photolithography process. In one embodiment, the first mask layer is a hard mask layer; in the method, the pattern in the mask plate is transferred to the photoresist layer on the first mask layer through a photoetching process, and then the pattern in the photoresist layer is transferred to the first mask layer through an etching step.

In a specific embodiment, the first location is within a dummy region of the three-dimensional memory. Thus, the working area of the three-dimensional memory is not affected.

In a specific embodiment, the first position is located in the middle of a preset formation position of the step in the step direction.

With continued reference to fig. 6a, the vertical dotted lines show the preset forming positions of the steps in the step areas, and the horizontal direction in the figure shows the step direction of the step areas. The first position is located in the middle of the preset forming position of the step in the step direction, which means that the first position is equidistant from the preset forming positions of two adjacent steps.

It is to be understood that the three-dimensional memory includes, but is not limited to, forming the step region in one plane or one direction, and when the step region is formed in at least two directions, the method for forming the step region of the three-dimensional memory provided by the embodiment of the present invention may be used.

In an embodiment, the first mask layer 42 further includes a second pattern 422, and the second pattern 422 corresponds to a storage area of the three-dimensional memory and a preset forming position of a top step in the step area.

It will be appreciated that the second pattern is used to form a mask layer covering the storage region and the top step in the step region (i.e. defining the top step formation location). The measuring mark in the embodiment can be formed in the same step with the top step, and an additional forming process is not required.

Next, please refer to fig. 6 b.

Step 303 is executed, the stack structure is etched by using the first mask layer as a mask, and the measurement mark 44 is formed at a first position in the preset forming position of the step.

In a specific embodiment, the etching the stack structure 41 by using the first mask layer 42 as a mask includes: the top step 411 is formed in the step area. It is understood that, at this time, the measurement mark 44 is located at the same layer as the top step 411, and the measurement mark is gradually transferred to each step in the subsequent etching process.

Here, the top step 411 may be formed by a gate layer (or dummy gate layer) and a dielectric layer.

The shape of the measurement indicia 44 may include a circle, square, polygon, ring, or other shape; in a preferred embodiment, the measurement mark 44 is shaped in an axisymmetric pattern, such that the distance between the left boundary of the measurement mark and the left boundary forming the step, and the distance between the right boundary of the measurement mark and the right boundary forming the step are conveniently measured.

It should be noted that, although fig. 6 and 7 show the case that the first pattern 421 is a solid pattern (i.e., a pattern for shielding the stacked structure 41), and the measurement mark 44 protrudes from the step surface; however, in other embodiments, the first pattern may also be a blank pattern; the measurement mark may be a mark recessed in the step surface.

After the measurement mark 44 is formed, the first mask layer 42 is removed.

Next, please refer to fig. 7 a. Step 304 is performed to form a second mask layer 43 on the stacked structure 41.

Here, the second mask layer covers the measurement mark formed in the previous step and exposes a region to be etched in the stacked structure; namely, the second mask layer is subjected to patterning treatment to form a shape corresponding to the pattern to be etched.

Next, step 305 is executed, the second mask layer 43 is used as a mask to etch the stacked structure 41, so as to form a plurality of steps; the measurement mark 44 is transferred to the surface of the step.

In a specific embodiment, the etching the stacked structure 41 by using the second mask layer 43 as a mask to form a plurality of steps includes: performing the step of trimming the size of the second mask layer for several times, so that more surfaces of the stacked structure are exposed by the trimmed second mask layer than before trimming; and etching the stacked structure by using the second mask layer formed on the stacked structure and the second mask layer after each trimming as a mask to form a plurality of steps.

Specifically, please continue to refer to fig. 7 b. The first etching (1) is performed using the second mask layer 43stETCH) that the etching is terminated at a position of the thickness of the sub-top step 412 in the stack structure 41, but at this time, the position of the sub-top step 412 in the step direction has not reached its preset formation position S412。

Next, please refer to fig. 7 c. Performing a step (1) of first trimming the dimension of the second mask layer 43stTRIM) to expose more of a surface of the stacked structure after trimming than before trimming; in one embodiment, the trimming dimension in the trimming step is equal to the distance between the boundaries of two adjacent steps along the step direction. At this time, the measurement mark between the adjacent two steps is exposed.

Next, please refer to fig. 7 d. The second etching (2) is performed using the trimmed second mask layer 43 as a maskstETCH) that is entirely lowered by the thickness of one step in the region of the stack structure not covered by the second mask layer 43. Thereby, the measurement mark exposed in the previous step is transferred to the next step.

Next, please refer to FIGS. 7e-7 h. Repeating the steps of trimming the second mask layer size and etching with the trimmed second mask layer as mask, e.g. performing step 2st TRIM—3st ETCH—3st TRIM—4stETCH (here, the number of trimming and etching is merely an example, and does not limit the embodiment), so as to form Steps (Steps). Thereby, the measurement mark is transferred onto the surface of the step.

Finally, please refer to fig. 7 i. The second mask layer 43 is removed.

An embodiment of the present invention further provides a three-dimensional memory, which may specifically refer to fig. 7i, including: a substrate 40 and a stacked structure 41 on the substrate 40; wherein the stacked structure 41 includes a step region, and a measurement mark 44 is formed in a first pattern at a first position on a surface of the step within the step region.

In a specific embodiment, the first location is within a dummy region of the three-dimensional memory.

In a specific embodiment, the first position is located in the middle of a preset formation position of the step in the step direction.

In a specific embodiment, the measurement marks are arranged in at least two directions corresponding to a forming direction of at least two step regions on the three-dimensional memory.

The embodiment of the present invention further provides a method for determining a step offset in a step region of a three-dimensional memory, including the steps in the method for forming the step region of the three-dimensional memory in any one of the foregoing embodiments, further including: and determining the offset of the step according to the position of the measuring mark and the actual forming position of the step in the step area.

In a specific embodiment, a first distance between a left side boundary of the measurement mark and a left side boundary forming a step and a second distance between a right side boundary of the measurement mark and a right side boundary forming a step are measured, and an offset amount of the step is calculated based on the first distance and the second distance.

Therefore, the actual forming position of the step in the step area of the three-dimensional memory and the deviation condition of the preset forming position are measured, the actual forming condition of the step can be monitored simply and timely, the yield of the three-dimensional memory can be judged in advance, and the improvement of a production line flow can be helped.

It should be noted that the embodiments of the mask plate, the three-dimensional memory, the method for forming the step region of the three-dimensional memory, and the method for determining the step offset in the step region of the three-dimensional memory provided by the invention belong to the same concept; the technical features of the technical means described in the embodiments may be arbitrarily combined without conflict. It should be further noted that, in the three-dimensional memory provided by the embodiment of the present invention, the technical feature combinations thereof can already solve the technical problems to be solved by the present invention; therefore, the three-dimensional memory provided by the embodiment of the present invention may not be limited by the method for forming the step region of the three-dimensional memory provided by the embodiment of the present invention, and any three-dimensional memory that can be manufactured by the method for manufacturing the three-dimensional memory structure provided by the embodiment of the present invention is within the protection scope of the present invention.

The above description is only exemplary of the present invention and should not be taken as limiting the scope of the present invention, and any modifications, equivalents, improvements, etc. that are within the spirit and principle of the present invention should be included in the present invention.

Claims (11)

1. A three-dimensional memory, comprising: a substrate and a stacked structure on the substrate; wherein,

the stacked structure includes a step region in which a measurement mark is formed at a first position on a surface of a step; the measurement mark is formed by etching the stack structure.

2. A three-dimensional memory, comprising: a substrate and a stacked structure on the substrate; wherein,

the stacked structure includes a step region in which a measurement mark is formed at a first position on a surface of a step;

the first position corresponds to a preset forming position of the step; the step is positioned at the actual forming position of the step;

and the position of the measuring mark and the actual forming position of the step in the step area are used for determining the offset of the step.

3. The three-dimensional memory according to claim 1 or 2, wherein the measurement mark is formed in a dummy area of the three-dimensional memory.

4. The three-dimensional memory according to claim 1 or 2, wherein the measurement mark is formed on a surface of a partial step within the step region.

5. The three-dimensional memory according to claim 1 or 2, wherein the first position is equidistant from the preset forming positions of two adjacent steps.

6. The three-dimensional memory according to claim 1 or 2, wherein the measurement marks are arranged in at least two directions corresponding to a forming direction of at least two step areas on the three-dimensional memory.

7. A method for forming a step area of a three-dimensional memory, the method comprising the steps of:

providing a substrate and a stacked structure on the substrate;

etching the stacked structure, and forming a measurement mark at a first position in preset forming positions of a plurality of steps in the step area of the three-dimensional memory;

etching the stacked structure to form a plurality of steps; the measurement mark is transferred to the surface of the step.

8. The method of claim 7, wherein the first location is within a dummy region of the three-dimensional memory.

9. The method of claim 7, wherein the first position is equidistant from the predetermined forming positions of two adjacent steps.

10. The method of claim 7, further comprising:

and forming a top step in the step area at the same time of forming the measuring mark.

11. The method according to any one of claims 7-10, further comprising:

and determining the offset of the step according to the position of the measuring mark and the actual forming position of the step in the step area.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202110209757.1A CN113035732B (en) | 2019-06-11 | 2019-06-11 | Three-dimensional memory and method for forming step area of three-dimensional memory |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202110209757.1A CN113035732B (en) | 2019-06-11 | 2019-06-11 | Three-dimensional memory and method for forming step area of three-dimensional memory |

| CN201910503430.8A CN110379724B (en) | 2019-06-11 | 2019-06-11 | Mask plate, three-dimensional memory and related preparation and measurement methods |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201910503430.8A Division CN110379724B (en) | 2019-06-11 | 2019-06-11 | Mask plate, three-dimensional memory and related preparation and measurement methods |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN113035732A true CN113035732A (en) | 2021-06-25 |

| CN113035732B CN113035732B (en) | 2021-12-28 |

Family

ID=68250170

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201910503430.8A Active CN110379724B (en) | 2019-06-11 | 2019-06-11 | Mask plate, three-dimensional memory and related preparation and measurement methods |

| CN202110209757.1A Active CN113035732B (en) | 2019-06-11 | 2019-06-11 | Three-dimensional memory and method for forming step area of three-dimensional memory |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201910503430.8A Active CN110379724B (en) | 2019-06-11 | 2019-06-11 | Mask plate, three-dimensional memory and related preparation and measurement methods |

Country Status (1)

| Country | Link |

|---|---|

| CN (2) | CN110379724B (en) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN111162081B (en) * | 2020-01-02 | 2022-04-26 | 长江存储科技有限责任公司 | Method for forming step region and method for manufacturing semiconductor device |

| CN112951805B (en) * | 2021-02-19 | 2023-08-08 | 长江存储科技有限责任公司 | Three-dimensional memory with marking structure, preparation method thereof and displacement monitoring method |

Citations (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104520985A (en) * | 2012-07-06 | 2015-04-15 | 美光科技公司 | Stair step formation using at least two masks |

| CN104662663A (en) * | 2012-06-15 | 2015-05-27 | 桑迪士克3D有限责任公司 | Non-volatile memory having 3d array architecture with staircase word lines and vertical bit lines and methods thereof |

| US20170083249A1 (en) * | 2015-09-18 | 2017-03-23 | Sandisk Technologies Inc. | Dynamic reconditioning of charge trapped based memory |

| CN106847822A (en) * | 2017-03-08 | 2017-06-13 | 长江存储科技有限责任公司 | 3D nand memories part, manufacture method and step calibration method |

| CN107564914A (en) * | 2017-08-31 | 2018-01-09 | 长江存储科技有限责任公司 | A kind of 3D nand memories part and preparation method thereof |

| US20180033881A1 (en) * | 2013-03-11 | 2018-02-01 | Monolithic 3D Inc. | 3dic device with memory |

| CN107818983A (en) * | 2017-08-25 | 2018-03-20 | 长江存储科技有限责任公司 | A kind of marker graphic and forming method thereof |

| CN107895724A (en) * | 2017-11-13 | 2018-04-10 | 中国科学院微电子研究所 | Three-dimensional memory and manufacturing method thereof |

| WO2018144957A1 (en) * | 2017-02-04 | 2018-08-09 | Monolithic 3D Inc. | 3d semiconductor device and structure |

| CN108550574A (en) * | 2018-05-03 | 2018-09-18 | 长江存储科技有限责任公司 | Three-dimensional storage part and its manufacturing method |

| CN109309095A (en) * | 2017-07-26 | 2019-02-05 | 三星电子株式会社 | Three-dimensional semiconductor device |

| US20190057959A1 (en) * | 2015-06-06 | 2019-02-21 | Monolithic 3D Inc. | Semiconductor device and structure with thermal isolation |

| US20190123061A1 (en) * | 2017-10-20 | 2019-04-25 | Nustorage Technology Co., Ltd. | Three-dimensional memory device and manufacturing method thereof |

| CN109712988A (en) * | 2018-12-27 | 2019-05-03 | 长江存储科技有限责任公司 | 3D memory device and its manufacturing method |

| CN109860196A (en) * | 2019-02-14 | 2019-06-07 | 长江存储科技有限责任公司 | The forming method of 3D nand memory |

| CN109860201A (en) * | 2019-04-09 | 2019-06-07 | 长江存储科技有限责任公司 | A kind of nand memory, mask plate and production method |

| CN109860036A (en) * | 2019-01-02 | 2019-06-07 | 华中科技大学 | A kind of nanometer wire grid electrodes and preparation method thereof of non-volatile 3D nand memory |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101117589B1 (en) * | 2010-02-19 | 2012-02-20 | 서울대학교산학협력단 | Fabrication method of single crystalline silicon stacked array and 3d nand flash memory array using the same |

| US8329051B2 (en) * | 2010-12-14 | 2012-12-11 | Lam Research Corporation | Method for forming stair-step structures |

| KR102499385B1 (en) * | 2015-10-01 | 2023-02-14 | 에스케이하이닉스 주식회사 | Manufacturing method of memory device |

| US9595535B1 (en) * | 2016-02-18 | 2017-03-14 | Sandisk Technologies Llc | Integration of word line switches with word line contact via structures |

-

2019

- 2019-06-11 CN CN201910503430.8A patent/CN110379724B/en active Active

- 2019-06-11 CN CN202110209757.1A patent/CN113035732B/en active Active

Patent Citations (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104662663A (en) * | 2012-06-15 | 2015-05-27 | 桑迪士克3D有限责任公司 | Non-volatile memory having 3d array architecture with staircase word lines and vertical bit lines and methods thereof |

| US20180130700A1 (en) * | 2012-07-06 | 2018-05-10 | Micron Technology, Inc. | Stair step formation using at least two masks |

| CN104520985A (en) * | 2012-07-06 | 2015-04-15 | 美光科技公司 | Stair step formation using at least two masks |

| US20180033881A1 (en) * | 2013-03-11 | 2018-02-01 | Monolithic 3D Inc. | 3dic device with memory |

| US20190057959A1 (en) * | 2015-06-06 | 2019-02-21 | Monolithic 3D Inc. | Semiconductor device and structure with thermal isolation |

| US20170083249A1 (en) * | 2015-09-18 | 2017-03-23 | Sandisk Technologies Inc. | Dynamic reconditioning of charge trapped based memory |

| CN107924701A (en) * | 2015-09-18 | 2018-04-17 | 桑迪士克科技有限责任公司 | The dynamic of memory based on capture electric charge is resetted |

| WO2018144957A1 (en) * | 2017-02-04 | 2018-08-09 | Monolithic 3D Inc. | 3d semiconductor device and structure |

| CN106847822A (en) * | 2017-03-08 | 2017-06-13 | 长江存储科技有限责任公司 | 3D nand memories part, manufacture method and step calibration method |

| CN109309095A (en) * | 2017-07-26 | 2019-02-05 | 三星电子株式会社 | Three-dimensional semiconductor device |

| CN107818983A (en) * | 2017-08-25 | 2018-03-20 | 长江存储科技有限责任公司 | A kind of marker graphic and forming method thereof |

| CN107564914A (en) * | 2017-08-31 | 2018-01-09 | 长江存储科技有限责任公司 | A kind of 3D nand memories part and preparation method thereof |

| US20190123061A1 (en) * | 2017-10-20 | 2019-04-25 | Nustorage Technology Co., Ltd. | Three-dimensional memory device and manufacturing method thereof |

| CN107895724A (en) * | 2017-11-13 | 2018-04-10 | 中国科学院微电子研究所 | Three-dimensional memory and manufacturing method thereof |

| CN108550574A (en) * | 2018-05-03 | 2018-09-18 | 长江存储科技有限责任公司 | Three-dimensional storage part and its manufacturing method |

| CN109712988A (en) * | 2018-12-27 | 2019-05-03 | 长江存储科技有限责任公司 | 3D memory device and its manufacturing method |

| CN109860036A (en) * | 2019-01-02 | 2019-06-07 | 华中科技大学 | A kind of nanometer wire grid electrodes and preparation method thereof of non-volatile 3D nand memory |

| CN109860196A (en) * | 2019-02-14 | 2019-06-07 | 长江存储科技有限责任公司 | The forming method of 3D nand memory |

| CN109860201A (en) * | 2019-04-09 | 2019-06-07 | 长江存储科技有限责任公司 | A kind of nand memory, mask plate and production method |

Non-Patent Citations (1)

| Title |

|---|

| 杨红官等: "p沟道锗/硅异质纳米结构MOSFET存储器及其逻辑阵列 ", 《半导体学报》 * |

Also Published As

| Publication number | Publication date |

|---|---|

| CN110379724B (en) | 2021-04-06 |

| CN113035732B (en) | 2021-12-28 |

| CN110379724A (en) | 2019-10-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100884855B1 (en) | Semiconductor device and method of manufactruing the same | |

| KR100599218B1 (en) | Semiconductor integrated circuit device | |

| US8163190B2 (en) | Method for fabricating a fine pattern | |

| EP3827460B1 (en) | Methods for forming multi-division staircase structure of three-dimensional memory device | |

| JP2002118235A (en) | Semiconductor device, method for manufacturing semiconductor, and mask for manufacturing the same | |

| US10474027B2 (en) | Method for forming an aligned mask | |

| KR20180029094A (en) | How to pattern without a dummy gate | |

| CN108666207B (en) | Method for manufacturing semiconductor element | |

| CN113035732B (en) | Three-dimensional memory and method for forming step area of three-dimensional memory | |

| US20100059825A1 (en) | Integrated circuit and a method of making an integrated circuit to provide a gate contact over a diffusion region | |

| US20070194466A1 (en) | Overlay measurement mark and pattern formation method for the same | |

| US10756022B2 (en) | Methods of alignment marking semiconductor wafers, and semiconductor packages having portions of alignment markings | |

| JP5044095B2 (en) | Manufacturing method of semiconductor device | |

| US20120286402A1 (en) | Protuberant structure and method for making the same | |

| US20230022941A1 (en) | Pick-up structure for memory device and manufacturing method thereof | |

| JP2008258493A (en) | Forming method of wiring of semiconductor memory device | |

| CN217334088U (en) | Semiconductor device with a plurality of semiconductor chips | |

| US20240147717A1 (en) | Pick-up structure of memory device and method for manufacturing memory device | |

| KR100946023B1 (en) | Align key and manufacturing method thereof | |

| US8057987B2 (en) | Patterning method of semiconductor device | |

| CN107968045B (en) | Etching method | |

| CN116844954A (en) | Method for forming semiconductor element pattern | |

| CN116259608A (en) | Overlay mark structure and forming method thereof | |

| CN117238849A (en) | Semiconductor device and method of manufacturing the same | |

| CN112951805A (en) | Three-dimensional memory with marking structure, preparation method thereof and displacement monitoring method |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PB01 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| GR01 | Patent grant | ||

| GR01 | Patent grant |