CN217334088U - Semiconductor device with a plurality of semiconductor chips - Google Patents

Semiconductor device with a plurality of semiconductor chips Download PDFInfo

- Publication number

- CN217334088U CN217334088U CN202220324522.7U CN202220324522U CN217334088U CN 217334088 U CN217334088 U CN 217334088U CN 202220324522 U CN202220324522 U CN 202220324522U CN 217334088 U CN217334088 U CN 217334088U

- Authority

- CN

- China

- Prior art keywords

- pattern

- patterns

- semiconductor device

- extension portion

- extension

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

The utility model discloses a semiconductor device, including a basement, a plurality of first patterns and a plurality of second pattern setting are on this basement, and each this first pattern includes a first main part and a first extension part interconnect, and each this second pattern includes a second main part and a second extension part interconnect, and wherein, this first main part all includes an at least arcuation pattern with this second main part. Therefore, the utility model discloses can utilize self-align double patterning manufacturing process cooperation patterning mask layer to form the specific pattern that the overall arrangement is intensive relatively and the size is small relatively to do benefit to going on of follow-up subassembly manufacturing process.

Description

Technical Field

The present invention relates to a semiconductor device, and more particularly to a semiconductor memory device.

Background

In a semiconductor fabrication process, some microstructures are fabricated by photolithography and etching on a suitable substrate or material layer, such as a semiconductor substrate/film, a dielectric material layer, or a metal material layer, to form a fine pattern with precise dimensions. To this end, in conventional semiconductor technology, a mask layer is formed over a target material layer so that the minute patterns are first formed/defined in the mask layer and then transferred to the target layer. Generally, the mask layer is, for example, a patterned photoresist layer formed by a photolithography process, and/or a patterned mask layer formed using the patterned photoresist layer.

As integrated circuits become more complex, the size of these micro-patterns is decreasing and the structure of the micro-patterns is changing, so that the equipment for generating the feature patterns must meet the strict requirements of resolution and overlay accuracy (overlay accuracy), and the single patterning method cannot meet the resolution requirement or the process requirement for manufacturing the micro-line width patterns. Therefore, how to improve the existing manufacturing process of these micro-structures is one of the important issues in the field today.

SUMMERY OF THE UTILITY MODEL

In one aspect of the present invention, a semiconductor device is provided, which includes a substrate, and a plurality of first patterns and a plurality of second patterns disposed on the substrate, wherein each of the first patterns includes a first main portion and a first extended portion connected to each other, and each of the second patterns includes a second main portion and a second extended portion connected to each other, wherein the first main portion and the second main portion each include at least one arc-shaped pattern.

Another aspect of the present invention is to provide a method for forming a semiconductor device, which includes providing a substrate, forming a material layer on the substrate, patterning the material layer to form a plurality of first patterns and a plurality of second patterns on the substrate, wherein each of the first patterns includes a first main portion and a first extended portion connected to each other, and each of the second patterns includes a second main portion and a second extended portion connected to each other, wherein each of the first main portion and the second main portion includes at least one arc-shaped pattern.

The utility model provides a semiconductor storage device and forming method thereof. The utility model is characterized in that a plurality of clearance walls are formed by self-aligned double patterning (SADP) manufacturing process, and the patterning manufacturing process of the material layer is carried out after the clearance walls are further trimmed by the patterning mask layer. Therefore, two opposite sides of the formed first pattern and the second pattern can respectively form two extending parts with larger areas, which extend towards opposite directions, so as to be beneficial to the subsequent component manufacturing process.

Drawings

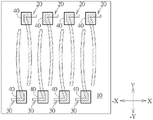

Fig. 1 to 6 are schematic top views illustrating a method for forming a semiconductor device according to a first preferred embodiment of the present invention.

Fig. 7 is a schematic top view of the first pattern, the second pattern and the contact structure according to another preferred embodiment of the present invention.

Fig. 8 is a schematic top view of the first pattern, the second pattern and the contact structure according to another preferred embodiment of the present invention.

Fig. 9 and fig. 10 are schematic top views respectively showing the first pattern, the second pattern and the contact structure according to another two preferred embodiments of the present invention.

Wherein the reference numerals are as follows:

10 base

11 layer of material

12 first sacrificial pattern

14 second sacrificial pattern

16 spacer

18 pattern

20 first pattern

22 first body part

24 first extension

26 first hook portion

30 second pattern

32 second body part

34 second extension

36 second hook portion

40 contact structure

A connecting part

Width of W1

Width of W2

In the X direction

Y direction

Detailed Description

To further clarify the present invention, those skilled in the art will be able to understand the present invention by referring to the following detailed description of several preferred embodiments of the present invention, and by referring to the accompanying drawings, the constituent elements of the present invention and intended functions will be described in detail.

Referring to fig. 1 to 6, fig. 1 to 6 are schematic top views illustrating a method for forming a semiconductor device according to a first preferred embodiment of the present invention. First, referring to fig. 1, a substrate 10 is provided, and a material layer 11 is formed on the substrate 10. The material layer 11 includes, for example, a conductive material, such as a low-resistance metal material, such as tungsten (W), aluminum (Al), or copper (Cu), or both include a dielectric material, such as silicon oxide, silicon nitride (SiN), silicon oxynitride (SiON), or silicon carbonitride (SiCN), but not limited thereto.

Then, a patterning process of the material layer 11 is performed. In the present embodiment, the patterning process is performed through a self-aligned double patterning process, but not limited thereto. In detail, a plurality of first sacrificial patterns 12 and two second sacrificial patterns 14 are formed on the material layer 11 by a photolithography process. The first sacrificial patterns 12 include oval shapes and are arranged in parallel along a vertical direction (e.g., Y-axis direction), and the two second sacrificial patterns are respectively located at two sides (e.g., upper and lower sides) of the first sacrificial patterns 12 and are arranged along a horizontal direction without contacting with each of the first sacrificial patterns 12.

As shown in fig. 2, deposition and etch back processes are sequentially performed to form a spacer 16 on the peripheral sidewalls of each of the first sacrificial patterns 12 and each of the second sacrificial patterns 14. It is noted that the distance between each first sacrificial pattern 12 and each second sacrificial pattern 14 is designed such that after the spacers 16 are formed, the spacers 16 surrounding each first sacrificial pattern 12 are connected to the spacers 16 partially surrounding the second sacrificial pattern 14 (e.g., the connection portion a circled in fig. 2).

Next, as shown in fig. 3, after each of the first sacrificial patterns 12 and two of the second sacrificial patterns 14 are completely removed, as shown in fig. 4, the pattern of the spacer 16 is transferred into the underlying material layer 11 by using the remaining spacer 16 as a mask. To form a pattern 18 of material layer 11 on substrate 10. That is, the material of the pattern 18 is the same as the material of the material layer 11.

As shown in fig. 5, an etch trim process is performed that will remove a portion of pattern 18. The etch trimming process described herein may, for example, cover a patterned mask (not shown) to shield portions of pattern 18 while exposing portions of pattern 18, and then remove portions of exposed pattern 18 using an etching step or other suitable steps, followed by removing the patterned mask. After the etching trimming process, the remaining pattern 18 is defined as a first pattern 20 and a second pattern 30, wherein the first pattern 20 includes an arc-shaped first main portion 22 and a linear first extension portion 24 connected to each other, and the second pattern 30 includes an arc-shaped second main portion 32 and a linear second extension portion 34 connected to each other. The first extending portions 24 and the second extending portions 34 are arranged along a horizontal direction (e.g., X direction), the first patterns 20 are the same as each other, the second patterns 30 are the same as each other, and the first patterns 20 and the second patterns 30 are alternately arranged when viewed from the horizontal direction (X direction). That is, any two first patterns 20 sandwich one second pattern 30, and similarly any two second patterns 30 sandwich one first pattern 20, except for the endmost pattern.

In the present embodiment, each first body portion 22 is convex in a positive X-direction, and each second body portion 32 is convex in a negative X-direction. Wherein the positive X direction is opposite the negative X direction. In addition, in the present embodiment, the first extension portion 24 is connected to a top end (i.e., the end facing the uppermost in the + Y direction) of the first main body portion 22, and similarly, the second extension portion 32 is connected to a bottom end (i.e., the end facing the lowermost in the-Y direction) of the second main body portion 34.

Finally, as shown in fig. 6, at least one contact structure 40 is formed, the contact structure 40 is, for example, a contact plug electrically connected to other devices, and the contact structure 40 overlaps and is electrically connected to a portion of the first pattern 20 and/or the second pattern 30. For example, contact structure 40 may contact the interface between the arc-shaped first body portion 22 and the first extension portion 24 of the first pattern 20, or the interface between the arc-shaped second body portion 32 and the second extension portion 34 of the second pattern 30. In the present embodiment, since the first pattern 20 and the second pattern 30 respectively have the first extending portion 24 and the second extending portion 34 at the ends, the areas of the ends of the first pattern 20 and the second pattern 30 are increased, and when the contact structure 40 needs to be electrically connected with the contact ends of the first pattern 20 and the second pattern 30, there is more sufficient space for the alignment of the contact structure 40 to reliably contact the first pattern 20 and the second pattern 30. In addition, since the contact area between the contact structure 40 and the first pattern 20 and/or the second pattern 30 is increased, the interface resistance can be also reduced, and the quality of the semiconductor device can be improved.

The first pattern 20 and the second pattern 30 can be applied to different semiconductor devices, such as Bit Line (BL) or Word Line (WL) patterns in a memory device, and all fall within the scope of the present invention.

In other embodiments of the present invention, the first pattern 20 and the second pattern 30 having different shapes may be formed by adjusting the position of the sacrificial pattern. The following drawings illustrate various embodiments of the present invention, and the main difference is that the shapes or arrangement positions of the first pattern 20, the second pattern 30 and the contact structure 40 are partially different from those of the first preferred embodiment. However, it is understood that the materials and fabrication processes for the components may be the same, and thus, the detailed description is not repeated. In the following description, reference will be made to the different parts of the pattern, and the same or similar components will be denoted by the same reference numerals.

Fig. 7 is a schematic view showing the distribution of the first pattern, the second pattern and the contact structure in another preferred embodiment of the present invention. As shown in fig. 7, the arrangement positions of the sacrificial patterns are adjusted to form the first pattern 20 and the second pattern 30 by the steps similar to those described in the above embodiment, wherein the difference from the above embodiment is that the first extension portion 24 of the present embodiment is not connected to the extreme end of the first main body portion 22, but is connected to the position where the side of the first main body portion 22 is close to the end but not the extreme end, and similarly, the second extension portion 34 is not connected to the extreme end of the second main body portion 32, but is connected to the position where the side of the second main body portion 32 is close to the end but not the extreme end. This embodiment also falls within the scope of the present invention.

Further, in this embodiment, the end of the first body portion 22 is defined as a first hook portion 26 and the end of the second body portion 32 is defined as a second hook portion 36. Since the first and second hook portions 26, 36 have relatively larger areas, for example, the maximum width W1 of the first hook portion 26 in the Y direction is greater than the width W2 of the first extension portion 24, the contact structure 40 may also overlap and electrically connect with the first and second hook portions 26, 36. In the present invention, the position of the contact structure 40 connecting the first pattern 20 or the second pattern 30 is not limited, and the contact structure 40 may be overlapped and electrically connected with the arc-shaped first/second main body portion, the linear first/second extending portion, and the first/second hook portion.

Fig. 8 is a schematic view illustrating the distribution of the first pattern, the second pattern and the contact structure according to another preferred embodiment of the present invention. As shown in fig. 8, the arrangement position of the sacrificial patterns may be adjusted to form the first pattern 20 and the second pattern 30 by similar steps as described in the above embodiments, wherein the first pattern 20 and the second pattern 30 may be staggered by a distance in the vertical direction (e.g., Y direction). That is, the first extension portions 24 of the respective first patterns 20 are aligned with each other along the X-direction, while the first body portions 22 of the respective first patterns 20 are not aligned with each other but staggered up and down in the X-direction. Similarly, the second extension portions 34 of the respective second patterns 30 are aligned with each other along the X-direction, while the second body portions 32 of the respective second patterns 30 are not aligned with each other but staggered up and down in the X-direction. Thus, when the contact structure 40 is formed, the contact structure 40 is less likely to be contacted, so that the probability of short circuit can be reduced.

Fig. 9 and fig. 10 are schematic top views respectively showing the first pattern, the second pattern and the contact structure according to another two preferred embodiments of the present invention. In the present embodiment, the shape of the first sacrificial pattern 12 or the second sacrificial pattern 14 formed at the beginning may be adjusted, thereby changing the shapes of the first pattern 20 and the second pattern 30. For example, in the embodiments, the first pattern 20 and the second pattern 30 have arc-shaped main body portions (including the first main body portion 22 and the second main body portion 32), but in the embodiments of fig. 9 and 10, the first pattern 20 and the second pattern 30 include straight-bar-shaped first main body portions 22 and second main body portions 32. Such embodiments are also within the scope of the present invention.

In summary, the present invention provides a semiconductor device, which comprises a substrate, a plurality of first patterns and a plurality of second patterns disposed on the substrate, wherein each of the first patterns comprises a first main portion and a first extending portion connected to each other, each of the second patterns comprises a second main portion and a second extending portion connected to each other, and wherein the first main portion and the second main portion all comprise at least one arc-shaped pattern, and at least one contact structure overlapping with the first pattern or the second pattern.

The present invention also provides a method of forming a semiconductor device, the method comprising providing a substrate, forming a material layer on the substrate, patterning the material layer to form a plurality of first patterns and a plurality of second patterns on the substrate, wherein each of the first patterns comprises a first main portion and a first extending portion connected to each other, and each of the second patterns comprises a second main portion and a second extending portion connected to each other, wherein the first main portion and the second main portion each comprise at least one arc-shaped pattern.

In some embodiments, the first extension portion and the second extension portion comprise a horizontal line pattern.

In some embodiments, the first extension portion and the second extension portion are both arranged in an X direction.

In some embodiments, the first pattern and the second pattern are alternately arranged along an X direction.

In some embodiments, each of the first body portions is convex in a positive X direction, and each of the second body portions is convex in a negative X direction, wherein the positive X direction is opposite to the negative X direction.

In some embodiments, the first extension portion is connected to a top end of the first body portion, and the second extension portion is connected to a bottom end of the second body portion.

In some embodiments, the first extension portion is connected to a side of the first body portion, and the second extension portion is connected to a side of the second body portion.

In some embodiments, along an X-direction, the first extension portions of the first patterns are aligned with each other, and the first main portions of the first patterns are not aligned with each other.

In some embodiments, an end of the first body portion includes a hook portion having a width greater than a width of the first extension portion.

In some embodiments, the method of forming the first pattern and the second pattern further comprises forming a sacrificial pattern on the material layer, wherein the sacrificial pattern comprises a plurality of first sacrificial patterns arranged in parallel in a Y direction and two second sacrificial patterns arranged in an X direction, wherein the second sacrificial patterns do not contact the first sacrificial patterns, and the Y direction is perpendicular to the X direction.

In some embodiments, each of the first sacrificial patterns has an oblong shape.

In some embodiments, a spacer is formed around the periphery of the first sacrificial pattern and the second sacrificial pattern.

In some embodiments, the spacer partially surrounding the periphery of the first sacrificial pattern directly contacts the spacer partially surrounding the periphery of the second sacrificial pattern.

In some embodiments, the method further comprises removing the spacer, and etching the material layer using the sacrificial pattern and the sacrificial material layer as masks to form the first pattern and the second pattern.

In some embodiments, further comprising forming a contact structure, wherein the contact structure contacts the first body portion of the first pattern.

In some embodiments, forming a contact structure, wherein the contact structure contacts the first extension of the first pattern, is further included.

In some embodiments, further comprising forming a contact structure, wherein an end of the first body portion comprises a hooked portion, and the contact structure contacts the hooked portion of the first body portion of the first pattern.

To sum up, the utility model provides a semiconductor storage device and forming method thereof. The utility model is characterized in that a plurality of clearance walls are formed by self-aligning double patterning (SADP) manufacturing process, and the patterning manufacturing process of the material layer is carried out after the clearance walls are further trimmed by the patterning mask layer. Therefore, two opposite sides of the formed first pattern and the second pattern can respectively form two extending parts with larger areas, which extend towards opposite directions, so as to be beneficial to the subsequent component manufacturing process.

The above description is only a preferred embodiment of the present invention and is not intended to limit the present invention, and various modifications and changes may be made by those skilled in the art. Any modification, equivalent replacement, or improvement made within the spirit and principle of the present invention should be included in the protection scope of the present invention. Any modification, equivalent replacement, or improvement made within the spirit and principle of the present invention should be included in the protection scope of the present invention.

Claims (9)

1. A semiconductor device, comprising:

a substrate; and

a plurality of first patterns and a plurality of second patterns are disposed on the substrate, each of the first patterns includes a first main portion and a first extension portion connected to each other, each of the second patterns includes a second main portion and a second extension portion connected to each other, wherein each of the first main portion and the second main portion includes at least one arc-shaped pattern.

2. The semiconductor device of claim 1, wherein the first extension portion and the second extension portion comprise a horizontal line pattern.

3. The semiconductor device according to claim 2, wherein the first extension portion and the second extension portion are arranged in an X direction.

4. The semiconductor device of claim 1, wherein the first pattern and the second pattern are alternately arranged along an X direction.

5. The semiconductor device of claim 1, wherein each of the first body portions is convex toward a positive X-direction, wherein each of the second body portions is convex toward a negative X-direction, wherein the positive X-direction is opposite to the negative X-direction.

6. The semiconductor device of claim 1, wherein the first extension portion is connected to a top end of the first body portion, and wherein the second extension portion is connected to a bottom end of the second body portion.

7. The semiconductor device of claim 1, wherein the first extension portion connects to a side of the first body portion, and wherein the second extension portion connects to a side of the second body portion.

8. The semiconductor device of claim 7, wherein an end of the first body portion includes a hook portion having a width greater than a width of the first extension portion.

9. The semiconductor device according to claim 1, wherein the first extension portions of the first patterns are aligned with each other and the first body portions of the first patterns are not aligned with each other along an X-direction.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202220324522.7U CN217334088U (en) | 2022-02-17 | 2022-02-17 | Semiconductor device with a plurality of semiconductor chips |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202220324522.7U CN217334088U (en) | 2022-02-17 | 2022-02-17 | Semiconductor device with a plurality of semiconductor chips |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN217334088U true CN217334088U (en) | 2022-08-30 |

Family

ID=82997337

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN202220324522.7U Active CN217334088U (en) | 2022-02-17 | 2022-02-17 | Semiconductor device with a plurality of semiconductor chips |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN217334088U (en) |

-

2022

- 2022-02-17 CN CN202220324522.7U patent/CN217334088U/en active Active

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN109166836B (en) | Semiconductor device and method of manufacture | |

| US8592978B2 (en) | Method of fabricating semiconductor device and the semiconductor device | |

| CN109148269B (en) | Method for forming semiconductor device | |

| JP2008004724A (en) | Semiconductor device and its manufacturing method | |

| US11342333B2 (en) | Semiconductor device | |

| US20060276019A1 (en) | Method for production of contacts on a wafer | |

| CN217334088U (en) | Semiconductor device with a plurality of semiconductor chips | |

| CN113035732B (en) | Three-dimensional memory and method for forming step area of three-dimensional memory | |

| CN110707038B (en) | Semiconductor device and method of forming the same | |

| US11804381B2 (en) | Conductive wire structure | |

| CN215955280U (en) | Semiconductor memory device with a plurality of memory cells | |

| CN114512476A (en) | Semiconductor device and method of forming the same | |

| CN212010970U (en) | Semiconductor device with a plurality of semiconductor chips | |

| JPH11251430A (en) | Method and system for mutually connecting conductive elements in integrated circuit | |

| US6413872B1 (en) | Method op optimizing vias between conductive layers in an integrated circuit structure | |

| CN109581817B (en) | Method for forming semiconductor device | |

| KR101087786B1 (en) | Semiconductor device and method for forming using the same | |

| CN114141698A (en) | Semiconductor structure and preparation method thereof | |

| US12087582B2 (en) | Improving resolution of masks for semiconductor manufacture | |

| US7030011B2 (en) | Method for avoiding short-circuit of conductive wires | |

| CN110767627A (en) | Semiconductor device and manufacturing process thereof | |

| US20010010958A1 (en) | Fabrication method to approach the conducting structure of a dram cell with straight forward bit line | |

| CN113140622B (en) | Method for arranging metal layers in power device | |

| US20230022941A1 (en) | Pick-up structure for memory device and manufacturing method thereof | |

| US20230326904A1 (en) | Method of manufacturing semiconductor device having air cavity |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| GR01 | Patent grant | ||

| GR01 | Patent grant |