FPGA Hardware Simulation Framework 2.0

-

includes generation of .exe file!

-

includes connection to circuitjs over websockets!

(the circuitjs simulation may even be run in a separate computer).

-

links:

To install dependencies go to python\hw_sim_fwk_2 and type:

pip_install_requirements.bat

To install the designer tool type:

pip install pygubu-designer

To generate and run an executable file go to python\hw_sim_fwk_2 and type:

gen_and_run_exe.bat

This only takes a moment to complete.

This tool provides the following features, usually not supported by standard simulation methods:

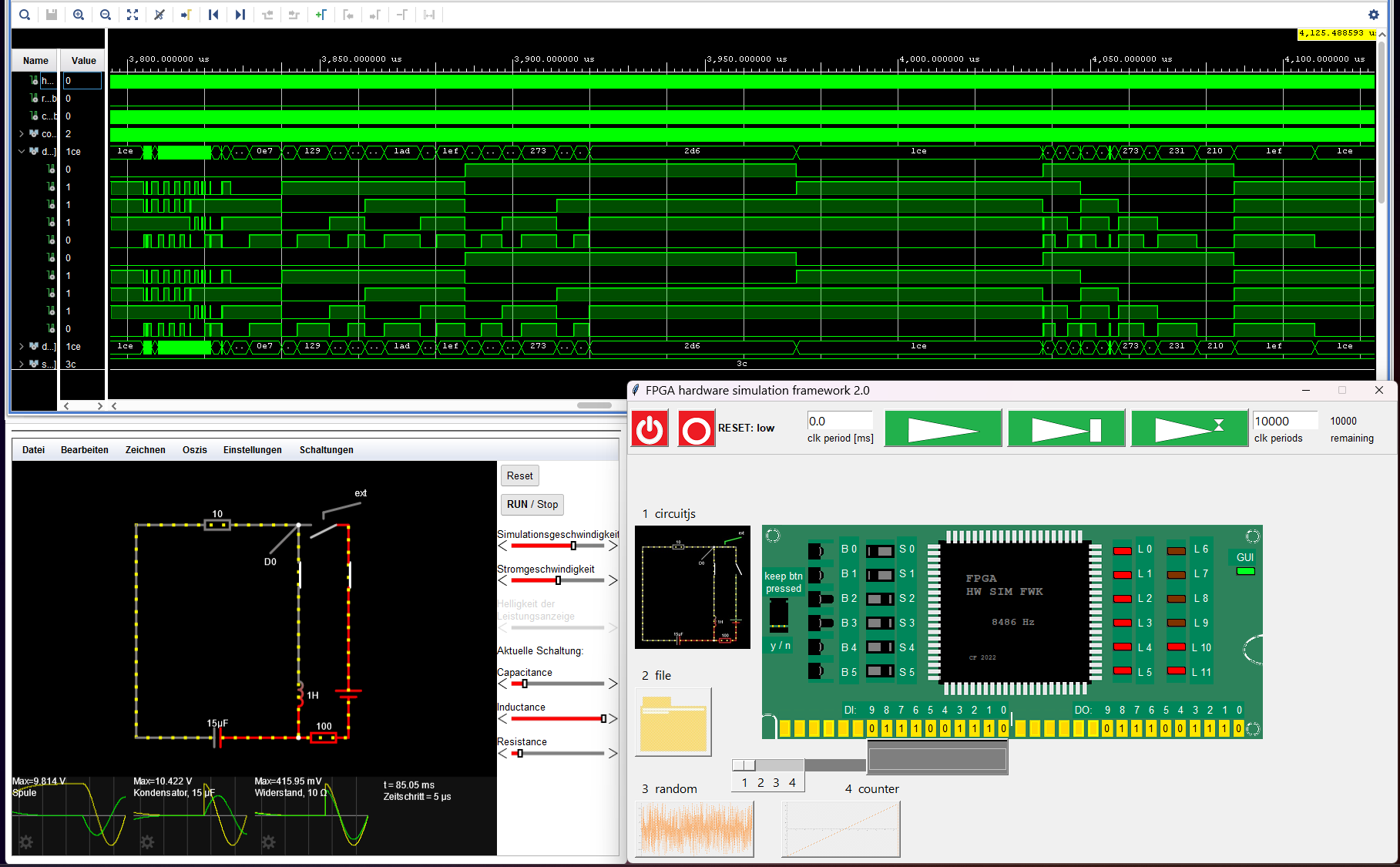

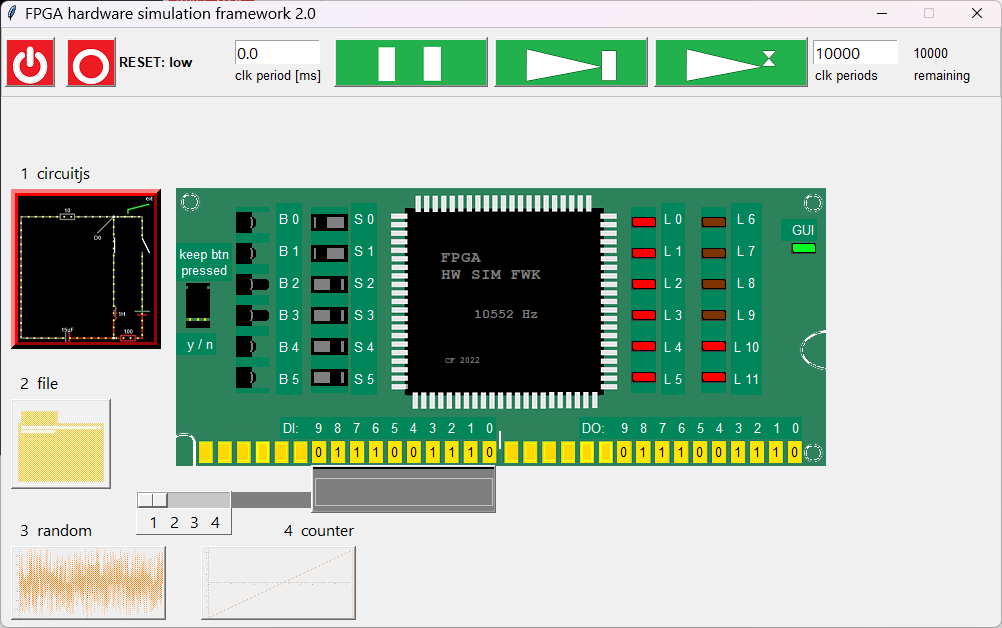

- GUI

- concurrent input / output (up to 40kHz!)

- interactive experience with emulated HW

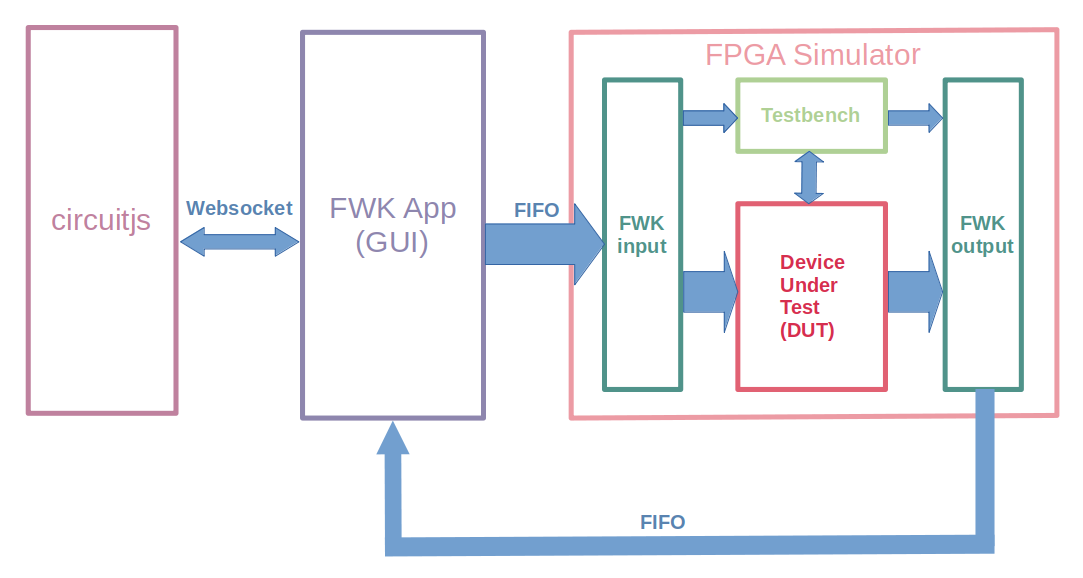

- communication interface between App and VHDL-Simulator based on named pipes (FIFOs)

- communication interface between App and circuitjs based on websockets

The stimulus and results exchanged between the Simulation App written in Python and the VHDL Simulation Tool (any tool supporting VHDL 2008), are fast enough to produce a realistic and interactive HW behavior. (The rate of data exchanged between Simulation App and circuitjs is also extremely high).

The current project is an improvement of an earlier project which has been optimized for performance, achieving simulation rates of up to 40kHz!

In order to support simulation of "asynchronous" signals, the current rate of the simulation clock is reduced to approx. 10kHz. But the overall simulation rate continues to be 40kHz because signals are exchanged in 4 different clock phases within each clock period.