WO2024180432A1 - Semiconductor device and method for producing semiconductor device - Google Patents

Semiconductor device and method for producing semiconductor device Download PDFInfo

- Publication number

- WO2024180432A1 WO2024180432A1 PCT/IB2024/051695 IB2024051695W WO2024180432A1 WO 2024180432 A1 WO2024180432 A1 WO 2024180432A1 IB 2024051695 W IB2024051695 W IB 2024051695W WO 2024180432 A1 WO2024180432 A1 WO 2024180432A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- transistor

- layer

- insulating layer

- opening

- semiconductor

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 607

- 238000004519 manufacturing process Methods 0.000 title claims description 82

- 239000003990 capacitor Substances 0.000 claims abstract description 119

- 238000012545 processing Methods 0.000 claims abstract description 99

- 239000000758 substrate Substances 0.000 claims abstract description 80

- 238000000034 method Methods 0.000 claims description 243

- 150000004706 metal oxides Chemical class 0.000 claims description 203

- 229910044991 metal oxide Inorganic materials 0.000 claims description 202

- 238000003860 storage Methods 0.000 claims description 130

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 71

- 229910052710 silicon Inorganic materials 0.000 claims description 71

- 239000010703 silicon Substances 0.000 claims description 71

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 claims description 42

- 229910052735 hafnium Inorganic materials 0.000 claims description 41

- 229910052782 aluminium Inorganic materials 0.000 claims description 29

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 claims description 29

- 150000004767 nitrides Chemical class 0.000 claims description 26

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 24

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 24

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 claims description 22

- 229910000449 hafnium oxide Inorganic materials 0.000 claims description 16

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 claims description 16

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 claims description 16

- 229910001928 zirconium oxide Inorganic materials 0.000 claims description 16

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 14

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 14

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 claims description 11

- 229910001195 gallium oxide Inorganic materials 0.000 claims description 11

- KQHQLIAOAVMAOW-UHFFFAOYSA-N hafnium(4+) oxygen(2-) zirconium(4+) Chemical compound [O--].[O--].[O--].[O--].[Zr+4].[Hf+4] KQHQLIAOAVMAOW-UHFFFAOYSA-N 0.000 claims description 7

- 229910052454 barium strontium titanate Inorganic materials 0.000 claims description 6

- 229910052797 bismuth Inorganic materials 0.000 claims description 6

- JCXGWMGPZLAOME-UHFFFAOYSA-N bismuth atom Chemical compound [Bi] JCXGWMGPZLAOME-UHFFFAOYSA-N 0.000 claims description 6

- 229910052451 lead zirconate titanate Inorganic materials 0.000 claims description 6

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 claims description 6

- 229910001936 tantalum oxide Inorganic materials 0.000 claims description 6

- 239000004952 Polyamide Substances 0.000 claims description 5

- 239000004642 Polyimide Substances 0.000 claims description 5

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 claims description 5

- JRPBQTZRNDNNOP-UHFFFAOYSA-N barium titanate Chemical compound [Ba+2].[Ba+2].[O-][Ti]([O-])([O-])[O-] JRPBQTZRNDNNOP-UHFFFAOYSA-N 0.000 claims description 5

- 229910002113 barium titanate Inorganic materials 0.000 claims description 5

- NKZSPGSOXYXWQA-UHFFFAOYSA-N dioxido(oxo)titanium;lead(2+) Chemical compound [Pb+2].[O-][Ti]([O-])=O NKZSPGSOXYXWQA-UHFFFAOYSA-N 0.000 claims description 5

- HFGPZNIAWCZYJU-UHFFFAOYSA-N lead zirconate titanate Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ti+4].[Zr+4].[Pb+2] HFGPZNIAWCZYJU-UHFFFAOYSA-N 0.000 claims description 5

- 229920002647 polyamide Polymers 0.000 claims description 5

- 239000004417 polycarbonate Substances 0.000 claims description 5

- 229920000515 polycarbonate Polymers 0.000 claims description 5

- 229920000728 polyester Polymers 0.000 claims description 5

- 229920001721 polyimide Polymers 0.000 claims description 5

- 229920000098 polyolefin Polymers 0.000 claims description 5

- VEALVRVVWBQVSL-UHFFFAOYSA-N strontium titanate Chemical compound [Sr+2].[O-][Ti]([O-])=O VEALVRVVWBQVSL-UHFFFAOYSA-N 0.000 claims description 5

- 229910000859 α-Fe Inorganic materials 0.000 claims description 5

- IVUXZQJWTQMSQN-UHFFFAOYSA-N distrontium;oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[O-2].[O-2].[Sr+2].[Sr+2].[Ta+5].[Ta+5] IVUXZQJWTQMSQN-UHFFFAOYSA-N 0.000 claims description 4

- 230000006870 function Effects 0.000 abstract description 173

- 239000010410 layer Substances 0.000 description 1450

- 230000015654 memory Effects 0.000 description 328

- 239000010408 film Substances 0.000 description 239

- 210000004027 cell Anatomy 0.000 description 142

- 230000015572 biosynthetic process Effects 0.000 description 104

- 239000000463 material Substances 0.000 description 97

- 229910052760 oxygen Inorganic materials 0.000 description 94

- 239000001301 oxygen Substances 0.000 description 93

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 91

- 239000004020 conductor Substances 0.000 description 69

- 229910052751 metal Inorganic materials 0.000 description 61

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 60

- 239000012535 impurity Substances 0.000 description 58

- 239000012212 insulator Substances 0.000 description 56

- 238000000231 atomic layer deposition Methods 0.000 description 50

- 239000001257 hydrogen Substances 0.000 description 50

- 229910052739 hydrogen Inorganic materials 0.000 description 50

- 125000004429 atom Chemical group 0.000 description 48

- 230000008569 process Effects 0.000 description 45

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 43

- 238000010586 diagram Methods 0.000 description 43

- 239000013078 crystal Substances 0.000 description 42

- 239000002184 metal Substances 0.000 description 39

- 239000007789 gas Substances 0.000 description 38

- 238000010438 heat treatment Methods 0.000 description 37

- 238000005229 chemical vapour deposition Methods 0.000 description 35

- 238000004544 sputter deposition Methods 0.000 description 35

- 229910052757 nitrogen Inorganic materials 0.000 description 28

- 230000007547 defect Effects 0.000 description 25

- 230000005621 ferroelectricity Effects 0.000 description 23

- 239000000203 mixture Substances 0.000 description 23

- 238000001312 dry etching Methods 0.000 description 19

- 230000000694 effects Effects 0.000 description 19

- 239000002356 single layer Substances 0.000 description 19

- 239000011701 zinc Substances 0.000 description 19

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 18

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 17

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 17

- 238000005530 etching Methods 0.000 description 17

- 229910052738 indium Inorganic materials 0.000 description 17

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 17

- 229910052721 tungsten Inorganic materials 0.000 description 17

- 239000010937 tungsten Substances 0.000 description 17

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 16

- 229910052733 gallium Inorganic materials 0.000 description 16

- 239000011229 interlayer Substances 0.000 description 16

- -1 silicon Chemical class 0.000 description 15

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 14

- 229910052799 carbon Inorganic materials 0.000 description 14

- 238000000151 deposition Methods 0.000 description 14

- 238000009792 diffusion process Methods 0.000 description 14

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 14

- 230000004888 barrier function Effects 0.000 description 13

- 239000000969 carrier Substances 0.000 description 13

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 12

- 229910052746 lanthanum Inorganic materials 0.000 description 12

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 12

- 230000002093 peripheral effect Effects 0.000 description 12

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 11

- 239000011810 insulating material Substances 0.000 description 11

- 230000003071 parasitic effect Effects 0.000 description 11

- 230000000630 rising effect Effects 0.000 description 11

- 239000000126 substance Substances 0.000 description 11

- 229910052796 boron Inorganic materials 0.000 description 10

- 238000001451 molecular beam epitaxy Methods 0.000 description 10

- 229910052726 zirconium Inorganic materials 0.000 description 10

- 238000003491 array Methods 0.000 description 9

- 230000008859 change Effects 0.000 description 9

- 150000002431 hydrogen Chemical class 0.000 description 9

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 9

- 229910052727 yttrium Inorganic materials 0.000 description 9

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 9

- 239000011787 zinc oxide Substances 0.000 description 9

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 8

- 238000001459 lithography Methods 0.000 description 8

- 230000000737 periodic effect Effects 0.000 description 8

- 229910052698 phosphorus Inorganic materials 0.000 description 8

- 230000005855 radiation Effects 0.000 description 8

- 239000002994 raw material Substances 0.000 description 8

- 229910052712 strontium Inorganic materials 0.000 description 8

- CIOAGBVUUVVLOB-UHFFFAOYSA-N strontium atom Chemical compound [Sr] CIOAGBVUUVVLOB-UHFFFAOYSA-N 0.000 description 8

- 229910052715 tantalum Inorganic materials 0.000 description 8

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 8

- 239000010936 titanium Substances 0.000 description 8

- 238000001039 wet etching Methods 0.000 description 8

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 7

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 7

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 7

- 238000004833 X-ray photoelectron spectroscopy Methods 0.000 description 7

- 239000010949 copper Substances 0.000 description 7

- 230000005684 electric field Effects 0.000 description 7

- 230000010354 integration Effects 0.000 description 7

- 239000011574 phosphorus Substances 0.000 description 7

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 7

- 239000002243 precursor Substances 0.000 description 7

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 7

- 229910052719 titanium Inorganic materials 0.000 description 7

- 238000011282 treatment Methods 0.000 description 7

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 6

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 6

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 6

- 229910045601 alloy Inorganic materials 0.000 description 6

- 239000000956 alloy Substances 0.000 description 6

- 238000004458 analytical method Methods 0.000 description 6

- 229910052801 chlorine Inorganic materials 0.000 description 6

- 239000000460 chlorine Substances 0.000 description 6

- 150000001875 compounds Chemical class 0.000 description 6

- 230000004044 response Effects 0.000 description 6

- 229910052707 ruthenium Inorganic materials 0.000 description 6

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 6

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 6

- VUFNLQXQSDUXKB-DOFZRALJSA-N 2-[4-[4-[bis(2-chloroethyl)amino]phenyl]butanoyloxy]ethyl (5z,8z,11z,14z)-icosa-5,8,11,14-tetraenoate Chemical group CCCCC\C=C/C\C=C/C\C=C/C\C=C/CCCC(=O)OCCOC(=O)CCCC1=CC=C(N(CCCl)CCCl)C=C1 VUFNLQXQSDUXKB-DOFZRALJSA-N 0.000 description 5

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 5

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 5

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 5

- 229910052779 Neodymium Inorganic materials 0.000 description 5

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 5

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 5

- 229910052802 copper Inorganic materials 0.000 description 5

- 230000008021 deposition Effects 0.000 description 5

- 229910001873 dinitrogen Inorganic materials 0.000 description 5

- 238000005516 engineering process Methods 0.000 description 5

- 230000005669 field effect Effects 0.000 description 5

- 229910003437 indium oxide Inorganic materials 0.000 description 5

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 5

- 230000003993 interaction Effects 0.000 description 5

- 229910052749 magnesium Inorganic materials 0.000 description 5

- 239000011777 magnesium Substances 0.000 description 5

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 5

- 239000000395 magnesium oxide Substances 0.000 description 5

- AXZKOIWUVFPNLO-UHFFFAOYSA-N magnesium;oxygen(2-) Chemical compound [O-2].[Mg+2] AXZKOIWUVFPNLO-UHFFFAOYSA-N 0.000 description 5

- 230000014759 maintenance of location Effects 0.000 description 5

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 5

- 239000010409 thin film Substances 0.000 description 5

- 229910052723 transition metal Inorganic materials 0.000 description 5

- 229910052684 Cerium Inorganic materials 0.000 description 4

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 4

- 101001094647 Homo sapiens Serum paraoxonase/arylesterase 1 Proteins 0.000 description 4

- 101000621061 Homo sapiens Serum paraoxonase/arylesterase 2 Proteins 0.000 description 4

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 4

- 102100035476 Serum paraoxonase/arylesterase 1 Human genes 0.000 description 4

- 102100022824 Serum paraoxonase/arylesterase 2 Human genes 0.000 description 4

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 4

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 4

- 238000004364 calculation method Methods 0.000 description 4

- ZMIGMASIKSOYAM-UHFFFAOYSA-N cerium Chemical compound [Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce] ZMIGMASIKSOYAM-UHFFFAOYSA-N 0.000 description 4

- 150000004770 chalcogenides Chemical class 0.000 description 4

- 229910001882 dioxygen Inorganic materials 0.000 description 4

- 230000002349 favourable effect Effects 0.000 description 4

- 238000007667 floating Methods 0.000 description 4

- 229910052731 fluorine Inorganic materials 0.000 description 4

- 239000011737 fluorine Substances 0.000 description 4

- 229910052732 germanium Inorganic materials 0.000 description 4

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 4

- 239000011159 matrix material Substances 0.000 description 4

- 229910052750 molybdenum Inorganic materials 0.000 description 4

- 239000011733 molybdenum Substances 0.000 description 4

- 229910052759 nickel Inorganic materials 0.000 description 4

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 4

- 229910021334 nickel silicide Inorganic materials 0.000 description 4

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 4

- 125000004430 oxygen atom Chemical group O* 0.000 description 4

- 239000011295 pitch Substances 0.000 description 4

- 238000004549 pulsed laser deposition Methods 0.000 description 4

- 239000000376 reactant Substances 0.000 description 4

- 229920005989 resin Polymers 0.000 description 4

- 239000011347 resin Substances 0.000 description 4

- 229910021332 silicide Inorganic materials 0.000 description 4

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 4

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 4

- 229910001930 tungsten oxide Inorganic materials 0.000 description 4

- 229910052725 zinc Inorganic materials 0.000 description 4

- 229910018137 Al-Zn Inorganic materials 0.000 description 3

- 229910018573 Al—Zn Inorganic materials 0.000 description 3

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 3

- 229910052693 Europium Inorganic materials 0.000 description 3

- MWUXSHHQAYIFBG-UHFFFAOYSA-N Nitric oxide Chemical compound O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 3

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 3

- 229910052783 alkali metal Inorganic materials 0.000 description 3

- 150000001340 alkali metals Chemical class 0.000 description 3

- 150000001342 alkaline earth metals Chemical class 0.000 description 3

- 229910052786 argon Inorganic materials 0.000 description 3

- 230000005540 biological transmission Effects 0.000 description 3

- 229910002092 carbon dioxide Inorganic materials 0.000 description 3

- 238000006243 chemical reaction Methods 0.000 description 3

- 229910052804 chromium Inorganic materials 0.000 description 3

- 239000011651 chromium Substances 0.000 description 3

- 239000000470 constituent Substances 0.000 description 3

- OGPBJKLSAFTDLK-UHFFFAOYSA-N europium atom Chemical compound [Eu] OGPBJKLSAFTDLK-UHFFFAOYSA-N 0.000 description 3

- YZZNJYQZJKSEER-UHFFFAOYSA-N gallium tin Chemical compound [Ga].[Sn] YZZNJYQZJKSEER-UHFFFAOYSA-N 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 3

- 239000011261 inert gas Substances 0.000 description 3

- XEEYBQQBJWHFJM-UHFFFAOYSA-N iron Substances [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 3

- 230000007774 longterm Effects 0.000 description 3

- 239000002245 particle Substances 0.000 description 3

- 238000009832 plasma treatment Methods 0.000 description 3

- 229910001925 ruthenium oxide Inorganic materials 0.000 description 3

- WOCIAKWEIIZHES-UHFFFAOYSA-N ruthenium(iv) oxide Chemical compound O=[Ru]=O WOCIAKWEIIZHES-UHFFFAOYSA-N 0.000 description 3

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 3

- 238000005477 sputtering target Methods 0.000 description 3

- 229910052714 tellurium Inorganic materials 0.000 description 3

- PORWMNRCUJJQNO-UHFFFAOYSA-N tellurium atom Chemical compound [Te] PORWMNRCUJJQNO-UHFFFAOYSA-N 0.000 description 3

- 229910052718 tin Inorganic materials 0.000 description 3

- 229910052720 vanadium Inorganic materials 0.000 description 3

- GPPXJZIENCGNKB-UHFFFAOYSA-N vanadium Chemical compound [V]#[V] GPPXJZIENCGNKB-UHFFFAOYSA-N 0.000 description 3

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 2

- 229910052582 BN Inorganic materials 0.000 description 2

- PZNSFCLAULLKQX-UHFFFAOYSA-N Boron nitride Chemical compound N#B PZNSFCLAULLKQX-UHFFFAOYSA-N 0.000 description 2

- WKBOTKDWSSQWDR-UHFFFAOYSA-N Bromine atom Chemical compound [Br] WKBOTKDWSSQWDR-UHFFFAOYSA-N 0.000 description 2

- OYPRJOBELJOOCE-UHFFFAOYSA-N Calcium Chemical compound [Ca] OYPRJOBELJOOCE-UHFFFAOYSA-N 0.000 description 2

- 229910052688 Gadolinium Inorganic materials 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 2

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 2

- 229910052777 Praseodymium Inorganic materials 0.000 description 2

- 229910052773 Promethium Inorganic materials 0.000 description 2

- 229910052772 Samarium Inorganic materials 0.000 description 2

- BUGBHKTXTAQXES-UHFFFAOYSA-N Selenium Chemical compound [Se] BUGBHKTXTAQXES-UHFFFAOYSA-N 0.000 description 2

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 2

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 2

- 229910020994 Sn-Zn Inorganic materials 0.000 description 2

- 229910009069 Sn—Zn Inorganic materials 0.000 description 2

- NINIDFKCEFEMDL-UHFFFAOYSA-N Sulfur Chemical compound [S] NINIDFKCEFEMDL-UHFFFAOYSA-N 0.000 description 2

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 2

- 241000724291 Tobacco streak virus Species 0.000 description 2

- DBKNIEBLJMAJHX-UHFFFAOYSA-N [As]#B Chemical compound [As]#B DBKNIEBLJMAJHX-UHFFFAOYSA-N 0.000 description 2

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 2

- 229910052787 antimony Inorganic materials 0.000 description 2

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 description 2

- 229910052788 barium Inorganic materials 0.000 description 2

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- ILAHWRKJUDSMFH-UHFFFAOYSA-N boron tribromide Chemical compound BrB(Br)Br ILAHWRKJUDSMFH-UHFFFAOYSA-N 0.000 description 2

- GDTBXPJZTBHREO-UHFFFAOYSA-N bromine Substances BrBr GDTBXPJZTBHREO-UHFFFAOYSA-N 0.000 description 2

- 229910052794 bromium Inorganic materials 0.000 description 2

- 229910052793 cadmium Inorganic materials 0.000 description 2

- BDOSMKKIYDKNTQ-UHFFFAOYSA-N cadmium atom Chemical compound [Cd] BDOSMKKIYDKNTQ-UHFFFAOYSA-N 0.000 description 2

- 229910052791 calcium Inorganic materials 0.000 description 2

- 239000011575 calcium Substances 0.000 description 2

- 239000001569 carbon dioxide Substances 0.000 description 2

- 229910052800 carbon group element Inorganic materials 0.000 description 2

- 230000015556 catabolic process Effects 0.000 description 2

- 239000000919 ceramic Substances 0.000 description 2

- 229910052798 chalcogen Inorganic materials 0.000 description 2

- 150000001787 chalcogens Chemical class 0.000 description 2

- 239000002131 composite material Substances 0.000 description 2

- 238000001816 cooling Methods 0.000 description 2

- JAONJTDQXUSBGG-UHFFFAOYSA-N dialuminum;dizinc;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Al+3].[Al+3].[Zn+2].[Zn+2] JAONJTDQXUSBGG-UHFFFAOYSA-N 0.000 description 2

- 238000010894 electron beam technology Methods 0.000 description 2

- 238000002003 electron diffraction Methods 0.000 description 2

- 238000002149 energy-dispersive X-ray emission spectroscopy Methods 0.000 description 2

- 238000000605 extraction Methods 0.000 description 2

- UIWYJDYFSGRHKR-UHFFFAOYSA-N gadolinium atom Chemical compound [Gd] UIWYJDYFSGRHKR-UHFFFAOYSA-N 0.000 description 2

- 230000020169 heat generation Effects 0.000 description 2

- 238000001095 inductively coupled plasma mass spectrometry Methods 0.000 description 2

- 238000002354 inductively-coupled plasma atomic emission spectroscopy Methods 0.000 description 2

- 238000010884 ion-beam technique Methods 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- MRELNEQAGSRDBK-UHFFFAOYSA-N lanthanum(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[La+3].[La+3] MRELNEQAGSRDBK-UHFFFAOYSA-N 0.000 description 2

- 239000007788 liquid Substances 0.000 description 2

- WPBNNNQJVZRUHP-UHFFFAOYSA-L manganese(2+);methyl n-[[2-(methoxycarbonylcarbamothioylamino)phenyl]carbamothioyl]carbamate;n-[2-(sulfidocarbothioylamino)ethyl]carbamodithioate Chemical compound [Mn+2].[S-]C(=S)NCCNC([S-])=S.COC(=O)NC(=S)NC1=CC=CC=C1NC(=S)NC(=O)OC WPBNNNQJVZRUHP-UHFFFAOYSA-L 0.000 description 2

- 229910052752 metalloid Inorganic materials 0.000 description 2

- PLDDOISOJJCEMH-UHFFFAOYSA-N neodymium(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Nd+3].[Nd+3] PLDDOISOJJCEMH-UHFFFAOYSA-N 0.000 description 2

- 229910052758 niobium Inorganic materials 0.000 description 2

- 239000010955 niobium Substances 0.000 description 2

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 2

- 125000004433 nitrogen atom Chemical group N* 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 230000001590 oxidative effect Effects 0.000 description 2

- 239000012466 permeate Substances 0.000 description 2

- 238000000206 photolithography Methods 0.000 description 2

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 2

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 2

- PUDIUYLPXJFUGB-UHFFFAOYSA-N praseodymium atom Chemical compound [Pr] PUDIUYLPXJFUGB-UHFFFAOYSA-N 0.000 description 2

- VQMWBBYLQSCNPO-UHFFFAOYSA-N promethium atom Chemical compound [Pm] VQMWBBYLQSCNPO-UHFFFAOYSA-N 0.000 description 2

- 238000001552 radio frequency sputter deposition Methods 0.000 description 2

- KZUNJOHGWZRPMI-UHFFFAOYSA-N samarium atom Chemical compound [Sm] KZUNJOHGWZRPMI-UHFFFAOYSA-N 0.000 description 2

- 239000000523 sample Substances 0.000 description 2

- 229910052706 scandium Inorganic materials 0.000 description 2

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 2

- 229910052711 selenium Inorganic materials 0.000 description 2

- 239000011669 selenium Substances 0.000 description 2

- 229910010271 silicon carbide Inorganic materials 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 239000004332 silver Substances 0.000 description 2

- 229910000679 solder Inorganic materials 0.000 description 2

- 238000005476 soldering Methods 0.000 description 2

- 239000011593 sulfur Substances 0.000 description 2

- 229910052717 sulfur Inorganic materials 0.000 description 2

- 230000003746 surface roughness Effects 0.000 description 2

- 238000012360 testing method Methods 0.000 description 2

- VZGDMQKNWNREIO-UHFFFAOYSA-N tetrachloromethane Chemical compound ClC(Cl)(Cl)Cl VZGDMQKNWNREIO-UHFFFAOYSA-N 0.000 description 2

- 229910001887 tin oxide Inorganic materials 0.000 description 2

- 238000012546 transfer Methods 0.000 description 2

- SDDGNMXIOGQCCH-UHFFFAOYSA-N 3-fluoro-n,n-dimethylaniline Chemical compound CN(C)C1=CC=CC(F)=C1 SDDGNMXIOGQCCH-UHFFFAOYSA-N 0.000 description 1

- 210000002925 A-like Anatomy 0.000 description 1

- 229910018140 Al-Sn Inorganic materials 0.000 description 1

- 229910018564 Al—Sn Inorganic materials 0.000 description 1

- 229910015845 BBr3 Inorganic materials 0.000 description 1

- 229910015844 BCl3 Inorganic materials 0.000 description 1

- FIPWRIJSWJWJAI-UHFFFAOYSA-N Butyl carbitol 6-propylpiperonyl ether Chemical compound C1=C(CCC)C(COCCOCCOCCCC)=CC2=C1OCO2 FIPWRIJSWJWJAI-UHFFFAOYSA-N 0.000 description 1

- 239000004215 Carbon black (E152) Substances 0.000 description 1

- KZBUYRJDOAKODT-UHFFFAOYSA-N Chlorine Chemical compound ClCl KZBUYRJDOAKODT-UHFFFAOYSA-N 0.000 description 1

- 239000004593 Epoxy Substances 0.000 description 1

- XPDWGBQVDMORPB-UHFFFAOYSA-N Fluoroform Chemical compound FC(F)F XPDWGBQVDMORPB-UHFFFAOYSA-N 0.000 description 1

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 1

- 206010021143 Hypoxia Diseases 0.000 description 1

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- 229910016001 MoSe Inorganic materials 0.000 description 1

- 239000004677 Nylon Substances 0.000 description 1

- BPQQTUXANYXVAA-UHFFFAOYSA-N Orthosilicate Chemical compound [O-][Si]([O-])([O-])[O-] BPQQTUXANYXVAA-UHFFFAOYSA-N 0.000 description 1

- 229910003910 SiCl4 Inorganic materials 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- 238000005411 Van der Waals force Methods 0.000 description 1

- 238000002441 X-ray diffraction Methods 0.000 description 1

- DZLPZFLXRVRDAE-UHFFFAOYSA-N [O--].[O--].[O--].[O--].[Al+3].[Zn++].[In+3] Chemical compound [O--].[O--].[O--].[O--].[Al+3].[Zn++].[In+3] DZLPZFLXRVRDAE-UHFFFAOYSA-N 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 150000001450 anions Chemical class 0.000 description 1

- 239000004760 aramid Substances 0.000 description 1

- 229920003235 aromatic polyamide Polymers 0.000 description 1

- 238000013473 artificial intelligence Methods 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- 229910052790 beryllium Inorganic materials 0.000 description 1

- ATBAMAFKBVZNFJ-UHFFFAOYSA-N beryllium atom Chemical compound [Be] ATBAMAFKBVZNFJ-UHFFFAOYSA-N 0.000 description 1

- LNMGXZOOXVAITI-UHFFFAOYSA-N bis(selanylidene)hafnium Chemical compound [Se]=[Hf]=[Se] LNMGXZOOXVAITI-UHFFFAOYSA-N 0.000 description 1

- WVMYSOZCZHQCSG-UHFFFAOYSA-N bis(sulfanylidene)zirconium Chemical compound S=[Zr]=S WVMYSOZCZHQCSG-UHFFFAOYSA-N 0.000 description 1

- 229910052795 boron group element Inorganic materials 0.000 description 1

- 239000002775 capsule Substances 0.000 description 1

- 125000004432 carbon atom Chemical group C* 0.000 description 1

- 229910002090 carbon oxide Inorganic materials 0.000 description 1

- 150000001768 cations Chemical class 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 1

- RKTYLMNFRDHKIL-UHFFFAOYSA-N copper;5,10,15,20-tetraphenylporphyrin-22,24-diide Chemical compound [Cu+2].C1=CC(C(=C2C=CC([N-]2)=C(C=2C=CC=CC=2)C=2C=CC(N=2)=C(C=2C=CC=CC=2)C2=CC=C3[N-]2)C=2C=CC=CC=2)=NC1=C3C1=CC=CC=C1 RKTYLMNFRDHKIL-UHFFFAOYSA-N 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000007812 deficiency Effects 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 230000001934 delay Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000018109 developmental process Effects 0.000 description 1

- 238000006073 displacement reaction Methods 0.000 description 1

- 239000003792 electrolyte Substances 0.000 description 1

- 230000005670 electromagnetic radiation Effects 0.000 description 1

- 239000000284 extract Substances 0.000 description 1

- YBMRDBCBODYGJE-UHFFFAOYSA-N germanium oxide Inorganic materials O=[Ge]=O YBMRDBCBODYGJE-UHFFFAOYSA-N 0.000 description 1

- 238000005247 gettering Methods 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 239000010931 gold Substances 0.000 description 1

- 229910021389 graphene Inorganic materials 0.000 description 1

- 229910002804 graphite Inorganic materials 0.000 description 1

- 239000010439 graphite Substances 0.000 description 1

- 239000005431 greenhouse gas Substances 0.000 description 1

- NRJVMVHUISHHQB-UHFFFAOYSA-N hafnium(4+);disulfide Chemical compound [S-2].[S-2].[Hf+4] NRJVMVHUISHHQB-UHFFFAOYSA-N 0.000 description 1

- 229910052736 halogen Inorganic materials 0.000 description 1

- 150000002367 halogens Chemical class 0.000 description 1

- 230000012447 hatching Effects 0.000 description 1

- 239000001307 helium Substances 0.000 description 1

- 229910052734 helium Inorganic materials 0.000 description 1

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 1

- 125000005842 heteroatom Chemical group 0.000 description 1

- 229930195733 hydrocarbon Natural products 0.000 description 1

- 150000002430 hydrocarbons Chemical class 0.000 description 1

- 238000007654 immersion Methods 0.000 description 1

- BDVZHDCXCXJPSO-UHFFFAOYSA-N indium(3+) oxygen(2-) titanium(4+) Chemical compound [O-2].[Ti+4].[In+3] BDVZHDCXCXJPSO-UHFFFAOYSA-N 0.000 description 1

- 238000009616 inductively coupled plasma Methods 0.000 description 1

- 229910052741 iridium Inorganic materials 0.000 description 1

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- 239000005435 mesosphere Substances 0.000 description 1

- 150000001247 metal acetylides Chemical class 0.000 description 1

- 150000002736 metal compounds Chemical class 0.000 description 1

- 238000002488 metal-organic chemical vapour deposition Methods 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 229910021424 microcrystalline silicon Inorganic materials 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- MHWZQNGIEIYAQJ-UHFFFAOYSA-N molybdenum diselenide Chemical compound [Se]=[Mo]=[Se] MHWZQNGIEIYAQJ-UHFFFAOYSA-N 0.000 description 1

- CWQXQMHSOZUFJS-UHFFFAOYSA-N molybdenum disulfide Chemical compound S=[Mo]=S CWQXQMHSOZUFJS-UHFFFAOYSA-N 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 230000001537 neural effect Effects 0.000 description 1

- 229920001778 nylon Polymers 0.000 description 1

- 230000001151 other effect Effects 0.000 description 1

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 1

- PVADDRMAFCOOPC-UHFFFAOYSA-N oxogermanium Chemical compound [Ge]=O PVADDRMAFCOOPC-UHFFFAOYSA-N 0.000 description 1

- 230000035699 permeability Effects 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 238000001020 plasma etching Methods 0.000 description 1

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 1

- 239000004033 plastic Substances 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229910052696 pnictogen Inorganic materials 0.000 description 1

- 230000010287 polarization Effects 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 229910052699 polonium Inorganic materials 0.000 description 1

- HZEBHPIOVYHPMT-UHFFFAOYSA-N polonium atom Chemical compound [Po] HZEBHPIOVYHPMT-UHFFFAOYSA-N 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 238000011002 quantification Methods 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 229910052761 rare earth metal Inorganic materials 0.000 description 1

- 238000005546 reactive sputtering Methods 0.000 description 1

- 230000008707 rearrangement Effects 0.000 description 1

- 238000011084 recovery Methods 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- HVEIXSLGUCQTMP-UHFFFAOYSA-N selenium(2-);zirconium(4+) Chemical compound [Se-2].[Se-2].[Zr+4] HVEIXSLGUCQTMP-UHFFFAOYSA-N 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- 229910021428 silicene Inorganic materials 0.000 description 1

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical class [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 1

- FDNAPBUWERUEDA-UHFFFAOYSA-N silicon tetrachloride Chemical compound Cl[Si](Cl)(Cl)Cl FDNAPBUWERUEDA-UHFFFAOYSA-N 0.000 description 1

- 229910052708 sodium Inorganic materials 0.000 description 1

- 239000011734 sodium Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 229910002076 stabilized zirconia Inorganic materials 0.000 description 1

- 239000005437 stratosphere Substances 0.000 description 1

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 1

- 239000005439 thermosphere Substances 0.000 description 1

- 150000003624 transition metals Chemical class 0.000 description 1

- FAQYAMRNWDIXMY-UHFFFAOYSA-N trichloroborane Chemical compound ClB(Cl)Cl FAQYAMRNWDIXMY-UHFFFAOYSA-N 0.000 description 1

- ITRNXVSDJBHYNJ-UHFFFAOYSA-N tungsten disulfide Chemical compound S=[W]=S ITRNXVSDJBHYNJ-UHFFFAOYSA-N 0.000 description 1

- 238000010792 warming Methods 0.000 description 1

- 229910001233 yttria-stabilized zirconia Inorganic materials 0.000 description 1

- TYHJXGDMRRJCRY-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) tin(4+) Chemical compound [O-2].[Zn+2].[Sn+4].[In+3] TYHJXGDMRRJCRY-UHFFFAOYSA-N 0.000 description 1

- OPCPDIFRZGJVCE-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) titanium(4+) Chemical compound [O-2].[Zn+2].[In+3].[Ti+4] OPCPDIFRZGJVCE-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/06—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/08—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind

- H01L27/085—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only

- H01L27/088—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/70—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates the floating gate being an electrode shared by two or more components

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B53/00—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors

- H10B53/20—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors characterised by the three-dimensional arrangements, e.g. with cells on different height levels

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B53/00—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors

- H10B53/30—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors characterised by the memory core region

Definitions

- One aspect of the present invention relates to a semiconductor device. Another aspect of the present invention relates to a memory device and a method for manufacturing the memory device. Another aspect of the present invention relates to a transistor and a method for manufacturing the transistor. Another aspect of the present invention relates to a capacitor and a method for manufacturing the capacitor. Another aspect of the present invention relates to an electronic device.

- one embodiment of the present invention is not limited to the above technical field.

- Examples of technical fields of one embodiment of the present invention include semiconductor devices, display devices, light-emitting devices, power storage devices, memory devices, lighting devices, input devices (e.g., touch sensors), input/output devices (e.g., touch panels), electronic devices having them, driving methods thereof, or manufacturing methods thereof.

- a semiconductor device is a device that utilizes semiconductor characteristics, and refers to a circuit including a semiconductor element (transistor, diode, photodiode, etc.), a device having such a circuit, etc. Also, it refers to any device that can function by utilizing semiconductor characteristics. For example, an integrated circuit, a chip including an integrated circuit, and an electronic component that houses a chip in a package are examples of semiconductor devices. Also, memory devices, display devices, light-emitting devices, lighting devices, and electronic devices may themselves be semiconductor devices and each may have a semiconductor device.

- CPUs central processing units

- memories are used in semiconductor devices.

- a CPU is a collection of semiconductor elements that have semiconductor integrated circuits (at least transistors and memories) that are chipped by processing a semiconductor wafer and on which electrodes that serve as connection terminals are formed.

- IC chips Semiconductor circuits (IC chips) such as CPUs and memories are mounted on circuit boards, such as printed wiring boards, and are used as components in a variety of electronic devices.

- transistors are widely used in electronic devices such as integrated circuits (ICs) and display devices.

- ICs integrated circuits

- Silicon-based semiconductor materials are widely known as semiconductor thin films that can be used in transistors, but oxide semiconductors are also attracting attention as other materials.

- Patent Document 1 discloses a low-power consumption CPU that utilizes the property of low leakage current of transistors using oxide semiconductors.

- Patent Document 2 discloses a memory device that can retain stored contents for a long period of time by utilizing the property of low leakage current of transistors using oxide semiconductors.

- Patent Document 3 and Non-Patent Document 1 disclose a technique for increasing the density of integrated circuits by stacking a first transistor using an oxide semiconductor film and a second transistor using an oxide semiconductor film to provide multiple overlapping memory cells.

- Patent Document 4 discloses a vertical transistor in which the side of the oxide semiconductor is covered by a gate electrode via a gate insulating layer.

- One aspect of the present invention has an object to provide a semiconductor device, memory device, or transistor that can be miniaturized or highly integrated. Another aspect of the present invention has an object to provide a highly reliable semiconductor device, memory device, or transistor. Another aspect of the present invention has an object to provide a transistor with a large on-state current. Another aspect of the present invention has an object to provide a transistor, memory device, or semiconductor device with favorable electrical characteristics. Another aspect of the present invention has an object to provide a low-cost semiconductor device or memory device. Another aspect of the present invention has an object to provide a semiconductor device or memory device with low power consumption. Another aspect of the present invention has an object to provide a semiconductor device or memory device with high operating speed. Another aspect of the present invention has an object to provide a novel semiconductor device, memory device, or transistor.

- An object of one embodiment of the present invention is to provide a method for manufacturing a semiconductor device, memory device, or transistor that can be miniaturized or highly integrated.

- An object of one embodiment of the present invention is to provide a method for manufacturing a highly reliable semiconductor device, memory device, or transistor.

- An object of one embodiment of the present invention is to provide a method for manufacturing a transistor with high on-state current.

- An object of one embodiment of the present invention is to provide a method for manufacturing a transistor, memory device, or semiconductor device with favorable electrical characteristics.

- An object of one embodiment of the present invention is to provide a method for manufacturing a semiconductor device or memory device with high yield.

- An object of one embodiment of the present invention is to provide a method for manufacturing a semiconductor device or memory device with low power consumption.

- An object of one embodiment of the present invention is to provide a method for manufacturing a semiconductor device or memory device with high operating speed.

- An object of one embodiment of the present invention is to provide a method for manufacturing a novel semiconductor device, memory device, or transistor

- One aspect of the present invention includes a first transistor, a second transistor, a capacitor, a first insulating layer, and a second insulating layer, the second transistor and the capacitor being provided overlapping the first transistor, the source electrode and the drain electrode of each of the first transistor being located at different heights relative to the substrate surface, the first insulating layer being provided between the source electrode and the drain electrode of the first transistor and having a first opening that reaches one of the source electrode or the drain electrode of the first transistor, and the other of the source electrode or the drain electrode of the first transistor being provided on the first insulating layer.

- the semiconductor layer of the first transistor has a region in contact with one upper surface of the source electrode or drain electrode of the first transistor in the first opening, a side surface of the first insulating layer in the first opening, the other side surface of the source electrode or drain electrode of the first transistor in the first opening, and the other upper surface of the source electrode or drain electrode of the first transistor; the gate insulating layer of the first transistor is provided in contact with the semiconductor layer of the first transistor; and the gate electrode of the first transistor is provided on the gate insulating layer of the first transistor so as to have a region overlapping with the semiconductor layer of the first transistor.

- a second insulating layer is provided between the source electrode and drain electrode of the second transistor and has a second opening reaching the gate electrode of the first transistor, the other of the source electrode or drain electrode of the second transistor is provided on the second insulating layer, and the semiconductor layer of the second transistor is provided on a top surface of the gate electrode of the first transistor in the second opening, a side surface of the second insulating layer in the second opening, and the other of the source electrode or drain electrode of the second transistor in the second opening.

- the gate insulating layer of the second transistor is provided in contact with the semiconductor layer of the second transistor, the gate electrode of the second transistor is provided on the gate insulating layer of the second transistor so as to have a region overlapping with the semiconductor layer of the second transistor, the dielectric layer of the capacitance is provided on the gate electrode of the first transistor, the other electrode of the capacitance has a region overlapping with the gate electrode of the first transistor, and is provided on the dielectric layer of the capacitance with a gap between it and the second opening in a plan view.

- At least one of the semiconductor layer of the first transistor and the semiconductor layer of the second transistor is a transistor having a metal oxide.

- the side surface of the semiconductor layer of the first transistor and the other side surface of the source electrode or drain electrode of the first transistor have a region that is approximately flush with each other, and that the side surface of the semiconductor layer of the second transistor and the other side surface of the source electrode or drain electrode of the second transistor have a region that is approximately flush with each other.

- the end of the other electrode of the capacitor that does not face the first opening is positioned outside the end of the gate electrode of the first transistor.

- the other electrode of the capacitor is provided in two places, on a first side end of the gate electrode of the first transistor and on a second side end opposite the first side end.

- the other electrode of the capacitor has a region that overlaps with the upper surface of the gate electrode of the first transistor so as to surround the second opening.

- the dielectric layer of the capacitor preferably comprises any one of aluminum oxide, gallium oxide, hafnium oxide, tantalum oxide, zirconium oxide, hafnium zirconium oxide, an oxide having aluminum and hafnium, an oxynitride having aluminum and hafnium, an oxide having silicon and hafnium, an oxynitride having silicon and hafnium, and a nitride having silicon and hafnium.

- the dielectric layer of the capacitor preferably contains any of hafnium oxide, zirconium oxide, lead titanate, barium strontium titanate, strontium titanate, lead zirconate titanate, strontium tantalate bismuthate, bismuth ferrite, and barium titanate.

- the first insulating layer and the second insulating layer have any one of silicon oxide, silicon oxynitride, silicon nitride oxide, polyester, polyolefin, polyamide, polyimide, polycarbonate, and acrylic.

- Another aspect of the present invention is to form a first conductive layer, form a first insulating layer and a first conductive film on the first conductive layer, process the first insulating layer and the first conductive film to form a second conductive layer from the first conductive film, form a first opening in the first conductive film and the first insulating layer to reach the first conductive layer, process the second conductive layer to form a third conductive layer, and form an upper surface of the first conductive layer in the first opening, a side surface of the first insulating layer in the first opening, and a side surface of the third conductive layer in the first opening.

- a first metal oxide film is formed in contact with the upper surface of the semiconductor layer and a third conductive layer, the first metal oxide film is processed to form a first semiconductor layer having a region overlapping with the first opening, a second insulating layer is formed in contact with the upper surface of the first semiconductor layer, a second conductive film is formed on the second insulating layer, the second conductive film is processed to form a fourth conductive layer having a region overlapping with the first semiconductor layer, a third insulating layer is formed on the fourth conductive layer and on the second insulating layer, and the third conductive film is formed on the third insulating layer.

- Another aspect of the present invention is to form a first conductive layer, form a first insulating layer and a first conductive film on the first conductive layer, process the first insulating layer and the first conductive film to form a second conductive layer from the first conductive film, form a first opening in the first conductive film and the first insulating layer, reaching the first conductive layer, form a first metal oxide film in contact with an upper surface of the first conductive layer in the first opening, a side surface of the first insulating layer in the first opening, a side surface of the second conductive layer in the first opening, and an upper surface of the second conductive layer, and form a first metal oxide film.

- a second insulating layer is formed on the upper surface of the first semiconductor layer; a second conductive layer is formed on the upper surface of the first semiconductor layer; a second conductive layer is formed on the second insulating layer; a fourth conductive layer is formed on the upper surface of the first semiconductor layer; a third insulating layer is formed on the fourth conductive layer and on the second insulating layer; a third conductive layer is formed on the third insulating layer; a fourth insulating layer and a fourth conductive film are formed on the fifth conductive layer and the third insulating layer, the fourth insulating layer and the fourth conductive film are processed to form a sixth conductive layer from the fourth conductive film, a second opening is formed in the fourth conductive film and the fourth insulating layer, the second opening reaches the fourth conductive layer, and a top surface of the fourth conductive layer in the second opening, a side surface of the third insulating layer in the second opening, a side surface of the fourth insulating layer in the second opening, and a sixth

- This is a method for manufacturing a semiconductor device which includes forming a second metal oxide film in contact with the side surface of the insulating layer and the top surface of the sixth conductive layer, processing the second metal oxide film to form a second semiconductor layer so as to have an area overlapping with the second opening, processing the sixth conductive layer to form a seventh conductive layer so as to have an area overlapping with the second semiconductor layer, forming a fifth insulating layer in contact with the top surface of the second semiconductor layer, forming a fifth conductive layer on the fifth insulating layer, and processing the fifth conductive layer to form an eighth conductive layer so as to have an area overlapping with the second semiconductor layer.

- one aspect of the present invention has a memory unit and a processing unit, the memory unit has a memory device and a sense amplifier, the processing unit has a CPU, MPU, or GPU, the sense amplifier and the processing unit are arranged on a first layer, the memory device is arranged on a second layer, the memory device has a first transistor, a second transistor, a capacitance, a first insulating layer, and a second insulating layer, the second layer is stacked on the first layer, the second transistor and the capacitance are each superimposed on the first transistor, the source electrode and the drain electrode of each of the first transistor and the second transistor are located at different heights with respect to the substrate surface, and the first insulating layer is a source electrode of the first transistor and a drain electrode of the second transistor.

- a first insulating layer provided between the source electrode and the drain electrode of the first transistor and having a first opening reaching one of the source electrode or the drain electrode of the first transistor, the other of the source electrode or the drain electrode of the first transistor being provided on the first insulating layer, the semiconductor layer of the first transistor having a region in contact with an upper surface of one of the source electrode or the drain electrode of the first transistor in the first opening, a side surface of the first insulating layer in the first opening, a side surface of the other of the source electrode or the drain electrode of the first transistor in the first opening, and an upper surface of the other of the source electrode or the drain electrode of the first transistor, the gate insulating layer of the first transistor being provided on and in contact with the semiconductor layer of the first transistor,

- the gate electrode of the first transistor is provided on the gate insulating layer of the first transistor so as to have a region overlapping with the semiconductor layer of the first transistor, and also functions as one of a source electrode or a drain electrode of the second transistor and as one electrode of a capacit

- the second insulating layer is provided between the source electrode and the drain electrode of the second transistor and has a second opening reaching the gate electrode of the first transistor.

- the other of the source electrode or the drain electrode of the second transistor is provided on the second insulating layer.

- the semiconductor layer of the second transistor is provided on an upper surface of the gate electrode of the first transistor in the second opening, a side surface of the second insulating layer in the second opening, and a second opening.

- the semiconductor device has a region in contact with the other side of the source electrode or drain electrode of the second transistor and the other top surface of the source electrode or drain electrode of the second transistor, the gate insulating layer of the second transistor is provided in contact with the semiconductor layer of the second transistor, the gate electrode of the second transistor is provided on the gate insulating layer of the second transistor so as to have a region overlapping with the semiconductor layer of the second transistor, the dielectric layer of the capacitance is provided on the gate electrode of the first transistor, the other electrode of the capacitance has a region overlapping with the gate electrode of the first transistor, and is provided on the dielectric layer of the capacitance with a gap between it and the second opening in a plan view.

- At least one of the semiconductor layer of the first transistor and the semiconductor layer of the second transistor is a transistor having a metal oxide.

- the side surface of the semiconductor layer of the first transistor and the other side surface of the source electrode or drain electrode of the first transistor have a region that is approximately flush with each other, and that the side surface of the semiconductor layer of the second transistor and the other side surface of the source electrode or drain electrode of the second transistor have a region that is approximately flush with each other.

- the end of the other electrode of the capacitor that does not face the first opening is positioned outside the end of the gate electrode of the first transistor.

- the other electrode of the capacitor is provided in two places, on a first side end of the gate electrode of the first transistor and on a second side end opposite the first side end.

- the other electrode of the capacitor has a region that overlaps with the upper surface of the gate electrode of the first transistor so as to surround the second opening.

- the dielectric layer of the capacitor preferably comprises any one of aluminum oxide, gallium oxide, hafnium oxide, tantalum oxide, zirconium oxide, hafnium zirconium oxide, an oxide having aluminum and hafnium, an oxynitride having aluminum and hafnium, an oxide having silicon and hafnium, an oxynitride having silicon and hafnium, and a nitride having silicon and hafnium.

- the dielectric layer of the capacitor contains any one of hafnium oxide, zirconium oxide, lead titanate, barium strontium titanate, strontium titanate, lead zirconate titanate, strontium tantalate bismuthate, bismuth ferrite, or barium titanate.

- the first insulating layer and the second insulating layer have any one of silicon oxide, silicon oxynitride, silicon nitride oxide, polyester, polyolefin, polyamide, polyimide, polycarbonate, and acrylic.

- a semiconductor device, memory device, or transistor that can be miniaturized or highly integrated can be provided.

- a highly reliable semiconductor device, memory device, or transistor can be provided.

- a transistor with a large on-state current can be provided.

- a transistor, memory device, or semiconductor device with favorable electrical characteristics can be provided.

- a low-cost semiconductor device or memory device can be provided.

- a semiconductor device or memory device with low power consumption can be provided.

- a semiconductor device or memory device with high operating speed can be provided.

- a novel semiconductor device, memory device, or transistor can be provided.

- a method for manufacturing a semiconductor device, memory device, or transistor that can be miniaturized or highly integrated.

- a method for manufacturing a highly reliable semiconductor device, memory device, or transistor it is possible to provide a method for manufacturing a transistor with high on-state current.

- a method for manufacturing a transistor, memory device, or semiconductor device with favorable electrical characteristics it is possible to provide a method for manufacturing a semiconductor device or memory device with high yield.

- a method for manufacturing a semiconductor device or memory device with low power consumption.

- a method for manufacturing a semiconductor device or memory device with high operating speed it is possible to provide a method for manufacturing a novel semiconductor device, memory device, or transistor.

- FIG. 1A is a block diagram for explaining an example of the configuration of a computer

- Fig. 1B and Fig. 1C are schematic diagrams for explaining an example of the configuration of a computer.

- FIG. 2 is a schematic diagram illustrating an example of the configuration of a computer.

- FIG. 3 is a circuit diagram illustrating an example of the configuration of a semiconductor device.

- 4A to 4D are circuit diagrams illustrating examples of the configuration of a semiconductor device.

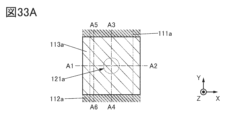

- Fig. 5A is a plan view showing an example of the configuration of a storage device

- Figs. 5B and 5C are cross-sectional views showing an example of the configuration of a storage device.

- FIG. 6 is a cross-sectional view showing an example of the configuration of a storage device.

- FIGS. 9B and 9C are cross-sectional views showing the configuration example of a storage device.

- Fig. 10A is a plan view showing a configuration example of a storage device, and Figs. 10B and 10C are cross-sectional views showing the configuration example of a storage device.

- FIG. 11 is a circuit diagram illustrating an example of the configuration of a semiconductor device.

- FIG. 12 is a timing chart illustrating an example of the operation of the semiconductor device.

- FIG. 13 is a block diagram illustrating an example of the configuration of a storage device.

- 14A and 14B are circuit diagrams illustrating an example of the configuration of a memory device.

- FIG. 15 is a schematic diagram illustrating an example of the configuration of a storage device.

- FIG. 16 is a circuit diagram illustrating a configuration example of a semiconductor device.

- FIG. 17 is a timing chart illustrating an example of the operation of the semiconductor device.

- 18A to 18D are schematic diagrams illustrating an example of the operation of the semiconductor device.

- FIG. 19 is a timing chart illustrating an example of the operation of the semiconductor device.

- 20A to 20G are schematic diagrams illustrating an example of the operation of the semiconductor device.

- 21 is a block diagram illustrating the CPU.