WO2016111142A1 - Washless flux, and method for manufacturing semiconductor package - Google Patents

Washless flux, and method for manufacturing semiconductor package Download PDFInfo

- Publication number

- WO2016111142A1 WO2016111142A1 PCT/JP2015/085518 JP2015085518W WO2016111142A1 WO 2016111142 A1 WO2016111142 A1 WO 2016111142A1 JP 2015085518 W JP2015085518 W JP 2015085518W WO 2016111142 A1 WO2016111142 A1 WO 2016111142A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- solder

- substrate

- flux

- semiconductor chip

- temperature

- Prior art date

Links

Images

Classifications

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B23—MACHINE TOOLS; METAL-WORKING NOT OTHERWISE PROVIDED FOR

- B23K—SOLDERING OR UNSOLDERING; WELDING; CLADDING OR PLATING BY SOLDERING OR WELDING; CUTTING BY APPLYING HEAT LOCALLY, e.g. FLAME CUTTING; WORKING BY LASER BEAM

- B23K1/00—Soldering, e.g. brazing, or unsoldering

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B23—MACHINE TOOLS; METAL-WORKING NOT OTHERWISE PROVIDED FOR

- B23K—SOLDERING OR UNSOLDERING; WELDING; CLADDING OR PLATING BY SOLDERING OR WELDING; CUTTING BY APPLYING HEAT LOCALLY, e.g. FLAME CUTTING; WORKING BY LASER BEAM

- B23K31/00—Processes relevant to this subclass, specially adapted for particular articles or purposes, but not covered by only one of the preceding main groups

- B23K31/02—Processes relevant to this subclass, specially adapted for particular articles or purposes, but not covered by only one of the preceding main groups relating to soldering or welding

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/22—Secondary treatment of printed circuits

- H05K3/28—Applying non-metallic protective coatings

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistor

- H05K3/32—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits

- H05K3/34—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits by soldering

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/91—Methods for connecting semiconductor or solid state bodies including different methods provided for in two or more of groups H01L2224/80 - H01L2224/90

- H01L2224/92—Specific sequence of method steps

- H01L2224/921—Connecting a surface with connectors of different types

- H01L2224/9212—Sequential connecting processes

- H01L2224/92122—Sequential connecting processes the first connecting process involving a bump connector

- H01L2224/92125—Sequential connecting processes the first connecting process involving a bump connector the second connecting process involving a layer connector

Definitions

- the present invention relates to a no-clean flux and a method for manufacturing a semiconductor package.

- a no-clean flux suitable for a soldering method in a package manufacturing method, and a semiconductor package manufacturing method using the no-clean flux.

- flip chip bonding has been used as a semiconductor package mounting method that can cope with higher density and higher frequency of wiring of electronic devices.

- a solder bump formed on a semiconductor chip and a solder-plated wiring formed on a substrate are soldered, and then the gap between the semiconductor chip and the substrate is a material called an underfill material. Seal with.

- solder bumps formed on a semiconductor chip and solder plated wiring formed on a substrate are soldered, cooled to room temperature, and then the gap between the semiconductor chip and the substrate is reduced under Sealed with fill material.

- a good bonding portion appears gray, whereas a bonding defect called white bump that causes the bonding portion to appear white occurs. It is easy.

- This white bump occurs after soldering and before sealing with the underfill material, and it is considered that the stress caused by the difference in thermal expansion between the semiconductor chip and the substrate is promoted by the enlargement of the substrate. .

- Non-Patent Document 1 A manufacturing method for curing a fill material (hereinafter referred to as a manufacturing method using a non-cleaning flux) has been studied (Non-Patent Document 1).

- This manufacturing method using no-cleaning flux has the advantage that the stress caused by the difference in thermal expansion between the semiconductor chip and the substrate can be reduced after soldering, and the manufacturing process is shortened.

- the manufacturing method using the non-cleaning flux since the flux residue cannot be cleaned after soldering, a non-residual flux is required.

- FIG. 1 is a diagram illustrating an example of a manufacturing method using no-clean flux.

- FIG. 1A is an example of a conventional process

- B is an example of a manufacturing method using no-clean flux.

- the major difference between A and B is the temperature after reflow (indicated as “Reflow” in FIG. 1).

- Reflow the temperature after reflow

- A when cooled to room temperature after reflow, white bumps are likely to occur during cooling.

- B the occurrence of white bumps can be suppressed by filling the underfill material at 100 to 120 ° C. (110 ° C. in FIG. 1) without cooling to room temperature after reflow.

- the residue-free flux for soldering includes pimelic acid and the first and second organic solvents, and the second organic solvent has a higher boiling point than the first solvent, and the pimelic acid and the above A flux composition (Patent Document 1) is disclosed in which the second organic solvent is soluble in the first organic solvent.

- a storage-stable gel containing a specific carboxylic acid component, a specific amine component, and a specific solvent (Patent Document 2) is also disclosed.

- this gel is used for soldering a flip chip having a size of 10 mm ⁇ or more, a large amount of residue remains, and the carboxylic acid component is not completely dissolved in the gel and the gel is not smooth. There is.

- the present invention is a non-residue that can be used in a manufacturing method in which, after soldering, after cooling to 100-120 ° C. without cooling to room temperature, filling the underfill material at 100-120 ° C. and then curing the underfill material

- the purpose is to provide flux.

- the present invention relates to a non-cleaning flux and a method for manufacturing a semiconductor package that have solved the above problems by having the following configuration.

- a non-cleaning flux is applied at room temperature between a solder bump formed on a semiconductor chip and a solder plated wiring formed on a substrate. After soldering the solder bump formed on the semiconductor chip and the solder plated wiring formed on the substrate at 240 to 270 ° C., Cool to 100-120 ° C, A non-cleaning flux used in a semiconductor package process in which an underfill material is filled between a semiconductor chip and a substrate while being maintained at 100 to 120 ° C., and the underfill material is cured at 130 to 160 ° C.

- thermogravimetric analysis (A) Solvent whose mass is reduced to 50% when measured at a rate of temperature increase of 10 ° C./min in thermogravimetric analysis, and (B) Temperature increase in thermogravimetric analysis The temperature at which the mass is reduced to 50% when measured at a rate of 10 ° C./min contains a dicarboxylic acid or tricarboxylic acid having a temperature of 190 to 320 ° C., and the component (B) is added to 100 parts by mass of the no-clean flux. And a non-cleaning flux characterized by containing 0.3 to 3.0 parts by mass.

- thermogravimetric analysis contains a tertiary amine having a temperature at which the mass decreases to 50% when measured at a rate of temperature increase of 10 ° C./min, from 130 to 170 ° C .; The non-cleaning flux according to the above [1].

- the non-cleaning flux according to the above [1] wherein the component (B) is an aliphatic dicarboxylic acid.

- the non-cleaning flux according to the above [1] wherein the solder of the solder bump formed on the semiconductor chip is tin-silver based.

- the solder bumps formed on the semiconductor chip and the solder-plated wiring formed on the substrate are heated at a temperature increase rate of 2.5 to 5.0 ° C./second and 30 to 240 to 270 ° C.

- the method for producing a semiconductor package according to [7] above comprising a step of soldering for 70 seconds.

- the temperature decreasing rate is 1.0 to 3.0 ° C./second.

- the method for producing a semiconductor package according to the above [7] comprising a step of cooling to 100 to 120 ° C.

- a manufacturing method in which, after soldering, after cooling to 100 to 120 ° C. without cooling to room temperature, filling the underfill material at 100 to 120 ° C. and then curing the underfill material.

- a usable residue-free flux can be provided.

- the no-clean flux of the present invention is Applying no-clean flux at room temperature between the solder bumps formed on the semiconductor chip and the solder-plated wiring formed on the substrate, After soldering the solder bump formed on the semiconductor chip and the solder plated wiring formed on the substrate at 240 to 270 ° C., Cool to 100-120 ° C, A non-cleaning flux used in a semiconductor package process in which an underfill material is filled between a semiconductor chip and a substrate while being maintained at 100 to 120 ° C., and the underfill material is cured at 130 to 160 ° C.

- thermogravimetric analysis contains a dicarboxylic acid or tricarboxylic acid whose mass decreases to 50% when measured at a rate of temperature increase of 10 ° C / min. It is characterized by containing 0.3 to 3.0 parts by mass with respect to 100 parts by mass of the cleaning flux.

- the present inventor has conducted intensive research on the flux composition and reflow conditions in order to obtain a solder bump, appropriate activation power for solder-plated wiring, volatility, and to obtain a flux with very little flux residue after reflow. And found a residue-free flux suitable for the production method using no-clean flux.

- the appropriate activation force for solder bumps and solder-plated wiring means that the oxide film of the solder bumps and solder-plated wiring can be removed, and no voids are generated and the solder voids are generated. This means that the occurrence of

- the component (A) mainly acts as a solvent in the no-clean flux.

- Component (A) is a solvent having a temperature at which the mass decreases to 50% when measured at a rate of temperature increase of 10 ° C./min by thermogravimetric analysis, at 160 to 210 ° C.

- ethylene glycol monophenyl ether EPH, C 6 H 5 OCH 2 CH 2 OH, T 50 : 181 ° C.

- 2-ethyl-1,3-hexanediol T 50 : 189 ° C.

- 2-ethyl-1,3-hexanediol isobornylhexanol

- Telsolve MTPH manufactured by Nippon Terpene Chemical

- 1 mixed solvent T 50 : 186 ° C.

- ethylene glycol monophenyl ether, 2- A mixed solvent of ethyl-1,3-hexanediol, 2-ethyl-1,3-hexanediol: isobornylhexanol (Telsolve MTPH manufactured by Nippon Terpene Chemical) 1: 1 is preferable.

- the component (A) is a thermogravimetric analysis, a solvent whose temperature is reduced to 50% when measured at a heating rate of 10 ° C./min, and a solvent whose temperature is from 160 to 190 ° C.

- a mixed solvent with a certain solvent for example, isobornyl hexanol (Tg: 234 ° C.)

- Tg: 234 ° C. is preferable from the viewpoint of solder connectivity.

- the mass ratio of the solvent at 160 to 190 ° C. and the solvent mixture at 200 to 240 ° C. is 1: (2 or less) Is preferred, 1: (0.1-2) is more preferred, and 1: (0.5-2) is even more preferred.

- the rate of temperature rise is 10 ° C./min.

- the temperature at which the mass decreases to 50% tends to be higher than 190 ° C. (that is, not easily the component (A)), and the residue tends to remain.

- the component (A) is preferably 95 to 99.7 parts by mass, more preferably 97 to 99.5 parts by mass with respect to 100 parts by mass of the non-cleaning flux.

- the component (B) mainly acts as an activator in the no-clean flux.

- Component (B) is a dicarboxylic acid or tricarboxylic acid having a temperature at which the mass decreases to 50% when measured at a rate of temperature increase of 10 ° C./minute by thermogravimetric analysis at 190 to 320 ° C.

- the component (B) mainly functions as an activator.

- oxalic acid HOOCCOOH, T 50 : 195 ° C.

- succinic acid HOOC (CH 2 ) 2 COOH, T 50 : 230 ° C.

- adipic acid HOOC (CH 2 ) 4 COOH, T 50 : 268 ° C.

- 1,2,4-cyclohexanetricarboxylic acid H-TMA, T 50 : 310 ° C.

- the compounds mentioned as the component (B) are solid, but those that dissolve in the component (A) are preferable from the viewpoint of uniform dispersibility in the non-cleaning flux.

- the component (B) is more preferably an aliphatic dicarboxylic acid.

- the component (B) is contained in an amount of 0.3 to 3.0 parts by mass and preferably 0.5 to 3.0 parts by mass with respect to 100 parts by mass of the non-cleaning flux. If it is less than 0.3 part by mass, the connectivity tends to be poor, and if it exceeds 3.0 parts by mass, the residue tends to remain.

- the non-cleaning flux further contains (C) a tertiary amine having a temperature at which the mass decreases to 50% when measured at a rate of temperature increase of 10 ° C / min in thermogravimetric analysis at 130 to 170 ° C. Then, it is preferable from a viewpoint of the dissolution stability of (B) component, and it is more preferable in it being tributylamine.

- the component (C) is preferably used when the component (B) is difficult to dissolve in the component (A).

- the component (C) mainly acts as an activator.

- the component (C) is preferably 10 times or less, more preferably 5 times or less, and even more preferably 2 times or less with respect to the mass of the component (B). If the component (C) is more than 10 times, the solder connectivity may be deteriorated. Moreover, the (C) component tends to exhibit the effect of addition as it is 0.5 times or more with respect to the mass of (B) component.

- the non-cleaning flux can be further blended with additives and the like as necessary, as long as the object of the present invention is not impaired.

- the no-clean flux is suitable when the solder bump solder formed on the semiconductor chip is tin-silver based. Further, the no-clean flux is suitable when the solder of the solder plated wiring formed on the substrate is a tin-silver-copper system.

- the underfill material preferably contains at least (UA) epoxy resin and (UB) curing agent.

- (UA) component includes bisphenol A type epoxy resin, brominated bisphenol A type epoxy resin, bisphenol F type epoxy resin, naphthalene type epoxy resin, biphenyl type epoxy resin, novolac type epoxy resin, aminophenol type epoxy resin, alicyclic ring Type epoxy resin, ether type or polyether type epoxy resin, oxirane ring-containing epoxy resin, etc., bisphenol F type epoxy resin, aminophenol type epoxy resin, bisphenol A type epoxy resin, naphthalene type epoxy resin are underfill materials From the viewpoint of glass transition point, reflow resistance, and moisture resistance.

- Bisphenol F type epoxy resin is preferably represented by the formula (1):

- n represents an average value, preferably 0 to 6, more preferably 0 to 3.

- the epoxy equivalent is preferably 150 to 900 g / eq.

- the aminophenol-based epoxy resin is preferably a formula (2):

- two functional groups are in the ortho position or the para position.

- the bisphenol A type epoxy resin is preferably represented by the formula (3):

- m represents an average value, and an epoxy resin having 0 to 6 and particularly preferably 0 to 3 is preferable.

- the epoxy equivalent is preferably 170 to 1000 g / eq.

- (UA) component may be used alone or in combination of two or more.

- Examples of the (UB) component include amine-based curing agents, acid anhydride-based curing agents, phenol-based curing agents, and the like, and amine-based curing agents are preferable from the viewpoint of reflow resistance and moisture resistance of the underfill material.

- Amine curing agents include aliphatic polyamines; aromatic amines; modified polyamines such as polyaminoamides, polyaminoimides, polyaminoesters and polyaminoureas; tertiary amines; imidazoles; hydrazides; dicyanamides; An aromatic amine compound is preferable.

- the aromatic amine compound includes an aromatic amine compound having one aromatic ring and / or an aromatic amine compound having two aromatic rings.

- aromatic amine compound having one aromatic ring examples include metaphenylenediamine and the like, and the formula (4) or the formula (5):

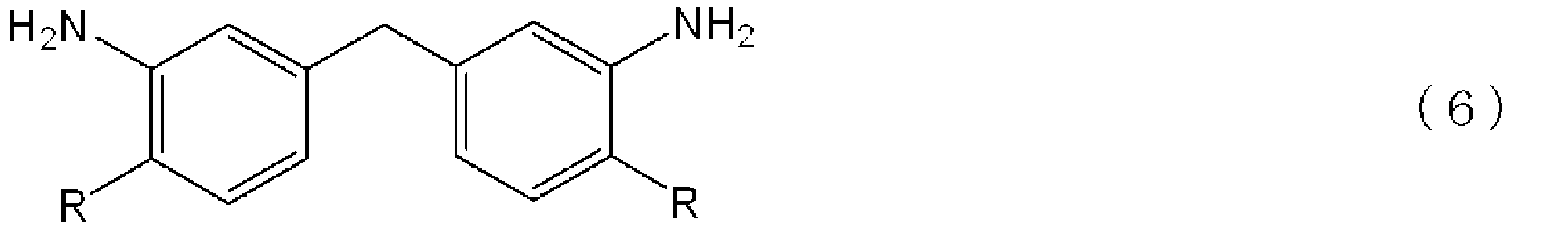

- aromatic amine compound having two aromatic rings examples include diaminodiphenylmethane and diaminodiphenylsulfone, and the formula (6) or the formula (7):

- R represents hydrogen or an alkyl group having 1 to 5 carbon atoms

- R is an alkyl group having 2 carbon atoms. Those are more preferred.

- (UB) component may be used alone or in combination of two or more.

- the underfill material further contains a (UC) filler from the viewpoint of the thermal expansion coefficient of the cured underfill material.

- a (UC) filler examples include silica, alumina, silicon nitride, mica, white carbon, and the like, and silica is preferable from the viewpoints of lowering the thermal expansion coefficient of the underfill material after curing and cost.

- silica various silicas used in this technical field such as amorphous silica, crystalline silica, fused silica, pulverized silica, and nano silica can be used, and the thermal expansion coefficient of the underfill material after curing is reduced. To amorphous silica is preferred.

- the particle size of the component (C) is preferably from 0.1 to 2.0 ⁇ m, more preferably from 0.1 to 1.0 ⁇ m, from the viewpoint of filling into the gap between the semiconductor chip and the substrate.

- the average particle diameter is measured by a laser diffraction particle size distribution measuring apparatus.

- the shape of (C) component is not specifically limited, A spherical shape, flake shape, an indeterminate form, etc. are mentioned, From the viewpoint of the fluidity

- (UC) component may be used alone or in combination of two or more.

- the underfill material contains 20 to 100 parts by mass, more preferably 40 to 60 parts by mass of the component (UB) with respect to 100 parts by mass of the component (UA). And from the viewpoint of moisture resistance.

- the component (UC) is contained in an amount of 160 to 400 parts by mass, more preferably 200 to 350 parts by mass with respect to 100 parts by mass of the component (UA), and the fluidity of the underfill material and the cured underfill material From the viewpoint of lowering the thermal expansion coefficient, it is preferable.

- a pigment such as carbon black, a dye, a silane coupling agent, an antifoaming agent, an antioxidant, other additives, etc.

- a solvent etc. can be mix

- the underfill material can be obtained, for example, by stirring, melting, mixing, and dispersing the (UA) component to the (UC) component and other additives simultaneously or separately, with heat treatment as necessary.

- the mixing, stirring, dispersing and the like devices are not particularly limited, and a raikai machine equipped with a stirring and heating device, a three-roll mill, a ball mill, a planetary mixer, a bead mill and the like can be used. . Moreover, you may use combining these apparatuses suitably.

- the underfill material preferably has a viscosity at a temperature of 25 ° C. of 1 to 100 Pa ⁇ s.

- the viscosity is measured with a viscometer manufactured by Brookfield (model number: DV-1).

- the underfill material is preferably cured at 130 to 160 ° C. for 90 to 150 minutes.

- a method for manufacturing a semiconductor package of the present invention includes a step of applying the above-described non-cleaning flux at room temperature between a solder bump formed on a semiconductor chip and a solder-plated wiring formed on a substrate, Soldering solder bumps formed on the semiconductor chip and solder plated wiring formed on the substrate at 240 to 270 ° C .; A step of cooling to 100 to 120 ° C. and a step of filling the underfill material between the semiconductor chip and the substrate while maintaining the temperature at 100 to 120 ° C. and curing the underfill material at 130 to 160 ° C. in this order are included. .

- FIG. 2 is a view for explaining the method for manufacturing a semiconductor package of the present invention.

- the method for manufacturing a semiconductor package of the present invention uses the above-mentioned non-cleaning flux at room temperature between a solder bump formed on a semiconductor chip and a solder-plated wiring formed on a substrate.

- Applying step A process of soldering solder bumps formed on the semiconductor chip and solder plated wiring formed on the substrate at 240 to 270 ° C. ((1) in FIG. 2); A process of cooling to 100 to 120 ° C. (between (1) and (2) in FIG. 2) and while maintaining the temperature at 100 to 120 ° C. ((2) in FIG. 2) Step of filling the fill material and curing the underfill material at 130 to 160 ° C. ((3) in FIG. 2) Are included in this order.

- the amount of the above-mentioned non-cleaning flux applied between the solder bump formed on the semiconductor chip and the solder-plated wiring formed on the substrate is preferably 0.02 to 0.08 mg / mm 2. 0.04 mg / mm 2 is most preferable.

- the process of cooling to 100 to 120 ° C. is performed at a temperature drop rate of 1.0 to It is preferable that it is 3.0 ° C./second.

- a temperature drop rate of 1.0 to It is preferable that it is 3.0 ° C./second.

- the temperature lowering rate is slower than 1.0 ° C./second, the productivity is deteriorated, and when the temperature lowering rate is higher than 3.0 ° C./second, the yield may be deteriorated.

- the substrate examples include, but are not limited to, epoxy resin, glass-epoxy resin, polyimide resin, and the like.

- the solder of the solder-plated wiring formed on the substrate is preferably a tin-silver-copper system that is a lead-free solder alloy because of environmental problems.

- a solder alloy made of tin, lead, copper, bismuth, silver, zinc, indium, etc. can be used. preferable.

- Examples 1 to 14 Comparative Examples 1 to 4

- mixing was performed using an ultrasonic cleaner to prepare a no-clean flux.

- 2-ethyl-1,3-hexanediol is described as “diol” and isobornylhexanol as “MTPH”.

- the underfill material was prepared as follows.

- Nippon Steel & Sumikin Chemicals bisphenol F type epoxy resin product name: YDF8170: 16.3 parts by mass, Mitsubishi Chemical aminophenol type epoxy resin (product name: EP630): 10.9 parts by mass, Nippon Kayaku amine-based curing agent ( Product name: Kayahard AA): 12.5 parts by mass, Admatex silica filler (Product name: SO-E2, average particle size: 0.5 ⁇ m): 60.0 parts by mass, and Shin-Etsu Chemical silane coupling agent ( Product name: KBM403) was mixed using a three-roll mill to prepare an underfill material.

- a semiconductor package was produced as follows. Chips manufactured by Waltz (product name: WALTS-TEG FC150JY_LF (PI) ⁇ 10 mm) are used for 10 mm ⁇ semiconductor chips, and chips manufactured by Waltz Co., Ltd. (product name: WALTS-TEG FC150JY_LF ( (PI) ⁇ 20 mm), 10 mm ⁇ substrate is made by Waltz Corporation (product name: WALTS-KIT 01A150P-10 (SAC)), and 20 mm ⁇ substrate is made by Waltz Corporation substrate (product name: WALTS). -KIT FC150-0103JY_2 ⁇ 2 (SAC)) was used.

- the substrate was baked in an N 2 atmosphere at 130 ° C. for 2 hours.

- a non-cleaning flux was applied to the mounting portion of the substrate with a brush.

- the semiconductor chip was plasma-treated at 400 W for 5 minutes in an Ar atmosphere at the mounting portion.

- a semiconductor chip was mounted on the substrate.

- a mounting machine (model number: FCB3) manufactured by Panasonic Factory Solutions Co., Ltd. is used, head temperature: 25 ° C., stage temperature: 25 ° C., load: 36.5 N (1 g per bump), load holding time: The test was performed for 5 seconds.

- reflow was performed in an N 2 atmosphere. The reflow was performed in a step of heating up to 260 ° C. at a temperature rising rate of 4.0 ° C./second, soldering at 260 ° C. for 45 seconds, and a step of cooling to 200 ° C. at a temperature falling rate of 2.2 ° C./second.

- FIG. 4 shows ultrasonic microscope (C-SAM) images of 10 mm ⁇ and 20 mm ⁇ chips of Comparative Example 4 produced by a manufacturing method using no-cleaning flux.

- the semiconductor chip was cooled to 110 ° C., kept under 110 ° C., filled with an underfill material between the semiconductor chip and the substrate, and cured at 150 ° C. for 120 minutes. .

- the semiconductor chip was cooled to 110 ° C., kept under 110 ° C., filled with an underfill material between the semiconductor chip and the substrate, and cured at 150 ° C. for 120 minutes.

- FIG. 4 in the case of the 20 mm ⁇ chip, more residue was observed than in the case of the 10 mm ⁇ chip.

- Comparative Example 3 using a dicarboxylic acid methyl ester mixture in place of component (A) has poor connectivity, and Comparative Example 4 has a large amount of residue and stain observed at 10 mm ⁇ , and residue and stain at 20 mm ⁇ . Was observed very often.

- Examples 1, 3 to 6 of a storage-stable gel (Patent Document 2) containing a specific carboxylic acid component, a specific amine component, and a specific solvent were conducted as comparative tests of the present invention (Comparative Examples 5 to 9).

- the raw material which is described as candy etc. and whose specific product name is unknown was not used.

- the total amount may be 97 parts by mass.

- the compounding of Example 2 of the storage-stable gel was similar to Example 1, it was not performed.

- Table 4 shows these results. As can be seen from Table 4, the storage-stable gels containing the specific carboxylic acid component, the specific amine component, and the specific solvent of Comparative Examples 5 to 9 remained as residues.

- Table 5 shows the temperature at which the mass decreases by 1, 50, 99% when the materials used in Examples and Comparative Examples are measured by thermogravimetric analysis at a heating rate of 10 ° C./min. .

- 2-ethyl-1,3-hexanediol is described as “diol”

- isobornylhexanol is described as “MTPH”.

- the no-clean flux of the present invention is residue-free, after soldering, it is not cooled to room temperature, cooled to about 110 ° C., and filled with an underfill material at the same temperature. It is possible to cure the material.

- the no-clean flux of the present invention is residue-free, after soldering, after cooling to about 110 ° C. without cooling to room temperature, the underfill material is filled at the same temperature and then the underfill material is cured. Is possible and very useful.

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Mechanical Engineering (AREA)

- Wire Bonding (AREA)

- Non-Metallic Protective Coatings For Printed Circuits (AREA)

- Electric Connection Of Electric Components To Printed Circuits (AREA)

Abstract

The invention of the present application provides a washless flux comprising (A) a solvent having such a property that the temperature at which the mass thereof is reduced to 50% of the original value is 160 to 210ºC as measured by a thermogravimetric analysis and (B) a di- or tri-carboxylic acid having such a property that the temperature at which the mass thereof is reduced to 50% of the original value is 190 to 320°C as measured by a thermogravimetric analysis, wherein the component (B) is contained in an amount of 0.3 to 3.0 parts by mass relative to 100 parts by mass of the washless flux. The washless flux can be used in a semiconductor packaging process comprising: applying the washless flux between a solder bump, which is formed on a semiconductor chip, and a wiring line, which is formed on a substrate and is coated with a solder, at room temperature; soldering the solder bump with the wiring line; cooling the soldered product to 100 to 120°C; filling an underfill material between the semiconductor chip and the substrate while keeping at the same temperature; and curing the underfill material.

Description

本発明は、無洗浄フラックス、および半導体パッケージの製造方法に関する。特に、半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線をはんだ付けした後、室温まで冷却しないで、100~120℃でアンダーフィル材を充填し、その後、硬化させるパッケージの製造方法でのはんだ付け工法に適した無洗浄フラックス、およびこの無洗浄フラックスを用いる半導体パッケージの製造方法に関する。

The present invention relates to a no-clean flux and a method for manufacturing a semiconductor package. In particular, after solder bumps formed on a semiconductor chip and solder-plated wiring formed on a substrate are soldered, an underfill material is filled at 100 to 120 ° C. without cooling to room temperature, and then cured. The present invention relates to a no-clean flux suitable for a soldering method in a package manufacturing method, and a semiconductor package manufacturing method using the no-clean flux.

近年、電子機器のさらなる配線等の高密度化、高周波化に対応可能な半導体パッケージの実装方式として、フリップチップボンディングが利用されている。一般的に、フリップチップボンディングでは、半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線とをはんだ付けした後、半導体チップと基板の間隙を、アンダーフィル材と呼ばれる材料で封止する。

In recent years, flip chip bonding has been used as a semiconductor package mounting method that can cope with higher density and higher frequency of wiring of electronic devices. In general, in flip chip bonding, a solder bump formed on a semiconductor chip and a solder-plated wiring formed on a substrate are soldered, and then the gap between the semiconductor chip and the substrate is a material called an underfill material. Seal with.

さらなる配線等の高密度化、高周波化に対応するための次世代半導体パッケージでは、はんだバンプや配線の狭ギャップ化に加えて、マルチコア化によるチップの大型化が要求されている。この狭ギャップ化やチップの大型化の際に、はんだ付け時に使用するフラックスの残渣が問題となっている。

In the next generation semiconductor package to cope with higher density and higher frequency of wiring, etc., in addition to narrowing the gaps of solder bumps and wiring, it is required to increase the size of the chip by making it multi-core. When the gap is narrowed or the chip is enlarged, a residue of flux used during soldering becomes a problem.

この狭ギャップ化の場合には、洗浄不良が発生し易いため、フラックス残渣が発生し易くなってしまう。このため、無残渣フラックスが要求されている。

In the case of this narrow gap, since a cleaning defect is likely to occur, a flux residue is likely to be generated. For this reason, a residue-free flux is required.

また、現行の製造工程では、半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線とをはんだ付けした後、室温まで冷却した後、半導体チップと基板の間隙を、アンダーフィル材で封止している。現在、チップを大型化する場合には、はんだバンプ近傍を超音波顕微鏡で観察したとき、良好な接合部が灰色に見えるのに対して、接合部が白く見えるホワイトバンプと呼ばれる接合不良が発生し易くなっている。

Also, in the current manufacturing process, solder bumps formed on a semiconductor chip and solder plated wiring formed on a substrate are soldered, cooled to room temperature, and then the gap between the semiconductor chip and the substrate is reduced under Sealed with fill material. Currently, when increasing the size of a chip, when the vicinity of a solder bump is observed with an ultrasonic microscope, a good bonding portion appears gray, whereas a bonding defect called white bump that causes the bonding portion to appear white occurs. It is easy.

このホワイトバンプは、はんだ付け後、アンダーフィル材で封止する前に発生しており、半導体チップと基板の熱膨張差に起因する応力が、基板の大型化により促進されている、と考えられる。

This white bump occurs after soldering and before sealing with the underfill material, and it is considered that the stress caused by the difference in thermal expansion between the semiconductor chip and the substrate is promoted by the enlargement of the substrate. .

このホワイトバンプの発生を抑制するための方法として、はんだ付け後、室温まで冷却せず、100~120℃まで冷却した後、100~120℃でアンダーフィル材を充填し、130~160℃でアンダーフィル材を硬化させる製造方法(以下、無洗浄フラックスによる製造方法という)が検討されている(非特許文献1)。この無洗浄フラックスによる製造方法により、はんだ付け後に半導体チップと基板の熱膨張差に起因する応力を減少させることができる、製造工程が短くなる、という利点がある。一方、この無洗浄フラックスによる製造方法では、はんだ付け後にフラックス残渣を洗浄することができないので、無残渣フラックスが要求される。図1に、無洗浄フラックスによる製造方法の一例を説明する図を示す。図1のAは、従来のプロセスの例であり、Bは、無洗浄フラックスによる製造方法の一例である。図1からわかるように、AとBの大きな違いは、リフロー(図1に「Reflow」と記載)後の温度である。Aのように、リフロー後に室温まで冷却すると、冷却時にホワイトバンプが発生し易くなってしまう。これに対して、Bのように、リフロー後に室温まで冷却せず、100~120℃(図1では110℃)でアンダーフィル材を充填することにより、ホワイトバンプの発生を抑制することができる。

As a method for suppressing the occurrence of white bumps, after soldering, do not cool to room temperature, cool to 100-120 ° C, fill with underfill material at 100-120 ° C, and undercoat at 130-160 ° C. A manufacturing method for curing a fill material (hereinafter referred to as a manufacturing method using a non-cleaning flux) has been studied (Non-Patent Document 1). This manufacturing method using no-cleaning flux has the advantage that the stress caused by the difference in thermal expansion between the semiconductor chip and the substrate can be reduced after soldering, and the manufacturing process is shortened. On the other hand, in the manufacturing method using the non-cleaning flux, since the flux residue cannot be cleaned after soldering, a non-residual flux is required. FIG. 1 is a diagram illustrating an example of a manufacturing method using no-clean flux. FIG. 1A is an example of a conventional process, and B is an example of a manufacturing method using no-clean flux. As can be seen from FIG. 1, the major difference between A and B is the temperature after reflow (indicated as “Reflow” in FIG. 1). As in A, when cooled to room temperature after reflow, white bumps are likely to occur during cooling. On the other hand, as in B, the occurrence of white bumps can be suppressed by filling the underfill material at 100 to 120 ° C. (110 ° C. in FIG. 1) without cooling to room temperature after reflow.

はんだ付け用の無残渣フラックスとしては、ピメリン酸、ならびに、第1および第2の有機溶剤を含み、上記第2の有機溶剤が上記第1の溶剤より高い沸点を有し、上記ピメリン酸および上記第2の有機溶剤が上記第1の有機溶剤に可溶であることを特徴とするフラックス組成物(特許文献1)が開示されている。

The residue-free flux for soldering includes pimelic acid and the first and second organic solvents, and the second organic solvent has a higher boiling point than the first solvent, and the pimelic acid and the above A flux composition (Patent Document 1) is disclosed in which the second organic solvent is soluble in the first organic solvent.

しかしながら、ピメリン酸を含むフラックス組成物を、無洗浄フラックスによる製造方法に使用すると、はんだ付け後にフラックス残渣が残り、アンダーフィル材が適切に注入できない、という問題がある。現在、室温まで冷却しない方法に使用可能な無残渣フラックスは、市販されていない。

However, when a flux composition containing pimelic acid is used in a production method using no-clean flux, there is a problem that a flux residue remains after soldering and the underfill material cannot be injected properly. Currently, no residue-free flux that can be used in methods that do not cool to room temperature is commercially available.

また、特定のカルボン酸成分、特定のアミン成分、特定の溶剤を含有する貯蔵安定性のゲル(特許文献2)も開示されている。しかしながら、このゲルは、サイズが10mm□以上のフリップチップの半田付けに使用すると、残渣が多く残ってしまう、カルボン酸成分がゲルに完全に溶解しておらず、ゲルが滑らかではない、という問題がある。

Further, a storage-stable gel containing a specific carboxylic acid component, a specific amine component, and a specific solvent (Patent Document 2) is also disclosed. However, when this gel is used for soldering a flip chip having a size of 10 mm □ or more, a large amount of residue remains, and the carboxylic acid component is not completely dissolved in the gel and the gel is not smooth. There is.

本発明は、はんだ付け後、室温まで冷却せず、100~120℃まで冷却した後、100~120℃でアンダーフィル材を充填した後、アンダーフィル材を硬化させる製造方法に使用可能な無残渣フラックスを提供することを目的とする。

The present invention is a non-residue that can be used in a manufacturing method in which, after soldering, after cooling to 100-120 ° C. without cooling to room temperature, filling the underfill material at 100-120 ° C. and then curing the underfill material The purpose is to provide flux.

本発明は、以下の構成を有することによって上記問題を解決した無洗浄フラックス、および半導体パッケージの製造方法に関する。

〔1〕半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線との間に、無洗浄フラックスを室温で塗布し、

半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線とを240~270℃ではんだ付けした後、

100~120℃まで冷却し、

100~120℃に保持したまま、半導体チップと基板との間にアンダーフィル材を充填し、130~160℃でアンダーフィル材を硬化させる

半導体パッケージ工程で使用される無洗浄フラックスであって、

(A)熱重量分析で、昇温速度が10℃/分で測定したときに質量が50%に減少する温度が、160~210℃である溶剤、および

(B)熱重量分析で、昇温速度が10℃/分で測定したときに質量が50%に減少する温度が、190~320℃であるジカルボン酸またはトリカルボン酸

を含有し、(B)成分を、無洗浄フラックス100質量部に対して、0.3~3.0質量部含有することを特徴とする、無洗浄フラックス。

〔2〕さらに、(C)熱重量分析で、昇温速度が10℃/分で測定したときに質量が50%に減少する温度が、130~170℃である第3級アミンを含有する、上記〔1〕記載の無洗浄フラックス。

〔3〕(B)成分が、脂肪族ジカルボン酸である、上記〔1〕記載の無洗浄フラックス。

〔4〕(C)成分が、トリブチルアミンである、上記〔1〕記載の無洗浄フラックス。

〔5〕半導体チップに形成されたはんだバンプのはんだが、錫銀系である、上記〔1〕記載の無洗浄フラックス。

〔6〕基板に形成されたはんだめっきされた配線のはんだが、錫銀銅系である、上記〔1〕記載の無洗浄フラックス。

〔7〕半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線との間に、上記〔1〕記載の無洗浄フラックスを室温で塗布する工程、

半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線とを240~270℃ではんだ付けする工程、

100~120℃まで冷却する工程、および

100~120℃に保持したまま、半導体チップと基板との間にアンダーフィル材を充填し、130~160℃でアンダーフィル材を硬化させる工程

をこの順に含む、半導体パッケージの製造方法。

〔8〕半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線とを、昇温速度2.5~5.0℃/秒で昇温し、240~270℃で30~70秒間はんだ付けする工程を含む、上記〔7〕記載の半導体パッケージの製造方法。

〔9〕半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線とを240~270℃ではんだ付けする工程の後、降温速度1.0~3.0℃/秒で100~120℃まで冷却する工程を含む、上記〔7〕記載の半導体パッケージの製造方法。

〔10〕上記〔7〕記載の半導体パッケージの製造方法で製造された、半導体パッケージ。 The present invention relates to a non-cleaning flux and a method for manufacturing a semiconductor package that have solved the above problems by having the following configuration.

[1] A non-cleaning flux is applied at room temperature between a solder bump formed on a semiconductor chip and a solder plated wiring formed on a substrate.

After soldering the solder bump formed on the semiconductor chip and the solder plated wiring formed on the substrate at 240 to 270 ° C.,

Cool to 100-120 ° C,

A non-cleaning flux used in a semiconductor package process in which an underfill material is filled between a semiconductor chip and a substrate while being maintained at 100 to 120 ° C., and the underfill material is cured at 130 to 160 ° C.

(A) Solvent whose mass is reduced to 50% when measured at a rate of temperature increase of 10 ° C./min in thermogravimetric analysis, and (B) Temperature increase in thermogravimetric analysis The temperature at which the mass is reduced to 50% when measured at a rate of 10 ° C./min contains a dicarboxylic acid or tricarboxylic acid having a temperature of 190 to 320 ° C., and the component (B) is added to 100 parts by mass of the no-clean flux. And a non-cleaning flux characterized by containing 0.3 to 3.0 parts by mass.

[2] Furthermore, (C) a thermogravimetric analysis contains a tertiary amine having a temperature at which the mass decreases to 50% when measured at a rate of temperature increase of 10 ° C./min, from 130 to 170 ° C .; The non-cleaning flux according to the above [1].

[3] The non-cleaning flux according to the above [1], wherein the component (B) is an aliphatic dicarboxylic acid.

[4] The non-cleaning flux according to the above [1], wherein the component (C) is tributylamine.

[5] The non-cleaning flux according to the above [1], wherein the solder of the solder bump formed on the semiconductor chip is tin-silver based.

[6] The non-cleaning flux according to the above [1], wherein the solder of the solder-plated wiring formed on the substrate is a tin-silver-copper system.

[7] A step of applying the non-cleaning flux according to the above [1] at room temperature between the solder bump formed on the semiconductor chip and the solder plated wiring formed on the substrate.

Soldering solder bumps formed on the semiconductor chip and solder plated wiring formed on the substrate at 240 to 270 ° C .;

A step of cooling to 100 to 120 ° C. and a step of filling the underfill material between the semiconductor chip and the substrate while maintaining the temperature at 100 to 120 ° C. and curing the underfill material at 130 to 160 ° C. in this order are included. And manufacturing method of semiconductor package.

[8] The solder bumps formed on the semiconductor chip and the solder-plated wiring formed on the substrate are heated at a temperature increase rate of 2.5 to 5.0 ° C./second and 30 to 240 to 270 ° C. The method for producing a semiconductor package according to [7] above, comprising a step of soldering for 70 seconds.

[9] After the step of soldering the solder bumps formed on the semiconductor chip and the solder plated wiring formed on the substrate at 240 to 270 ° C., the temperature decreasing rate is 1.0 to 3.0 ° C./second. The method for producing a semiconductor package according to the above [7], comprising a step of cooling to 100 to 120 ° C.

[10] A semiconductor package manufactured by the method for manufacturing a semiconductor package described in [7] above.

〔1〕半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線との間に、無洗浄フラックスを室温で塗布し、

半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線とを240~270℃ではんだ付けした後、

100~120℃まで冷却し、

100~120℃に保持したまま、半導体チップと基板との間にアンダーフィル材を充填し、130~160℃でアンダーフィル材を硬化させる

半導体パッケージ工程で使用される無洗浄フラックスであって、

(A)熱重量分析で、昇温速度が10℃/分で測定したときに質量が50%に減少する温度が、160~210℃である溶剤、および

(B)熱重量分析で、昇温速度が10℃/分で測定したときに質量が50%に減少する温度が、190~320℃であるジカルボン酸またはトリカルボン酸

を含有し、(B)成分を、無洗浄フラックス100質量部に対して、0.3~3.0質量部含有することを特徴とする、無洗浄フラックス。

〔2〕さらに、(C)熱重量分析で、昇温速度が10℃/分で測定したときに質量が50%に減少する温度が、130~170℃である第3級アミンを含有する、上記〔1〕記載の無洗浄フラックス。

〔3〕(B)成分が、脂肪族ジカルボン酸である、上記〔1〕記載の無洗浄フラックス。

〔4〕(C)成分が、トリブチルアミンである、上記〔1〕記載の無洗浄フラックス。

〔5〕半導体チップに形成されたはんだバンプのはんだが、錫銀系である、上記〔1〕記載の無洗浄フラックス。

〔6〕基板に形成されたはんだめっきされた配線のはんだが、錫銀銅系である、上記〔1〕記載の無洗浄フラックス。

〔7〕半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線との間に、上記〔1〕記載の無洗浄フラックスを室温で塗布する工程、

半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線とを240~270℃ではんだ付けする工程、

100~120℃まで冷却する工程、および

100~120℃に保持したまま、半導体チップと基板との間にアンダーフィル材を充填し、130~160℃でアンダーフィル材を硬化させる工程

をこの順に含む、半導体パッケージの製造方法。

〔8〕半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線とを、昇温速度2.5~5.0℃/秒で昇温し、240~270℃で30~70秒間はんだ付けする工程を含む、上記〔7〕記載の半導体パッケージの製造方法。

〔9〕半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線とを240~270℃ではんだ付けする工程の後、降温速度1.0~3.0℃/秒で100~120℃まで冷却する工程を含む、上記〔7〕記載の半導体パッケージの製造方法。

〔10〕上記〔7〕記載の半導体パッケージの製造方法で製造された、半導体パッケージ。 The present invention relates to a non-cleaning flux and a method for manufacturing a semiconductor package that have solved the above problems by having the following configuration.

[1] A non-cleaning flux is applied at room temperature between a solder bump formed on a semiconductor chip and a solder plated wiring formed on a substrate.

After soldering the solder bump formed on the semiconductor chip and the solder plated wiring formed on the substrate at 240 to 270 ° C.,

Cool to 100-120 ° C,

A non-cleaning flux used in a semiconductor package process in which an underfill material is filled between a semiconductor chip and a substrate while being maintained at 100 to 120 ° C., and the underfill material is cured at 130 to 160 ° C.

(A) Solvent whose mass is reduced to 50% when measured at a rate of temperature increase of 10 ° C./min in thermogravimetric analysis, and (B) Temperature increase in thermogravimetric analysis The temperature at which the mass is reduced to 50% when measured at a rate of 10 ° C./min contains a dicarboxylic acid or tricarboxylic acid having a temperature of 190 to 320 ° C., and the component (B) is added to 100 parts by mass of the no-clean flux. And a non-cleaning flux characterized by containing 0.3 to 3.0 parts by mass.

[2] Furthermore, (C) a thermogravimetric analysis contains a tertiary amine having a temperature at which the mass decreases to 50% when measured at a rate of temperature increase of 10 ° C./min, from 130 to 170 ° C .; The non-cleaning flux according to the above [1].

[3] The non-cleaning flux according to the above [1], wherein the component (B) is an aliphatic dicarboxylic acid.

[4] The non-cleaning flux according to the above [1], wherein the component (C) is tributylamine.

[5] The non-cleaning flux according to the above [1], wherein the solder of the solder bump formed on the semiconductor chip is tin-silver based.

[6] The non-cleaning flux according to the above [1], wherein the solder of the solder-plated wiring formed on the substrate is a tin-silver-copper system.

[7] A step of applying the non-cleaning flux according to the above [1] at room temperature between the solder bump formed on the semiconductor chip and the solder plated wiring formed on the substrate.

Soldering solder bumps formed on the semiconductor chip and solder plated wiring formed on the substrate at 240 to 270 ° C .;

A step of cooling to 100 to 120 ° C. and a step of filling the underfill material between the semiconductor chip and the substrate while maintaining the temperature at 100 to 120 ° C. and curing the underfill material at 130 to 160 ° C. in this order are included. And manufacturing method of semiconductor package.

[8] The solder bumps formed on the semiconductor chip and the solder-plated wiring formed on the substrate are heated at a temperature increase rate of 2.5 to 5.0 ° C./second and 30 to 240 to 270 ° C. The method for producing a semiconductor package according to [7] above, comprising a step of soldering for 70 seconds.

[9] After the step of soldering the solder bumps formed on the semiconductor chip and the solder plated wiring formed on the substrate at 240 to 270 ° C., the temperature decreasing rate is 1.0 to 3.0 ° C./second. The method for producing a semiconductor package according to the above [7], comprising a step of cooling to 100 to 120 ° C.

[10] A semiconductor package manufactured by the method for manufacturing a semiconductor package described in [7] above.

本発明〔1〕によれば、はんだ付け後、室温まで冷却せず、100~120℃まで冷却した後、100~120℃でアンダーフィル材を充填した後、アンダーフィル材を硬化させる製造方法に使用可能な無残渣フラックスを提供することができる。

According to the present invention [1], there is provided a manufacturing method in which, after soldering, after cooling to 100 to 120 ° C. without cooling to room temperature, filling the underfill material at 100 to 120 ° C. and then curing the underfill material. A usable residue-free flux can be provided.

本発明〔7〕によれば、はんだバンプや配線の狭ギャップ化や、マルチコア化によるチップの大型化に対応した半導体パッケージを、簡便に製造することができる。

According to the present invention [7], it is possible to easily manufacture a semiconductor package corresponding to the narrowing of the gap between the solder bumps and the wiring and the enlargement of the chip due to the multicore.

本発明〔10〕によれば、はんだバンプや配線の狭ギャップ化や、マルチコア化によるチップの大型化に対応した半導体パッケージを提供することができる。

According to the present invention [10], it is possible to provide a semiconductor package that can cope with the narrowing of the gaps of solder bumps and wiring and the enlargement of the chip due to the multicore.

〔無洗浄フラックス〕

本発明の無洗浄フラックスは、

半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線との間に、無洗浄フラックスを室温で塗布し、

半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線とを240~270℃ではんだ付けした後、

100~120℃まで冷却し、

100~120℃に保持したまま、半導体チップと基板との間にアンダーフィル材を充填し、130~160℃でアンダーフィル材を硬化させる

半導体パッケージ工程で使用される無洗浄フラックスであって、

(A)熱重量分析で、昇温速度が10℃/分で測定したときに質量が50%に減少する温度(以下、T50という)が、160~210℃である溶剤、および

(B)熱重量分析で、昇温速度が10℃/分で測定したときに質量が50%に減少する温度が、190~320℃であるジカルボン酸またはトリカルボン酸

を含有し、(B)成分を、無洗浄フラックス100質量部に対して、0.3~3.0質量部含有することを特徴とする。本発明者は、はんだバンプ、はんだめっきされた配線への適切な活性力、揮発性を満足させ、かつリフロー後のフラックス残渣が極めて少ないフラックスを得るために、フラックス組成とリフロー条件について鋭意研究を行い、無洗浄フラックスによる製造方法に適合した無残渣フラックスを見出した。ここで、はんだバンプ、はんだめっきされた配線への適切な活性力とは、はんだバンプやはんだメッキされた配線の酸化膜を除去することができ、かつ過剰に気泡を発生させず、はんだのボイドの発生を抑制できることをいう。 [No-clean flux]

The no-clean flux of the present invention is

Applying no-clean flux at room temperature between the solder bumps formed on the semiconductor chip and the solder-plated wiring formed on the substrate,

After soldering the solder bump formed on the semiconductor chip and the solder plated wiring formed on the substrate at 240 to 270 ° C.,

Cool to 100-120 ° C,

A non-cleaning flux used in a semiconductor package process in which an underfill material is filled between a semiconductor chip and a substrate while being maintained at 100 to 120 ° C., and the underfill material is cured at 130 to 160 ° C.

(A) a solvent having a temperature at which the mass decreases to 50% (hereinafter referred to as T 50 ) when measured at 10 ° C./min in a thermogravimetric analysis at a temperature rising rate of 160 to 210 ° C., and (B) The thermogravimetric analysis contains a dicarboxylic acid or tricarboxylic acid whose mass decreases to 50% when measured at a rate of temperature increase of 10 ° C / min. It is characterized by containing 0.3 to 3.0 parts by mass with respect to 100 parts by mass of the cleaning flux. The present inventor has conducted intensive research on the flux composition and reflow conditions in order to obtain a solder bump, appropriate activation power for solder-plated wiring, volatility, and to obtain a flux with very little flux residue after reflow. And found a residue-free flux suitable for the production method using no-clean flux. Here, the appropriate activation force for solder bumps and solder-plated wiring means that the oxide film of the solder bumps and solder-plated wiring can be removed, and no voids are generated and the solder voids are generated. This means that the occurrence of

本発明の無洗浄フラックスは、

半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線との間に、無洗浄フラックスを室温で塗布し、

半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線とを240~270℃ではんだ付けした後、

100~120℃まで冷却し、

100~120℃に保持したまま、半導体チップと基板との間にアンダーフィル材を充填し、130~160℃でアンダーフィル材を硬化させる

半導体パッケージ工程で使用される無洗浄フラックスであって、

(A)熱重量分析で、昇温速度が10℃/分で測定したときに質量が50%に減少する温度(以下、T50という)が、160~210℃である溶剤、および

(B)熱重量分析で、昇温速度が10℃/分で測定したときに質量が50%に減少する温度が、190~320℃であるジカルボン酸またはトリカルボン酸

を含有し、(B)成分を、無洗浄フラックス100質量部に対して、0.3~3.0質量部含有することを特徴とする。本発明者は、はんだバンプ、はんだめっきされた配線への適切な活性力、揮発性を満足させ、かつリフロー後のフラックス残渣が極めて少ないフラックスを得るために、フラックス組成とリフロー条件について鋭意研究を行い、無洗浄フラックスによる製造方法に適合した無残渣フラックスを見出した。ここで、はんだバンプ、はんだめっきされた配線への適切な活性力とは、はんだバンプやはんだメッキされた配線の酸化膜を除去することができ、かつ過剰に気泡を発生させず、はんだのボイドの発生を抑制できることをいう。 [No-clean flux]

The no-clean flux of the present invention is

Applying no-clean flux at room temperature between the solder bumps formed on the semiconductor chip and the solder-plated wiring formed on the substrate,

After soldering the solder bump formed on the semiconductor chip and the solder plated wiring formed on the substrate at 240 to 270 ° C.,

Cool to 100-120 ° C,

A non-cleaning flux used in a semiconductor package process in which an underfill material is filled between a semiconductor chip and a substrate while being maintained at 100 to 120 ° C., and the underfill material is cured at 130 to 160 ° C.

(A) a solvent having a temperature at which the mass decreases to 50% (hereinafter referred to as T 50 ) when measured at 10 ° C./min in a thermogravimetric analysis at a temperature rising rate of 160 to 210 ° C., and (B) The thermogravimetric analysis contains a dicarboxylic acid or tricarboxylic acid whose mass decreases to 50% when measured at a rate of temperature increase of 10 ° C / min. It is characterized by containing 0.3 to 3.0 parts by mass with respect to 100 parts by mass of the cleaning flux. The present inventor has conducted intensive research on the flux composition and reflow conditions in order to obtain a solder bump, appropriate activation power for solder-plated wiring, volatility, and to obtain a flux with very little flux residue after reflow. And found a residue-free flux suitable for the production method using no-clean flux. Here, the appropriate activation force for solder bumps and solder-plated wiring means that the oxide film of the solder bumps and solder-plated wiring can be removed, and no voids are generated and the solder voids are generated. This means that the occurrence of

(A)成分は、無洗浄フラックス中で、主に、溶剤として作用する。(A)成分は、熱重量分析で、昇温速度が10℃/分で測定したときに質量が50%に減少する温度が、160~210℃である溶剤である。(A)成分としては、エチレングリコールモノフェニルエーテル(EPH、C6H5OCH2CH2OH、T50:181℃)、2-エチル-1,3-ヘキサンジオール(T50:189℃)、2-エチル-1,3-ヘキサンジオール:イソボルニルヘキサノール(日本テルペン化学製テルソルブMTPH)=1:1の混合溶剤(T50:186℃)等が挙げられ、エチレングリコールモノフェニルエーテル、2-エチル-1,3-ヘキサンジオール、2-エチル-1,3-ヘキサンジオール:イソボルニルヘキサノール(日本テルペン化学製テルソルブMTPH)=1:1の混合溶剤が好ましい。

The component (A) mainly acts as a solvent in the no-clean flux. Component (A) is a solvent having a temperature at which the mass decreases to 50% when measured at a rate of temperature increase of 10 ° C./min by thermogravimetric analysis, at 160 to 210 ° C. As the component (A), ethylene glycol monophenyl ether (EPH, C 6 H 5 OCH 2 CH 2 OH, T 50 : 181 ° C.), 2-ethyl-1,3-hexanediol (T 50 : 189 ° C.), 2-ethyl-1,3-hexanediol: isobornylhexanol (Telsolve MTPH manufactured by Nippon Terpene Chemical) = 1: 1 mixed solvent (T 50 : 186 ° C.) and the like, ethylene glycol monophenyl ether, 2- A mixed solvent of ethyl-1,3-hexanediol, 2-ethyl-1,3-hexanediol: isobornylhexanol (Telsolve MTPH manufactured by Nippon Terpene Chemical) = 1: 1 is preferable.

また、(A)成分は、熱重量分析で、昇温速度が10℃/分で測定したときに質量が50%に減少する温度が、160~190℃である溶剤と、200~240℃である溶剤(例えば、イソボルニルヘキサノール(Tg:234℃))との混合溶剤であると、はんだの接続性の観点から、好ましい。特に、20mm□レベルの大きな半導体チップを用いる場合には、(A)160~190℃である溶剤と、200~240℃である溶剤との混合溶剤との質量比が、1:(2以下)が好ましく、1:(0.1~2)がより好ましく、1:(0.5~2)が更に好ましい。なお、160~190℃である溶剤と、200~240℃である溶剤との混合溶剤との質量比が、1:(4~5)になると、昇温速度が10℃/分で測定したときに質量が50%に減少する温度が、190℃より高くなりやすく(すなわち、(A)成分ではなくなりやすく)、残渣が残りやすくなってしまう。また、(A)成分は、無洗浄フラックス100質量部に対して、95~99.7質量部であると好ましく、97~99.5質量部であると、より好ましい。

In addition, the component (A) is a thermogravimetric analysis, a solvent whose temperature is reduced to 50% when measured at a heating rate of 10 ° C./min, and a solvent whose temperature is from 160 to 190 ° C. A mixed solvent with a certain solvent (for example, isobornyl hexanol (Tg: 234 ° C.)) is preferable from the viewpoint of solder connectivity. In particular, when a large semiconductor chip of 20 mm □ level is used, (A) the mass ratio of the solvent at 160 to 190 ° C. and the solvent mixture at 200 to 240 ° C. is 1: (2 or less) Is preferred, 1: (0.1-2) is more preferred, and 1: (0.5-2) is even more preferred. When the mass ratio of the solvent having a temperature of 160 to 190 ° C. and the solvent mixture of 200 to 240 ° C. is 1: (4 to 5), the rate of temperature rise is 10 ° C./min. In addition, the temperature at which the mass decreases to 50% tends to be higher than 190 ° C. (that is, not easily the component (A)), and the residue tends to remain. Further, the component (A) is preferably 95 to 99.7 parts by mass, more preferably 97 to 99.5 parts by mass with respect to 100 parts by mass of the non-cleaning flux.

(B)成分は、無洗浄フラックス中で、主に、活性剤として作用する。(B)成分は、熱重量分析で、昇温速度が10℃/分で測定したときに質量が50%に減少する温度が、190~320℃であるジカルボン酸またはトリカルボン酸である。(B)成分は、主に、活性剤として機能する。(B)成分としては、シュウ酸(HOOCCOOH、T50:195℃)、コハク酸(HOOC(CH2)2COOH、T50:230℃)、アジピン酸(HOOC(CH2)4COOH、T50:268℃)、1,2,4-シクロヘキサントリカルボン酸(H-TMA、T50:310℃)が挙げられ、シュウ酸、コハク酸、アジピン酸、1,2,4-シクロヘキサントリカルボン酸が好ましい。ここで、(B)成分として挙げた化合物は、固体であるが、(A)成分に溶解するものが、無洗浄フラックス中への均一な分散性の観点から好ましい。(B)成分が、脂肪族ジカルボン酸であると、より好ましい。

The component (B) mainly acts as an activator in the no-clean flux. Component (B) is a dicarboxylic acid or tricarboxylic acid having a temperature at which the mass decreases to 50% when measured at a rate of temperature increase of 10 ° C./minute by thermogravimetric analysis at 190 to 320 ° C. The component (B) mainly functions as an activator. As the component (B), oxalic acid (HOOCCOOH, T 50 : 195 ° C.), succinic acid (HOOC (CH 2 ) 2 COOH, T 50 : 230 ° C.), adipic acid (HOOC (CH 2 ) 4 COOH, T 50 : 268 ° C.) and 1,2,4-cyclohexanetricarboxylic acid (H-TMA, T 50 : 310 ° C.), and oxalic acid, succinic acid, adipic acid, and 1,2,4-cyclohexanetricarboxylic acid are preferred. Here, the compounds mentioned as the component (B) are solid, but those that dissolve in the component (A) are preferable from the viewpoint of uniform dispersibility in the non-cleaning flux. The component (B) is more preferably an aliphatic dicarboxylic acid.

(B)成分は、無洗浄フラックス100質量部に対して、0.3~3.0質量部含有され、0.5~3.0質量部であると、好ましい。0.3質量部未満では、接続性が悪くなりやすくなってしまい、3.0質量部を超えると、残渣が残りやすくなってしまう。

The component (B) is contained in an amount of 0.3 to 3.0 parts by mass and preferably 0.5 to 3.0 parts by mass with respect to 100 parts by mass of the non-cleaning flux. If it is less than 0.3 part by mass, the connectivity tends to be poor, and if it exceeds 3.0 parts by mass, the residue tends to remain.

無洗浄フラックスは、さらに、(C)熱重量分析で、昇温速度が10℃/分で測定したときに質量が50%に減少する温度が、130~170℃である第3級アミンを含有すると、(B)成分の溶解安定性の観点から、好ましく、トリブチルアミンであると、より好ましい。(C)成分は、(B)成分が(A)成分に溶解しにくい場合に、使用されると好ましい。(C)成分は、主に、活性剤として作用する。

The non-cleaning flux further contains (C) a tertiary amine having a temperature at which the mass decreases to 50% when measured at a rate of temperature increase of 10 ° C / min in thermogravimetric analysis at 130 to 170 ° C. Then, it is preferable from a viewpoint of the dissolution stability of (B) component, and it is more preferable in it being tributylamine. The component (C) is preferably used when the component (B) is difficult to dissolve in the component (A). The component (C) mainly acts as an activator.

(C)成分は、(B)成分の質量に対して、10倍以下であると好ましく、5倍以下であるとより好ましく、2倍以下であるとさらに好ましい。(C)成分が、10倍より多くなると、はんだの接続性が悪化するおそれがある。また、(C)成分は、(B)成分の質量に対して、0.5倍以上であると、添加の効果を発揮しやすい。

The component (C) is preferably 10 times or less, more preferably 5 times or less, and even more preferably 2 times or less with respect to the mass of the component (B). If the component (C) is more than 10 times, the solder connectivity may be deteriorated. Moreover, the (C) component tends to exhibit the effect of addition as it is 0.5 times or more with respect to the mass of (B) component.

無洗浄フラックスは、本発明の目的を損なわない範囲で、更に必要に応じ、添加剤等を配合することができる。

The non-cleaning flux can be further blended with additives and the like as necessary, as long as the object of the present invention is not impaired.

無洗浄フラックスは、半導体チップに形成されたはんだバンプのはんだが、錫銀系である場合に適している。また、無洗浄フラックスは、基板に形成されたはんだめっきされた配線のはんだが、錫銀銅系である場合に適している。

The no-clean flux is suitable when the solder bump solder formed on the semiconductor chip is tin-silver based. Further, the no-clean flux is suitable when the solder of the solder plated wiring formed on the substrate is a tin-silver-copper system.

〔アンダーフィル材〕

アンダーフィル材は、特に限定されないが、以下、好ましいアンダーフィル材であるエポキシ樹脂組成物について説明する。アンダーフィル材は、少なくとも(UA)エポキシ樹脂、(UB)硬化剤を含むと好ましい。 [Underfill material]

Although an underfill material is not specifically limited, Hereinafter, the epoxy resin composition which is a preferable underfill material is demonstrated. The underfill material preferably contains at least (UA) epoxy resin and (UB) curing agent.

アンダーフィル材は、特に限定されないが、以下、好ましいアンダーフィル材であるエポキシ樹脂組成物について説明する。アンダーフィル材は、少なくとも(UA)エポキシ樹脂、(UB)硬化剤を含むと好ましい。 [Underfill material]

Although an underfill material is not specifically limited, Hereinafter, the epoxy resin composition which is a preferable underfill material is demonstrated. The underfill material preferably contains at least (UA) epoxy resin and (UB) curing agent.

(UA)成分としては、ビスフェノールA型エポキシ樹脂、臭素化ビスフェノールA型エポキシ樹脂、ビスフェノールF型エポキシ樹脂、ナフタレン型エポキシ樹脂、ビフェニル型エポキシ樹脂、ノボラック型エポキシ樹脂、アミノフェノール系エポキシ樹脂、脂環式エポキシ樹脂、エーテル系またはポリエーテル系エポキシ樹脂、オキシラン環含有エポキシ樹脂等が挙げられ、ビスフェノールF型エポキシ樹脂、アミノフェノール系エポキシ樹脂、ビスフェノールA型エポキシ樹脂、ナフタレン型エポキシ樹脂が、アンダーフィル材のガラス転移点、耐リフロー性、および耐湿性の観点から好ましい。

(UA) component includes bisphenol A type epoxy resin, brominated bisphenol A type epoxy resin, bisphenol F type epoxy resin, naphthalene type epoxy resin, biphenyl type epoxy resin, novolac type epoxy resin, aminophenol type epoxy resin, alicyclic ring Type epoxy resin, ether type or polyether type epoxy resin, oxirane ring-containing epoxy resin, etc., bisphenol F type epoxy resin, aminophenol type epoxy resin, bisphenol A type epoxy resin, naphthalene type epoxy resin are underfill materials From the viewpoint of glass transition point, reflow resistance, and moisture resistance.

ビスフェノールF型エポキシ樹脂は、好ましくは、式(1):

Bisphenol F type epoxy resin is preferably represented by the formula (1):

で示され、式中、nは平均値を表し、好ましくは0~6、より好ましくは0~3である。エポキシ当量は、150~900g/eqが好ましい。

In the formula, n represents an average value, preferably 0 to 6, more preferably 0 to 3. The epoxy equivalent is preferably 150 to 900 g / eq.

アミノフェノール系エポキシ樹脂は、好ましくは、式(2):

The aminophenol-based epoxy resin is preferably a formula (2):

で示され、2個の官能基がオルト位、またはパラ位にあるものがより好ましい。

It is more preferable that two functional groups are in the ortho position or the para position.

ビスフェノールA型エポキシ樹脂は、好ましくは、式(3):

The bisphenol A type epoxy resin is preferably represented by the formula (3):

で示され、式中、mは平均値を表し、好ましくは0~6、特に好ましくは0~3である、エポキシ樹脂が挙げられる。エポキシ当量は、170~1000g/eqが好ましい。

In the formula, m represents an average value, and an epoxy resin having 0 to 6 and particularly preferably 0 to 3 is preferable. The epoxy equivalent is preferably 170 to 1000 g / eq.

(UA)成分は、単独でも2種以上を併用してもよい。

(UA) component may be used alone or in combination of two or more.

(UB)成分としては、アミン系硬化剤、酸無水物系硬化剤、フェノール系硬化剤等が挙げられ、アミン系硬化剤が、アンダーフィル材の耐リフロー性、および耐湿性の観点から好ましい。

Examples of the (UB) component include amine-based curing agents, acid anhydride-based curing agents, phenol-based curing agents, and the like, and amine-based curing agents are preferable from the viewpoint of reflow resistance and moisture resistance of the underfill material.

アミン系硬化剤は、脂肪族ポリアミン;芳香族アミン;ポリアミノアミド、ポリアミノイミド、ポリアミノエステルおよびポリアミノ尿素等の変成ポリアミン;第三級アミン系;イミダゾール系;ヒドラジド系;ジシアンアミド系;メラミン系の化合物等が挙げられ、芳香族アミン系化合物が好ましい。

Amine curing agents include aliphatic polyamines; aromatic amines; modified polyamines such as polyaminoamides, polyaminoimides, polyaminoesters and polyaminoureas; tertiary amines; imidazoles; hydrazides; dicyanamides; An aromatic amine compound is preferable.

芳香族アミン系化合物は、1個の芳香族環を有する芳香族アミン化合物および/または2個の芳香族環を有する芳香族アミン化合物を含むことが、より好ましい。

It is more preferable that the aromatic amine compound includes an aromatic amine compound having one aromatic ring and / or an aromatic amine compound having two aromatic rings.

1個の芳香族環を有する芳香族アミン化合物としては、メタフェニレンジアミン等が挙げられ、式(4)または式(5):

Examples of the aromatic amine compound having one aromatic ring include metaphenylenediamine and the like, and the formula (4) or the formula (5):

で示されるものが、好ましい。

What is shown is preferable.

2個の芳香族環を有する芳香族アミン化合物としては、ジアミノジフェニルメタン、ジアミノジフェニルスルフォン等が挙げられ、式(6)または式(7):

Examples of the aromatic amine compound having two aromatic rings include diaminodiphenylmethane and diaminodiphenylsulfone, and the formula (6) or the formula (7):

(式中、Rは、水素、または炭素数1~5個のアルキル基を表す)で示されるものが好ましく、式(8)または式(9)でRが炭素数2個のアルキル基であるものが、より好ましい。

(Wherein R represents hydrogen or an alkyl group having 1 to 5 carbon atoms) is preferred, and in formula (8) or formula (9), R is an alkyl group having 2 carbon atoms. Those are more preferred.

(UB)成分は、単独でも2種以上を併用してもよい。

(UB) component may be used alone or in combination of two or more.

アンダーフィル材は、さらに、(UC)フィラーを含むと、硬化後のアンダーフィル材の熱膨張係数の観点から好ましい。(UC)成分としては、シリカ、アルミナ、窒化ケイ素、マイカ、ホワイトカーボン等が挙げられ、硬化後のアンダーフィル材の熱膨張係数の低下、およびコストの観点から、シリカが好ましい。シリカは、非晶質シリカ、結晶性シリカ、溶融シリカ、粉砕シリカ、ナノシリカ等、当技術分野で使用される各種シリカを使用することができ、硬化後のアンダーフィル材の熱膨張係数低下の点から非晶質シリカが好ましい。(C)成分の粒径は、半導体チップと基板の間隙への充填性の観点から0.1~2.0μmが好ましく、0.1~1.0μmがより好ましい。ここで、平均粒径は、レーザー回折式粒度分布測定装置により測定する。また、(C)成分の形状は、特に限定されず、球状、リン片状、不定形等が挙げられ、封止用液状樹脂組成物の流動性の観点から、球状が好ましい。

It is preferable that the underfill material further contains a (UC) filler from the viewpoint of the thermal expansion coefficient of the cured underfill material. Examples of the (UC) component include silica, alumina, silicon nitride, mica, white carbon, and the like, and silica is preferable from the viewpoints of lowering the thermal expansion coefficient of the underfill material after curing and cost. As silica, various silicas used in this technical field such as amorphous silica, crystalline silica, fused silica, pulverized silica, and nano silica can be used, and the thermal expansion coefficient of the underfill material after curing is reduced. To amorphous silica is preferred. The particle size of the component (C) is preferably from 0.1 to 2.0 μm, more preferably from 0.1 to 1.0 μm, from the viewpoint of filling into the gap between the semiconductor chip and the substrate. Here, the average particle diameter is measured by a laser diffraction particle size distribution measuring apparatus. Moreover, the shape of (C) component is not specifically limited, A spherical shape, flake shape, an indeterminate form, etc. are mentioned, From the viewpoint of the fluidity | liquidity of the liquid resin composition for sealing, a spherical shape is preferable.

(UC)成分は、単独でも2種以上を併用してもよい。

(UC) component may be used alone or in combination of two or more.

アンダーフィル材は、成分(UA)100質量部に対して、成分(UB)を20~100質量部、より好ましくは40~60質量部含むことが、アンダーフィル材のガラス転移点、耐リフロー性、および耐湿性の観点から、好ましい。

The underfill material contains 20 to 100 parts by mass, more preferably 40 to 60 parts by mass of the component (UB) with respect to 100 parts by mass of the component (UA). And from the viewpoint of moisture resistance.

また、成分(UA)100質量部に対して、成分(UC)を160~400質量部、より好ましくは200~350質量部含むことが、アンダーフィル材の流動性、および硬化後のアンダーフィル材の熱膨張係数低下の観点から、好ましい。

Further, the component (UC) is contained in an amount of 160 to 400 parts by mass, more preferably 200 to 350 parts by mass with respect to 100 parts by mass of the component (UA), and the fluidity of the underfill material and the cured underfill material From the viewpoint of lowering the thermal expansion coefficient, it is preferable.

アンダーフィル材には、本発明の目的を損なわない範囲で、更に必要に応じ、カーボンブラックなどの顔料、染料、シランカップリング剤、消泡剤、酸化防止剤、その他の添加剤等、更に有機溶剤等を配合することができる。

In the underfill material, as long as the object of the present invention is not impaired, a pigment such as carbon black, a dye, a silane coupling agent, an antifoaming agent, an antioxidant, other additives, etc. A solvent etc. can be mix | blended.

アンダーフィル材は、例えば、(UA)成分~(UC)成分およびその他の添加剤等を同時にまたは別々に、必要により加熱処理を加えながら、撹拌、溶融、混合、分散させることにより得ることができる。これらの混合、撹拌、分散等の装置としては、特に限定されるものではないが、撹拌、加熱装置を備えたライカイ機、3本ロールミル、ボールミル、プラネタリーミキサー、ビーズミル等を使用することができる。また、これら装置を適宜組み合わせて使用してもよい。

The underfill material can be obtained, for example, by stirring, melting, mixing, and dispersing the (UA) component to the (UC) component and other additives simultaneously or separately, with heat treatment as necessary. . The mixing, stirring, dispersing and the like devices are not particularly limited, and a raikai machine equipped with a stirring and heating device, a three-roll mill, a ball mill, a planetary mixer, a bead mill and the like can be used. . Moreover, you may use combining these apparatuses suitably.

アンダーフィル材は、温度:25℃での粘度が1~100Pa・sであると、好ましい。ここで、粘度は、Brookfield社製粘度計(型番:DV-1)で測定する。

The underfill material preferably has a viscosity at a temperature of 25 ° C. of 1 to 100 Pa · s. Here, the viscosity is measured with a viscometer manufactured by Brookfield (model number: DV-1).

アンダーフィル材の硬化は、130~160℃で、90~150分間行うことが好ましい。

The underfill material is preferably cured at 130 to 160 ° C. for 90 to 150 minutes.

〔半導体パッケージの製造方法〕

本発明の半導体パッケージの製造方法は、半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線との間に、上述の無洗浄フラックスを室温で塗布する工程、

半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線とを240~270℃ではんだ付けする工程、

100~120℃まで冷却する工程、および

100~120℃に保持したまま、半導体チップと基板との間にアンダーフィル材を充填し、130~160℃でアンダーフィル材を硬化させる工程

をこの順に含む。図2に、本発明の半導体パッケージの製造方法を説明するための図を示す。図2に示すように、本発明の半導体パッケージの製造方法は、半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線との間に、上述の無洗浄フラックスを室温で塗布する工程、

半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線とを240~270℃ではんだ付けする工程(図2の(1))、

100~120℃まで冷却する工程(図2の(1)と(2)の間)、および

100~120℃に保持したまま(図2の(2))、半導体チップと基板との間にアンダーフィル材を充填し、130~160℃でアンダーフィル材を硬化させる工程(図2の(3))

をこの順に含む。 [Method of manufacturing semiconductor package]

A method for manufacturing a semiconductor package of the present invention includes a step of applying the above-described non-cleaning flux at room temperature between a solder bump formed on a semiconductor chip and a solder-plated wiring formed on a substrate,

Soldering solder bumps formed on the semiconductor chip and solder plated wiring formed on the substrate at 240 to 270 ° C .;

A step of cooling to 100 to 120 ° C. and a step of filling the underfill material between the semiconductor chip and the substrate while maintaining the temperature at 100 to 120 ° C. and curing the underfill material at 130 to 160 ° C. in this order are included. . FIG. 2 is a view for explaining the method for manufacturing a semiconductor package of the present invention. As shown in FIG. 2, the method for manufacturing a semiconductor package of the present invention uses the above-mentioned non-cleaning flux at room temperature between a solder bump formed on a semiconductor chip and a solder-plated wiring formed on a substrate. Applying step,

A process of soldering solder bumps formed on the semiconductor chip and solder plated wiring formed on the substrate at 240 to 270 ° C. ((1) in FIG. 2);

A process of cooling to 100 to 120 ° C. (between (1) and (2) in FIG. 2) and while maintaining the temperature at 100 to 120 ° C. ((2) in FIG. 2) Step of filling the fill material and curing the underfill material at 130 to 160 ° C. ((3) in FIG. 2)

Are included in this order.

本発明の半導体パッケージの製造方法は、半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線との間に、上述の無洗浄フラックスを室温で塗布する工程、

半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線とを240~270℃ではんだ付けする工程、

100~120℃まで冷却する工程、および

100~120℃に保持したまま、半導体チップと基板との間にアンダーフィル材を充填し、130~160℃でアンダーフィル材を硬化させる工程

をこの順に含む。図2に、本発明の半導体パッケージの製造方法を説明するための図を示す。図2に示すように、本発明の半導体パッケージの製造方法は、半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線との間に、上述の無洗浄フラックスを室温で塗布する工程、

半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線とを240~270℃ではんだ付けする工程(図2の(1))、

100~120℃まで冷却する工程(図2の(1)と(2)の間)、および

100~120℃に保持したまま(図2の(2))、半導体チップと基板との間にアンダーフィル材を充填し、130~160℃でアンダーフィル材を硬化させる工程(図2の(3))

をこの順に含む。 [Method of manufacturing semiconductor package]

A method for manufacturing a semiconductor package of the present invention includes a step of applying the above-described non-cleaning flux at room temperature between a solder bump formed on a semiconductor chip and a solder-plated wiring formed on a substrate,

Soldering solder bumps formed on the semiconductor chip and solder plated wiring formed on the substrate at 240 to 270 ° C .;

A step of cooling to 100 to 120 ° C. and a step of filling the underfill material between the semiconductor chip and the substrate while maintaining the temperature at 100 to 120 ° C. and curing the underfill material at 130 to 160 ° C. in this order are included. . FIG. 2 is a view for explaining the method for manufacturing a semiconductor package of the present invention. As shown in FIG. 2, the method for manufacturing a semiconductor package of the present invention uses the above-mentioned non-cleaning flux at room temperature between a solder bump formed on a semiconductor chip and a solder-plated wiring formed on a substrate. Applying step,

A process of soldering solder bumps formed on the semiconductor chip and solder plated wiring formed on the substrate at 240 to 270 ° C. ((1) in FIG. 2);

A process of cooling to 100 to 120 ° C. (between (1) and (2) in FIG. 2) and while maintaining the temperature at 100 to 120 ° C. ((2) in FIG. 2) Step of filling the fill material and curing the underfill material at 130 to 160 ° C. ((3) in FIG. 2)

Are included in this order.

半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線との間に塗布する、上述の無洗浄フラックスの量は、0.02~0.08mg/mm2であると好ましく、0.04mg/mm2であると、最も好ましい。

The amount of the above-mentioned non-cleaning flux applied between the solder bump formed on the semiconductor chip and the solder-plated wiring formed on the substrate is preferably 0.02 to 0.08 mg / mm 2. 0.04 mg / mm 2 is most preferable.

半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線とを240~270℃ではんだ付けする工程において、無洗浄フラックスは、はんだ濡れが生じる直前までは存在し、はんだ接合後に揮発することが好ましい。昇温速度2.5~5.0℃/秒で昇温し、240~270℃で30~70秒間はんだ付けする工程であると、無洗浄フラックスの揮発挙動の観点から好ましい。

In the process of soldering solder bumps formed on a semiconductor chip and solder-plated wiring formed on a substrate at 240 to 270 ° C., no-clean flux exists until just before solder wetting occurs, It is preferable to volatilize later. The step of heating at a rate of temperature increase of 2.5 to 5.0 ° C./second and soldering at 240 to 270 ° C. for 30 to 70 seconds is preferable from the viewpoint of volatilization behavior of the non-cleaning flux.

半導体チップに形成されたはんだバンプと、基板に形成されたはんだめっきされた配線とを240~270℃ではんだ付けする工程の後、100~120℃まで冷却する工程は、降温速度1.0~3.0℃/秒であると、好ましい。降温速度が1.0℃/秒より遅いと生産性が悪くなり、降温速度が3.0℃/秒より速くなると歩留まりが悪くなるおそれがある。

After the process of soldering the solder bumps formed on the semiconductor chip and the solder-plated wiring formed on the substrate at 240 to 270 ° C., the process of cooling to 100 to 120 ° C. is performed at a temperature drop rate of 1.0 to It is preferable that it is 3.0 ° C./second. When the temperature lowering rate is slower than 1.0 ° C./second, the productivity is deteriorated, and when the temperature lowering rate is higher than 3.0 ° C./second, the yield may be deteriorated.

基板には、エポキシ樹脂、ガラス-エポキシ樹脂、ポリイミド樹脂等が挙げられるが、これらに限定されない。基板に形成されたはんだめっきされた配線のはんだは、環境問題から、鉛フリーハンダ合金である錫銀銅系が好ましい。半導体チップに形成されたバンプには、錫、鉛、銅、ビスマス、銀、亜鉛、インジウム等からなるハンダ合金等を使用することができ、環境問題から、鉛フリーハンダ合金である錫銀系が好ましい。

Examples of the substrate include, but are not limited to, epoxy resin, glass-epoxy resin, polyimide resin, and the like. The solder of the solder-plated wiring formed on the substrate is preferably a tin-silver-copper system that is a lead-free solder alloy because of environmental problems. For the bumps formed on the semiconductor chip, a solder alloy made of tin, lead, copper, bismuth, silver, zinc, indium, etc. can be used. preferable.

本発明について、実施例により説明するが、本発明はこれらに限定されるものではない。なお、以下の実施例において、部、%はことわりのない限り、重量部、重量%を示す。

The present invention will be described with reference to examples, but the present invention is not limited thereto. In the following examples, parts and% represent parts by weight and% by weight unless otherwise specified.

〔実施例1~14、比較例1~4〕

表1~3に示す配合で、超音波洗浄機を用いて混合し、無洗浄フラックスを調製した。表1、3では、2-エチル-1,3-ヘキサンジオールを「ジオール」と、イソボルニルヘキサノールを「MTPH」と記載した。また、以下のように、アンダーフィル材を調製した。新日鉄住金化学製ビスフェノールF型エポキシ樹脂(品名:YDF8170):16.3質量部、三菱化学製アミノフェノール型エポキシ樹脂(品名:EP630):10.9質量部、日本化薬製アミン系硬化剤(品名:カヤハードA-A):12.5質量部、アドマテックス製シリカフィラー(品名:SO-E2、平均粒径:0.5μm):60.0質量部、および信越化学製シランカップリング剤(品名:KBM403)を、3本ロールミルを用いて混合し、アンダーフィル材を調製した。なお、比較例3で使用したジカルボン酸メチルエステル混合物(DBE)は、CH3OOC(CH2)nCOOCH3(n=2~4)であった。 [Examples 1 to 14, Comparative Examples 1 to 4]

With the formulations shown in Tables 1 to 3, mixing was performed using an ultrasonic cleaner to prepare a no-clean flux. In Tables 1 and 3, 2-ethyl-1,3-hexanediol is described as “diol” and isobornylhexanol as “MTPH”. Moreover, the underfill material was prepared as follows. Nippon Steel & Sumikin Chemicals bisphenol F type epoxy resin (product name: YDF8170): 16.3 parts by mass, Mitsubishi Chemical aminophenol type epoxy resin (product name: EP630): 10.9 parts by mass, Nippon Kayaku amine-based curing agent ( Product name: Kayahard AA): 12.5 parts by mass, Admatex silica filler (Product name: SO-E2, average particle size: 0.5 μm): 60.0 parts by mass, and Shin-Etsu Chemical silane coupling agent ( Product name: KBM403) was mixed using a three-roll mill to prepare an underfill material. The dicarboxylic acid methyl ester mixture (DBE) used in Comparative Example 3 was CH 3 OOC (CH 2 ) n COOCH 3 (n = 2 to 4).

表1~3に示す配合で、超音波洗浄機を用いて混合し、無洗浄フラックスを調製した。表1、3では、2-エチル-1,3-ヘキサンジオールを「ジオール」と、イソボルニルヘキサノールを「MTPH」と記載した。また、以下のように、アンダーフィル材を調製した。新日鉄住金化学製ビスフェノールF型エポキシ樹脂(品名:YDF8170):16.3質量部、三菱化学製アミノフェノール型エポキシ樹脂(品名:EP630):10.9質量部、日本化薬製アミン系硬化剤(品名:カヤハードA-A):12.5質量部、アドマテックス製シリカフィラー(品名:SO-E2、平均粒径:0.5μm):60.0質量部、および信越化学製シランカップリング剤(品名:KBM403)を、3本ロールミルを用いて混合し、アンダーフィル材を調製した。なお、比較例3で使用したジカルボン酸メチルエステル混合物(DBE)は、CH3OOC(CH2)nCOOCH3(n=2~4)であった。 [Examples 1 to 14, Comparative Examples 1 to 4]

With the formulations shown in Tables 1 to 3, mixing was performed using an ultrasonic cleaner to prepare a no-clean flux. In Tables 1 and 3, 2-ethyl-1,3-hexanediol is described as “diol” and isobornylhexanol as “MTPH”. Moreover, the underfill material was prepared as follows. Nippon Steel & Sumikin Chemicals bisphenol F type epoxy resin (product name: YDF8170): 16.3 parts by mass, Mitsubishi Chemical aminophenol type epoxy resin (product name: EP630): 10.9 parts by mass, Nippon Kayaku amine-based curing agent ( Product name: Kayahard AA): 12.5 parts by mass, Admatex silica filler (Product name: SO-E2, average particle size: 0.5 μm): 60.0 parts by mass, and Shin-Etsu Chemical silane coupling agent ( Product name: KBM403) was mixed using a three-roll mill to prepare an underfill material. The dicarboxylic acid methyl ester mixture (DBE) used in Comparative Example 3 was CH 3 OOC (CH 2 ) n COOCH 3 (n = 2 to 4).

調製した無洗浄フラックス、アンダーフィル材を用い、以下のようにして半導体パッケージを作製した。10mm□の半導体チップには、(株)ウォルツ製チップ(品名:WALTS-TEG FC150JY_LF(PI) □10mm)、20mm□の半導体チップには、(株)ウォルツ製チップ(品名:WALTS-TEG FC150JY_LF(PI) □20mm)、10mm□の基板には、(株)ウォルツ製基板(品名:WALTS-KIT 01A150P-10 (SAC))、20mm□の基板には、(株)ウォルツ製基板(品名:WALTS-KIT FC150-0103JY_2×2 (SAC))を用いた。