WO2013165031A1 - 반도체 소자 제조 방법 - Google Patents

반도체 소자 제조 방법 Download PDFInfo

- Publication number

- WO2013165031A1 WO2013165031A1 PCT/KR2012/003341 KR2012003341W WO2013165031A1 WO 2013165031 A1 WO2013165031 A1 WO 2013165031A1 KR 2012003341 W KR2012003341 W KR 2012003341W WO 2013165031 A1 WO2013165031 A1 WO 2013165031A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- layer

- metal

- semiconductor device

- metal layer

- forming

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 150

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 44

- 229910052751 metal Inorganic materials 0.000 claims abstract description 304

- 239000002184 metal Substances 0.000 claims abstract description 304

- 238000000034 method Methods 0.000 claims abstract description 78

- 238000005530 etching Methods 0.000 claims abstract description 43

- 238000001039 wet etching Methods 0.000 claims abstract description 41

- 238000005520 cutting process Methods 0.000 claims abstract description 33

- 238000000053 physical method Methods 0.000 claims abstract description 5

- 239000000126 substance Substances 0.000 claims abstract description 4

- 239000010410 layer Substances 0.000 claims description 411

- 229920002120 photoresistant polymer Polymers 0.000 claims description 130

- 238000007747 plating Methods 0.000 claims description 73

- 239000010949 copper Substances 0.000 claims description 36

- 239000000463 material Substances 0.000 claims description 25

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 claims description 24

- 229910052802 copper Inorganic materials 0.000 claims description 24

- 229910000881 Cu alloy Inorganic materials 0.000 claims description 17

- 239000011241 protective layer Substances 0.000 claims description 14

- 230000001681 protective effect Effects 0.000 claims description 10

- 239000000853 adhesive Substances 0.000 claims description 7

- 230000001070 adhesive effect Effects 0.000 claims description 7

- 230000006866 deterioration Effects 0.000 claims description 4

- 238000012546 transfer Methods 0.000 claims description 4

- 238000004140 cleaning Methods 0.000 claims description 3

- 239000002390 adhesive tape Substances 0.000 claims description 2

- 230000035939 shock Effects 0.000 claims description 2

- 239000002356 single layer Substances 0.000 claims description 2

- 238000005336 cracking Methods 0.000 claims 1

- 238000000926 separation method Methods 0.000 abstract description 17

- 230000004888 barrier function Effects 0.000 abstract description 16

- 230000007797 corrosion Effects 0.000 abstract description 16

- 238000005260 corrosion Methods 0.000 abstract description 16

- 235000012431 wafers Nutrition 0.000 description 64

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 17

- 230000008569 process Effects 0.000 description 14

- 230000035882 stress Effects 0.000 description 12

- 238000009792 diffusion process Methods 0.000 description 11

- 239000011651 chromium Substances 0.000 description 10

- 239000010409 thin film Substances 0.000 description 8

- 230000006870 function Effects 0.000 description 7

- 238000005516 engineering process Methods 0.000 description 6

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 6

- 239000000758 substrate Substances 0.000 description 6

- 229910045601 alloy Inorganic materials 0.000 description 5

- 239000000956 alloy Substances 0.000 description 5

- 238000011049 filling Methods 0.000 description 5

- 239000010931 gold Substances 0.000 description 5

- 229910052759 nickel Inorganic materials 0.000 description 5

- 229910003460 diamond Inorganic materials 0.000 description 4

- 239000010432 diamond Substances 0.000 description 4

- 230000008646 thermal stress Effects 0.000 description 4

- 229910052804 chromium Inorganic materials 0.000 description 3

- 230000006378 damage Effects 0.000 description 3

- 239000012535 impurity Substances 0.000 description 3

- 238000002955 isolation Methods 0.000 description 3

- 229910052750 molybdenum Inorganic materials 0.000 description 3

- 229910052697 platinum Inorganic materials 0.000 description 3

- 238000012545 processing Methods 0.000 description 3

- 230000007480 spreading Effects 0.000 description 3

- 238000003892 spreading Methods 0.000 description 3

- 239000010936 titanium Substances 0.000 description 3

- 229910052721 tungsten Inorganic materials 0.000 description 3

- 238000001771 vacuum deposition Methods 0.000 description 3

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 2

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 2

- 229910003266 NiCo Inorganic materials 0.000 description 2

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 2

- 230000009471 action Effects 0.000 description 2

- 210000000988 bone and bone Anatomy 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 238000002844 melting Methods 0.000 description 2

- 230000008018 melting Effects 0.000 description 2

- 150000002739 metals Chemical class 0.000 description 2

- 239000011733 molybdenum Substances 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 229910052594 sapphire Inorganic materials 0.000 description 2

- 239000010980 sapphire Substances 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 239000004332 silver Substances 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 2

- 239000010937 tungsten Substances 0.000 description 2

- 229910002651 NO3 Inorganic materials 0.000 description 1

- NHNBFGGVMKEFGY-UHFFFAOYSA-N Nitrate Chemical compound [O-][N+]([O-])=O NHNBFGGVMKEFGY-UHFFFAOYSA-N 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- 239000000654 additive Substances 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 238000001311 chemical methods and process Methods 0.000 description 1

- VNNRSPGTAMTISX-UHFFFAOYSA-N chromium nickel Chemical compound [Cr].[Ni] VNNRSPGTAMTISX-UHFFFAOYSA-N 0.000 description 1

- ORTQZVOHEJQUHG-UHFFFAOYSA-L copper(II) chloride Chemical compound Cl[Cu]Cl ORTQZVOHEJQUHG-UHFFFAOYSA-L 0.000 description 1

- 230000001186 cumulative effect Effects 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000009713 electroplating Methods 0.000 description 1

- 238000011156 evaluation Methods 0.000 description 1

- 238000000227 grinding Methods 0.000 description 1

- 230000017525 heat dissipation Effects 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- XEEYBQQBJWHFJM-UHFFFAOYSA-N iron Substances [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 1

- FBAFATDZDUQKNH-UHFFFAOYSA-M iron chloride Chemical compound [Cl-].[Fe] FBAFATDZDUQKNH-UHFFFAOYSA-M 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910001120 nichrome Inorganic materials 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 230000002265 prevention Effects 0.000 description 1

- 230000009993 protective function Effects 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 238000005215 recombination Methods 0.000 description 1

- 230000006798 recombination Effects 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000009877 rendering Methods 0.000 description 1

- 238000011160 research Methods 0.000 description 1

- 238000005389 semiconductor device fabrication Methods 0.000 description 1

- 238000009281 ultraviolet germicidal irradiation Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/44—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the coatings, e.g. passivation layer or anti-reflective coating

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/005—Processes

- H01L33/0095—Post-treatment of devices, e.g. annealing, recrystallisation or short-circuit elimination

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/36—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes

- H01L33/38—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes with a particular shape

- H01L33/382—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes with a particular shape the electrode extending partially in or entirely through the semiconductor body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/62—Arrangements for conducting electric current to or from the semiconductor body, e.g. lead-frames, wire-bonds or solder balls

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/64—Heat extraction or cooling elements

- H01L33/647—Heat extraction or cooling elements the elements conducting electric current to or from the semiconductor body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2933/00—Details relating to devices covered by the group H01L33/00 but not provided for in its subgroups

- H01L2933/0008—Processes

- H01L2933/0025—Processes relating to coatings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2933/00—Details relating to devices covered by the group H01L33/00 but not provided for in its subgroups

- H01L2933/0008—Processes

- H01L2933/0033—Processes relating to semiconductor body packages

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2933/00—Details relating to devices covered by the group H01L33/00 but not provided for in its subgroups

- H01L2933/0008—Processes

- H01L2933/0033—Processes relating to semiconductor body packages

- H01L2933/0066—Processes relating to semiconductor body packages relating to arrangements for conducting electric current to or from the semiconductor body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2933/00—Details relating to devices covered by the group H01L33/00 but not provided for in its subgroups

- H01L2933/0008—Processes

- H01L2933/0033—Processes relating to semiconductor body packages

- H01L2933/0075—Processes relating to semiconductor body packages relating to heat extraction or cooling elements

Definitions

- the present invention relates to a method for manufacturing a semiconductor device.

- the present invention relates to a method of separating a semiconductor device from a wafer using wet etching without dicing or scribing when fabricating the semiconductor device.

- the present invention is derived from the research conducted as part of the knowledge economy technology innovation project (parts material technology development project) of the Ministry of Knowledge Economy and Korea Institute of Industrial Technology Evaluation and Management. [Task control number: 10036981, Task name: High color rendering LED for digital display -BLU panel].

- fabrication and isolation techniques for semiconductor devices include depositing layers to form multiple semiconductor devices on a wafer substrate and then separating the individual semiconductor devices using mechanical or chemical techniques.

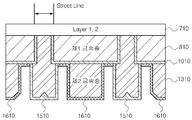

- FIG. 1 shows an example of a wafer configuration and a street line for separating semiconductor devices from the wafer.

- a conventional wafer 100 may be composed of three layers.

- the first layer 110 is a device layer in which impurity semiconductors such as Si and GaN are formed.

- the third layer 130 is a layer formed by plating some functions of the second layer 120.

- the fourth layer 140 is a layer formed by plating for heat dissipation, wiring, grounding, and mechanical support.

- Process yield issues are becoming more important for semiconductor devices with rigid substrate materials such as GaN on sapphire or GaN materials on SiC.

- separation yield is greatly influenced by any cracks or defects generated by substrate grinding and polishing. If the cutting line passes through the defective area, the device separation yield is very low.

- the back end process yield for manufacturing GaN-based semiconductors is as low as less than 50%, and the front end manufacturing process yield is typically in the range of 90% or more.

- the device performance after device separation may be significantly degraded.

- LED device sidewalls that emit light may be damaged by abrasive cutting action during device separation, which is a major cause of light output reduction after device separation.

- the average die separation processing time for GaN / sapphire LED devices with approximately 10,000-12,000 devices per wafer is approximately 40 minutes to 1 hour according to conventional separation methods. This can only handle 24 to 36 wafers (700 to 1,000 wafers / month) per day when one device separation machine is operating 24 hours / day. In order to achieve commercially desired factory output, a large number of machinery and significant significant equipment investments are required.

- the main consumable is a laser source.

- the laser source gas In order to maintain a constant laser beam energy, the laser source gas must be regularly recharged. Laser sources are one of the most expensive components in laser scribing systems.

- the third layer 130 or the fourth layer 140 that is relatively thicker than the first layer 110 has a problem in that side corrosion may occur seriously when cutting through etching.

- the present invention has been made to solve the above problems of the prior art, and an object thereof is to provide a method of manufacturing a semiconductor device and separating the semiconductor devices from a wafer.

- an object of the present invention is to provide a method for manufacturing a semiconductor device, and separating the semiconductor devices using wet etching.

- an object of the present invention is to plate an etch barrier on the metal layer of the wafer so that side etching of the metal layer does not occur when the semiconductor devices are separated from the wafer through a wet etching method.

- a semiconductor device manufacturing method comprises the steps of forming a semiconductor device layer for generating light by the current; And forming at least one metal layer on the semiconductor device layer to provide mechanical support, wherein forming the at least one metal layer comprises a street line that is a boundary for separating the semiconductor device layer into individual semiconductor devices. Forming the at least one metal layer on which the etch barrier is plated so as to prevent side etching of the metal layer when wet etching.

- the method of manufacturing a semiconductor device may include reflection, light block layer (CBL), etching barrier, diffusion barrier, adhesion, and the like before forming the at least one metal layer.

- the method may further include forming a thin metal layer or thin metal layer by vacuum deposition (hereinafter, referred to as a metal thin film layer) having a function including some or all of electrical transfer or spreading.

- the forming of the at least one metal layer may include forming the at least one metal layer on which the etch protection layer is plated, on the metal thin film layer for preventing diffusion.

- the forming of the at least one metal layer on the semiconductor device layer may include forming a first metal layer on which the first etch protection layer is plated on the semiconductor device layer to prevent side corrosion when the street line is wet etched. Forming; And forming a second metal layer plated with a second etching protection layer to prevent side corrosion when the street line is wet etched, according to a second pattern.

- the forming of the at least one metal layer on the semiconductor device layer may include forming a first metal layer and a second metal layer step by step into a first pattern and a second pattern, and then performing side corrosion when wet etching the street line.

- An etch protection layer is formed by collectively plating the first metal layer and the second metal layer to prevent the plating, and a plating is performed on the street line and the first and second metal layers as a whole. It may also include the step.

- the forming of the at least one metal layer on the semiconductor device layer may include forming a first metal layer and a second metal layer step by step into a first pattern and a second pattern, and then performing side corrosion when wet etching the street line.

- An etch protection layer is formed by plating on the first metal layer and the second metal layer in order to prevent it, and when filling the street line with the third metal plating, the surface and sidewalls of the second metal layer are covered with a third pattern. It may also include plating only the portions corresponding to the street lines.

- the forming of the first metal layer on the semiconductor device layer may include forming a total thickness of the first metal layer and the second metal layer to be greater than or equal to 80 ⁇ m based on a minimum thickness, and having a hardness of 100 to 100 mm. In the case of 200 Hv, the first metal layer may be formed to be at least 40 ⁇ m.

- the first metal may be copper (Cu) or a copper alloy or may include a single or a plurality of thermal stress relief plating layers inserted in the middle of a main metal such as copper or a copper alloy.

- the forming of the second metal layer may include forming a second photoresist in an inversion region of the second pattern; Plating a region where the second photoresist is not formed with a second metal according to the second pattern; Removing the second photo resist; Forming a third photoresist over a second metal located at the street line; Plating the second etching protection layer on a second metal on which a third photoresist is not formed; And removing the third photoresist.

- the forming of the second metal layer may include forming a second photoresist in the inversion region of the second pattern; Plating a region where the second photoresist is not formed with a second metal according to the second pattern; Removing the second photoresist, subjecting the first metal layer and the second metal layer to an etch-proof plating, a third metal on the street line and the first and second metal layers, or a third metal or the first and second metal layers. And collectively plating with the same metal as the metal.

- the forming of the second metal layer may include forming a second photoresist in the inversion region of the second pattern; Plating a region where the second photoresist is not formed with a second metal according to the second pattern; Removing the second photoresist, subjecting the first metal layer and the second metal layer to anti-etch plating, covering the surface and the sidewalls of the second metal layer with a third pattern photoresist and the first metal layer Filling the street line region located between the photoresist and the photoresist with a third metal plating or the same metal plating as the first and second metals.

- the second metal may be copper (Cu) or a copper alloy, or may include a single or multiple thermal stress relaxation plating layer interposed between a main metal such as copper or a copper alloy.

- the third metal may be a metal having the same material as that of the first metal.

- the semiconductor device manufacturing method may further include: cutting a street line of the semiconductor device layer through a physical method or a chemically wet etching method; And a second cutting step of wet etching the metal, which is not plated, by the etch protective layer existing on the street line between the one or more metal layers formed on the semiconductor device layer.

- the forming of the pinned layer may include applying a protective PR including a positive photoresist on the surface of the semiconductor device; And attaching a UV tape on the positive photoresist.

- Applying the protective PR including the positive photoresist may be applied so that the thickness of the positive photoresist is 3um or more from the surface of the device.

- the protective PR may be applied to fill the cut bones between the semiconductor devices that are separately separated.

- an expanding tape having an adhesive force higher than that of the positive PR and the UV tape of the device surface fixing layer is adhered onto the second metal layer to form a fixing layer tape. Lumping individual elements cut into the expanding tape; And removing and cleaning the fixed layer.

- the present invention relates to a method for fabricating a semiconductor device and separating the semiconductor devices using wet etching.

- the present invention relates to a method for fabricating semiconductor devices by wet etching by plating an etch barrier on a metal layer of the wafer. Side etching of the metal layer did not occur when the separation was performed.

- the present invention separates the semiconductor devices by using wet etching, the processor yield is higher, the performance deterioration of the semiconductor devices is lower, and the cost is relatively lower than the mechanical separation technology.

- FIG. 1 shows an example of a wafer configuration and a street line for separating semiconductor devices from the wafer.

- FIG. 2 is a cross-sectional view illustrating an example of a wafer on which semiconductor devices are formed in accordance with an embodiment of the present invention.

- FIG. 3 is a flowchart illustrating a method of manufacturing a semiconductor device in accordance with an embodiment of the present invention.

- FIG. 4 is a flowchart illustrating a method of forming a first metal layer according to an embodiment of the present invention.

- FIG. 5 shows a flowchart illustrating a method of forming a second metal layer according to an embodiment of the present invention.

- FIG. 6 is a flowchart illustrating a method of forming a pinned layer according to an embodiment of the present invention.

- FIG. 7 is a cross-sectional view of a wafer on which a first photoresist is formed in accordance with an embodiment of the invention.

- FIG. 8 is a cross-sectional view of a wafer plated with a first metal in accordance with an embodiment of the present invention.

- FIG. 9 is a cross-sectional view of a wafer from which a first photoresist has been removed in accordance with an embodiment of the present invention.

- FIG. 10 is a cross-sectional view of a wafer on which a first etch protection layer is plated on a first metal layer according to an embodiment of the present invention.

- FIG. 14 is a cross-sectional view of a wafer from which a second photoresist has been removed in accordance with an embodiment of the present invention.

- FIG. 15 illustrates a cross-sectional view of a wafer in which a third photoresist is formed over a second metal located on a street line in accordance with an embodiment of the present invention.

- 16 is a cross-sectional view of a wafer on which a second etching protection layer is plated on a second metal layer according to an embodiment of the present invention.

- 17 is a cross-sectional view of a wafer from which a third photoresist has been removed in accordance with an embodiment of the present invention.

- FIG. 18 is a cross-sectional view of the street lines of the first and second layers cut according to the exemplary embodiment of the present invention.

- 19 is a cross-sectional view of a wafer on which a pinned layer is formed in accordance with an embodiment of the present invention.

- FIG. 20 illustrates a cross-sectional view of a wafer in which a metal not plated with an etch protective layer is removed by wet etching according to an embodiment of the present invention.

- Figure 21 illustrates a cross-sectional view of a wafer with an expanding tape adhered on a second metal layer in accordance with an embodiment of the present invention.

- FIG. 24 is a cross-sectional view of a wafer on which an etch protection layer and a plurality of metal layers are plated according to another embodiment of the present invention.

- a semiconductor device manufacturing method comprises the steps of forming a semiconductor device layer for generating light by the current; And forming at least one metal layer on the semiconductor device layer to provide mechanical support, wherein forming the at least one metal layer comprises a street line that is a boundary for separating the semiconductor device layer into individual semiconductor devices. Forming the at least one metal layer on which the etch barrier is plated so as to prevent side etching of the metal layer when wet etching.

- the method of manufacturing a semiconductor device may include reflection, light block layer (CBL), etching barrier, diffusion barrier, adhesion, and the like before forming the at least one metal layer.

- the method may further include forming a thin metal layer or thin metal layer by vacuum deposition (hereinafter, referred to as a metal thin film layer) having a function including some or all of electrical transfer or spreading.

- the forming of the at least one metal layer may include forming the at least one metal layer on which the etch protection layer is plated, on the metal thin film layer for preventing diffusion.

- the forming of the at least one metal layer on the semiconductor device layer may include forming a first metal layer on which the first etch protection layer is plated on the semiconductor device layer to prevent side corrosion when the street line is wet etched. Forming; And forming a second metal layer plated with a second etching protection layer to prevent side corrosion when the street line is wet etched, according to a second pattern.

- the forming of the at least one metal layer on the semiconductor device layer may include forming a first metal layer and a second metal layer step by step into a first pattern and a second pattern, and then performing side corrosion when wet etching the street line.

- An etch protection layer is formed by collectively plating the first metal layer and the second metal layer to prevent the plating, and a plating is performed on the street line and the first and second metal layers as a whole. It may also include the step.

- the forming of the at least one metal layer on the semiconductor device layer may include forming a first metal layer and a second metal layer step by step into a first pattern and a second pattern, and then performing side corrosion when wet etching the street line.

- An etch protection layer is formed by plating on the first metal layer and the second metal layer in order to prevent it, and when filling the street line with the third metal plating, the surface and sidewalls of the second metal layer are covered with a third pattern. It may also include plating only the portions corresponding to the street lines.

- the forming of the first metal layer on the semiconductor device layer may include forming a total thickness of the first metal layer and the second metal layer to be greater than or equal to 80 ⁇ m based on a minimum thickness, and having a hardness of 100 to 100 mm. In the case of 200 Hv, the first metal layer may be formed to be at least 40 ⁇ m.

- the forming of the second metal layer may include forming a second photoresist in an inversion region of the second pattern; Plating a region where the second photoresist is not formed with a second metal according to the second pattern; Removing the second photo resist; Forming a third photoresist over a second metal located at the street line; Plating the second etching protection layer on a second metal on which a third photoresist is not formed; And removing the third photoresist.

- the forming of the second metal layer may include forming a second photoresist in the inversion region of the second pattern; Plating a region where the second photoresist is not formed with a second metal according to the second pattern; Removing the second photoresist, subjecting the first metal layer and the second metal layer to an etch-proof plating, a third metal on the street line and the first and second metal layers, or a third metal or the first and second metal layers. And collectively plating with the same metal as the metal.

- the forming of the second metal layer may include forming a second photoresist in the inversion region of the second pattern; Plating a region where the second photoresist is not formed with a second metal according to the second pattern; Removing the second photoresist, subjecting the first metal layer and the second metal layer to anti-etch plating, covering the surface and the sidewalls of the second metal layer with a third pattern photoresist and the first metal layer Filling the street line region located between the photoresist and the photoresist with a third metal plating or the same metal plating as the first and second metals.

- the second metal may be copper (Cu) or a copper alloy, or may include a single or multiple thermal stress relaxation plating layer interposed between a main metal such as copper or a copper alloy.

- the third metal may be a metal having the same material as that of the first metal.

- the semiconductor device manufacturing method may further include: cutting a street line of the semiconductor device layer through a physical method or a chemically wet etching method; And a second cutting step of wet etching the metal, which is not plated, by the etch protective layer existing on the street line between the one or more metal layers formed on the semiconductor device layer.

- the method may further include forming a pinned layer for fixing the chips in the wafer.

- the forming of the pinned layer may include applying a protective PR including a positive photoresist on the surface of the semiconductor device; And attaching a UV tape on the positive photoresist.

- Applying the protective PR including the positive photoresist may be applied so that the thickness of the positive photoresist is 3um or more from the surface of the device.

- the protective PR may be applied to fill the cut bones between the semiconductor devices that are separately separated.

- an expanding tape having an adhesive force higher than that of the positive PR and the UV tape of the device surface fixing layer is adhered onto the second metal layer to form a fixing layer tape. Lumping individual elements cut into the expanding tape; And removing and cleaning the fixed layer.

- FIG. 2 is a cross-sectional view illustrating an example of a wafer on which semiconductor devices are formed in accordance with an embodiment of the present invention.

- the wafer 200 may be largely composed of four layers.

- the second layer 220 is formed between the first layer 210, which is an impurity semiconductor element layer, and the third layer 230, which corresponds to the metal plating layer.

- a metal thin film layer having a function including some or all of etching barrier, diffusion barrier, adhesion, and electrical transfer or spreading.

- the second layer 220 is platinum (Pt; platinum), gold (Au Gold), silver (Ag: silver), chromium (Cr; chromium ), titanium (Ti; titanium) , molybdenum (Mo; molybdenum) , Tungsten (W; tungsten) , may be composed of a material containing at least one of nickel (Ni; nickel ) and can be optionally omitted because not all materials are essential components.

- the third layer 230 is a layer in which some functions of the second layer 220 are formed by plating.

- the third layer 230 is referred to as a third layer or a first metal layer in the following description.

- the fourth layer 240 is a layer formed by plating for heat radiation, wiring, grounding, and mechanical support.

- the fourth layer 240 is referred to as a fourth layer or a second metal layer in the following description.

- a semiconductor device layer that generates light by a current is formed (S310), and a diffusion prevention layer that prevents diffusion of metal into the semiconductor device layer is formed on the semiconductor device layer (S320). .

- FIG. 4 is a flowchart illustrating a method of forming a first metal layer according to an embodiment of the present invention.

- the first photoresist (PR) is formed at the street line positions of the first and second layers 710, which are the semiconductor device layer and the diffusion barrier layer, as in the example of FIG. 7.

- 720 is formed (S410).

- the first photoresist 720 serves to prevent the first metal from being plated at the street line position.

- 7 is a cross-sectional view of a wafer on which a first photoresist is formed in accordance with an embodiment of the invention.

- the region in which the first photoresist 720 is not formed is plated with the first metal 810 according to the first pattern (S420).

- the first metal 810 is composed of copper (Cu) or a copper alloy, and in the case of pure copper, the Vickers hardness of the first metal 810 is preferably 120 Hv or less.

- 8 is a cross-sectional view of a wafer plated with a first metal in accordance with an embodiment of the present invention.

- the method of fabricating a semiconductor device forms a second metal layer plated with a second etching protection layer on the first metal layer according to a second pattern to prevent side corrosion when wet etching the street line. S340).

- FIG. 5 shows a flowchart illustrating a method of forming a second metal layer according to an embodiment of the present invention.

- the second photoresist 1110 is formed in the inverted region of the second pattern (S510).

- the second photoresist 1110 is formed to have a predetermined area around a street line, which is an inversion region of the second pattern, and serves to distinguish between a region to be wet etched and a region not to be wet etched when the semiconductor is separated by wet etching. And it may be formed as shown in the plan view of FIG.

- the main component of the first and second metal layers is copper (Cu) or a copper alloy

- an etchant using pure copper chloride (CuCl 2), iron chloride (Cu 2 Fe 3), or a mixture of the two may be used. It is possible to use nitrate based etchant.

- the etching protection layer Pure Au (gold) or NiAu, Pt, Pd, or the like may be used.

- the etching protection layer is Pure Au, it is preferable to have a thickness of 0.5 ⁇ m or more and 1.5 ⁇ m or less.

- the etch protective layer needs to have a thickness of 0.5 ⁇ m or more in order to perform an etch protection function, and preferably has a thickness of 1.5 ⁇ m or less in order to maintain the bond between the etch protection layer and the first and second metal layers smoothly.

- the etching protective layer is NiAu

- a range of about 0.5 ⁇ m Ni and about 1.0 ⁇ m Au is preferable, and Ni is preferably not thicker than 0.5 ⁇ m.

- the reason for the selection for the optimum thickness range is similar to that described previously.

- a third metal which serves to relieve stress between the device and the metal layer, may be additionally inserted as a single layer or multiple layers between the semiconductor device layer and the metal layer, or between the plurality of metal layers.

- the third metal may be formed of a group consisting of at least one combination of the above.

- the third metal is intended for stress relaxation and relaxation of the thermal expansion coefficient, it is possible to select a material having a smaller thermal expansion coefficient than Cu and larger than GaN.

- a material having a compressive stress is preferable as the third metal, and Ni, Cr, NiCo alloy, or Mo, W or a plating layer containing these materials is used. Can be inserted.

- Ni is preferably 0.2um or more for each layer, and Cr is 1um or more based on the cumulative thickness.

- a NiCo alloy can be inserted into the stress relaxation layer (third metal).

- the proportion of Co is preferably and important factor to set the content of Co and the current density so that the stress of the plated alloy layer is in zero stress.

- first metal layer and the second metal layer is plated with a pure copper or a pure copper plating and a metal having a strength within a range of + /-10% and the total thickness is formed to be more than 80um based on the minimum thickness portion, 1

- the metal layer is preferably formed to be at least 40um.

- the first metal layer may include copper (Cu) or copper alloy plating, and has a property in which stress by plating is in a range of ⁇ 0.2 kgf / mm 2 to + 1.0, kgf / mm 2.

- FIG. 11 is a cross-sectional view of a wafer on which a second photoresist is formed in accordance with an embodiment of the invention.

- 12 is a plan view of a wafer on which a second photoresist is formed in accordance with an embodiment of the invention.

- a dotted line is a reference line which shows the cross section of the sectional drawing of FIG.

- the second metal 1310 is made of copper (Cu) or a copper alloy, and in the case of pure copper, the Vickers hardness of the second metal 1310 is preferably 120 Hv or more.

- 13 is a cross-sectional view of a wafer plated with a second metal in accordance with an embodiment of the present invention.

- the second metal layer forming method S340 removes the second photoresist 1110 as illustrated in FIG. 14.

- 14 is a cross-sectional view of a wafer from which a second photoresist has been removed in accordance with an embodiment of the present invention.

- a third photoresist 1510 is formed on the second metal located on the street line (S540).

- the third photoresist 1510 serves to prevent the second etch protective layer from being plated on the region to be wet etched when the semiconductor is separated by the wet etch.

- 15 illustrates a cross-sectional view of a wafer in which a third photoresist is formed over a second metal located on a street line in accordance with an embodiment of the present invention.

- the second metal layer forming method S340 may plate the second etching protection layer 1610 on the second metal on which the third photoresist 1510 is not formed, as shown in the example of FIG. 16.

- 16 is a cross-sectional view of a wafer on which a second etching protection layer is plated on a second metal layer according to an embodiment of the present invention.

- the second metal layer forming method S340 removes the third photoresist 1510 as shown in FIG. 17.

- 17 is a cross-sectional view of a wafer from which a third photoresist has been removed in accordance with an embodiment of the present invention.

- the first photoresist 720, the second photoresist 1110, and the third photoresist 1610 are divided according to the order of manufacturing a semiconductor device.

- the first photoresist 720, the second photoresist 1110 and the third photoresist 1610 may be the same material or at least one may be a different material.

- the semiconductor device manufacturing method cuts the street lines of the first and second layers 710 through physical (mechanical) methods or chemically wet etching as in the example of FIG. 18 (S350).

- 18 is a cross-sectional view of the street lines of the first and second layers cut according to the exemplary embodiment of the present invention.

- FIG. 6 is a flowchart illustrating a method of forming a pinned layer according to an embodiment of the present invention.

- a positive photoresist (Positive PR) 1910 is coated on a surface of a semiconductor device (S610).

- the fixed layer forming method (S360) is formed to have a higher etching depth than the depth of the cut device to protect the sidewalls and surfaces of the layers 1 and 2 710 which have been chemically cut. It should be applied at least 3um in consideration of the thickness of the devices to be commercialized because it can be a protective function of the side wall and the surface.

- the UV tape 1920 that loses the adhesive strength when the ultraviolet ray is exposed on the positive photoresist 1910 is adhered (S620).

- UV tapes allows the fixed layer to be easily separated when the separated chips are transferred onto an expanding tape, so the UV tapes that are exposed to the UVs lose their adhesion with the positive photoresist and are easily separated.

- the pinned layer is formed using the positive photoresist 1910 and the ultraviolet tape 1920, but in addition, the pinned layer is formed by using another material that can fix the semiconductor device during wet etching of the metal layer while protecting the chip surface. It may be formed.

- the material of the fixed layer is preferably a material that can be easily removed later.

- the photoresist when UV tape is applied together as a fixed layer on the PR, the photoresist must be positive type to have a property of melting when exposed to ultraviolet rays. If negative type photoresist is used, the photoresist hardens and adversely affects.

- the semiconductor device is separated by wet etching a metal that is not plated with an etch protection layer present on the street lines of the one or more metal layers (S370).

- FIG. 20 illustrates a cross-sectional view of a wafer in which a metal not plated with an etch protective layer is removed by wet etching according to an embodiment of the present invention.

- step S350 is performed before the step S370, but the order of execution may be reversed. However, it is because the process of the process is simpler to perform the step of S350 first. If performing the step S370 first simplifies the process, the step S370 may be performed first.

- some thin films may be removed from the plurality of thin films of layers 1 and 2 in step S350, and the thin films left after the step S370 may be removed.

- Figure 21 illustrates a cross-sectional view of a wafer with an expanding tape adhered on a second metal layer in accordance with an embodiment of the present invention.

- FIG. 22 is a cross-sectional view of a wafer from which a pinned layer has been removed in accordance with an embodiment of the present invention.

- FIG. 23 is a cross-sectional view of a wafer on which an etch protection layer and a plurality of metal layers are plated according to another embodiment of the present invention.

- the first metal layer 2310 is plated on the first and second layers 710, which are the semiconductor device layer and the diffusion protection layer, according to a first pattern.

- the first pattern is a pattern corresponding to the street line.

- the second metal layer 2320 is plated on the first metal layer 2310 according to the second pattern.

- the first metal layer 2310 and the second metal layer 2320 may include copper or a copper alloy in common, and the range of physical properties that the first metal layer 2310 and the second metal layer 2320 may have is described above. As shown.

- the second pattern is similar to the first pattern, but the area of the second pattern is smaller than the area of the first pattern, as described above.

- an etching protection layer 2330 is plated on the first metal layer 2310 and the second metal layer 2320.

- the third metal layer 2340 is plated on the etch protection layer 2330, and in particular, a portion corresponding to the street line left empty by the etch protection layer 2330 is filled by the third metal layer 2340. do.

- the space between the etch protection layer 2330 corresponding to the street line is filled by the third metal layer 2340 so that the first metal layers 2310 and the second metal layers 2320 may be physically connected to provide mechanical support. This allows the process to proceed in the form of a single wafer.

- a first metal layer 2410 is plated according to a first pattern on layers 1 and 710, which are a semiconductor device layer and a diffusion protection layer, and then on the first metal layer 2410 according to a second pattern.

- the second metal layer 2420 is plated on it. Since the etching protection layer 2430 is plated is the same as the embodiment of FIG.

- a semiconductor device manufacturing method comprises the steps of forming a semiconductor device layer for generating light by the current; Forming at least one metal layer on the semiconductor device layer to provide mechanical support; A first cutting step of cutting the street line of the semiconductor device layer through a physical method or a chemical wet etching method; And a second cutting step of wet etching the metal, which is not plated, by the etch protective layer present on the street line of the at least one metal layer.

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Dicing (AREA)

Abstract

반도체 소자 제조 방법을 개시한다. 본 발명의 실시예에 따른 반도체 소자 제조 방법은 전류에 의해 빛을 발생시키는 반도체 소자층을 형성하는 단계; 상기 반도체 소자층 위에 기계적 지지를 제공하는 하나 이상의 금속층을 형성하는 단계; 상기 반도체 소자층의 스트리트 라인을 물리적 방법 또는 화학적으로 습식 식각 방법을 통해 절단하는 제1 절단 단계; 및 상기 하나 이상의 금속층의 상기 스트리트 라인 상에 존재하는 식각 보호층이 도금되지 않은 금속을 습식 식각해서 절단하는 제2 절단 단계를 포함할 수 있다. 이때, 상기 하나 이상의 금속층을 형성하는 단계는 상기 반도체 소자층을 개별 반도체 소자로 분리하기 위한 경계선인 스트리트 라인(street line)을 습식 식각(wet etching) 할 때 상기 금속층의 측면부식(side etching)이 발생하지 않도록 식각 보호층(etch barrier)이 도금된 상기 하나 이상의 금속층을 상기 반도체 소자층 위에 형성하는 단계를 포함해서 습식 식각을 통한 반도체 소자 분리시 발생하는 측면부식을 억제할 수 있다.

Description

본 발명은 반도체 소자의 제조 방법에 관한 것이다. 구체적으로, 본 발명은 반도체 소자를 제조할 때 다이싱(dicing) 또는 스크라이빙(scribing) 하지 않고 습식 식각(wet etching)을 이용해서 웨이퍼에서 반도체 소자를 분리하는 방법에 관한 것이다.

본 발명은 지식경제부 및 한국산업기술평가관리원의 지식경제 기술혁신사업(부품소재기술개발사업)의 일환으로 수행한 연구로부터 도출된 것이다 [과제관리번호 : 10036981, 과제명 : 디지털 디스플레이용 고연색 LED-BLU 패널].

종래, 반도체 소자의 제조 및 분리 기술은, 층들을 증착하여 웨이퍼 기판 상에 다수의 반도체 소자들을 형성한 후 기계적인 기법 또는 화학적인 기법을 사용하여 개별 반도체 소자들을 분리하는 것을 포함한다.

도 1은 웨이퍼의 구성과 웨이퍼에서 반도체 소자들을 분리하기 위한 스트리트 라인의 예를 나타낸다.

도 1(a)는 웨이퍼의 단면도에 표시된 스트리트 라인의 예를 나타내고, 도 1(b)는 웨이퍼의 평면도에 표시된 스트리트 라인의 예를 나타낸다.

도 1(a)를 참조하면, 종래의 웨이퍼(100)는 크게 3개의 레이어로 구성될 수 있다. 제1 레이어(110)는 Si, GaN 등 불순물 반도체가 형성되어 있는 소자 층이다.

제3 레이어(130)는 제2 레이어(120)의 일부 기능을 도금 방식으로 형성한 층이다. 제4 레이어(140)는 방열, 배선, 접지, 기계적 지지를 위해 도금으로 형성한 층이다.

웨이퍼(100)에서 반도체 소자를 분리하는 기계적인 기법에는 대표적으로 기판을 다이싱 또는 스크라이빙함으로써 개별적인 반도체 소자들을 분리한다. 다이싱은 대표적으로 다이아몬드 톱, 다이아몬드 스크라이버 또는 레이저에 의해 행해지며, 이는 매우 고가의 기계에 의해 수행되는 시간 소모적인 프로세스이다. 종래 기술에는 프로세스 수율 문제, 장치 성능 문제 및 프로세싱 비용 문제를 포함하는 여러가지 공지된 문제점들이 발생 할 수 있다.

먼저 프로세스 수율 문제를 살펴보면, 종래의 다이싱 방법, 스크라이빙 방법, 및 레이저 스크라이빙 방법과 같은 기계적인 장치 분리 방법에 따르면, 각 개별 반도체 소자는 선택된 방법에 의해 반도체 소자들 사이에서 아래 도 2와 같은 그리드 라인 또는 스트리트 라인(street line) 을 따라 컷팅함으로써 분리된다. 이는 각 스트리트 라인이 한번에 하나씩 순차적으로 커팅되기 때문에 느린 프로세스이다.

프로세스 수율 문제는 사파이어 상의 GaN 또는 SiC 상의 GaN 재료와 같은 경질 기판 재료를 갖는 반도체 장치에 대해 더욱 중요해진다. 또한, 분리 수율은 기판 그라인딩 및 폴리싱에 의해 생성된 임의의 크랙 또는 결함에 의해 크게 영향을 받는다. 커팅 라인이 결함이 있는 영역을 통과할 경우, 장치 분리 수율은 매우 낮아진다.

따라서, 장치 분리는 전체 반도체 장치 제조 프로세스들 중에서 가장 지루하고 낮은 수율의 프로세스라고 알려져 있다. 실용상, GaN계 반도체를 제조하기 위한 백엔드 프로세스 수율은 50% 미만만큼 낮고, 프론트엔드 제조 프로세스 수율은 대표적으로 90% 이상의 범위내에 있다.

다음으로 장치 성능 문제를 살펴보면, 다이싱 및 스크라이빙의 물리적인 연마 작용으로 인해, 장치 분리 이후의 장치 성능은 상당히 열화될 수도 있다. 예컨대, 광이 방출하는 LED 장치 측벽은 장치 분리동안 연마 커팅 작용에 의해 손상될 수도 있으며, 이는 장치 분리 이후에 광 출력 감소의 주요 원인이 된다.

레이저 스크라이빙의 경우, 장치 분리는 고강도 레이저 빔에 의해 기판 재료를 용융시킴으로써 달성된다. 따라서, 용융된 기판 재료가 장치 측벽에 축적되는 경우가 있으며, 이는 또한 LED 장치의 광 출력을 저하시키게 된다.

마지막으로 프로세싱 비용 문제를 살펴보면, 웨이퍼마다 대략 10,000~12,000 장치를 갖는 GaN/사파이어 LED 장치에 대한 평균 다이 분리 프로세싱 시간은, 종래의 분리 방법에 의하면 대략 40분 내지 1시간이다. 이는, 하나의 장치 분리 기계가 24 시간/하루 동작할 경우, 매일 24 내지 36개의 웨이퍼 (700~1,000개의 웨이퍼/월)만을 취급할 수 있다. 상업적으로 소망하는 공장 생산량을 달성하기 위해서는, 다수의 기계 및 상당한 중요 장비 투자가 필요하다.

또한, 다이싱 기계용 다이아몬드 커팅 휠 및 스크라이빙 기계용 다이아몬드 팁은 매우 고가의 소모품이기 때문에, 종래의 다이 분리 프로세스에 관련된 소모품 비용이 상당하다. 그리고, 레이저 스크라이빙의 경우, 주요 소모품은 레이저원이다. 일정한 레이저 빔 에너지를 유지하기 위해서는, 레이저원 가스가 정기적으로 재충전되어야만 한다. 레이저원은 레이저 스크라이빙 시스템에서 가장 고가의 구성요소 중 하나이다.

반도체 소자를 분리하는 기계적인 기법의 이러한 문제점을 화학적인 기법인 습식 식각(wet etching)을 이용해서 일정부분 해소할 수 있다.

하지만 습식 식각(wet etching)을 이용한 반도체 소자를 분리하는 기법에도 측면부식(side etch)의 문제점이 존재한다.

도 1(a)를 살펴보면, 제1레이어(110)는 두께가 수 um 내외이므로 습식 식각을 통한 절단시 측면부식(side etch)이 발생하더라도 크게 문제가 되지 않는 정도이다.

하지만, 제1 레이어(110)에 비해 상대적으로 두께가 두꺼운 제3 레이어(130) 또는 제4 레이어(140)는 식각을 통한 절단시 측면부식이 심각하게 발생할 수 있는 문제가 있다.

따라서, 습식 식각을 통해 반도체 소자를 분리시 측면부식의 문제를 해결하는 방법이 요구된다.

종래의 반도체 소자의 제조 및 분리 기술에 대한 설명은 한국공개특허 제2007-0085374호 에 기술된 바 있다.

종래의 반도체 소자의 제조 및 분리 기술은 습식 식각을 통한 절단시 측면부식에 대한 대비책을 고려하지 않고 있다. 따라서 종래의 반도체 소자의 제조 및 분리 기술에서는 측면부식이 발생할 가능성이 존재한다.

또한, 종래의 반도체 소자의 분리 기술은 금속층의 절단을 용이하도록 포토 레지스트(PR: Photo Resist)를 사용하고 있다. 하지만 포토 레지스트의 두께는 일정하게 제어되기 어려우므로 포토 레지스트를 제거하지 않고 웨이퍼 캐리어를 적층하는 경우, 포토 레지스트를 평탄화하는 등의 추가 작업이 발생하는 등의 제조공정에서 어려움이 발생할 수 있다.

본 발명은 상기와 같은 종래 기술의 문제점을 해결하고자 도출된 것으로서, 반도체 소자를 제조하고 웨이퍼에서 반도체 소자들을 분리하는 방법을 제공하는 것을 목적으로 한다.

구체적으로, 본 발명은 반도체 소자를 제조하고, 습식 식각(wet etching)을 이용해서 반도체 소자들을 분리하는 방법을 제공하는 것을 목적으로 한다.

또한, 본 발명은 웨이퍼의 금속층에 식각 보호층(etch barrier)을 도금해서 습식 식각 방법을 통해서 웨이퍼에서 반도체 소자들을 분리할 때 금속층의 측면부식(side etching)이 발생하지 않도록 하는 것을 목적으로 한다.

상기와 같은 목적을 달성하기 위하여, 본 발명의 일 실시 예에 따른 반도체 소자 제조 방법은 전류에 의해 빛을 발생시키는 반도체 소자층을 형성하는 단계; 및 상기 반도체 소자층 위에 기계적 지지를 제공하는 하나 이상의 금속층을 형성하는 단계를 포함하고, 상기 하나 이상의 금속층을 형성하는 단계는 상기 반도체 소자층을 개별 반도체 소자로 분리하기 위한 경계선인 스트리트 라인(street line)을 습식 식각(wet etching) 할 때 상기 금속층의 측면부식(side etching)이 발생하지 않도록 식각 보호층(etch barrier)이 도금된 상기 하나 이상의 금속층을 상기 반도체 소자층 위에 형성하는 단계를 포함한다.

상기 반도체 소자 제조 방법은 상기 하나 이상의 금속층을 형성하는 단계 이전에, 빛의 반사(reflection), CBL(Current Block Layer), 에칭 방어(Etch Barrier), 확산방지(diffusion barrier), 밀착(adhesion) 및 전기전도 혹은 확장(electrical transfer, or spreading) 등의 일부 또는 모두를 포함하는 기능을 갖는 진공 증착 금속박막층 (thin metal layer or thin metal layer by vacuum deposition, 이하 금속 박막층) 형성 단계를 더 포함하고, 이때, 상기 하나 이상의 금속 층을 형성하는 단계는 상기 식각 보호층이 도금된 상기 하나 이상의 금속 층을 상기 확산 방지를 위한 금속 박막 층 위에 형성할 수 있다.

상기 하나 이상의 금속층을 상기 반도체 소자층 위에 형성하는 단계는 상기 스트리트 라인을 습식 식각할 때 측면부식을 방지하기 위한 제1 식각 보호층이 도금된 제1 금속층을 제1 패턴에 따라 상기 반도체 소자층 위에 형성하는 단계; 및 상기 스트리트 라인을 습식 식각할 때 측면부식을 방지하기 위한 제2 식각 보호층이 도금된 제2 금속층을 제2 패턴에 따라 상기 제1 금속층 위에 형성하는 단계를 포함할 수 있다.

또한 상기 하나 이상의 금속 층을 상기 반도체 소자 층 위에 형성하는 단계는 제1 금속 층과 제2금속 층을 제1 패턴과 제2패턴으로 단계적으로 형성한 후 상기 스트리트 라인을 습식 식각 할 때 측면부식을 방지하기 위한 식각 보호 층을 상기 제1 금속 층과 상기 제2금속 층위에 일괄 도금하여 형성하고 제3의 금속도금으로 스트리트 라인을 채우는 도금을 스트리트 라인과 제1, 2금속 층 위에 전체적으로 일시에 도금하는 단계도 포함할 수 있다.

또한 상기 하나 이상의 금속 층을 상기 반도체 소자 층 위에 형성하는 단계는 제1 금속 층과 제2금속 층을 제1 패턴과 제2패턴으로 단계적으로 형성한 후 상기 스트리트 라인을 습식 식각 할 때 측면부식을 방지하기 위한 식각 보호 층을 상기 제1 금속 층과 상기 제2금속 층위에 일괄 도금하여 형성하고 제3의 금속도금으로 스트리트 라인을 채울 때 제3의 패턴으로 제2 금속 층의 표면과 측벽을 가리고 스트리트 라인에 해당하는 부분만 채워 도금하는 것도 포함할 수 있다.

상기 제1 금속 층을 상기 반도체 소자 층 위에 형성하는 단계는 상기 제1 금속 층과 상기 제2 금속 층의 전체 두께가 최소 두께 부위를 기준으로 기준 80um 이상으로 형성되고 도금된 금속의 경도가 100~200 Hv 사이인 경우 상기 제1 금속 층을 최소 40um이상이 되도록 형성할 수 있다.

상기 제1 금속층을 형성하는 단계는 상기 반도체 소자층의 상기 스트리트 라인 위치에 제1 포토 레지스트(PR: Photo Resist)를 형성하는 단계; 상기 제1 패턴에 따라 상기 제1 포토 레지스트가 형성되지 않은 영역을 제1 금속으로 도금하는 단계; 상기 제1 포토 레지스트를 제거하는 단계; 및 상기 제1 금속 위에 제1 식각 보호층을 도금하는 단계를 포함할 수 있다.

상기 제1 금속은 구리(Cu; copper) 또는 구리 합금이거나 구리 또는 구리 합금과 같은 주 금속 중간에 단일 혹은 다수의 열 응력 완화 도금 층을 삽입한 것을 포함할 수 있다.

상기 제2 금속층을 형성하는 단계는 상기 제2 패턴의 반전 영역에 제2 포토 레지스트를 형성하는 단계; 상기 제2 패턴에 따라 상기 제2 포토 레지스트가 형성되지 않은 영역을 제2 금속으로 도금하는 단계; 상기 제2 포토 레지스트를 제거하는 단계; 상기 스트리트 라인에 위치한 제2 금속 위에 제3 포토 레지스트를 형성하는 단계; 제3 포토 레지스트가 형성되지 않은 제2 금속 위에 상기 제2 식각 보호층을 도금하는 단계; 및 상기 제3 포토 레지스트를 제거하는 단계를 포함할 수 있다.

또한 상기 제2 금속 층을 형성하는 단계는 상기 제2 패턴의 반전 영역에 제2 포토 레지스트를 형성하는 단계; 상기 제2 패턴에 따라 상기 제2 포토 레지스트가 형성되지 않은 영역을 제2 금속으로 도금하는 단계; 상기 제2 포토 레지스트를 제거하는 단계, 상기 제1금속 층과 제2금속 층 전면에 식각 방지 도금을 하는 단계, 스트리트 라인과 제 1, 2,금속 층 위를 제3의 금속 혹은 제1, 2금속과 동일한 금속으로 일괄 도금하는 단계를 포함할 수 있다.

또한 상기 제2 금속 층을 형성하는 단계는 상기 제2 패턴의 반전 영역에 제2 포토 레지스트를 형성하는 단계; 상기 제2 패턴에 따라 상기 제2 포토 레지스트가 형성되지 않은 영역을 제2 금속으로 도금하는 단계; 상기 제2 포토 레지스트를 제거하는 단계, 상기 제1금속 층과 제2금속 층 전면에 식각 방지 도금을 하는 단계, 상기 제2 금속 층의 표면과 측벽을 제3 패턴 포토 레지스트로 가리고 제1 금속 층 사이와 포토레지스트 사이의 위치한 스트리트 라인 영역을 제3의 금속도금 혹은 제1, 2 금속과 동일한 금속 도금으로 채우는 단계를 포함할 수 있다.

상기 제2 금속은 구리(Cu; copper) 또는 구리 합금이거나 구리나 구리합금과 같은 주 금속 중간에 단일 혹은 다수의 열 응력 완화 도금 층을 삽입한 것을 포함할 수 있다.

상기 제3 금속은 제1금속과 동일한 소재의 금속을 사용할 수 있다.

상기 반도체 소자 제조 방법은 상기 반도체 소자층의 스트리트 라인을 물리적 방법 또는 화학적으로 습식 식각 방법을 통해 절단하는 제1 절단 단계; 및 상기 반도체 소자층 상에 형성된 상기 하나 이상의 금속층 사이의 상기 스트리트 라인 상에 존재하는 식각 보호층이 도금되지 않은 금속을 습식 식각해서 절단하는 제2 절단 단계를 더 포함할 수 있다.

상기 제1 절단 단계 이후 상기 제2 절단 단계 이전에, 웨이퍼 내의 칩들을 고정하는 고정층을 형성하는 단계를 더 포함할 수 있다.

상기 고정층을 형성하는 단계는 상기 반도체 소자의 표면 위에 포지티브 포토 레지스트(Positive PR)를 포함하는 보호 PR을 도포하는 단계; 및 상기 포지티브 포토 레지스트 위에 자외선 테이프(UV Tape)를 접착하는 단계를 포함할 수 있다.

상기 포지티브 포토 레지스트를 포함하는 보호 PR을 도포하는 단계는 상기 포지티브 포토 레지스트의 두께가 소자의 표면으로부터 3um 이상이 되도록 도포할 수 있다. 이 때 보호 PR은 개별적으로 분리되는 반도체 소자 사이의 절단된 골을 가득 채울 수 있도록 도포될 수 있다.

상기 반도체 소자 제조 방법은 상기 제2 절단 단계 이후에, 소자 표면 고정 층의 포지티브 PR과 UV tape간의 접착력보다 높은 접착력의 익스펜딩 테이프(Expanding Tape)를 상기 제2 금속 층 위에 접착하여 고정 층 테이프에서 익스펜딩 테이프 쪽으로 절단된 개별 소자를 일괄적으로 옮겨 붙이는 단계; 및 상기 고정층을 제거하고 세정하는 단계를 더 포함할 수 있다.

본 발명은 반도체 소자를 제조하고, 습식 식각(wet etching)을 이용해서 반도체 소자들을 분리하는 방법에 관한 것으로, 웨이퍼의 금속층에 식각 보호층(etch barrier)을 도금해서 습식 식각을 통해서 웨이퍼에서 반도체 소자들을 분리할 때 금속층의 측면부식(side etching)이 발생하지 않도록 하였다.

또한, 본 발명은 습식 식각을 이용해서 반도체 소자들을 분리하기 때문에 기계적인 분리 기술에 비해 프로세서 수율이 높고, 반도체 소자의 성능 열화가 적으며, 상대적으로 비용이 저렴한 효과를 가진다.

도 1은 웨이퍼의 구성과 웨이퍼에서 반도체 소자들을 분리하기 위한 스트리트 라인의 예를 나타낸다.

도 2는 본 발명의 실시예에 따라 반도체 소자들이 형성된 웨이퍼의 예를 도시한 단면도를 나타낸다.

도 3은 본 발명의 일 실시예에 따라 반도체 소자 제조 방법을 도시한 흐름도를 나타낸다.

도 4는 본 발명의 일 실시예에 따라 제1 금속층을 형성하는 방법을 도시한 흐름도를 나타낸다.

도 5는 본 발명의 일 실시예에 따라 제2 금속층을 형성하는 방법을 도시한 흐름도를 나타낸다.

도 6은 본 발명의 일 실시예에 따라 고정층을 형성하는 방법을 도시한 흐름도를 나타낸다.

도 7은 본 발명의 실시예에 따라 제1 포토 레지스트가 형성된 웨이퍼의 단면도를 나타낸다.

도 8은 본 발명의 실시예에 따라 제1 금속이 도금된 웨이퍼의 단면도를 나타낸다.

도 9는 본 발명의 실시예에 따라 제1 포토 레지스트가 제거된 웨이퍼의 단면도를 나타낸다.

도 10는 본 발명의 실시예에 따라 제1 금속층 위에 제1 식각 보호층이 도금된 웨이퍼의 단면도를 나타낸다.

도 11은 본 발명의 실시예에 따라 제2 포토 레지스트가 형성된 웨이퍼의 단면도를 나타낸다.

도 12는 본 발명의 실시예에 따라 제2 포토 레지스트가 형성된 웨이퍼의 평면도를 나타낸다.

도 13은 본 발명의 실시예에 따라 제2 금속이 도금된 웨이퍼의 단면도를 나타낸다.

도 14는 본 발명의 실시예에 따라 제2 포토 레지스트가 제거된 웨이퍼의 단면도를 나타낸다.

도 15는 본 발명의 실시예에 따라 스트리트 라인에 위치한 제2 금속 위에 제3 포토 레지스트가 형성된 웨이퍼의 단면도를 나타낸다.

도 16은 본 발명의 실시예에 따라 제2 금속층 위에 제2 식각 보호층이 도금된 웨이퍼의 단면도를 나타낸다.

도 17은 본 발명의 실시예에 따라 제3 포토 레지스트가 제거된 웨이퍼의 단면도를 나타낸다.

도 18은 본 발명의 실시예에 따라 제1,2 레이어의 스트리트 라인이 절단된 단면도를 나타낸다.

도 19는 본 발명의 실시예에 따라 고정층이 형성된 웨이퍼의 단면도를 나타낸다.

도 20은 본 발명의 실시예에 따라 식각 보호층이 도금되지 않은 금속이 습식 식각으로 제거된 웨이퍼의 단면도를 나타낸다.

도 21은 본 발명의 실시예에 따라 제2 금속층 위에 익스펜딩 테이프 접착된 웨이퍼의 단면도를 나타낸다.

도 22는 본 발명의 실시예에 따라 고정층이 제거된 웨이퍼의 단면도를 나타낸다.

도 23은 본 발명의 다른 실시예에 따라 식각 보호층 및 다수의 금속층이 도금된 웨이퍼의 단면도를 나타낸다.

도 24는 본 발명의 또 다른 실시예에 따라 식각 보호층 및 다수의 금속층이 도금된 웨이퍼의 단면도를 나타낸다.

상기와 같은 목적을 달성하기 위하여, 본 발명의 일 실시 예에 따른 반도체 소자 제조 방법은 전류에 의해 빛을 발생시키는 반도체 소자층을 형성하는 단계; 및 상기 반도체 소자층 위에 기계적 지지를 제공하는 하나 이상의 금속층을 형성하는 단계를 포함하고, 상기 하나 이상의 금속층을 형성하는 단계는 상기 반도체 소자층을 개별 반도체 소자로 분리하기 위한 경계선인 스트리트 라인(street line)을 습식 식각(wet etching) 할 때 상기 금속층의 측면부식(side etching)이 발생하지 않도록 식각 보호층(etch barrier)이 도금된 상기 하나 이상의 금속층을 상기 반도체 소자층 위에 형성하는 단계를 포함한다.

상기 반도체 소자 제조 방법은 상기 하나 이상의 금속층을 형성하는 단계 이전에, 빛의 반사(reflection), CBL(Current Block Layer), 에칭 방어(Etch Barrier), 확산방지(diffusion barrier), 밀착(adhesion) 및 전기전도 혹은 확장(electrical transfer, or spreading) 등의 일부 또는 모두를 포함하는 기능을 갖는 진공 증착 금속박막층 (thin metal layer or thin metal layer by vacuum deposition, 이하 금속 박막층) 형성 단계를 더 포함하고, 이때, 상기 하나 이상의 금속 층을 형성하는 단계는 상기 식각 보호층이 도금된 상기 하나 이상의 금속 층을 상기 확산 방지를 위한 금속 박막 층 위에 형성할 수 있다.

상기 하나 이상의 금속층을 상기 반도체 소자층 위에 형성하는 단계는 상기 스트리트 라인을 습식 식각할 때 측면부식을 방지하기 위한 제1 식각 보호층이 도금된 제1 금속층을 제1 패턴에 따라 상기 반도체 소자층 위에 형성하는 단계; 및 상기 스트리트 라인을 습식 식각할 때 측면부식을 방지하기 위한 제2 식각 보호층이 도금된 제2 금속층을 제2 패턴에 따라 상기 제1 금속층 위에 형성하는 단계를 포함할 수 있다.

또한 상기 하나 이상의 금속 층을 상기 반도체 소자 층 위에 형성하는 단계는 제1 금속 층과 제2금속 층을 제1 패턴과 제2패턴으로 단계적으로 형성한 후 상기 스트리트 라인을 습식 식각 할 때 측면부식을 방지하기 위한 식각 보호 층을 상기 제1 금속 층과 상기 제2금속 층위에 일괄 도금하여 형성하고 제3의 금속도금으로 스트리트 라인을 채우는 도금을 스트리트 라인과 제1, 2금속 층 위에 전체적으로 일시에 도금하는 단계도 포함할 수 있다.

또한 상기 하나 이상의 금속 층을 상기 반도체 소자 층 위에 형성하는 단계는 제1 금속 층과 제2금속 층을 제1 패턴과 제2패턴으로 단계적으로 형성한 후 상기 스트리트 라인을 습식 식각 할 때 측면부식을 방지하기 위한 식각 보호 층을 상기 제1 금속 층과 상기 제2금속 층위에 일괄 도금하여 형성하고 제3의 금속도금으로 스트리트 라인을 채울 때 제3의 패턴으로 제2 금속 층의 표면과 측벽을 가리고 스트리트 라인에 해당하는 부분만 채워 도금하는 것도 포함할 수 있다.

상기 제1 금속 층을 상기 반도체 소자 층 위에 형성하는 단계는 상기 제1 금속 층과 상기 제2 금속 층의 전체 두께가 최소 두께 부위를 기준으로 기준 80um 이상으로 형성되고 도금된 금속의 경도가 100~200 Hv 사이인 경우 상기 제1 금속 층을 최소 40um이상이 되도록 형성할 수 있다.

상기 제1 금속층을 형성하는 단계는 상기 반도체 소자층의 상기 스트리트 라인 위치에 제1 포토 레지스트(PR: Photo Resist)를 형성하는 단계; 상기 제1 패턴에 따라 상기 제1 포토 레지스트가 형성되지 않은 영역을 제1 금속으로 도금하는 단계; 상기 제1 포토 레지스트를 제거하는 단계; 및 상기 제1 금속 위에 제1 식각 보호층을 도금하는 단계를 포함할 수 있다.

상기 제1 금속은 구리(Cu; copper) 또는 구리 합금이거나 구리 또는 구리 합금과 같은 주 금속 중간에 단일 혹은 다수의 열 응력 완화 도금 층을 삽입한 것을 포함할 수 있다.

상기 제2 금속층을 형성하는 단계는 상기 제2 패턴의 반전 영역에 제2 포토 레지스트를 형성하는 단계; 상기 제2 패턴에 따라 상기 제2 포토 레지스트가 형성되지 않은 영역을 제2 금속으로 도금하는 단계; 상기 제2 포토 레지스트를 제거하는 단계; 상기 스트리트 라인에 위치한 제2 금속 위에 제3 포토 레지스트를 형성하는 단계; 제3 포토 레지스트가 형성되지 않은 제2 금속 위에 상기 제2 식각 보호층을 도금하는 단계; 및 상기 제3 포토 레지스트를 제거하는 단계를 포함할 수 있다.

또한 상기 제2 금속 층을 형성하는 단계는 상기 제2 패턴의 반전 영역에 제2 포토 레지스트를 형성하는 단계; 상기 제2 패턴에 따라 상기 제2 포토 레지스트가 형성되지 않은 영역을 제2 금속으로 도금하는 단계; 상기 제2 포토 레지스트를 제거하는 단계, 상기 제1금속 층과 제2금속 층 전면에 식각 방지 도금을 하는 단계, 스트리트 라인과 제 1, 2,금속 층 위를 제3의 금속 혹은 제1, 2금속과 동일한 금속으로 일괄 도금하는 단계를 포함할 수 있다.

또한 상기 제2 금속 층을 형성하는 단계는 상기 제2 패턴의 반전 영역에 제2 포토 레지스트를 형성하는 단계; 상기 제2 패턴에 따라 상기 제2 포토 레지스트가 형성되지 않은 영역을 제2 금속으로 도금하는 단계; 상기 제2 포토 레지스트를 제거하는 단계, 상기 제1금속 층과 제2금속 층 전면에 식각 방지 도금을 하는 단계, 상기 제2 금속 층의 표면과 측벽을 제3 패턴 포토 레지스트로 가리고 제1 금속 층 사이와 포토레지스트 사이의 위치한 스트리트 라인 영역을 제3의 금속도금 혹은 제1, 2 금속과 동일한 금속 도금으로 채우는 단계를 포함할 수 있다.

상기 제2 금속은 구리(Cu; copper) 또는 구리 합금이거나 구리나 구리합금과 같은 주 금속 중간에 단일 혹은 다수의 열 응력 완화 도금 층을 삽입한 것을 포함할 수 있다.

상기 제3 금속은 제1금속과 동일한 소재의 금속을 사용할 수 있다.

상기 반도체 소자 제조 방법은 상기 반도체 소자층의 스트리트 라인을 물리적 방법 또는 화학적으로 습식 식각 방법을 통해 절단하는 제1 절단 단계; 및 상기 반도체 소자층 상에 형성된 상기 하나 이상의 금속층 사이의 상기 스트리트 라인 상에 존재하는 식각 보호층이 도금되지 않은 금속을 습식 식각해서 절단하는 제2 절단 단계를 더 포함할 수 있다.

상기 제1 절단 단계 이후 상기 제2 절단 단계 이전에, 웨이퍼 내의 칩들을 고정하는 고정층을 형성하는 단계를 더 포함할 수 있다.

상기 고정층을 형성하는 단계는 상기 반도체 소자의 표면 위에 포지티브 포토 레지스트(Positive PR)를 포함하는 보호 PR을 도포하는 단계; 및 상기 포지티브 포토 레지스트 위에 자외선 테이프(UV Tape)를 접착하는 단계를 포함할 수 있다.

상기 포지티브 포토 레지스트를 포함하는 보호 PR을 도포하는 단계는 상기 포지티브 포토 레지스트의 두께가 소자의 표면으로부터 3um 이상이 되도록 도포할 수 있다. 이 때 보호 PR은 개별적으로 분리되는 반도체 소자 사이의 절단된 골을 가득 채울 수 있도록 도포될 수 있다.

상기 반도체 소자 제조 방법은 상기 제2 절단 단계 이후에, 소자 표면 고정 층의 포지티브 PR과 UV tape간의 접착력보다 높은 접착력의 익스펜딩 테이프(Expanding Tape)를 상기 제2 금속 층 위에 접착하여 고정 층 테이프에서 익스펜딩 테이프 쪽으로 절단된 개별 소자를 일괄적으로 옮겨 붙이는 단계; 및 상기 고정층을 제거하고 세정하는 단계를 더 포함할 수 있다.

상기 목적 외에 본 발명의 다른 목적 및 특징들은 첨부 도면을 참조한 실시 예에 대한 설명을 통하여 명백히 드러나게 될 것이다.

본 발명의 바람직한 실시예를 첨부된 도면들을 참조하여 상세히 설명한다. 본 발명을 설명함에 있어, 관련된 공지 구성 또는 기능에 대한 구체적인 설명이 본 발명의 요지를 흐릴 수 있다고 판단되는 경우에는 그 상세한 설명은 생략한다.

그러나, 본 발명이 실시예들에 의해 제한되거나 한정되는 것은 아니다. 각 도면에 제시된 동일한 참조 부호는 동일한 부재를 나타낸다.

이하에서는, 본 발명의 일 실시 예에 따른 반도체 소자 제조 방법을 첨부된 도 2 내지 도 22를 참조하여 상세히 설명한다.

도 2은 본 발명의 실시예에 따라 반도체 소자들이 형성된 웨이퍼의 예를 도시한 단면도를 나타낸다.

도 2를 참조하면, 웨이퍼(200)는 크게 4개의 레이어로 구성될 수 있다.

제1 레이어(210)는 Si, GaN 등 불순물 반도체가 형성되어 있는 소자 층으로 제1 레이어(210)는 이하의 설명에서 제1 레이어 또는 반도체 소자층이라 칭한다. 제1 레이어(210)가 GaN 기반의 발광 다이오드 층인 경우에는 N-GaN 층과 P-GaN 층을 포함하고, N-GaN 층과 P-GaN 층 사이에 위치하는 활성층(MQW)도 포함한다. N-GaN 층과 P-GaN 층 사이에 전류가 흐르면 활성층에서 전자-정공 재결합이 일어나 소정 파장의 빛을 발생하게 된다.

제2 레이어(220)는 불순물 반도체 소자층인 제1 레이어(210)와 금속 도금 층에 해당하는 제3 레이어(230) 사이에서 빛의 반사(reflection), CBL(Current Block Layer), 에칭 방어(Etch Barrier), 확산방지(diffusion barrier), 밀착(adhesion) 및 전기전도 혹은 확장(electrical transfer, or spreading) 등의 일부 또는 모두를 포함하는 기능을 갖는 금속 박막 층이다. 이때, 제2 레이어(220)는 백금(Pt; platinum), 금(Au Gold), 은(Ag: silver), 크롬(Cr; chromium), 티탄(Ti; titanium), 몰리브덴(Mo; molybdenum), 텅스텐(W; tungsten), 니켈(Ni; nickel) 중 적어도 하나 이상을 포함하는 소재로 구성될 수 있으며 모든 소재가 필수구성이 아니므로 선택적으로 생략 가능하다.

제2 레이어(220)는 Si, SiO2등의 무기 소재를 부분적으로 진공 증착한 것을 포함 할 수 있다 제2 레이어(220)는 이하의 설명에서 제2 레이어 또는 확산 방지층이라 칭한다.

제3 레이어(230)는 제2 레이어(220)의 일부 기능을 도금 방식으로 형성한 층이다. 제3 레이어(230)는 이하의 설명에서 제3 레이어 또는 제1 금속층 이라 칭한다.

제4 레이어(240)는 방열, 배선, 접지, 기계적 지지를 위해 도금으로 형성한 층이다. 제4 레이어(240)는 이하의 설명에서 제4 레이어 또는 제2 금속층 이라 칭한다.

도 3은 본 발명의 일 실시예에 따라 반도체 소자 제조 방법을 도시한 흐름도를 나타낸다.

도 3을 참조하면, 반도체 소자 제조 방법은 전류에 의해 빛을 발생시키는 반도체 소자층을 형성하고(S310), 반도체 소자층으로 금속의 확산을 방지하는 확산 방지층을 반도체 소자층 위에 형성한다(S320).

그리고, 반도체 소자 제조 방법은 반도체 소자층을 개별 반도체 소자로 분리하기 위한 경계선인 스트리트 라인(street line)을 습식 식각(wet etching)할 때 측면부식(side etching)을 방지하기 위한 제1 식각 보호층(etch barrier)이 도금된 제1 금속층을 제1 패턴에 따라 반도체 소자층 위에 형성한다(S330).

이때, 제1 패턴은 스트리트 라인의 영역을 제외한 웨이퍼의 모든 영역이 될 수 있다. 다만 전기도금을 하는 경우 웨이퍼의 테두리에 전기적 접점이 형성되어야 하므로 테두리에서 전기적 접점에 필요한 수mm를 제외한 안쪽까지만 포토레지스트가 도포되도록 하는 것이 바람직하다. 그리고, 제1금속 층과 제2 금속층을 합금이 아닌 순수 구리도금으로 하는 경우 전체 도금 두께가 최소 두께 부위를 기준으로 80um 이상으로 형성하는 경우, 제1 금속 층의 두께는 최소 40um 이상이 되도록 형성하는 것이 바람직하다. 제2 금속 층의 형성은 제1 금속 층보다 면적이 작게 형성되므로 일차적으로 반도체 소자 테두리를 주로 제1 금속 층이 떠받치게 될 것이다. 이 때 제1 금속 층의 두께가 얇으면 도금응력과 소자 취급시의 문제로 테두리에 균열이 발생할 수 있으므로 제1 금속 층의 두께는 최소 40um 이상을 유지하는 것이 바람직하다

그러면 제1 금속 층을 형성하는 방법(S330)을 아래에서 도 4, 도7- 도10을 참조해서 상세히 설명하고자 한다.

도 4는 본 발명의 일 실시예에 따라 제1 금속층을 형성하는 방법을 도시한 흐름도를 나타낸다.

도 4를 참조하면, 제1 금속층 형성 방법(S330)은 도 7의 예와 같이 반도체 소자층과 확산 방지층인 제1, 2 레이어(710)의 스트리트 라인 위치에 제1 포토 레지스트(PR: Photo Resist)(720)를 형성한다(S410). 이때, 제1 포토 레지스트(720)는 스트리트 라인 위치에 제1 금속이 도금되지 않도록 하는 역할은 한다. 도 7은 본 발명의 실시예에 따라 제1 포토 레지스트가 형성된 웨이퍼의 단면도를 나타낸다.

그리고, 제1 금속층 형성 방법(S330)은 도 8의 예와 같이 제1 패턴에 따라 제1 포토 레지스트(720)가 형성되지 않은 영역을 제1 금속(810)으로 도금한다(S420). 이때, 제1 금속(810)은 구리(Cu; copper) 또는 구리 합금으로 구성되며, 순수 구리인 경우 제1 금속(810)의 비커스 경도는 120Hv 이하가 바람직하다. 도 8은 본 발명의 실시예에 따라 제1 금속이 도금된 웨이퍼의 단면도를 나타낸다.

그리고, 제1 금속층 형성 방법(S330)은 도 9의 예와 같이 제1 포토 레지스트(720)를 제거한다(S430). 도 9는 본 발명의 실시예에 따라 제1 포토 레지스트가 제거된 웨이퍼의 단면도를 나타낸다.

그리고, 제1 금속층 형성 방법(S330)은 도 10의 예와 같이 습식 식각을 이용한 반도체 소자를 분리할 때 습식 식각 되지 않도록 습식 식각 되지 않는 소재로 제1 식각 보호층(1010)을 제1 금속(810) 위에 도금한다(S440). 도 10는 본 발명의 실시예에 따라 제1 금속층 위에 제1 식각 보호층이 도금된 웨이퍼의 단면도를 나타낸다.

다시 도 3의 설명으로 돌아와서, 반도체 소자 제조 방법은 스트리트 라인을 습식 식각할 때 측면부식을 방지하기 위한 제2 식각 보호층이 도금된 제2 금속층을 제2 패턴에 따라 제1 금속층 위에 형성한다(S340).

그러면 제2 금속층을 형성하는 방법(S340)을 아래에서 도 5, 도 11 내지 도 17을 참조해서 상세히 설명하고자 한다.

도 5는 본 발명의 일 실시예에 따라 제2 금속층을 형성하는 방법을 도시한 흐름도를 나타낸다.

도 5를 참조하면, 제2 금속층 형성 방법(S340)은 도 11의 예와 같이 제2 패턴의 반전 영역에 제2 포토 레지스트(1110)를 형성한다(S510). 이때, 제2 포토 레지스트(1110)는 제2 패턴의 반전 영역인 스트리트 라인의 주변에 기설정된 넓이로 형성되며, 습식 식각으로 반도체 분리시 습식 식각 될 영역과 습식 식각 되면 안되는 영역을 구분하는 역할은 하며 도 12의 평면도와 같이 형성될 수 있다.

도 2 내지 도 10의 실시예에서 설명된 식각 보호층(etch barrier)은 제1, 제2 금속층과 에칭액의 성질을 고려하여 선택될 수 있다.

예를 들어, 제1, 제2 금속층의 주된 성분이 구리(Cu) 또는 구리 합금인 경우 에천트(etchant)로는 순수 염화동(CuCl2), 염화철(Cu2Fe3) 또는 이 두 가지가 혼합된 에천트를 사용할 수 있으며, 질산계 에천트의 사용이 가능하다.

이 때 식각 보호층으로는 Pure Au(금) 또는 NiAu, Pt, Pd 등을 이용할 수 있으며, 식각 보호층이 Pure Au 인 경우 0.5 um 이상 1.5 um 이하의 두께를 가지는 것이 바람직하다. 식각 보호층이 식각 보호 기능을 하기 위하여 0.5 um 이상의 두께를 가질 필요가 있고, 식각 보호층과 제1, 제2 금속층 간의 결합이 원활히 유지되기 위하여 1.5 um 이하의 두께를 가지는 것이 바람직하다.

식각 보호층이 NiAu 인 경우 Ni 0.5 um, Au 1.0 um 정도의 범위가 바람직하며, Ni이 0.5 um보다 두껍지 않은 것이 바람직하다. 최적의 두께 범위에 대한 선택 이유는 앞에서 설명한 바와 유사하다.

AuSn Eutetic 합금을 최종 식각 보호층으로 사용하는 경우에는 Pure Ni/AuSn 또는 Ni/Au/AuSn 등을 식각 보호층의 일부 또는 전체 레이어로 적용할 수 있는데 Ni 은 0.5 um, Au 는 1 um, AuSn 은 3 ~ 5 um 정도의 두께가 바람직하다.

도 2 내지 도 10의 실시예에서 상세히 도시되지는 않았으나, 본 발명의 다른 실시예에 따라서는 반도체 소자층과 금속층 간의 열팽창계수 차이와 열 충격에 따른, 소자의 균열이나 소자 특성저하, 신뢰성 저하 등을 최소화하기 위해 소자와 금속 층 간의 응력을 완화하는 역할을 하는 제3의 금속이 반도체 소자층과 금속층 간, 또는 복수의 금속층 사이에 단층 또는 다층으로 추가적으로 삽입될 수 있다. 이 때 제3의 금속은 중 적어도 하나 이상의 조합으로부터 이루어지는 군으로 형성될 수 있다.

이 때 제3의 금속은 응력완화 및 열팽창계수의 완화를 목적으로 하므로, Cu보다 열팽창계수가 작고 GaN보다는 큰 소재를 선택할 수 있다.

제1, 제2 금속층의 주된 성분이 인장 응력을 가지는 경우, 압축 응력을 가지는 소재가 제3의 금속으로 바람직하고, Ni, Cr, NiCo 합금, 또는 Mo, W 이나 이들 물질이 포함된 도금층 등을 삽입할 수 있다.

이 때 Ni/Cr/Ni 또는 Ni/Cr/NiCr/Ni 과 같이 Cr을 1회 이상 삽입하되 Cr도금 전과 후에 Ni을 삽입하여 Cr 도금 전후의 소재에 대한 밀착력을 높일수 있다. 이 경우 Ni은 각 layer별 0.2um 이상, Cr은 누적 두께를 기준하여 1um이상이 바람직하다.

또 다른 실시예로는 응력 완화층(제3의 금속)으로 NiCo 합금을 삽입할 수 있다. 이 때 Co의 비율은 도금된 합금층의 응력이 Zero Stress 영영에 있도록 Co의 함량과 전류밀도를 설정하는 것이 바람직하고 중요한 팩터이다.

또한 제1 금속층과 제2 금속층이 순수 구리 혹은 순수 구리도금과 +/- 10% 이내의 범위의 강도를 갖는 금속으로 도금되고 전체 두께가 최소 두께 부위를 기준으로 80um 이상으로 형성되는 경우, 상기 제1 금속 층은 최소 40um 이상이 되도록 형성되는 것이 바람직하다.

제1 금속층은 구리(Cu; copper) 또는 구리 합금도금을 포함하며 도금 응력(Stress by plating)이 - 0.2kgf/mm2 ~ + 1.0,kgf/mm2 이내의 범위인 성질을 갖는 것이 바람직하다.

제2 금속층은 구리 또는 구리 합금을 포함하고 제1 금속층의 도금응력이 -0.2kgf/mm2~+1.0kgf/mm2인 경우 제1, 제2 금속층의 두께를 합산하여 55% ~ 65% 두께를 제1 금속층의 도금소재로 도금하고 제2 금속층의 나머지 두께를 -1.0kgfmm2~+`1.0kgf/mm2의 도금응력을 갖는 금속으로 도금하는 과정에 의하여 형성될 수 있다.

도 11은 본 발명의 실시예에 따라 제2 포토 레지스트가 형성된 웨이퍼의 단면도를 나타낸다. 도 12는 본 발명의 실시예에 따라 제2 포토 레지스트가 형성된 웨이퍼의 평면도를 나타낸다. 도 12에서 점선은 도 11의 단면도의 단면을 나타내는 기준선이다.

그리고, 제2 금속층 형성 방법(S340)은 도 13의 예와 같이 제2 패턴에 따라 제2 포토 레지스트가 형성되지 않은 영역을 제2 금속(1310)으로 도금한다(S520). 이때, 제2 금속(1310)은 구리(Cu; copper) 또는 구리 합금으로 구성되며, 순수 구리인 경우 제2 금속(1310)의 비커스 경도는 120Hv 이상이 바람직하다. 도 13은 본 발명의 실시예에 따라 제2 금속이 도금된 웨이퍼의 단면도를 나타낸다.

그리고, 제2 금속층 형성 방법(S340)은 도 14의 예와 같이 제2 포토 레지스트(1110)를 제거한다(S530). 도 14는 본 발명의 실시예에 따라 제2 포토 레지스트가 제거된 웨이퍼의 단면도를 나타낸다.

그리고, 제2 금속층 형성 방법(S340)은 도 15의 예와 같이 스트리트 라인에 위치한 제2 금속 위에 제3 포토 레지스트(1510)를 형성한다(S540). 이때, 제3 포토 레지스트(1510)는 습식 식각으로 반도체 분리시 습식 식각 될 영역에 제2 식각 보호층이 도금되지 않도록 하는 역할은 한다. 도 15는 본 발명의 실시예에 따라 스트리트 라인에 위치한 제2 금속 위에 제3 포토 레지스트가 형성된 웨이퍼의 단면도를 나타낸다.

그리고, 제2 금속층 형성 방법(S340)은 도 16의 예와 같이 제3 포토 레지스트(1510)가 형성되지 않은 제2 금속 위에 제2 식각 보호층(1610)을 도금한다(S550). 도 16은 본 발명의 실시예에 따라 제2 금속층 위에 제2 식각 보호층이 도금된 웨이퍼의 단면도를 나타낸다.

그리고, 제2 금속층 형성 방법(S340)은 도 17의 예와 같이 제3 포토 레지스트(1510)를 제거한다(S560). 도 17은 본 발명의 실시예에 따라 제3 포토 레지스트가 제거된 웨이퍼의 단면도를 나타낸다.

한편, 본 발명의 설명에서 제1 포토 레지스트(720), 제2 포토 레지스트(1110) 및 제3 포토 레지스트(1610)로 구분해서 작성한 것은 반도체 소자를 제조하는 공정의 순서에 따라 구분한 것으로, 제1 포토 레지스트(720), 제2 포토 레지스트(1110) 및 제3 포토 레지스트(1610)는 동일한 소재 일 수도 있고 적어도 하나는 다른 소재일 수도 있다.

또한, 제1 식각 보호층(1010)과 제2 식각 보호층(1610)의 경우도 반도체 소자를 제조하는 공정의 순서에 따라 구분한 것으로, 제1 식각 보호층(1010)과 제2 식각 보호층(1610)은 동일한 소재 일 수도 있고 각기 다른 소재일 수도 있다.

다시 도 3의 설명으로 돌아와서, 반도체 소자 제조 방법은 도 18의 예와 같이 제1,2 레이어(710)의 스트리트 라인을 물리적(기계적인) 방법 또는 화학적으로 습식 식각을 통해 절단한다(S350). 도 18은 본 발명의 실시예에 따라 제1,2 레이어의 스트리트 라인이 절단된 단면도를 나타낸다.

그리고, 반도체 소자 제조 방법은 웨이퍼 내의 칩면을 보호하고 칩들을 고정하기 위해 웨이퍼의 칩면을 고정하는 고정층을 형성한다(S350). 그러면 고정층을 형성하는 방법(S360)을 아래에서 도 6과 도 19를 참조해서 상세히 설명하고자 한다.

도 6은 본 발명의 일 실시예에 따라 고정층을 형성하는 방법을 도시한 흐름도를 나타낸다.

도 19는 본 발명의 실시예에 따라 고정층이 형성된 웨이퍼의 단면도를 나타낸다.

도 6과 19를 참조하면, 고정층 형성 방법(S360)은 반도체 소자의 표면 위에 포지티브 포토 레지스트(Positive PR)(1910)를 도포한다(S610). 이때, 고정층 형성 방법(S360)은 습식 식각으로 반도체 소자를 분리할 때, 식각용 에칭액이 이미 화학적으로 절단한 레이어 1, 2(710)의 측벽과 표면을 보호하도록 절단된 소자의 깊이보다 높게 형성하여야 측벽과 표면의 보호 기능이 될 수 있으므로 상용화되는 소자들의 두께를 감안할 때 최소 3um이상 도포하는 것이 바람직하다.

고정층에 포토 레지스트를 도포하지 않고 UV Tape 혹은 비감광성 점착 Tape 등 만을 도포하는 경우 소자 측벽으로 점착제가 파고들지 못하고 표면을 감싸는 역할이 부족하게 되어 레이어 1, 2(710)의 측벽과 표면에 화학적 손상 및 기계적 손상이 있을 수 있게 된다. 포지티브 포토 레지스트는 웨이퍼 전면에 도포하는 것이고 도포 후에 노광 없이 경화만 하여 주고 이후 제거할 때 UV조사 후 포토 레지스트 현상액 만으로도 쉽게 제거되도록 한다

그리고, 고정층 형성 방법(S360)은 포지티브 포토 레지스트(1910) 위에 자외선을 쬐면 접착력을 상실하는 자외선 테이프(UV Tape)(1920)를 접착한다(S620).

자외선 테이프의 사용은 분리된 칩을 익스펜딩 테이프(expanding tape) 위에 옮겨 붙일 때 고정 층이 쉽게 분리 되도록 하기 위함으로 자외선을 받은 UV Tape는 포지티브 포토 레지스트와 함께 접착력을 잃어 쉽게 분리된다..

도 6에서 고정층을 포지티브 포토 레지스트(1910)와 자외선 테이프(1920)를 이용해서 형성하고 있으나 그 외에도 칩 면을 보호하면서 이후 금속층의 습식 식각시 반도체 소자를 고정할 수 있는 다른 소재를 이용해서 고정층을 형성할 수도 있다. 이때, 고정층의 소재는 추후 제거가 용이한 소재가 바람직하다.

접착력이 강한 소재를 사용한 경우 옮겨 붙이는 과정에 손실이 발생하고 소자 표면에 손상을 주게 된다

다만, UV Tape를 PR위에 고정 층으로 함께 적용 할 경우 포토 레지스트는 반드시 포지티브 타입이어야 자외선을 받았을 때 녹는 성질을 갖게 된다. 만일 네거티브 타입의 포토 레지스트를 사용하게 되면 오히려 포토레지스트가 굳게 되어 역효과를 일으키게 된다

포토 레지스트는 제1, 2 금속층 사이의 스트리트 라인에 형성되어 있는 금속을 제거하는 에칭액의 선정에도 영향을 준다. 즉 상기 제1, 2 금속층 형성 과정의 설명에서 스트리트 라인에 도금되는 금속은 제2금속 층과 동시에 형성되고 동일 소재일 수도 있고 구리(Cu, copper)나 구리 합금을 포함한 제3의 금속도금일 수도 있는데 이를 제거하는 에칭액은 금속을 제거한 후 포토레지스트를 만나게 되므로 에칭액은 포토레지스트에 손상을 주지 않는 성질을 갖는 것을 선정하여야 한다 즉 알카리성 첨가제가 포함된 에칭액은 대부분의 포토 레지스트에 영향을 줄 수 있게 되므로 이를 제외한 에칭액을 사용하여야 한다

다시 도 3의 설명으로 돌아와서, 반도체 소자 제조 방법은 도 20의 예와 같이 하나 이상의 금속층의 스트리트 라인 상에 존재하는 식각 보호층이 도금되지 않은 금속을 습식 식각해서 반도체 소자를 분리한다(S370).

도 20은 본 발명의 실시예에 따라 식각 보호층이 도금되지 않은 금속이 습식 식각으로 제거된 웨이퍼의 단면도를 나타낸다.

도 3의 예에서는 S350의 단계가 S370의 단계보다 먼저 수행되고 있으나, 수행 순서는 반대가 될 수도 있다. 다만, S350의 단계를 먼저 수행하는 것이 공정의 과정이 더 간단하기 때문이다. S370의 단계를 먼저 수행하는 것이 공정의 과정을 더욱 간소화 하는 경우 S370단계를 먼저 수행할 수도 있다.

또한 S370단계에서 레이어 1, 2의 측면 손상 및 표면 손상을 보호하기 위해 S350의 단계에서 레이어 1, 2의 다수 박막에서 일부 박막 층을 남겨두고 S370 단계를 진행한 이후에 남겨둔 박막을 제거할 수도 있다

이후, 반도체 소자 제조 방법은 도 21의 예와 같이 제2 금속층 위에 익스펜딩 테이프(Expanding Tape)(2110)를 접착하고(S380), 도 22의 예와 같이 고정층을 제거한다(S390). 고정층을 제거(S390)하는 방법은 자외선 테이프(1920)에 자외선을 조사해서 자외선 테이프를 제거하고, 포지티브 포토 레지스트(1910)를 제거한다.

도 21은 본 발명의 실시예에 따라 제2 금속층 위에 익스펜딩 테이프 접착된 웨이퍼의 단면도를 나타낸다.

도 22는 본 발명의 실시예에 따라 고정층이 제거된 웨이퍼의 단면도를 나타낸다.

도 23은 본 발명의 다른 실시예에 따라 식각 보호층 및 다수의 금속층이 도금된 웨이퍼의 단면도를 나타낸다.

도 23을 참조하면, 반도체 소자층 및 확산 보호층인 레이어 1,2 (710) 상에 제1 패턴에 따라 제1 금속층(2310)이 도금된다. 제1 패턴은 스트리트 라인에 대응하는 패턴이다.

이어 제2 패턴에 따라 제1 금속층(2310) 상에 제2 금속층(2320)이 도금된다. 제1 금속층(2310)과 제2 금속층(2320)은 구리 또는 구리 합금을 공통적으로 포함할 수 있으며, 제1 금속층(2310)과 제2 금속층(2320)이 가질 수 있는 물리적 성질의 범위는 앞에서 설명한 바와 같다.

제2 패턴은 제1 패턴과 유사하지만 제2 패턴의 면적이 제1 패턴의 면적보다 좁게 형성됨은 앞에서 설명한 바와 같다.

다음으로, 제1 금속층(2310) 및 제2 금속층(2320) 상에 식각 보호층(2330)이 도금된다. 이어서 제3 금속층(2340)이 식각 보호층(2330) 상에 도금되는데, 특히 식각 보호층(2330)에 의하여 빈 공간으로 남겨져 있던 스트리트 라인에 대응하는 부분이 제3 금속층(2340)에 의하여 채워지게 된다.

제3 금속층(2340)에 의하여 스트리트 라인에 대응하는 식각 보호층(2330) 사이의 공간이 채워짐으로써 제1 금속층(2310)끼리, 또한 제2 금속층(2320)끼리 물리적으로 연결되어 기계적 지지를 제공할 수 있게 되며, 이로 인하여 단일 웨이퍼 형태로 공정이 진행될 수 있다.

도 24는 본 발명의 또 다른 실시예에 따라 식각 보호층 및 다수의 금속층이 도금된 웨이퍼의 단면도를 나타낸다.

도 24를 참조하면 반도체 소자층 및 확산 보호층인 레이어 1,2 (710) 상에 제1 패턴에 따라 제1 금속층(2410)이 도금되고, 이어 제2 패턴에 따라 제1 금속층(2410) 상에 제2 금속층(2420)이 도금된다. 이후 식각 보호층(2430)이 도금되는 과정까지는 도 23의 실시예와 동일하다.

이후 제3 금속층(2450)이 도금되기 전에 제3 패턴에 대응하는 3차 포토 레지스트(2440)가 도포된다. 3차 포토 레지스트(2440)가 미리 도포됨으로써 제3 금속층(2450)은 스트리트 라인에 대응하는 식각 보호층(2430) 사이의 빈 공간만을 효율적으로 채울 수 있다.

스트리트 라인에 대응하는 식각 보호층(2430) 사이의 빈 공간을 채우는 제3 금속층(2450)이 서로 다른 개별 반도체 소자들의 제1 금속층(2310) 간을 연결시킴으로써 단일 웨이퍼 형태로 공정이 진행될 수 있음은 도 23의 실시예와 동일하다.

이상과 같이 본 발명에서는 구체적인 구성 요소 등과 같은 특정 사항들과 한정된 실시예 및 도면에 의해 설명되었으나 이는 본 발명의 보다 전반적인 이해를 돕기 위해서 제공된 것일 뿐, 본 발명은 상기의 실시예에 한정되는 것은 아니며, 본 발명이 속하는 분야에서 통상적인 지식을 가진 자라면 이러한 기재로부터 다양한 수정 및 변형이 가능하다.

따라서, 본 발명의 사상은 설명된 실시예에 국한되어 정해져서는 아니 되며, 후술하는 특허청구범위뿐 아니라 이 특허청구범위와 균등하거나 등가적 변형이 있는 모든 것들은 본 발명 사상의 범주에 속한다고 할 것이다.

반도체 소자 제조 방법을 개시한다. 본 발명의 실시예에 따른 반도체 소자 제조 방법은 전류에 의해 빛을 발생시키는 반도체 소자층을 형성하는 단계; 상기 반도체 소자층 위에 기계적 지지를 제공하는 하나 이상의 금속층을 형성하는 단계; 상기 반도체 소자층의 스트리트 라인을 물리적 방법 또는 화학적으로 습식 식각 방법을 통해 절단하는 제1 절단 단계; 및 상기 하나 이상의 금속층의 상기 스트리트 라인 상에 존재하는 식각 보호층이 도금되지 않은 금속을 습식 식각해서 절단하는 제2 절단 단계를 포함할 수 있다.

이때, 상기 하나 이상의 금속층을 형성하는 단계는 상기 반도체 소자층을 개별 반도체 소자로 분리하기 위한 경계선인 스트리트 라인(street line)을 습식 식각(wet etching) 할 때 상기 금속층의 측면부식(side etching)이 발생하지 않도록 식각 보호층(etch barrier)이 도금된 상기 하나 이상의 금속층을 상기 반도체 소자층 위에 형성하는 단계를 포함해서 습식 식각을 통한 반도체 소자 분리시 발생하는 측면부식을 억제할 수 있다.

Claims (15)

- 전류에 의해 빛을 발생시키는 반도체 소자층을 형성하는 단계; 및상기 반도체 소자층 상에 및 기계적 지지를 제공하는 하나 이상의 금속층을 형성하는 단계를 포함하고,상기 하나 이상의 금속층을 형성하는 단계는,상기 반도체 소자층을 개별 반도체 소자로 분리하기 위한 경계선인 스트리트 라인(street line)을 습식 식각(wet etching)할 때 상기 금속 층의 측면부식(side etching)이 발생하지 않도록 식각 보호층(etch barrier)이 도금된 상기 하나 이상의 금속 층을 상기 반도체 소자층 상에 형성하는 단계를 포함하는 반도체 소자 제조 방법.

- 제1항에 있어서,상기 하나 이상의 금속층을 형성하는 단계는,상기 식각 보호층이 도금된 상기 하나 이상의 금속층을 상기 반도체 소자층 위에 형성하는 단계 이후에추가적으로 도금을 진행하여 상기 스트리트 라인을 채우는 단계를 더 포함하는 반도체 소자 제조 방법.

- 제1항에 있어서,상기 하나 이상의 금속층을 형성하는 단계는,상기 반도체 소자층과 상기 하나 이상의 금속층 간의 열팽창계수 차이와 열 충격에 따른, 소자의 균열이나 소자 특성저하, 신뢰성 저하 등을 최소화하기 위해 소자와 금속층 간의 응력을 완화하는 역할을 하는 제3의 금속을 상기 반도체 소자층과 상기 하나 이상의 금속층 간에 또는 상기 하나 이상의 금속 층 사이에 단층 또는 다층으로 도금하는 단계를 더 포함하는 반도체 소자 제조 방법.