KR20180013469A - 유기발광다이오드 표시장치 - Google Patents

유기발광다이오드 표시장치 Download PDFInfo

- Publication number

- KR20180013469A KR20180013469A KR1020160097257A KR20160097257A KR20180013469A KR 20180013469 A KR20180013469 A KR 20180013469A KR 1020160097257 A KR1020160097257 A KR 1020160097257A KR 20160097257 A KR20160097257 A KR 20160097257A KR 20180013469 A KR20180013469 A KR 20180013469A

- Authority

- KR

- South Korea

- Prior art keywords

- layer

- light emitting

- pixel region

- thickness

- bank

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/122—Pixel-defining structures or layers, e.g. banks

-

- H01L27/3246—

-

- H01L27/3211—

-

- H01L51/5012—

-

- H01L51/5056—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

- H10K50/10—OLEDs or polymer light-emitting diodes [PLED]

- H10K50/11—OLEDs or polymer light-emitting diodes [PLED] characterised by the electroluminescent [EL] layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

- H10K50/10—OLEDs or polymer light-emitting diodes [PLED]

- H10K50/14—Carrier transporting layers

- H10K50/15—Hole transporting layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/30—Devices specially adapted for multicolour light emission

- H10K59/35—Devices specially adapted for multicolour light emission comprising red-green-blue [RGB] subpixels

-

- H01L2251/558—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K2102/00—Constructional details relating to the organic devices covered by this subclass

- H10K2102/301—Details of OLEDs

- H10K2102/351—Thickness

Landscapes

- Physics & Mathematics (AREA)

- Optics & Photonics (AREA)

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Electroluminescent Light Sources (AREA)

Abstract

본 발명은 유기발광다이오드 표시장치에 관한 것으로, 기판 상의 제1, 제2, 제3 화소영역의 각각에 위치하는 제1 전극과, 제1 전극의 가장자리를 덮는 뱅크층과, 뱅크층 내의 제1 전극 상부의 발광층과, 발광층 상부의 제2 전극을 포함하고, 용액 공정에 의해 발광층을 형성한다. 이때, 마이크로 캐비티 효과를 구현하기 위해, 더 긴 파장의 빛을 방출하는 제1 화소영역의 발광층의 두께는 제2 화소영역의 발광층 두께보다 크게 하는데, 제1 화소영역의 뱅크층은 제1 높이를 가지며 제2 화소영역의 뱅크층은 제1 높이보다 큰 제2 높이를 갖도록 함으로써, 각 화소영역마다 균일한 두께의 발광층을 형성하여 화질을 향상시킨다.

Description

본 발명은 유기발광다이오드 표시장치에 관한 것으로, 특히 색순도(color purity) 및 광 방출 효율(light extraction efficiency)을 높이면서 고화질을 갖는 유기발광다이오드 표시장치에 관한 것이다.

최근, 박형화, 경량화, 저 소비전력화 등의 우수한 특성을 가지는 평판표시장치(flat panel display)가 널리 개발되어 다양한 분야에 적용되고 있다.

평판표시장치 중에서, 유기 전계발광 표시장치 또는 유기 전기발광 표시장치(organic electroluminescent display device)라고도 불리는 유기발광다이오드 표시장치(organic light emitting diode display device: OLED display device)는, 전자 주입 전극인 음극과 정공 주입 전극인 양극 사이에 형성된 발광층에 전하를 주입하여 전자와 정공이 엑시톤(exciton)을 형성한 후, 이 엑시톤이 발광 재결합(radiative recombination) 함으로써 빛을 내는 소자이다. 이러한 유기발광다이오드 표시장치는 플라스틱과 같은 유연한 기판(flexible substrate) 위에도 형성할 수 있을 뿐 아니라, 자체 발광형이기 때문에 대조비(contrast ratio)가 크며, 응답시간이 수 마이크로초(㎲) 정도이므로 동화상 구현이 쉽고, 시야각의 제한이 없으며 저온에서도 안정적이고, 직류 5V 내지 15V의 비교적 낮은 전압으로 구동이 가능하므로 구동회로의 제작 및 설계가 용이한 장점을 가진다.

유기발광다이오드 표시장치의 발광층은 미세금속마스크(fine metal mask)를 이용하여 유기발광물질을 선택적으로 진공 증착함으로써 열 증착(thermal evaporation)법에 의해 형성될 수 있다. 그런데, 열 증착법에 의한 발광층 형성은, 마스크의 제작 편차와, 처짐, 쉐도우 효과(shadow effect) 등에 의해 대면적 및 고해상도 표시장치에 적용하기 어려운 문제가 있다.

이를 해결하기 위해, 용액 공정(solution process)에 의해 발광층을 형성하는 방법이 제안되었다. 이러한 용액 공정에 의해 형성된 발광층을 포함하는 종래의 유기발광다이오드 표시장치에 대해 도면을 참조하여 설명한다.

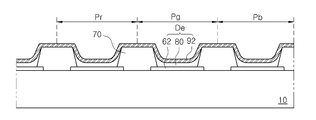

도 1은 종래의 유기발광다이오드 표시장치를 개략적으로 도시한 단면도이다.

도 1에 도시한 바와 같이, 기판(10) 상에 적, 녹, 청색 화소영역(Pr, Pg, Pb)이 정의되고, 기판(10) 상부의 각 화소영역(Pr, Pg, Pb)에는 제1 전극(62)이 형성된다. 제1 전극(62) 상부에는 제1 전극(62)의 가장자리를 덮는 뱅크층(70)이 형성되고, 뱅크층(70)으로 둘러싸인 제1 전극(62) 상부에는 발광층(80)이 형성된다. 발광층(80)과 뱅크층(70) 상부에는 실질적으로 기판(10) 전면에 제2 전극(92)이 형성된다. 제1 전극(62)과 발광층(80) 및 제2 전극(92)은 유기발광다이오드(De)를 이룬다.

여기서, 발광층(80)은 용액 공정을 통해 형성된다. 보다 상세하게는, 각 화소영역(Pr, Pg, Pb)에서 뱅크층(70)으로 둘러싸여 노출된 제1 전극(62) 상에 발광물질을 포함하는 용액을 적하(drop)한 후, 이를 건조하여 발광층(80)을 형성한다. 이때, 뱅크층(70)은 발광층(80)이 형성될 영역을 정의하며, 한 화소영역(Pr, Pg, Pb)에 적하된 용액이 인접한 화소영역(Pr, Pg, Pb)으로 침투하는 것을 방지한다.

이러한 용액 공정은 마스크 없이 각 화소영역(Pr, Pg, Pb)에 해당 발광층(80)을 용이하게 형성할 수 있으므로, 대면적 및 고해상도 표시장치에 적용 가능하다.

한편, 유기발광다이오드 표시장치의 색순도 및 광 방출 효율을 높이기 위해 유기발광다이오드(De)에 마이크로 캐비티(microcavity) 효과를 적용하는 구조가 제안되어 사용되고 있다. 보다 상세하게는, 발광층(80)에서 방출된 빛이 두 전극(62, 92) 사이에서 간섭을 일으키는 마이크로 캐비티 효과를 이용하여 파장을 선택적으로 증폭시켜 좁은 색 스펙트럼을 방출하도록 함으로써, 고색순도의 빛을 얻을 수 있고 정면에서 높은 효율을 갖도록 할 수 있다.

이러한 마이크로 캐비티 효과는 두 전극(62, 92) 사이의 거리, 즉, 발광층(80)의 두께를 조절함으로써 구현할 수 있는데, 각 화소영역(Pr, Pg, Pb)에서 방출되는 빛의 파장이 다르므로, 적, 녹, 청색 화소영역(Pr, Pg, Pb)별로 다른 두께를 갖는 발광층(80)이 요구된다.

이러한 발광층(80)의 두께는, 동일 농도의 용액을 이용할 경우 용액의 적하 수, 즉, 적하된 용액의 양에 따라 조절될 수 있다. 이때, 요구되는 두께를 달성하기 위해 용액의 농도 및 단위 면적 등에 따라 한계 적하 수가 결정되는데, 적, 녹, 청색 화소영역(Pr, Pg, Pb)별로 발광층(80)의 두께를 다르게 할 경우, 한계 적하 수보다 용액이 적게 적하되거나 많이 적하될 수 있다. 한계 적하 수보다 용액이 적게 적하될 경우, 적하된 용액이 화소영역(Pr, Pg, Pb)의 제1 전극(62)을 완전히 덮지 못하는 디(dewet) 현상이 발생할 수 있으며, 한계 적하 수보다 용액이 많이 적하될 경우, 적하된 용액이 뱅크층(70)을 넘어 인접한 화소영역(Pr, Pg, Pb)으로 침투하는 오버플로우(overflow) 현상이 발생할 수 있다. 이에 따라, 불균일한 두께를 갖는 발광층(80)이 형성된다.

도 2a와 도 2b는 종래의 불균일한 두께를 갖는 발광층의 프로파일을 개략적으로 도시한 도면이다. 도 2a에 도시한 바와 같이, 발광층(80)은 일측의 두께가 타측의 두께에 비해 급격히 두꺼워지는 비대칭 U자 모양을 가질 수 있다. 이와 달리, 도 2b에 도시한 바와 같이, 발광층(80)은 중앙의 두께가 가장자리에 비해 두꺼워지는 W자 모양을 가질 수도 있다.

이러한 불균일한 두께의 발광층(80)을 갖는 유기발광다이오드는 발광이 균일하지 않게 되므로, 표시장치의 화질을 저하시킨다. 또한, 발광층(80)이 도 2a의 비대칭 U자 모양을 가질 경우, 유기발광다이오드의 구동전압이 증가하게 되어 소비전력이 상승하게 되며, 발광층(80)이 도 2b의 W자 모양을 가질 경우, 누설 전류(leakage current)가 발생하여 유기발광다이오드의 수명을 저하시킨다.

이를 해결하기 위해, 다른 농도의 용액을 이용하여 발광층(80)의 두께를 조절할 수 있으나, 이 경우 재료 및 장비의 추가 등이 필요하여 제조 비용이 증가하게 된다.

본 발명은, 상기한 문제점을 해결하기 위하여 제시된 것으로, 유기발광다이오드 표시장치의 화질 저하 문제를 해결하고자 한다.

또한, 본 발명은 유기발광다이오드 표시장치의 소비전력 상승 및 수명 저하 문제를 해결하고자 한다.

상기의 목적을 달성하기 위하여, 본 발명은, 제1, 제2, 제3 화소영역이 정의된 기판과, 상기 기판 상의 상기 제1, 제2, 제3 화소영역의 각각에 위치하는 제1 전극과, 상기 제1 전극의 가장자리를 덮는 뱅크층과, 상기 뱅크층 내의 상기 제1 전극 상부의 발광층과, 상기 발광층 상부의 제2 전극을 포함하고, 상기 제1 화소영역의 뱅크층은 제1 높이를 가지며 상기 제2 화소영역의 뱅크층은 상기 제1 높이보다 큰 제2 높이를 갖고, 상기 제1 화소영역의 발광층은 상기 제2 화소영역의 발광층보다 긴 파장의 빛을 방출하며, 상기 제1 화소영역의 중앙에서 발광층의 두께는 상기 제2 화소영역의 중앙에서 발광층 두께보다 큰 유기발광다이오드 표시장치를 제공한다.

또한, 상기 제3 화소영역의 뱅크층은 상기 제1 높이보다 낮은 제3 높이를 가지며, 상기 제3 화소영역의 발광층은 상기 제2 화소영역의 발광층보다 짧은 파장의 빛을 방출하고, 상기 제3 화소영역의 중앙에서 발광층의 두께는 상기 제2 화소영역의 중앙에서 발광층 두께보다 작다.

본 발명에서는, 용액 공정에 의해 유기발광다이오드 표시장치의 발광층을 형성함으로써, 대면적 및 고해상도의 표시장치를 제공할 수 있으며, 발광층의 두께를 화소영역별로 다르게 하여 마이크로 캐비티 효과를 구현함으로써, 색순도 및 광 방출 효율을 높일 수 있다.

또한, 화소영역별로 뱅크층의 높이를 달리하여 각 화소영역마다 균일한 두께의 발광층을 형성함으로써, 화질을 향상시킬 수 있다.

또한, 불균일한 두께의 발광층에 의해 야기되는 소비전력 상승 및 수명 저하를 방지할 수 있다.

도 1은 종래의 유기발광다이오드 표시장치를 개략적으로 도시한 단면도이다.

도 2a와 도 2b는 종래의 불균일한 두께를 갖는 발광층의 프로파일을 개략적으로 도시한 도면이다.

도 3은 본 발명의 실시예에 따른 유기발광다이오드 표시장치의 하나의 화소영역에 대한 회로도이다.

도 4는 본 발명의 실시예에 따른 유기발광다이오드 표시장치를 개략적으로 도시한 단면도이다.

도 5a 내지 도 5c는 본 발명의 실시예에 따른 유기발광다이오드 표시장치의 제조 공정 중 표시장치를 개략적으로 도시한 단면도이다.

도 6은 뱅크층의 높이에 따른 정공주입층의 프로파일을 개략적으로 도시한 도면이다.

도 7a 내지 도 7c는 정공주입층의 프로파일에 따른 정공수송층 및 발광물질층의 프로파일을 개략적으로 도시한 도면이다.

도 8은 본 발명의 실시예에 따른 뱅크층의 다른 예를 개략적으로 도시한 단면도이다.

도 2a와 도 2b는 종래의 불균일한 두께를 갖는 발광층의 프로파일을 개략적으로 도시한 도면이다.

도 3은 본 발명의 실시예에 따른 유기발광다이오드 표시장치의 하나의 화소영역에 대한 회로도이다.

도 4는 본 발명의 실시예에 따른 유기발광다이오드 표시장치를 개략적으로 도시한 단면도이다.

도 5a 내지 도 5c는 본 발명의 실시예에 따른 유기발광다이오드 표시장치의 제조 공정 중 표시장치를 개략적으로 도시한 단면도이다.

도 6은 뱅크층의 높이에 따른 정공주입층의 프로파일을 개략적으로 도시한 도면이다.

도 7a 내지 도 7c는 정공주입층의 프로파일에 따른 정공수송층 및 발광물질층의 프로파일을 개략적으로 도시한 도면이다.

도 8은 본 발명의 실시예에 따른 뱅크층의 다른 예를 개략적으로 도시한 단면도이다.

본 발명의 실시예에 따른 유기발광다이오드 표시장치는, 제1, 제2, 제3 화소영역이 정의된 기판과, 상기 기판 상의 상기 제1, 제2, 제3 화소영역의 각각에 위치하는 제1 전극과, 상기 제1 전극의 가장자리를 덮는 뱅크층과, 상기 뱅크층 내의 상기 제1 전극 상부의 발광층과, 상기 발광층 상부의 제2 전극을 포함하고, 상기 제1 화소영역의 뱅크층은 제1 높이를 가지며 상기 제2 화소영역의 뱅크층은 상기 제1 높이보다 큰 제2 높이를 가진다.

상기 제1 화소영역의 중앙에서 발광층의 두께는 상기 제2 화소영역의 중앙에서 발광층 두께보다 크다.

상기 제1 및 제2 화소영역의 발광층 각각은 정공보조층과 발광물질층 및 전자보조층을 포함하고, 상기 제1 화소영역의 중앙에서 정공보조층의 두께는 상기 제2 화소영역의 중앙에서 정공보조층의 두께보다 크다.

상기 제1 화소영역과 상기 제2 화소영역은 동일한 개구율을 가진다.

상기 제1 화소영역의 발광층은 상기 제2 화소영역의 발광층보다 긴 파장의 빛을 방출한다.

상기 제1 화소영역의 뱅크층은 상기 제1 화소영역의 뱅크층에 인접한 상기 제2 화소영역의 뱅크층과 연결되어 서로 일체화된다.

상기 제3 화소영역의 뱅크층은 상기 제1 높이보다 낮은 제3 높이를 가진다.

상기 제3 화소영역의 중앙에서 발광층의 두께는 상기 제2 화소영역의 중앙에서 발광층 두께보다 작다.

상기 제3 화소영역의 발광층은 상기 제2 화소영역의 발광층보다 짧은 파장의 빛을 방출한다.

상기 제2 화소영역의 뱅크층은 상기 제2 화소영역의 뱅크층에 인접한 상기 제3 화소영역의 뱅크층과 연결되어 서로 일체화된다.

이하, 도면을 참조하여 본 발명의 실시예에 따른 유기발광다이오드 표시장치에 대하여 상세히 설명한다.

도 3은 본 발명의 실시예에 따른 유기발광다이오드 표시장치의 하나의 화소영역에 대한 회로도이다.

도 3에 도시한 바와 같이, 본 발명의 실시예에 따른 유기발광다이오드 표시장치는 서로 교차하여 화소영역(P)을 정의하는 게이트배선(GL)과 데이터배선(DL)을 포함하고, 각각의 화소영역(P)에는 스위칭 박막트랜지스터(Ts)와 구동 박막트랜지스터(Td), 스토리지 커패시터(Cst), 그리고 유기발광다이오드(De)가 형성된다.

보다 상세하게, 스위칭 박막트랜지스터(Ts)의 게이트전극은 게이트배선(GL)에 연결되고 소스전극은 데이터배선(DL)에 연결된다. 구동 박막트랜지스터(Td)의 게이트전극은 스위칭 박막트랜지스터(Ts)의 드레인전극에 연결되고, 소스전극은 고전위 전압(VDD)에 연결된다. 유기발광다이오드(De)의 애노드(anode)는 구동 박막트랜지스터(Td)의 드레인전극에 연결되고, 캐소드(cathode)는 저전위 전압(VSS)에 연결된다. 스토리지 커패시터(Cst)는 구동 박막트랜지스터(Td)의 게이트전극과 드레인전극에 연결된다.

이러한 유기발광다이오드 표시장치의 영상표시 동작을 살펴보면, 게이트배선(GL)을 통해 인가된 게이트신호에 따라 스위칭 박막트랜지스터(Ts)가 턴-온(turn-on) 되고, 이때, 데이터배선(DL)으로 인가된 데이터신호가 스위칭 박막트랜지스터(Ts)를 통해 구동 박막트랜지스터(Td)의 게이트전극과 스토리지 커패시터(Cst)의 일 전극에 인가된다.

구동 박막트랜지스터(Td)는 데이터신호에 따라 턴-온 되어 유기발광다이오드(De)를 흐르는 전류를 제어하여 영상을 표시한다. 유기발광다이오드(De)는 구동 박막트랜지스터(Td)를 통하여 전달되는 고전위 전압(VDD)의 전류에 의하여 발광한다.

즉, 유기발광다이오드(De)를 흐르는 전류의 양은 데이터신호의 크기에 비례하고, 유기발광다이오드(De)가 방출하는 빛의 세기는 유기발광다이오드(De)를 흐르는 전류의 양에 비례하므로, 화소영역(P)은 데이터신호의 크기에 따라 상이한 계조를 표시하고, 그 결과 유기발광다이오드 표시장치는 영상을 표시한다.

스토리지 커패시터(Cst)는 데이터신호에 대응되는 전하를 일 프레임(frame) 동안 유지하여 유기발광다이오드(De)를 흐르는 전류의 양을 일정하게 하고 유기발광다이오드(De)가 표시하는 계조를 일정하게 유지시키는 역할을 한다.

도 4는 본 발명의 실시예에 따른 유기발광다이오드 표시장치를 개략적으로 도시한 단면도로, 다수의 화소영역에 대응하는 구조를 도시한다.

도 4에 도시한 바와 같이, 절연 기판(110) 상에 다수의 화소영역, 일례로, 제1, 제2, 제3 화소영역(P1, P2, P3)이 정의되고, 기판(110) 상부의 각 화소영역(P1, P2, P3)에 대응하여 패터닝된 반도체층(122)이 형성된다. 기판(110)은 유리기판이나 플라스틱기판일 수 있다. 반도체층(122)은 산화물 반도체 물질로 이루어질 수 있는데, 이 경우 반도체층(122) 하부에는 차광패턴(도시하지 않음)과 버퍼층(도시하지 않음)이 형성될 수 있으며, 차광패턴은 반도체층(122)으로 입사되는 빛을 차단하여 반도체층(122)이 빛에 의해 열화되는 것을 방지한다. 이와 달리, 반도체층(122)은 다결정 실리콘으로 이루어질 수도 있으며, 이 경우 반도체층(122)의 양 가장자리에는 불순물이 도핑되어 있을 수 있다.

반도체층(122) 상부에는 절연물질로 이루어진 게이트 절연막(130)이 실질적으로 기판(110) 전면에 형성된다. 게이트 절연막(130)은 무기절연물질로 형성될 수 있으며, 일례로, 게이트 절연막(130)은 산화 실리콘(SiO2)으로 이루어질 수 있다. 반도체층(122)이 다결정 실리콘으로 이루어질 경우, 게이트 절연막(130)은 산화 실리콘(SiO2)이나 질화 실리콘(SiNx)으로 형성될 수 있다.

게이트 절연막(130) 상부에는 금속과 같은 도전성 물질로 이루어진 게이트전극(132)이 각 화소영역(P1, P2, P3)의 반도체층(122)의 중앙에 대응하여 형성된다. 또한, 게이트 절연막(130) 상부에는 게이트배선(도시하지 않음)과 제1 커패시터 전극(도시하지 않음)이 형성될 수 있다. 게이트배선은 제1 방향을 따라 연장되고, 제1 커패시터 전극은 게이트전극(132)에 연결될 수 있다.

한편, 본 발명의 실시예에서는 게이트 절연막(130)이 기판(110) 전면에 형성되어 있으나, 게이트 절연막(130)은 게이트전극(132)과 동일한 모양으로 패터닝될 수도 있다.

게이트전극(132) 상부에는 절연물질로 이루어진 층간 절연막(140)이 실질적으로 기판(110) 전면에 형성된다. 층간 절연막(140)은 산화 실리콘(SiO2)이나 질화 실리콘(SiNx)과 같은 무기절연물질로 형성되거나, 포토 아크릴(photo acryl)이나 벤조사이클로부텐(benzocyclobutene)과 같은 유기절연물질로 형성될 수 있다.

층간 절연막(140)은 반도체층(122)의 양측 상면을 노출하는 제1 및 제2 컨택홀(140a, 140b)을 가진다. 제1 및 제2 컨택홀(140a, 140b)은 게이트전극(132)의 양측에 게이트전극(132)과 이격되어 위치한다. 여기서, 제1 및 제2 컨택홀(140a, 140b)은 게이트 절연막(130) 내에도 형성된다. 이와 달리, 게이트 절연막(130)이 게이트전극(132)과 동일한 모양으로 패터닝될 경우, 제1 및 제2 컨택홀(140a, 140b)은 층간 절연막(140) 내에만 형성된다.

각 화소영역(P1, P2, P3)에 대응하여 층간 절연막(140) 상부에는 금속과 같은 도전성 물질로 소스 및 드레인전극(142, 144)이 형성된다. 또한, 층간 절연막(140) 상부에는 제2 방향을 따라 연장되는 데이터배선(도시하지 않음)과 전원배선(도시하지 않음) 및 제2 커패시터 전극(도시하지 않음)이 형성될 수 있다.

소스 및 드레인전극(142, 144)은 게이트전극(132)을 중심으로 이격되어 위치하며, 각각 제1 및 제2 컨택홀(140a, 140b)을 통해 반도체층(122)의 양측과 접촉한다. 도시하지 않았지만, 데이터배선은 제2 방향을 따라 연장되고 게이트배선과 교차하여 각 화소영역(P1, P2, P3)을 정의하며, 고전위 전압을 공급하는 전원배선은 데이터배선과 이격되어 위치할 수 있다. 제2 커패시터 전극은 드레인전극(144)과 연결되고, 제1 커패시터 전극과 중첩하여 둘 사이의 층간 절연막(140)을 유전체로 스토리지 커패시터를 이룬다.

한편, 반도체층(122)과, 게이트전극(132), 그리고 소스 및 드레인전극(142, 144)은 박막트랜지스터를 이룬다. 여기서, 박막트랜지스터는 반도체층(122)의 일측, 즉, 반도체층(122)의 상부에 게이트전극(132)과 소스 및 드레인전극(142, 144)이 위치하는 코플라나(coplanar) 구조를 가지며, 이는 탑-게이트(top gate) 구조라고 일컬어지기도 한다.

이와 달리, 박막트랜지스터는 반도체층의 하부에 게이트전극이 위치하고 반도체층의 상부에 소스 및 드레인전극이 위치하는 역 스태거드(inverted staggered) 구조를 가질 수 있으며, 이는 버텀-게이트(bottom gate) 구조라고 일컬어지기도 한다. 이 경우, 반도체층은 비정질 실리콘으로 이루어질 수 있다.

여기서, 박막트랜지스터는 유기발광다이오드 표시장치의 구동 박막트랜지스터에 해당하며, 구동 박막트랜지스터와 동일한 구조의 스위칭 박막트랜지스터(도시하지 않음)가 각 화소영역(P1, P2, P3)에 대응하여 기판(110) 상에 더 형성된다. 구동 박막트랜지스터의 게이트 전극(132)은 스위칭 박막트랜지스터의 드레인전극(도시하지 않음)에 연결되고 구동 박막트랜지스터의 소스전극(142)은 전원배선(도시하지 않음)에 연결된다. 또한, 스위칭 박막트랜지스터의 게이트전극(도시하지 않음)과 소스전극(도시하지 않음)은 게이트 배선 및 데이터 배선과 각각 연결된다.

소스 및 드레인전극(142, 144) 상부에는 절연물질로 제1 보호막(152)과 제2 보호막(154)이 실질적으로 기판(110) 전면에 순차적으로 형성된다. 제1 보호막(152)은 산화 실리콘(SiO2)이나 질화 실리콘(SiNx)과 같은 무기절연물질로 형성될 수 있으며, 제2 보호막(154)은 벤조사이클로부텐이나 포토 아크릴과 같은 유기절연물질로 형성되어 제2 보호막(154)의 상면은 평탄할 수 있다.

제1 보호막(152)과 제2 보호막(154)은 드레인전극(144)을 노출하는 드레인 컨택홀(156)을 가진다. 여기서, 드레인 컨택홀(156)은 제2 컨택홀(140b) 바로 위에 형성된 것으로 도시되어 있으나, 드레인 컨택홀(156)은 제2 컨택홀(140b)과 이격되어 형성될 수도 있다.

제1 보호막(152)과 제2 보호막(154) 중 하나는 생략될 수도 있으며, 일례로, 무기절연물질로 이루어진 제1 보호막(152)이 생략될 수 있다.

제2 보호막(154) 상부에는 비교적 일함수가 높은 도전성 물질로 제1 전극(162)이 형성된다. 제1 전극(162)은 각 화소영역(P1, P2, P3)마다 형성되고, 드레인 컨택홀(156)을 통해 드레인전극(144)과 접촉한다. 일례로, 비교적 일함수가 높은 도전성 물질은 인듐-틴-옥사이드(indium tin oxide: ITO)나 인듐-징크-옥사이드(indium zinc oxide: IZO)와 같은 투명 도전성 물질일 수 있다.

제1 전극(162) 상부에는 절연물질로 뱅크층(170)이 형성된다. 뱅크층(170)은 각 화소영역(P1, P2, P3)의 가장자리에 대응하여 위치하고, 제1 전극(162)의 가장자리를 덮으며, 제1 전극(162)을 노출하는 투과홀(170a)을 가진다. 인접한 화소영역(P1, P2, P3)의 뱅크층(170)은 서로 연결되어 일체로 형성될 수 있다.

뱅크층(170)은 상대적으로 표면 에너지가 낮은 물질로 이루어져 추후 형성되는 발광층 재료와의 접촉각을 크게 함으로써, 발광층의 형성 시 인접한 화소영역(P1, P2, P3)으로 발광층 재료가 넘치는 것을 방지한다. 이러한 뱅크층(170)은 소수성 특성을 갖는 유기절연물질로 형성될 수 있다. 이와 달리, 뱅크층(170)은 유기절연물질로 형성된 후 소수성 처리를 통해 형성될 수도 있다.

여기서, 제1, 제2, 제3 화소영역(P1, P2, P3)의 뱅크층(170)은 서로 다른 높이를 가지며, 이에 대해 추후 상세히 설명한다.

뱅크층(170)의 투과홀(170a)을 통해 노출된 제1 전극(162) 상부에는 발광층(180)이 형성된다. 각 화소영역(P1, P2, P3)의 발광층(180)은 적, 녹, 청색 빛 중 하나를 방출한다.

여기서, 제1, 제2, 제3 화소영역(P1, P2, P3)의 발광층(180)은 서로 다른 두께를 가진다. 보다 상세하게, 제1, 제2, 제3 화소영역(P1, P2, P3) 각각의 발광층(180)은 발광 파장을 고려하여 마이크로 캐비티 효과를 구현하기 위한 두께를 가지며, 발광 파장이 클수록 발광층(180)의 두께는 커질 수 있다.

일례로, 제1 화소영역(P1)의 발광층(180)은 적색 빛을 방출하고, 제2 화소영역(P2)의 발광층(180)은 녹색 빛을 방출하며, 제3 화소영역(P3)의 발광층(180)은 청색 빛을 방출할 수 있다. 이때, 제2 화소영역(P2)의 발광층(180)의 두께는 제1 화소영역(P1)의 발광층(180)의 두께보다 작고 제3 화소영역(P3)의 발광층(180)의 두께보다 클 수 있다. 여기서, 발광층(180)의 두께는 화소영역(P1, P2, P3)의 중앙에서의 두께를 의미한다.

이러한 발광층(180)은 용액 공정을 통해 형성될 수 있다. 용액 공정으로는 다수의 노즐을 포함하는 분사장치를 이용한 인쇄법이나 코팅법이 이용될 수 있으며, 이에 제한되지 않는다. 일례로, 용액 공정으로 잉크젯 인쇄법(inkjet printing method)이 이용될 수 있다.

도시하지 않았지만, 각 화소영역(P1, P2, P3)의 발광층(180)은 제1 전극(162) 상부로부터 순차적으로 적층된 정공보조층(hole auxiliary layer)과 발광물질층(light-emitting material layer), 그리고 전자보조층(electron auxiliary layer)을 포함한다. 정공보조층은 정공주입층(hole injecting layer)과 정공수송층(hole transporting layer) 중 적어도 하나를 포함할 수 있으며, 전자보조층은 전자수송층(electron transporting layer)과 전자주입층(electron injecting layer) 중 적어도 하나를 포함할 수 있다.

여기서, 각 화소영역(P1, P2, P3)의 발광층(180)의 두께는 정공보조층의 두께에 따라 달라질 수 있다. 즉, 제2 화소영역(P2)의 정공보조층의 두께는 제1 화소영역(P1)의 정공보조층의 두께보다 작고 제3 화소영역(P3)의 정공보조층의 두께보다 클 수 있으며, 이러한 정공보조층의 두께에 따라 제1, 제2, 제3 화소영역(P1, P2, P3)의 발광층(180)은 서로 다른 두께를 가질 수 있다.

한편, 정공보조층과 발광물질층은 투과홀(170a) 내에만 형성되고, 전자보조층은 실질적으로 기판(110) 전면에 형성될 수도 있다. 이때, 정공보조층과 발광물질층은 용액 공정을 통해 형성될 수 있으며, 전자보조층은 진공 증착 공정을 통해 형성될 수 있다.

발광층(180) 상부에는 비교적 일함수가 낮은 도전성 물질로 제2 전극(192)이 기판(110) 전면에 형성된다. 여기서, 제2 전극(192)은 알루미늄(aluminum)이나 마그네슘(magnesium), 은(silver) 또는 이들의 합금으로 형성될 수 있다.

제1 전극(162)과 발광층(180) 및 제2 전극(192)은 유기발광다이오드(De)를 이루며, 제1 전극(162)은 애노드(anode)의 역할을 하고, 제2 전극(192)은 캐소드(cathode)의 역할을 한다.

여기서, 본 발명의 실시예에 따른 유기발광다이오드 표시장치는 발광층(180)으로부터 발광된 빛이 제2 전극(192)을 통해 외부로 출력되는 상부발광방식(top emission type)일 수 있다. 이때, 제1 전극(162)은 불투명 도전성 물질로 이루어진 반사층(도시하지 않음)을 더 포함한다. 일례로, 반사층은 알루미늄-팔라듐-구리(aluminum-paladium-copper: APC) 합금으로 형성될 수 있으며, 제1 전극(162)은 ITO/APC/ITO의 3중층 구조를 가질 수 있다. 또한, 제2 전극(192)은 빛이 투과되도록 비교적 얇은 두께를 가지며, 제2 전극(192)의 빛 투과도는 약 45-50%일 수 있다.

이와 같이, 본 발명의 실시예에 따른 유기발광다이오드 표시장치에서는, 용액 공정을 통해 발광층(180)을 형성함으로써, 대면적 및 고해상도의 표시장치를 제공할 수 있으며, 발광층(180)의 두께를 화소영역(P1, P2, P3)별로 다르게 하여 마이크로 캐비티 효과를 구현함으로써, 색순도 및 광 방출 효율을 높일 수 있다.

이때, 뱅크층(170)의 높이를 화소영역(P1, P2, P3)별로 다르게 하여 각 화소영역(P1, P2, P3)마다 균일한 두께의 발광층(180)을 형성함으로써, 화질을 향상시킬 수 있다.

또한, 불균일한 두께를 갖는 발광층(180)에 의해 야기되는 소비전력의 상승 및 수명의 저하를 방지할 수 있다.

이러한 본 발명의 실시예에 따른 뱅크층(170)의 높이와 발광층(180)의 두께, 특히, 정공보조층의 두께에 대해 도면을 참조하여 보다 상세히 설명한다.

도 5a 내지 도 5c는 본 발명의 실시예에 따른 유기발광다이오드 표시장치의 제조 공정 중 표시장치를 개략적으로 도시한 단면도로, 뱅크층과 정공보조층의 형성 단계를 나타낸다. 여기서, 정공보조층은 정공주입층일 수 있다.

도 5a에 도시한 바와 같이, 기판(110) 상에 제1, 제2, 제3 화소영역(P1, P2, P3)이 정의된다. 여기서, 제1, 제2, 제3 화소영역(P1, P2, P3)은 실질적으로 동일한 면적을 가진다. 일례로, 제1, 제2, 제3 화소영역(P1, P2, P3)은 각각 적, 녹, 청색 화소영역에 해당할 수 있다.

한편, 도시하지 않았지만, 기판(110) 상부에는 각 화소영역(P1, P2, P3)에 대응하여 박막트랜지스터 및 제1 전극(도시하지 않음)이 형성된다.

이어, 제1 전극을 포함하는 기판(110) 상부에 뱅크물질을 도포하고 마스크를 이용한 사진식각공정을 통해 선택적으로 패터닝함으로써, 각 화소영역(P1, P2, P3)에 투과홀(170a)을 갖는 뱅크층(170)을 형성한다. 여기서, 뱅크물질은 소수성 특성을 갖는 유기절연물질일 수 있다. 투과홀(170a)의 면적은 각 화소영역(P1, P2, P3)에서 동일하여 제1, 제2, 제3 화소영역(P1, P2, P3)은 동일한 개구율을 가질 수 있다.

뱅크층(170)은 제1, 제2, 제3 화소영역(P1, P2, P3)에 각각 대응하는 제1, 제2, 제3 뱅크(172, 174, 176)를 포함한다. 제1, 제2, 제3 뱅크(172, 174, 176)는 제1, 제2, 제3 화소영역(P1, P2, P3)의 가장자리에 각각 위치하고, 제1, 제2, 제3 뱅크(172, 174, 176)의 각각은 투과홀(170a)을 통해 하부의 막, 즉, 제1 전극을 노출한다. 인접한 화소영역(P1, P2, P3)의 뱅크층(170)은 서로 연결되어 뱅크층(170)은 실질적으로 기판(110) 전면에 일체로 형성된다. 즉, 인접한 제1 뱅크(172)와 제2 뱅크(174)가 서로 연결되고, 인접한 제2 뱅크(174)와 제3 뱅크(176)가 서로 연결되며, 인접한 제1 뱅크(172)와 제3 뱅크(176)가 서로 연결되어 일체화된다.

제1 화소영역(P1)의 제1 뱅크(172)는 제1 높이(h1)를 갖고, 제2 화소영역(P2)의 제2 뱅크(174)는 제2 높이(h2)를 가지며, 제3 화소영역(P3)의 제3 뱅크(176)는 제3 높이(h3)를 가진다. 여기서, 제1 높이(h1)는 제2 높이(h2)보다 작고 제3 높이(h3)보다 크다.

일례로, 제1 높이(h1)는 1 내지 1.5 ㎛이고, 제2 높이(h2)는 1.5 내지 2.0 ㎛이며, 제3 높이(h3)는 0.7 내지 1 ㎛일 수 있다. 그러나, 이에 제한되지 않는다.

다음, 도 5b에 도시한 바와 같이, 다수의 노즐을 포함하는 분사장치(도시하지 않음)를 이용하여 정공주입물질을 포함하는 용액을 적하함으로써 각 화소영역(P1, P2, P3)의 투과홀(170a) 내에 용액층(182a)을 형성한다.

이때, 각 화소영역(P1, P2, P3)에 대한 용액의 적하 수를 다르게 하여 추후 각 화소영역(P1, P2, P3)별로 형성되는 정공주입층의 두께를 다르게 한다. 용액의 적하 수는 제1, 제2, 제3 화소영역(P1, P2, P3) 순으로 작아질 수 있다.

다음, 도 5c에 도시한 바와 같이, 용액층(도 5b의 182a)을 건조하여 각 화소영역(P1, P2, P3)에 정공주입층(182)을 형성한다. 이때, 제1 화소영역(P1)의 정공주입층(182)은 제1 두께(t1)를 갖고, 제2 화소영역(P2)의 정공주입층(182)은 제2 두께(t2)를 가지며, 제3 화소영역(P3)의 정공주입층(182)은 제3 두께(t3)를 가진다. 여기서, 제1, 제2, 제3 두께(t1, t2, t3)는 각 화소영역(P1, P2, P3)의 중앙에서의 두께를 의미하며, 제2 두께(t2)는 제1 두께(t1)보다 작고 제3 두께(t3)보다 크다.

일례로, 제1 두께(t1)는 70nm 내지 80nm이고, 제2 두께(t2)는 50nm 내지 60nm이며, 제3 두께(t3)는 30nm일 수 있다.

이어, 각 화소영역(P1, P2, P3)의 정공주입층(182) 상부에 용액 공정을 통해 정공수송층(도시하지 않음)과 발광물질층(도시하지 않음)을 순차적으로 형성한다.

이와 같이, 본 발명의 실시예에 따른 유기발광다이오드 표시장치에서는 정공주입층(182)의 두께를 다르게 하여 제1, 제2, 제3 화소영역(P1, P2, P3)의 발광층(도 4의 180)의 두께를 다르게 할 수 있다.

이때, 뱅크층(170)의 높이(h1, h2, h3)를 제1, 제2, 제3 화소영역(P1, P2, P3)별로 다르게 함으로써, 요구되는 두께에 대한 용액의 적하 수를 한정하지 않아도 되므로 오버플로우나 디 현상을 막을 수 있다.

한편, 정공주입층(182)은 제1 화소영역(P1)에서의 제1 두께(t1)가 제2 화소영역(P2)의 제2 두께(t2)에 비해 큰 반면, 뱅크층(170)은 제2 화소영역(P2)의 제2 높이(h2)가 제1 화소영역(P1)의 제1 높이(h1)에 비해 크다. 이는 뱅크층(170)이 높을수록 용액이 건조될 때 화소영역 주변부에 파일업(pile-up) 현상이 발생되어, 화소영역 중앙부의 막의 두께가 얇아지고 중앙부와 주변부의 막의 균일도가 떨어지는 문제점을 해결할 수 있다. 즉, 뱅크층(170)의 높이를 낮출수록 파일업 현상을 완화시켜 정공주입층(182)의 두께를 증가시킬 수 있으며, 뱅크층(170)의 높이를 낮출수록 동일 두께에 대응하는 용액의 적하 수를 줄일 수 있으므로, 가장 두꺼운 정공주입층(182)이 형성되는 제1 화소영역(P1)의 제1 뱅크(172)의 높이를 낮추어 정공주입층(182)의 제1 두께(t1)를 확보하면서 재료를 절감할 수 있기 때문이다.

도 6은 뱅크층의 높이에 따른 정공주입층의 프로파일을 개략적으로 도시한 도면이다. 여기서, 정공주입층을 형성하기 위한 용액의 적하 수, 즉, 적하된 용액의 부피는 동일하며, 샘플1, 2(S1, S2)의 뱅크층은 2 ㎛의 높이를 갖고, 샘플3, 4(S3, S4)의 뱅크층은 1.4 ㎛의 높이를 가지며, 샘플5, 6(S5, S6)의 뱅크층은 0.7 ㎛의 높이를 가진다.

도 6에 도시한 바와 같이, 용액의 적하 수를 동일하게 하여 특정 부피의 용액을 적하하고 건조함으로써 정공주입층을 형성하였을 때, 뱅크층의 높이가 낮아질수록 정공주입층의 두께가 두꺼워지고 균일해지는 것을 확인할 수 있다.

따라서, 본 발명에서는 제1 화소영역(도 5c의 P1)의 뱅크층(도 5c의 172) 높이를 제2 화소영역(도 5c의 P2)의 뱅크층(도 5c의 174) 높이보다 낮추어, 제1 화소영역(도 5c의 P1)의 정공주입층(도 5c의 182)의 제1 두께(t1)를 제2 화소영역(도 5c의 P2)의 정공주입층(도 5c의 182)의 제2 두께(t2)에 비해 두껍게 하면서, 제1 화소영역(도 5c의 P1)에 대한 용액의 적하 수를 줄여 재료를 절감할 수 있다.

도 7a 내지 도 7c는 정공주입층의 프로파일에 따른 정공수송층 및 발광물질층의 프로파일을 개략적으로 도시한 도면으로, 도 7a의 뱅크층은 2 ㎛의 높이를 갖고, 도 7b의 뱅크층은 1.4 ㎛의 높이를 가지며, 도 7c의 뱅크층은 0.7 ㎛의 높이를 가진다.

도 7a 내지 도 7c에 도시한 바와 같이, 정공주입층의 프로파일에 따라 정공주입층 상부에 형성되는 정공수송층 및 발광물질층의 프로파일이 결정되는 것을 알 수 있다.

따라서, 본 발명의 실시예에서는 뱅크층의 높이를 조절하여 정공주입층의 최적 두께 및 프로파일을 확보할 수 있다.

도 8은 본 발명의 실시예에 따른 뱅크층의 다른 예를 개략적으로 도시한 단면도이다.

도 8에 도시한 바와 같이, 기판(110) 상의 각 화소영역(P1, P2, P3)에 투과홀(170a)을 갖는 뱅크층(170)이 형성되고, 뱅크층(170)은 제1, 제2, 제3 화소영역(P1, P2, P3) 각각에 대응하는 제1, 제2, 제3 뱅크(172, 174, 176)를 포함한다. 제1, 제2, 제3 뱅크(172, 174, 176)는 각각 제1, 제2, 제3 높이(h1, h2, h3)를 가지며, 제1 높이(h1)는 제2 높이(h2)보다 작고 제3 높이(h3)보다 크다. 인접한 뱅크(172, 174, 176)는 서로 연결되어 일체로 형성될 수 있다.

한편, 제1 뱅크(172)와 제3 뱅크(176)는 제2 뱅크(174)의 제2 높이(h2)에 대응하는 단차부(172a, 176a)를 각각 포함한다.

이러한 뱅크층(170)은 한 화소영역(P1, P2, P3)의 용액층이 인접한 화소영역(P1, P2, P3)으로 침투하는 것을 방지하는데 보다 유리하다.

앞서 언급한 본 발명의 실시예에서는 화소영역의 면적, 특히, 개구율이 동일한 경우에 대해 설명하였으나, 이에 제한되지 않는다.

보다 상세하게, 적, 녹, 청색 발광물질은 수명이 다르므로, 수명이 낮은 발광물질이 포함되는 화소영역의 개구율을 크게 하여 각 화소영역에서의 수명을 균일하게 할 수 있다. 이때, 개구율이 커질수록 화소영역의 면적도 커질 수 있다.

또한, 개구율이 동일한 앞선 실시예에서는 가장 두꺼운 정공주입층이 형성되는 화소영역의 뱅크층의 높이를 낮추었으나, 개구율이 다른 경우, 용액의 적하 수가 가장 많은 화소영역의 뱅크층의 높이를 낮출 수 있다.

상기에서는 본 발명의 바람직한 실시예를 참조하여 설명하였지만, 해당 기술분야의 통상의 지식을 가진 자는 하기의 특허청구범위에 기재된 본 발명의 기술적 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 수 있을 것이다.

110: 기판

122: 반도체층

130: 게이트 절연막 132: 게이트전극

140: 층간 절연막 140a, 140b: 제1 및 제2 컨택홀

142: 소스전극 144: 드레인전극

152, 154: 제1 및 제2 보호막 156: 드레인 컨택홀

162: 재1전극 170: 뱅크층

170a: 투과홀 180: 발광층

192: 제2 전극 De: 유기발광다이오드

130: 게이트 절연막 132: 게이트전극

140: 층간 절연막 140a, 140b: 제1 및 제2 컨택홀

142: 소스전극 144: 드레인전극

152, 154: 제1 및 제2 보호막 156: 드레인 컨택홀

162: 재1전극 170: 뱅크층

170a: 투과홀 180: 발광층

192: 제2 전극 De: 유기발광다이오드

Claims (10)

- 제1, 제2, 제3 화소영역이 정의된 기판과;

상기 기판 상의 상기 제1, 제2, 제3 화소영역의 각각에 위치하는 제1 전극과;

상기 제1 전극의 가장자리를 덮는 뱅크층과;

상기 뱅크층 내의 상기 제1 전극 상부의 발광층과;

상기 발광층 상부의 제2 전극

을 포함하고,

상기 제1 화소영역의 뱅크층은 제1 높이를 가지며 상기 제2 화소영역의 뱅크층은 상기 제1 높이보다 큰 제2 높이를 가지는 유기발광다이오드 표시장치.

- 제1항에 있어서,

상기 제1 화소영역의 중앙에서 발광층의 두께는 상기 제2 화소영역의 중앙에서 발광층 두께보다 큰 유기발광다이오드 표시장치.

- 제2항에 있어서,

상기 제1 및 제2 화소영역의 발광층 각각은 정공보조층과 발광물질층 및 전자보조층을 포함하고, 상기 제1 화소영역의 중앙에서 정공보조층의 두께는 상기 제2 화소영역의 중앙에서 정공보조층의 두께보다 큰 유기발광다이오드 표시장치.

- 제2항에 있어서,

상기 제1 화소영역과 상기 제2 화소영역은 동일한 개구율을 가지는 유기발광다이오드 표시장치.

- 제2항에 있어서,

상기 제1 화소영역의 발광층은 상기 제2 화소영역의 발광층보다 긴 파장의 빛을 방출하는 유기발광다이오드 표시장치.

- 제1항에 있어서,

상기 제1 화소영역의 뱅크층은 상기 제1 화소영역의 뱅크층에 인접한 상기 제2 화소영역의 뱅크층과 연결되어 서로 일체화되는 유기발광다이오드 표시장치.

- 제1항 내지 제6항 중 어느 한 항에 있어서,

상기 제3 화소영역의 뱅크층은 상기 제1 높이보다 낮은 제3 높이를 가지는 유기발광다이오드 표시장치.

- 제7항에 있어서,

상기 제3 화소영역의 중앙에서 발광층의 두께는 상기 제2 화소영역의 중앙에서 발광층 두께보다 작은 유기발광다이오드 표시장치.

- 제8항에 있어서,

상기 제3 화소영역의 발광층은 상기 제2 화소영역의 발광층보다 짧은 파장의 빛을 방출하는 유기발광다이오드 표시장치.

- 제8항에 있어서,

상기 제2 화소영역의 뱅크층은 상기 제2 화소영역의 뱅크층에 인접한 상기 제3 화소영역의 뱅크층과 연결되어 서로 일체화되는 유기발광다이오드 표시장치.

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020160097257A KR102574594B1 (ko) | 2016-07-29 | 2016-07-29 | 유기발광다이오드 표시장치 |

| US15/635,888 US10141377B2 (en) | 2016-07-29 | 2017-06-28 | Electroluminescent display device |

| CN201710536525.0A CN107665904B (zh) | 2016-07-29 | 2017-07-04 | 电致发光显示装置 |

| EP17180877.7A EP3276690B1 (en) | 2016-07-29 | 2017-07-12 | Electroluminescent display device |

| US16/166,782 US10553649B2 (en) | 2016-07-29 | 2018-10-22 | Electroluminescent display device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020160097257A KR102574594B1 (ko) | 2016-07-29 | 2016-07-29 | 유기발광다이오드 표시장치 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20180013469A true KR20180013469A (ko) | 2018-02-07 |

| KR102574594B1 KR102574594B1 (ko) | 2023-09-04 |

Family

ID=61204044

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020160097257A KR102574594B1 (ko) | 2016-07-29 | 2016-07-29 | 유기발광다이오드 표시장치 |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR102574594B1 (ko) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20200071428A (ko) * | 2018-12-11 | 2020-06-19 | 엘지디스플레이 주식회사 | 유기전계발광 표시장치 및 그 제조방법 |

| KR20210015258A (ko) * | 2019-08-01 | 2021-02-10 | 엘지디스플레이 주식회사 | 전계발광 표시장치 |

| US11063099B2 (en) | 2018-12-11 | 2021-07-13 | Lg Display Co., Ltd. | Organic light-emitting display device |

| KR20220096392A (ko) * | 2020-12-31 | 2022-07-07 | 엘지디스플레이 주식회사 | 유기 발광 표시 장치 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2012017498A1 (ja) * | 2010-08-06 | 2012-02-09 | パナソニック株式会社 | 有機el表示パネルとその製造方法 |

| KR20140050933A (ko) * | 2012-10-22 | 2014-04-30 | 삼성디스플레이 주식회사 | 유기발광장치 및 그것의 제조방법 |

| KR20160039105A (ko) * | 2014-09-30 | 2016-04-08 | 엘지디스플레이 주식회사 | 유기발광표시장치 |

-

2016

- 2016-07-29 KR KR1020160097257A patent/KR102574594B1/ko active IP Right Grant

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2012017498A1 (ja) * | 2010-08-06 | 2012-02-09 | パナソニック株式会社 | 有機el表示パネルとその製造方法 |

| KR20140050933A (ko) * | 2012-10-22 | 2014-04-30 | 삼성디스플레이 주식회사 | 유기발광장치 및 그것의 제조방법 |

| KR20160039105A (ko) * | 2014-09-30 | 2016-04-08 | 엘지디스플레이 주식회사 | 유기발광표시장치 |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20200071428A (ko) * | 2018-12-11 | 2020-06-19 | 엘지디스플레이 주식회사 | 유기전계발광 표시장치 및 그 제조방법 |

| US11063099B2 (en) | 2018-12-11 | 2021-07-13 | Lg Display Co., Ltd. | Organic light-emitting display device |

| KR20210015258A (ko) * | 2019-08-01 | 2021-02-10 | 엘지디스플레이 주식회사 | 전계발광 표시장치 |

| KR20220096392A (ko) * | 2020-12-31 | 2022-07-07 | 엘지디스플레이 주식회사 | 유기 발광 표시 장치 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR102574594B1 (ko) | 2023-09-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP3276690B1 (en) | Electroluminescent display device | |

| EP3321985B1 (en) | Electroluminescent display device and method of fabricating the same | |

| US10170521B2 (en) | Organic light-emitting diode display device | |

| KR102690328B1 (ko) | 유기발광다이오드 표시장치 | |

| KR20150042367A (ko) | 유기전계 발광소자 및 이의 제조 방법 | |

| US10872948B2 (en) | Electroluminescent display device | |

| JP6868676B2 (ja) | 電界発光表示装置およびその製造方法 | |

| KR102309282B1 (ko) | 유기발광다이오드 표시장치 | |

| US11018198B2 (en) | Electroluminescent display device | |

| CN108258132B (zh) | 电致发光显示装置 | |

| KR20180077856A (ko) | 전계발광 표시장치 | |

| US10797127B2 (en) | Electroluminescent display device | |

| KR102574594B1 (ko) | 유기발광다이오드 표시장치 | |

| US11658205B2 (en) | Electroluminescent display device | |

| KR102284991B1 (ko) | 유기발광다이오드 표시장치 | |

| KR102546420B1 (ko) | 전계발광 표시장치 및 그 제조방법 | |

| KR20180077855A (ko) | 전계발광 표시장치 및 그 제조 방법 | |

| KR102702327B1 (ko) | 유기발광다이오드 표시장치 | |

| KR102503745B1 (ko) | 전계발광 표시장치 | |

| KR20180077833A (ko) | 전계발광 표시장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant |