KR102009188B1 - Filter chip package and RF front-end module having improved skirt feature - Google Patents

Filter chip package and RF front-end module having improved skirt feature Download PDFInfo

- Publication number

- KR102009188B1 KR102009188B1 KR1020180018327A KR20180018327A KR102009188B1 KR 102009188 B1 KR102009188 B1 KR 102009188B1 KR 1020180018327 A KR1020180018327 A KR 1020180018327A KR 20180018327 A KR20180018327 A KR 20180018327A KR 102009188 B1 KR102009188 B1 KR 102009188B1

- Authority

- KR

- South Korea

- Prior art keywords

- electrode

- bulk

- filter chip

- acoustic wave

- wave filter

- Prior art date

Links

- 230000000903 blocking effect Effects 0.000 claims abstract description 11

- 238000010897 surface acoustic wave method Methods 0.000 claims description 68

- 230000005540 biological transmission Effects 0.000 claims description 13

- 125000006850 spacer group Chemical group 0.000 claims description 8

- 238000000034 method Methods 0.000 claims description 5

- 108090000841 L-Lactate Dehydrogenase (Cytochrome) Proteins 0.000 claims 4

- 101150012619 FCS1 gene Proteins 0.000 claims 2

- 239000000758 substrate Substances 0.000 description 23

- 238000010295 mobile communication Methods 0.000 description 8

- 238000000465 moulding Methods 0.000 description 7

- 239000000463 material Substances 0.000 description 4

- 238000012545 processing Methods 0.000 description 4

- 239000004065 semiconductor Substances 0.000 description 4

- 238000005516 engineering process Methods 0.000 description 3

- 238000001914 filtration Methods 0.000 description 3

- 230000000694 effects Effects 0.000 description 2

- 230000008030 elimination Effects 0.000 description 2

- 238000003379 elimination reaction Methods 0.000 description 2

- 229920006336 epoxy molding compound Polymers 0.000 description 2

- 230000014509 gene expression Effects 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 229910000679 solder Inorganic materials 0.000 description 2

- 244000126211 Hericium coralloides Species 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000005496 eutectics Effects 0.000 description 1

- 239000012778 molding material Substances 0.000 description 1

- 238000004806 packaging method and process Methods 0.000 description 1

- 230000008707 rearrangement Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H9/00—Networks comprising electromechanical or electro-acoustic devices; Electromechanical resonators

- H03H9/46—Filters

- H03H9/54—Filters comprising resonators of piezoelectric or electrostrictive material

- H03H9/56—Monolithic crystal filters

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H3/00—Apparatus or processes specially adapted for the manufacture of impedance networks, resonating circuits, resonators

- H03H3/007—Apparatus or processes specially adapted for the manufacture of impedance networks, resonating circuits, resonators for the manufacture of electromechanical resonators or networks

- H03H3/02—Apparatus or processes specially adapted for the manufacture of impedance networks, resonating circuits, resonators for the manufacture of electromechanical resonators or networks for the manufacture of piezoelectric or electrostrictive resonators or networks

- H03H3/04—Apparatus or processes specially adapted for the manufacture of impedance networks, resonating circuits, resonators for the manufacture of electromechanical resonators or networks for the manufacture of piezoelectric or electrostrictive resonators or networks for obtaining desired frequency or temperature coefficient

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H9/00—Networks comprising electromechanical or electro-acoustic devices; Electromechanical resonators

- H03H9/02—Details

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H9/00—Networks comprising electromechanical or electro-acoustic devices; Electromechanical resonators

- H03H9/15—Constructional features of resonators consisting of piezoelectric or electrostrictive material

- H03H9/17—Constructional features of resonators consisting of piezoelectric or electrostrictive material having a single resonator

Landscapes

- Physics & Mathematics (AREA)

- Acoustics & Sound (AREA)

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Surface Acoustic Wave Elements And Circuit Networks Thereof (AREA)

Abstract

Description

본 발명은 스커트 특성이 향상된 필터 칩 패키지 및 고주파 프론트 엔드 모듈에 관한 것으로서, 더욱 상세하게는 특정 주파수 대역에 대한 스커트 특성이 향상된 필터 칩 패키지 및 고주파 프론트 엔드 모듈에 관한 것이다.The present invention relates to a filter chip package and a high frequency front end module with improved skirt characteristics, and more particularly, to a filter chip package and a high frequency front end module with improved skirt characteristics for a specific frequency band.

이동통신 기술이 발달하면서 고주파(RF) 신호를 필터링(filtering)하는 다양한 필터가 등장하였다. 이러한 고주파(RF) 신호에 대한 필터로는 표면 탄성파 필터(SAW Filter: SurfaceAcoustic Wave Filter), 벌크 탄성파 필터(BAW Filter: BulkAcoustic Wave Filter) 등이 있다. 다만, 표면 탄성파 필터(SAW Filter: SurfaceAcoustic Wave Filter)로는 고대역 및 광대역폭의 고주파(RF) 신호 처리를 요구하는 최신 이동통신 기술에 대응하기 어려워, 해당 요구 조건을 만족시킬 수 있는 벌크 탄성파 필터(BAW Filter)의 수요가 최근 들어 더 증대되고 있다. With the development of mobile communication technology, various filters for filtering high frequency (RF) signals have emerged. Filters for such high frequency (RF) signals include surface acoustic wave filters (SAW filters) and bulk acoustic wave filters (BAW filters). However, the SAW Filter (Surface Acoustic Wave Filter) is difficult to cope with the latest mobile communication technology requiring high frequency and wideband high frequency (RF) signal processing. The demand for BAW filters has been increasing recently.

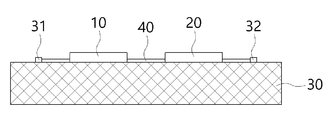

도 1은 통상적인 벌크 탄성파 필터 칩(10) 및 표면 탄성파 필터 칩(20)의 구조를 나타낸다.1 shows the structure of a conventional bulk acoustic

벌크 탄성파 필터 칩(10)은 벌크 탄성파 필터 기능을 수행하는 반도체 집적회로 칩으로서, 도 1에 도시된 바와 같이, 전극으로 작용하는 제1 벌크용 전극(11) 및 제2 벌크용 전극(12)과, 이들 전극(11, 12) 사이에 마련되고 압전 물질로 이루어진 벌크용 압전층(13)을 각각 포함한다. 이때, 전기적 신호에 의해 벌크용 압전층(3) 내에 발생되는 탄성파 전파 속도가 빨라 같은 주파수라도 음파의 파장이 짧아지며, 이에 따라, 벌크 탄성파 필터 칩(10)은 소형화가 가능한 이점이 있다.The bulk acoustic

표면 탄성파 필터 칩(20)은 표면 탄성파 필터 기능을 수행하는 반도체 집적회로 칩으로서, 도 1에 도시된 바와 같이, 전극으로 작용하는 서로 이격된 빗살무늬 형태의 제1 표면용 전극(21) 및 제2 표면용 전극(22)과, 그 일측 면에 이들 전극(21, 22)이 마련된 표면용 압전층(23)을 포함한다. 이때, 표면 탄성파 필터 칩(20)은 차단 기울기가 날카로운 스커트 특성을 가지므로, 뛰어난 대역외 제거 성능을 갖는다.The surface acoustic

또한, 벌크 탄성파 필터 칩(10) 및 표면 탄성파 필터 칩(20)의 상부 또는 하부에는 기판이 구비될 수 있다.In addition, a substrate may be provided above or below the bulk acoustic

한편, 벌크 탄성파 필터 칩(10)은 이동통신 단말기의 고주파(RF) 프론트 엔드 모듈(Front-End Module)의 필터부에 포함되어, 고주파(RF) 신호 중 원하는 주파수 대역만을 통과시키는 기능을 담당한다. 하지만, 차단 기울기가 완만한 스커트 특성을 가지는 벌크 탄성파 필터 칩(10)만으로는 대역외 제거 성능이 떨어지는 문제점이 있었다.Meanwhile, the bulk acoustic

상기한 바와 같은 종래 기술의 문제점을 해결하기 위하여, 본 발명은 벌크 탄성파 필터(BAW Filter)를 통과한 신호가 표면 탄성파 필터(SAW Filter)를 통과하여 출력되게 함으로써, 차단 기울기가 날카로운 스커트 특성을 가지는 필터 칩 패키지 및 고주파 프론트 엔드 모듈을 제공하는데 그 목적이 있다.In order to solve the problems of the prior art as described above, the present invention allows the signal passing through the bulk acoustic wave filter (BAW Filter) is output through the surface acoustic wave filter (SAW Filter), so that the cutoff slope has a sharp skirt characteristics Its purpose is to provide a filter chip package and a high frequency front end module.

다만, 본 발명이 해결하고자 하는 과제는 이상에서 언급한 과제에 제한되지 않으며, 언급되지 않은 또 다른 과제들은 아래의 기재로부터 당업자에게 명확하게 이해될 수 있을 것이다.However, the problem to be solved by the present invention is not limited to the above-mentioned problem, another task that is not mentioned will be clearly understood by those skilled in the art from the following description.

상기와 같은 과제를 해결하기 위한 본 발명의 일 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지는, (1) 입출력 신호가 인가되는 제1 베이스 전극 및 제2 베이스 전극을 구비하는 베이스, (2) 제1 벌크용 전극 및 제2 벌크용 전극과, 제1 벌크용 전극 및 제2 벌크용 전극 사이의 벌크용 압전층을 각각 구비하고, 제1 벌크용 전극이 제1 베이스 전극과 연결되며, 베이스의 상부에 마련되는 벌크 탄성파 필터 칩, (3) 표면용 압전층과, 표면용 압전층의 상부에 서로 이격되게 구비된 제1 표면용 전극 및 제2 표면용 전극을 각각 구비하고, 제1 표면용 전극이 제2 벌크용 전극과 연결되며, 제2 표면용 전극이 제2 베이스 전극과 연결되고, 베이스의 상부에 마련되는 표면 탄성파 필터 칩을 포함하며, 상기 표면 탄성파 필터 칩의 차단 기울기는 상기 벌크 탄성파 필터 칩의 차단 기울기 보다 클 수 있다.According to an aspect of the present invention, there is provided a filter chip package having improved skirt characteristics, including (1) a base having a first base electrode and a second base electrode to which an input / output signal is applied, and (2) A bulk piezoelectric layer between the first bulk electrode and the second bulk electrode, and the first bulk electrode and the second bulk electrode, wherein the first bulk electrode is connected to the first base electrode, A bulk acoustic wave filter chip provided on an upper portion of the upper surface of the piezoelectric layer, and (3) a piezoelectric layer for a surface, and a first surface electrode and a second surface electrode provided on the upper surface of the surface piezoelectric layer and spaced apart from each other, respectively. A fork electrode is connected to the second bulk electrode, a second surface electrode is connected to the second base electrode, and includes a surface acoustic wave filter chip provided on an upper portion of the base, and the blocking slope of the surface acoustic wave filter chip is Bulk acoustic wave filter The blocking slope of the chip can be greater than.

상기 벌크 탄성파 필터 칩은 저역 차단 주파수 FCB1과 고역 차단 주파수 FCB2의 사이를 통과시키는 대역 통과 필터고, 상기 표면 탄성파 필터 칩은 제1 저역 차단 주파수 FCS1과 제1 고역 차단 주파수 FCS2의 사이를 차단하고 제2 저역 차단 주파수 FCS3과 제2 고역 차단 주파수 FCS4의 사이를 차단하는 대역 제거 필터이다. 이때, 상기 FCB1은 상기 FCS2 보다 작으며, 상기 FCB2는 상기 FCS3 보다 크다.The bulk acoustic wave filter chip is a band pass filter that passes between a low pass frequency F CB1 and a high pass cut frequency F CB2 , and the surface acoustic wave filter chip is between a first low pass cut frequency F CS1 and a first high pass cut frequency F CS2 . And a band reject filter for blocking between the second low pass frequency F CS3 and the second high pass cut frequency F CS4 . In this case, the F CB1 is smaller than the F CS2 , and the F CB2 is larger than the F CS3 .

상기 FCS1과 상기 FCS2의 사이에 FCB1이 위치할 수 있으며, 상기 FCS3과 상기 FCS4의 사이에 FCB2가 위치할 수 있다.F CB1 may be located between the F CS1 and the F CS2 , and F CB2 may be located between the F CS3 and the F CS4 .

본 발명의 일 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지는 상기 제2 벌크용 전극과 상기 제1 표면용 전극 사이에 연결되며, 상기 벌크 탄성파 필터 칩과 상기 표면 탄성파 필터 칩을 매칭시키는 매칭부를 더 포함할 수 있다.The filter chip package having an improved skirt characteristic according to an embodiment of the present invention is connected between the second bulk electrode and the first surface electrode, and a matching unit for matching the bulk acoustic wave filter chip and the surface acoustic wave filter chip. It may further include.

상기 벌크 탄성파 필터 칩과 상기 표면 탄성파 필터 칩은 베이스 상에 나란하게 배치될 수 있다.The bulk acoustic wave filter chip and the surface acoustic wave filter chip may be disposed side by side on a base.

상기 베이스 상에 벌크 탄성파 필터 칩이 배치되며, 상기 벌크 탄성파 필터 칩 상에 상기 표면 탄성파 필터 칩이 적층되게 배치될 수 있다.A bulk acoustic wave filter chip may be disposed on the base, and the surface acoustic wave filter chip may be stacked on the bulk acoustic wave filter chip.

본 발명의 일 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지는, (1) 필터 칩이 포함되는 내부 공간을 베이스와의 사이에 구비하도록 베이스 상에 마련된 캡, (2) 필터 칩 주변을 폐곡선 형태로 둘러쌈으로써 밀봉된 상기 내부 공간을 형성하는 스페이서를 더 포함할 수 있다.The filter chip package having improved skirt characteristics according to an embodiment of the present invention includes: (1) a cap provided on the base to have an internal space including the filter chip between the base, and (2) a closed curve around the filter chip. It may further include a spacer to form the inner space sealed by enclosing.

본 발명의 일 실시예에 따른 고주파 프론트 엔드 모듈은 고주파 신호에 대해 송수신 신호를 분리하는 고주파 프론트 엔드 모듈로서, (1) 입출력 신호가 인가되는 제1 베이스 전극 및 제2 베이스 전극을 구비하는 인쇄회로기판, (2) 인쇄회로기판 상에 구비되고, 각각이 서로 다른 주파수 대역을 통과시키는 하나 이상의 채널 필터부를 포함한다.The high frequency front end module according to an embodiment of the present invention is a high frequency front end module that separates a transmission / reception signal from a high frequency signal, and (1) a printed circuit having a first base electrode and a second base electrode to which an input / output signal is applied. A substrate, (2) comprising at least one channel filter portion provided on the printed circuit board, each passing a different frequency band.

어느 한 채널 필터부는, (1) 제1 벌크용 전극 및 제2 벌크용 전극과, 제1 벌크용 전극 및 제2 벌크용 전극 사이의 벌크용 압전층을 각각 구비하고, 제1 벌크용 전극이 제1 베이스 전극과 연결되는 벌크 탄성파 필터 칩, (2) 표면용 압전층과, 표면용 압전층의 상부에 서로 이격되게 구비된 제1 표면용 전극 및 제2 표면용 전극을 각각 구비하고, 제1 표면용 전극이 제2 벌크용 전극과 연결되며, 제2 표면용 전극이 제2 베이스 전극과 연결되는 표면 탄성파 필터 칩을 포함하며, 상기 표면 탄성파 필터 칩의 차단 기울기는 상기 벌크 탄성파 필터 칩의 차단 기울기 보다 크다.One channel filter unit includes (1) a first piezoelectric layer and a bulk piezoelectric layer between the first bulk electrode and the second bulk electrode, and the first bulk electrode and the second bulk electrode. A bulk acoustic wave filter chip connected to the first base electrode, (2) a piezoelectric layer for a surface, and a first surface electrode and a second surface electrode provided on the surface of the piezoelectric layer and spaced apart from each other; And a surface acoustic wave filter chip having a first surface electrode connected to a second bulk electrode and a second surface electrode connected to a second base electrode, wherein the inclination slope of the surface acoustic wave filter chip is determined by the bulk acoustic wave filter chip. Greater than the blocking slope.

상기와 같이 구성되는 본 발명의 일 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지 및 고주파 프론트 엔드 모듈은 벌크 탄성파 필터(BAW Filter)를 통과한 신호가 표면 탄성파 필터(SAW Filter)를 통과하여 출력되게 함으로써, 벌크 탄성파 필터 단독으로는 구현할 수 없는 날카로운 차단 기울기를 갖는 스커트 특성을 구현할 수 있는 이점이 있다.The filter chip package and the high frequency front end module having improved skirt characteristics according to the embodiment of the present invention configured as described above may output a signal passing through a bulk acoustic wave filter through a surface acoustic wave filter. By doing so, there is an advantage in that a skirt characteristic having a sharp cutoff slope cannot be realized by the bulk acoustic wave filter alone.

도 1은 통상적인 벌크 탄성파 필터 칩(10) 및 표면 탄성파 필터 칩(20)의 구조를 나타낸다.

도 2는 수평형으로 구현된 본 발명의 일 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지의 전체적인 측면 구조를 나타낸다.

도 3은 수평형으로 구현된 본 발명의 제1 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지의 보다 상세한 측면 구조를 나타낸다.

도 4는 수평형으로 구현된 본 발명의 제2 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지의 보다 상세한 측면 구조를 나타낸다.

도 5는 수평형으로 구현된 본 발명의 제3 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지의 보다 상세한 측면 구조를 나타낸다.

도 6은 수평형으로 구현된 본 발명의 제4 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지의 보다 상세한 측면 구조를 나타낸다.

도 7은 수평형으로 구현된 본 발명의 일 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지가 몰딩층(50)을 더 포함하는 경우의 전체적인 측면 구조를 나타낸다.

도 8은 수평형으로 구현된 본 발명의 일 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지가 캡(60)을 더 포함하는 경우의 전체적인 측면 구조를 나타낸다.

도 9는 수직형으로 구현된 본 발명의 일 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지의 전체적인 측면 구조를 나타낸다.

도 10은 수직형으로 구현된 본 발명의 제1 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지의 보다 상세한 측면 구조를 나타낸다.

도 11은 수직형으로 구현된 본 발명의 제2 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지의 보다 상세한 측면 구조를 나타낸다.

도 12는 수직형으로 구현된 본 발명의 일 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지가 몰딩층(50)을 더 포함하는 경우의 전체적인 측면 구조를 나타낸다.

도 13은 수직형으로 구현된 본 발명의 일 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지가 캡(60)을 더 포함하는 경우의 전체적인 측면 구조를 나타낸다.

도 14는 본 발명의 일 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지에서 벌크 탄성파 필터 칩(10)과 표면 탄성파 필터 칩(20)의 필터링 특성을 나타낸다.

도 15는 본 발명의 일 실시예에 따른 고주파 프론트 엔드 모듈(RF front-end module)의 전체적인 구성을 나타낸다.1 shows the structure of a conventional bulk acoustic

Figure 2 shows the overall side structure of the filter chip package with improved skirt characteristics according to an embodiment of the present invention implemented in a horizontal type.

Figure 3 shows a more detailed side structure of the filter chip package with improved skirt characteristics according to the first embodiment of the present invention implemented in a horizontal type.

Figure 4 shows a more detailed side structure of the filter chip package with improved skirt characteristics according to the second embodiment of the present invention implemented in a horizontal type.

Figure 5 shows a more detailed side structure of the filter chip package with improved skirt characteristics according to the third embodiment of the present invention implemented in a horizontal type.

6 illustrates a more detailed side structure of a filter chip package having improved skirt characteristics according to a fourth embodiment of the present invention implemented in a horizontal type.

FIG. 7 illustrates an overall side structure when the filter chip package having the improved skirt property according to the exemplary embodiment of the present invention further includes a

FIG. 8 shows the overall side structure of the case where the filter chip package having improved skirt characteristics according to the embodiment of the present invention, which is implemented in a horizontal type, further includes a

FIG. 9 illustrates an overall side structure of a filter chip package having improved skirt characteristics according to an exemplary embodiment of the present invention, which is vertically implemented.

FIG. 10 illustrates a more detailed side structure of a filter chip package having improved skirt characteristics according to the first embodiment of the present invention, which is embodied vertically.

FIG. 11 illustrates a more detailed side structure of a filter chip package having improved skirt characteristics according to a second embodiment of the present invention, which is embodied vertically.

12 illustrates the overall side structure of the case where the filter chip package having the improved skirt property according to the exemplary embodiment of the present invention further includes a

FIG. 13 shows the overall side structure of the case where the filter chip package having the improved skirt property according to the exemplary embodiment of the present invention further includes a

FIG. 14 illustrates filtering characteristics of the bulk acoustic

FIG. 15 shows the overall configuration of an RF front-end module according to an embodiment of the present invention.

본 발명의 상기 목적과 수단 및 그에 따른 효과는 첨부된 도면과 관련한 다음의 상세한 설명을 통하여 보다 분명해 질 것이며, 그에 따라 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자가 본 발명의 기술적 사상을 용이하게 실시할 수 있을 것이다. 또한, 본 발명을 설명함에 있어서 본 발명과 관련된 공지 기술에 대한 구체적인 설명이 본 발명의 요지를 불필요하게 흐릴 수 있다고 판단되는 경우에는 그 상세한 설명을 생략하기로 한다.The above objects, means, and effects thereof will become more apparent from the following detailed description taken in conjunction with the accompanying drawings, and as a result, those skilled in the art to which the present invention pertains may easily facilitate the technical idea of the present invention. It can be done. In addition, in describing the present invention, when it is determined that the detailed description of the known technology related to the present invention may unnecessarily obscure the gist of the present invention, the detailed description thereof will be omitted.

또한, 본 명세서에서 사용된 용어는 실시예들을 설명하기 위한 것이며, 본 발명을 제한하고자 하는 것은 아니다. 본 명세서에서, 단수형은 문구에서 특별히 언급하지 않는 한 경우에 따라 복수형도 포함한다. 명세서에서 사용되는 "포함하다", “구비하다”, “마련하다” 또는 “가지다” 등의 용어는 언급된 구성요소 외의 하나 이상의 다른 구성요소의 존재 또는 추가를 배제하지 않는다.Also, the terminology used herein is for the purpose of describing particular embodiments only and is not intended to be limiting of the invention. In this specification, the singular forms also include the plural forms as the case otherwise indicates. As used herein, the terms "comprise," "comprise," "presume" or "have" do not exclude the presence or addition of one or more components other than the components mentioned.

본 명세서에서, “또는”, “적어도 하나” 등의 표현은 함께 나열된 단어들 중 하나를 나타내거나, 또는 둘 이상의 조합을 나타낼 수 있다. 예를 들어, “A 또는 B”, “A 및 B 중 적어도 하나”는 A 또는 B 중 하나만을 포함할 수 있고, A와 B를 모두 포함할 수도 있다.In this specification, expressions such as “or”, “at least one,” and the like may represent one of the words listed together or a combination of two or more. For example, “A or B”, “at least one of A and B” may include only one of A or B, and may include both A and B.

본 명세서에서, “예를 들어”와 같은 표현에 따라는 설명은 인용된 특성, 변수, 또는 값과 같이 제시한 정보들이 정확하게 일치하지 않을 수 있고, 허용 오차, 측정 오차, 측정 정확도의 한계와 통상적으로 알려진 기타 요인을 비롯한 변형과 같은 효과로 본 발명의 다양한 실시 예에 따른 발명의 실시 형태를 한정하지 않아야 할 것이다.In this specification, descriptions according to expressions such as “for example” may not exactly match the information presented, such as the recited characteristics, variables, or values, and are typical of tolerances, measurement errors, and limits of measurement accuracy. Embodiments of the invention according to various embodiments of the present invention should not be limited to such effects as modifications including other factors.

본 명세서에서, 어떤 구성요소가 다른 구성요소에 '연결되어’ 있다거나 '접속되어' 있다고 언급된 때에는, 그 다른 구성요소에 직접적으로 연결되어 있거나 또는 접속되어 있을 수도 있지만, 중간에 다른 구성요소가 존재할 수도 있다고 이해되어야 할 것이다. 반면에, 어떤 구성요소가 다른 구성 요소에 '직접 연결되어' 있다거나 '직접 접속되어' 있다고 언급된 때에는, 중간에 다른 구성요소가 존재하지 않는 것으로 이해될 수 있어야 할 것이다.In the present specification, when a component is referred to as being 'connected' or 'connected' to another component, it may be directly connected to or connected to the other component, but another component may be It should be understood that it may exist. On the other hand, when a component is said to be 'directly connected' or 'directly connected' to another component, it should be understood that there is no other component in between.

본 명세서에서, 'A의 주변'이라고 언급된 때에는, A를 중심에 두고 A의 바깥쪽에 위치하는 영역을 지칭하는 것으로 이해되어야 할 것이다.In the present specification, when referred to as the 'periphery of A', it should be understood to refer to an area located outside of A with respect to A.

다른 정의가 없다면, 본 명세서에서 사용되는 모든 용어는 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 공통적으로 이해될 수 있는 의미로 사용될 수 있을 것이다. 또, 일반적으로 사용되는 사전에 정의되어 있는 용어들은 명백하게 특별히 정의되어 있지 않는 한 이상적으로 또는 과도하게 해석되지 않는다. Unless otherwise defined, all terms used in the present specification may be used in a sense that can be commonly understood by those skilled in the art. Moreover, the terms defined in the commonly used dictionaries are not ideally or excessively interpreted unless they are specifically defined clearly.

이하, 본 발명의 일 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지에 대하여 상세히 설명하도록 한다.Hereinafter, a filter chip package having improved skirt characteristics according to an embodiment of the present invention will be described in detail.

도 2는 수평형으로 구현된 본 발명의 일 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지의 전체적인 측면 구조를 나타내며, 도 9는 수직형으로 구현된 본 발명의 일 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지의 전체적인 측면 구조를 나타낸다.2 shows the overall side structure of the filter chip package with improved skirt characteristics according to an embodiment of the present invention implemented in a horizontal type, Figure 9 is an improved skirt characteristic according to an embodiment of the present invention implemented in a vertical type The overall side structure of the filter chip package is shown.

본 발명의 일 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지는, 도 1 및 도 9에 도시된 바와 같이, 벌크 탄성파 필터 칩(10), 표면 탄성파 필터 칩(20), 베이스(30) 및 매칭부(40)를 포함한다. 이때, 벌크 탄성파 필터 칩(10)과 표면 탄성파 필터 칩(20)이 배치되는 형태에 따라 도 1과 같은 수평형과, 도 9와 같은 수직형으로 구분된다. 즉, 수평형은 벌크 탄성파 필터 칩(10) 및 표면 탄성파 필터 칩(20)이 베이스(30)의 상부에 나란하게 배치된 것을 지칭한다. 또한, 수직형은 베이스(30) 상에 벌크 탄성파 필터 칩(10)가 마련되고, 벌크 탄성파 필터 칩(10) 상에 표면 탄성파 필터 칩(20)가 마련되어, 벌크 탄성파 필터 칩(10) 및 표면 탄성파 필터 칩(20)가 적층되게 배치된 것을 지칭한다.As shown in FIGS. 1 and 9, a filter chip package having improved skirt characteristics according to an embodiment of the present invention may include a bulk acoustic

벌크 탄성파 필터 칩(10)은 벌크 탄성파를 이용하여 RF 신호 등에 대해 대역 통과 필터로 작용하는 반도체 집적회로 칩으로서, 도 1(a)에 도시된 바와 같은 구조를 갖는다. 즉, 벌크 탄성파 필터 칩(10)은 제1 벌크용 전극(11) 및 제2 벌크용 전극(12)과, 제1 벌크용 전극(11) 및 제2 벌크용 전극(12) 사이의 구비되는 벌크용 압전층(13)을 각각 포함한다. 이때, 제1 벌크용 전극(11)는 전기 신호를 입력 받는 입력 전극이며, 제2 벌크용 전극(12)는 벌크 압전층(13)에서 발생된 벌크 탄성파에 따른 전기 신호를 출력하는 출력 전극이다.The bulk acoustic

표면 탄성파 필터 칩(20)은 표면 탄성파를 이용하여 RF 신호 등에 대해 대역 제거 필터로 작용하는 반도체 집적회로 칩으로서, 도 1(b)에 도시된 바와 같은 구조를 갖는다. 즉, 표면 탄성파 필터 칩(20)은 표면용 압전층(23)과, 표면용 압전층(23)의 상부에 서로 이격되게 구비된 빗살무늬 형태의 제1 표면용 전극(21) 및 제2 표면용 전극(22)을 각각 포함한다. 이때, 제1 표면용 전극(21)는 전기 신호를 입력 받는 입력 전극이며, 제2 표면용 전극(22)는 표면 압전층(23)에서 발생된 표면 탄성파에 따른 전기 신호를 출력하는 출력 전극이다.The surface acoustic

베이스(30)는 기판으로서, 베이스 웨이퍼로부터 절단된 구성일 수 있다. 베이스(30)의 상부에 벌크 탄성파 필터 칩(10) 및 표면 탄성파 필터 칩(20)이 각각 마련된다. 특히, 베이스(30)는 전체 입출력 신호가 인가되는 제1 베이스 전극(31) 및 제2 베이스 전극(32)을 포함한다. 즉, 제1 베이스 전극(31)은 필터 칩 패키지의 전체 입력 신호가 입력되는 입력 전극이며, 제2 베이스 전극(32)은 필터 칩 패키지의 전체 출력 신호가 출력되는 출력 전극이다.The base 30 may be a substrate cut from the base wafer. The bulk acoustic

매칭부(40)는 벌크 탄성파 필터 칩(10)과 표면 탄성파 필터 칩(20)의 사이에 연결되는 임피던스 매칭용 구성이다. 즉, 매칭부(40)는 벌크 탄성파 필터 칩(10) 및 표면 탄성파 필터 칩(20)를 통과하는 신호가 왜곡 등이 되지 않도록 벌크 탄성파 필터 칩(10)과 표면 탄성파 필터 칩(20)의 임피던스를 매칭시킨다.The matching

한편, 벌크 탄성파 필터(BAW Filter)(10), 표면 탄성파 필터(SAW Filter)(20), 베이스(30) 및 매칭부(40) 간의 연결은 다음과 같다. 즉, 입력 신호가 인가되는 베이스(30)의 제1 베이스 전극(31)은 벌크 탄성파 필터 칩(10)의 입력 전극인 제1 벌크용 전극(11)과 연결되며, 벌크 탄성파 필터 칩(10)의 출력 전극인 제2 벌크용 전극(12)은 매칭부(40)의 일단과 연결된다. 또한, 매칭부(40)의 타단은 표면 탄성파 필터 칩(20)의 입력 전극인 제1 표면용 전극(21)과 연결되며, 표면 탄성파 필터 칩(20)의 출력 전극인 제2 표면용 전극(22)은 베이스(30)의 출력 전극인 제2 베이스 전극(32)과 연결된다.On the other hand, the connection between the bulk acoustic wave filter (BAW Filter) 10, the surface acoustic wave filter (SAW Filter) 20, the

도 14는 본 발명의 일 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지에서 벌크 탄성파 필터 칩(10)과 표면 탄성파 필터 칩(20)의 필터링 특성을 나타낸다.FIG. 14 illustrates filtering characteristics of the bulk acoustic

도 14를 참조하면, 벌크 탄성파 필터 칩(10)은 FCB1과 고역 차단 주파수 FCB2의 사이를 통과(굵은 실선으로 표시)시키는 대역 통과 필터이다. 또한, 표면 탄성파 필터 칩(20)은 제1 저역 차단 주파수 FCS1과 제1 고역 차단 주파수 FCS2의 사이를 차단하고 제2 저역 차단 주파수 FCS3과 제2 고역 차단 주파수 FCS4의 사이를 차단(얇은 실선으로 표시)하는 대역 제거 필터이다. 이때, 표면 탄성파 필터 칩(20)이 갖는 대역 제거의 차단 기울기(즉, FCS1, FCS2, FCS3 및 FCS4의 주변에서 나타나는 감쇠 정도)는 벌크 탄성파 필터 칩(10)이 갖는 대역 통과의 차단 기울기(즉, FCB1 및 FCB2 주변에서 나타나는 감쇠 정도) 보다 크다. Referring to FIG. 14, the bulk acoustic

특히, 도 14에 도시된 바와 같이, FCB1이 FCS2 보다 작고 FCB2이 FCS3 보다 크도록 구현할 수 있다. 이 경우, 발명의 일 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지는 고역 차단 주파수에 대해 벌크 탄성파 필터 칩(10) 단독으로 구현할 수 없는 날카로운 차단 기울기의 스커트 특성을 구현할 수 있다. 즉, FCS1과 FCS2의 사이에 FCB1이 위치하도록 구현하고 FCS3과 FCS4의 사이에 FCB2가 위치하도록 구현함으로써, 이러한 날카로운 스커트 특성을 보장할 수 있다.In particular, as shown in FIG. 14, F CB1 may be smaller than F CS2 and F CB2 may be larger than F CS3 . In this case, the filter chip package having improved skirt characteristics according to an embodiment of the present invention may implement a skirt characteristic of a sharp cutoff slope that cannot be implemented by the bulk acoustic

이하, 수평형으로 구현된 본 발명의 제1 실시예 내지 제4 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지의 구조에 대해 보다 상세하게 설명하도록 한다. 다만, 설명의 편의를 위해, 각 실시예에 대하여 “수평형 제1 실시예”, “수평형 제2 실시예”, “수평형 제3 실시예” 및 “수평형 제4 실시예”라고 지칭하며, 세부적으로 달라지는 내용에 대해서만 설명하도록 한다.Hereinafter, the structure of the filter chip package having improved skirt characteristics according to the first to fourth embodiments of the present invention implemented in a horizontal type will be described in more detail. However, for convenience of description, each embodiment is referred to as "horizontal first embodiment", "horizontal second embodiment", "horizontal third embodiment", and "horizontal fourth embodiment". Only the details that vary will be explained.

도 3 내지 도 6은 각각 수평형으로 구현된 본 발명의 제1 실시예 내지 제4 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지의 보다 상세한 측면 구조를 나타낸다.3 to 6 show a more detailed side structure of the filter chip package with improved skirt characteristics according to the first to fourth embodiments of the present invention implemented in a horizontal type, respectively.

도 3 내지 도 6을 참조하면, 수평형 제1 실시예 내지 제4 실시예는 벌크 탄성파 필터 칩(10) 및 표면 탄성파 필터 칩(20)의 구조가 다르다. 3 to 6, the horizontal first and fourth embodiments have different structures of the bulk acoustic

먼저, 도 3을 참조하여, 수평형 제1 실시예에 대하여 설명하도록 한다. First, with reference to FIG. 3, the first embodiment will be described.

수평형 제1 실시예에서, 벌크 탄성파 필터 칩(10)은 벌크용 연결층(14) 및 제3 벌크용 전극(15)을 더 포함한다. 이때, 제3 벌크용 전극(15)은 벌크용 압전층(13)의 하부에 제1 벌크용 전극(11)과 이격되게 마련된다. 또한, 벌크용 연결층(14)은 벌크용 압전층(13)을 관통하여 제2 벌크용 전극(12)과 제3 벌크용 전극(15)을 전기적으로 연결한다.In the first horizontal embodiment, the bulk acoustic

한편, 표면 탄성파 필터 칩(20)은 제1 표면용 전극(21)과 제2 표면용 전극(22)이 각각 표면용 압전층(23)의 하부에 마련된다. 이때, 벌크 탄성파 필터 칩(10)의 제3 벌크용 전극(15)은 제1 표면용 전극(21)과 연결된다. 이에 따라, 벌크 탄성파 필터 칩(10)의 출력 전극인 제2 벌크용 전극(12)은 제3 벌크용 전극(15)을 통해 표면 탄성파 필터 칩(20)의 입력 전극인 제1 표면용 전극(21)과 연결된다.In the surface acoustic

즉, 제1 베이스 전극(31)은 제1 베이스 연결층(33)을 통해 제1 벌크용 전극(11)과 연결되며, 제2 벌크용 전극(12)은 벌크용 연결층(14) 및 제3 벌크용 전극(15)을 통해 매칭부(40)의 일단과 연결된다. 또한, 매칭부(40)의 타단은 제1 표면용 전극(21)과 연결되며, 제2 표면용 전극(22)은 제2 베이스 연결층(34)을 통해 제2 베이스 전극(32)과 연결된다. 이때, 제1 베이스 연결층(33) 및 제2 베이스 연결층(34)은 각각 제1 베이스 전극(31) 및 제2 베이스 전극(32)과 다른 전극을 전기적으로 연결하는 것으로서, 베이스(30) 상에 마련될 수 있다.That is, the

다음으로, 도 4를 참조하여, 수평형 제2 실시예에 대하여 설명하도록 한다. Next, with reference to FIG. 4, the second embodiment will be described.

수평형 제2 실시예는 수평형 제1 실시예에서 추가 구성을 더 포함한다. 즉, 벌크 탄성파 필터 칩(10)은 벌크용 기판(16), 제1 벌크용 외부 접속 단자(17) 및 제2 벌크용 외부 접속 단자(18)를 더 포함한다. The horizontal second embodiment further includes an additional configuration in the horizontal first embodiment. That is, the bulk acoustic

벌크용 기판(16)은 제1 벌크용 전극(11) 및 제3 벌크용 전극(15)의 하부에 마련되는 기판이다. 이때, 벌크용 기판(16)의 하부에는 절연 재료로 이루어진 벌크용 쿠션층을 더 포함할 수 있다. 즉, 벌크용 쿠션층은 벌크용 기판(16)의 하부에 다양한 패턴으로 형성된 벌크용 재배치층(RDL)을 덮어 보호한다. 이때, 벌크용 재배치층은 제1 벌크용 외부 접속 단자(17)와 제1 벌크용 전극(11)을 전기적으로 연결하는 층과, 제2 벌크용 외부 접속 단자(18)와 제3 벌크용 전극(15)을 전기적으로 연결하는 층을 각각 포함한다.The

제1 및 제2 벌크용 외부 접속 단자(17, 18)는 벌크용 쿠션층의 하부에 마련되어 벌크용 재배치층과 전기적으로 연결되는 단자이다. 예를 들어, 제1 및 제2 벌크용 외부 접속 단자(17, 18)는 솔더볼(Solder Ball)일 수 있다.The first and second bulk

한편, 표면 탄성파 필터 칩(20)은 표면용 기판(24), 제1 표면용 외부 접속 단자(25) 및 제2 표면용 외부 접속 단자(26)를 더 포함한다. Meanwhile, the surface acoustic

표면용 기판(24)은 제1 표면용 전극(21) 및 제2 표면용 전극(22)의 하부에 마련되는 기판이다. 이때, 표면용 기판(24)의 하부에는 절연 재료로 이루어진 표면용 쿠션층을 더 포함할 수 있다. 즉, 표면용 쿠션층은 표면용 기판(24)의 하부에 다양한 패턴으로 형성된 표면용 재배치층(RDL)을 덮어 보호한다. 이때, 표면용 재배치층은 제1 표면용 외부 접속 단자(25)와 제1 표면용 전극(21)을 전기적으로 연결하는 층과, 제2 표면용 외부 접속 단자(26)와 제2 표면용 전극(22)을 전기적으로 연결하는 층을 각각 포함한다. The

제1 및 제2 표면용 외부 접속 단자(25, 26)는 표면용 쿠션층의 하부에 마련되어 표면용 재배치층과 전기적으로 연결되는 단자이다. 예를 들어, 제1 및 제2 표면용 외부 접속 단자(25, 26)는 솔더볼(Solder Ball)일 수 있다.The first and second surface

이에 따라, 벌크 탄성파 필터 칩(10)의 입력 전극인 제1 벌크용 전극(11)은 제1 벌크용 외부 접속 단자(17)를 통해 베이스(30)의 입력 단자인 제1 베이스 전극(31)과 연결되고, 벌크 탄성파 필터 칩(10)의 출력 전극인 제2 벌크용 전극(12)은 제2 벌크용 외부 접속 단자(18)를 매칭부(40)의 일단과 연결된다. 또한, 표면 탄성파 필터 칩(20)의 입력 전극인 제1 표면용 전극(21)은 제1 표면용 외부 접속 단자(25)를 통해 매칭부(40)의 타단과 연결되고, 표면 탄성파 필터 칩(20)의 출력 전극인 제2 표면용 전극(22)은 제2 표면용 외부 접속 단자(26)를 통해 베이스(30)의 출력 전극인 제2 베이스 전극(32)과 연결된다.Accordingly, the

즉, 제1 베이스 전극(31)은 제1 베이스 연결층(33)과 제1 벌크용 외부 접속 단자(17)를 통해 제1 벌크용 전극(11)과 연결되고, 제2 벌크용 전극(12)은 벌크용 연결층(14), 제3 벌크용 전극(15) 및 제2 벌크용 외부 접속 단자(18)를 통해 매칭부(40)의 일단과 연결된다. 또한, 매칭부(40)의 타단은 제1 표면용 외부 접속 단자(25)를 통해 제1 표면용 전극(21)과 연결되며, 제2 표면용 전극(22)은 제2 표면용 외부 접속 단자(26) 및 제2 베이스 연결층(34)을 통해 제2 베이스 전극(32)과 연결된다.That is, the

다음으로, 도 5를 참조하여, 수평형 제3 실시예에 대하여 설명하도록 한다. Next, referring to FIG. 5, a third embodiment will be described.

수평형 제3 실시예는 수평형 제1 실시예에서 표면 탄성파 필터 칩(20)의 구성 위치가 바뀌고 표면 탄성파 필터 칩(20)에 추가 구성이 더 포함된다. 즉, 표면 탄성파 필터 칩(20)은 제1 표면용 전극(21)과 제2 표면용 전극(22)이 각각 표면용 압전층(23)의 상부에 구비하며, 제1 표면용 연결층(27) 및 제2 표면용 연결층(28)을 더 포함한다. 제1 표면용 연결층(27)은 표면용 압전층(23)을 관통하여 제1 표면용 전극(21)과 전기적으로 연결한다. 또한, 제2 표면용 연결층(28)은 표면용 압전층(23)을 관통하여 제2 표면용 전극(22)과 전기적으로 연결한다.In the third embodiment of the horizontal type, the configuration position of the surface acoustic

이에 따라, 매칭부(40)의 타단은 제1 표면용 연결층(27)을 통해 표면 탄성파 필터 칩(20)의 입력 전극인 제1 표면용 전극(21)과 연결된다. 또한, 표면 탄성파 필터 칩(20)의 출력 전극인 제2 표면용 전극(21)은 제2 표면용 연결층(28)을 통해 베이스(30)의 출력 전극인 제2 베이스 전극(32)과 연결된다.Accordingly, the other end of the matching

즉, 제1 베이스 전극(31)은 제1 베이스 연결층(33)을 통해 제1 벌크용 전극(11)과 연결되며, 제2 벌크용 전극(12)은 벌크용 연결층(14) 및 제3 벌크용 전극(15)을 통해 매칭부(40)의 일단과 연결된다. 또한, 매칭부(40)의 타단은 제1 표면용 연결층(27)을 통해 제1 표면용 전극(21)과 연결되며, 제2 표면용 전극(22)은 제2 표면용 연결층(28) 및 제2 베이스 연결층(34)을 통해 제2 베이스 전극(32)과 연결된다.That is, the

다음으로, 도 6을 참조하여, 수평형 제4 실시예에 대하여 설명하도록 한다. Next, referring to FIG. 6, a fourth embodiment will be described.

수평형 제4 실시예는 수평형 제3 실시예에서 추가 구성을 더 포함한다. 즉, 벌크 탄성파 필터 칩(10)은 벌크용 기판(16), 제1 벌크용 외부 접속 단자(17) 및 제2 벌크용 외부 접속 단자(18)를 더 포함한다. 이들 추가 구성은 수평형 제2 실시예에서 설명한 바와 동일하다.The horizontal fourth embodiment further includes an additional configuration in the horizontal third embodiment. That is, the bulk acoustic

한편, 표면 탄성파 필터 칩(20)은 표면용 기판(24), 제1 표면용 외부 접속 단자(25) 및 제2 표면용 외부 접속 단자(26)를 더 포함한다. 이들 추가 구성은 수평형 제2 실시예에서 설명한 바와 동일하다. 다만, 표면용 기판(24)은 표면용 압전층(24)의 하부에 마련된다. 또한, 표면용 재배치층은 제1 표면용 외부 접속 단자(25)와 제1 표면용 연결층(27)을 전기적으로 연결하는 층과, 제2 표면용 외부 접속 단자(26)와 제2 표면용 연결층(28)을 전기적으로 연결하는 층을 각각 포함한다.Meanwhile, the surface acoustic

즉, 제1 베이스 전극(31)은 제1 베이스 연결층(33)과 제1 벌크용 외부 접속 단자(17)를 통해 제1 벌크용 전극(11)과 연결되고, 제2 벌크용 전극(12)은 벌크용 연결층(14), 제3 벌크용 전극(15) 및 제2 벌크용 외부 접속 단자(18)를 통해 매칭부(40)의 일단과 연결된다. 또한, 매칭부(40)의 타단은 제1 표면용 외부 접속 단자(25) 및 제1 표면용 연결층(27)을 통해 제1 표면용 전극(21)과 연결되며, 제2 표면용 전극(22)은 제2 표면용 연결층(28), 제2 표면용 외부 접속 단자(26) 및 제2 베이스 연결층(34)을 통해 제2 베이스 전극(32)과 연결된다.That is, the

이하, 수직형으로 구현된 본 발명의 제1 실시예 및 제2 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지의 구조에 대해 보다 상세하게 설명하도록 한다. 다만, 설명의 편의를 위해, 각 실시예에 대하여 “수직형 제1 실시예” 및 “수직형 제2 실시예”라고 지칭하며, 세부적으로 달라지는 내용에 대해서만 설명하도록 한다.Hereinafter, the structure of the filter chip package having improved skirt characteristics according to the first and second embodiments of the present invention, which are implemented in a vertical type, will be described in more detail. However, for convenience of description, each of the embodiments will be referred to as the "vertical first embodiment" and the "vertical second embodiment", and only the details changed in detail will be described.

도 10 및 도 11은 각각 수직형으로 구현된 본 발명의 제1 실시예 및 제2 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지의 보다 상세한 측면 구조를 나타낸다.10 and 11 illustrate a more detailed side structure of a filter chip package having improved skirt characteristics according to the first and second embodiments of the present invention, which are implemented in a vertical manner, respectively.

도 10 내지 도 11을 참조하면, 수직형 제1 실시예 및 제2 실시예는 벌크 탄성파 필터 칩(10) 및 표면 탄성파 필터 칩(20)의 구조가 다르다. 10 to 11, the vertical first and second embodiments have different structures of the bulk acoustic

먼저, 도 10을 참조하며, 수직형 제1 실시예에 대하여 설명하도록 한다. First, referring to FIG. 10, the vertical first embodiment will be described.

수직형 제1 실시예에서, 벌크 탄성파 필터 칩(10)은 벌크용 연결층(14) 및 제3 벌크용 전극(15)을 더 포함한다. 이들 추가 구성은 수평형 제1 실시예에서 설명한 바와 동일하다.In the first vertical embodiment, the bulk acoustic

표면 탄성파 필터 칩(20)은 제1 표면용 전극(21)과 제2 표면용 전극(22)을 각각 표면용 압전층(23)의 상부에 구비하며, 제2 벌크용 전극(12) 상에 마련된다. 이때, 표면용 압전층(23)과 제2 벌크용 전극(12) 사이에는 별도의 절연층(I)이 마련될 수 있다.The surface acoustic

한편, 수직형 제1 실시예는 제1 도전 와이어(35) 및 제2 도전 와이어(36)를 더 포함한다. 이때, 제1 도전 와이어(35)는 제1 표면용 전극(21)과 매칭부(40)의 타단을 전기적으로 연결하며, 제2 도전 와이어(36)는 제2 표면용 전극(22)과 베이스(30)의 출력 단자인 제2 베이스 전극(32)의 전기적으로 연결한다.Meanwhile, the vertical first embodiment further includes a first

즉, 제1 베이스 전극(31)은 제1 베이스 연결층(33)을 통해 제1 벌크용 전극(11)과 연결되며, 제2 벌크용 전극(12)은 벌크용 연결층(14) 및 제3 벌크용 전극(15)을 통해 매칭부(40)의 일단과 연결된다. 또한, 매칭부(40)의 타단은 제1 도전 와이어(35)를 통해 제1 표면용 전극(21)과 연결되며, 제2 표면용 전극(22)은 제2 도전 와이어(36)를 통해 제2 베이스 전극(32)과 연결된다.That is, the

다음으로, 도 11을 참조하여, 수직형 제2 실시예에 대하여 설명하도록 한다. Next, referring to FIG. 11, a second embodiment will be described.

수직형 제2 실시예는 수직형 제1 실시예에서 추가 구성을 더 포함한다. 즉, 벌크 탄성파 필터 칩(10)은 벌크용 기판(16), 제1 벌크용 외부 접속 단자(17) 및 제2 벌크용 외부 접속 단자(18)를 더 포함한다. 이들 추가 구성은 수평형 제2 실시예에서 설명한 바와 동일하다.The vertical second embodiment further includes an additional configuration in the vertical first embodiment. That is, the bulk acoustic

표면 탄성파 필터 칩(20)은 제1 표면용 전극(21)과 제2 표면용 전극(22)을 각각 표면용 압전층(23)의 하부에 구비하며, 제2 벌크용 전극(12) 상에 마련된다. 이때, 표면용 제1 전극(21) 및 표면용 제2 전극(22)과, 제2 벌크용 전극(12) 사이에는 별도의 절연층(I)이 마련될 수 있다.The surface acoustic

또한, 표면 탄성파 필터 칩(20)은 표면용 기판(24), 제1 표면용 외부 접속 단자(25), 제2 표면용 외부 접속 단자(26), 제1 표면용 연결층(27) 및 제2 표면용 연결층(28)를 더 포함한다. 이들 추가 구성은 수평형 제2 실시예에서 설명한 바와 동일하다. 다만, 표면용 기판(24)은 표면용 압전층(23) 상에 마련된다. 이에 따라, 표면용 재배치층, 표면용 쿠션층, 제1 표면용 외부 접속 단자(25) 및 제2 표면용 외부 접속 단자(26)도 표면용 기판(24) 상에 마련된다.In addition, the surface acoustic

한편, 수직형 제2 실시예는 제1 도전 와이어(35) 및 제2 도전 와이어(36)를 더 포함한다. 이때, 제1 도전 와이어(35)는 제1 표면용 외부 접속 단자(25)와 매칭부(40)의 타단을 전기적으로 연결하며, 제2 도전 와이어(36)는 제2 표면용 외부 접속 단자(26)와 베이스(30)의 출력 단자인 제2 베이스 전극(32)의 전기적으로 연결한다.On the other hand, the vertical second embodiment further includes a first

즉, 제1 베이스 전극(31)은 제1 베이스 연결층(33) 및 제1 벌크용 외부 접속 단자(17)를 통해 제1 벌크용 전극(11)과 연결되며, 제2 벌크용 전극(12)은 벌크용 연결층(14), 제3 벌크용 전극(13) 및 제2 벌크용 외부 접속 단자(18)를 통해 매칭부(40)의 일단과 연결된다. 또한, 매칭부(40)의 타단은 제1 도전 와이어(35), 제1 표면용 외부 접속 단자(25) 및 제1 표면용 연결층(27)을 통해 제1 표면용 전극(21)과 연결되며, 제2 표면용 전극(22)은 제2 표면용 연결층(28), 제2 표면용 외부 접속 단자(26) 및 제2 도전 와이어(36)를 통해 제2 베이스 전극(32)과 연결된다.That is, the

이하, 본 발명의 일 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지를 패키징(packaging)하는데 추가될 수 있는 구성에 대하여 설명하도록 한다.Hereinafter, a configuration that may be added to packaging a filter chip package having improved skirt characteristics according to an embodiment of the present invention will be described.

도 7 및 도 12는 각각 수평형 및 수직형으로 구현된 본 발명의 일 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지가 몰딩층(50)을 더 포함하는 경우의 전체적인 측면 구조를 나타낸다.7 and 12 show the overall side structure when the filter chip package with improved skirt characteristics according to an embodiment of the present invention implemented in a horizontal type and a vertical type further includes a

한편, 도 7 및 도 12에 도시된 바와 같이, 본 발명의 일 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지는 몰딩부(50)를 더 포함할 수 있다. 몰딩부(50)는 몰드 공정을 통해 형성되어, 벌크 탄성파 필터 칩(10), 표면 탄성파 필터 칩(20), 베이스(30) 및 매칭부(40)를 덮어 보호하는 층으로서, 다양한 몰딩 재료로 이루어질 수 있다. 예를 들어, 몰딩부(50)는 에폭시 몰딩 컴파운드(EMC: Epoxy Molding Compound)로 이루어질 수 있다.Meanwhile, as illustrated in FIGS. 7 and 12, the filter chip package having improved skirt characteristics according to an embodiment of the present invention may further include a

도 8 및 도 13은 각각 수평형 및 수직형으로 구현된 본 발명의 일 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지가 캡(60)을 더 포함하는 경우의 전체적인 측면 구조를 나타낸다. 8 and 13 illustrate the overall side structure of the case where the filter chip package having improved skirt characteristics according to the embodiment of the present invention, which is implemented in a horizontal type and a vertical type, further includes a

또한, 도 8 및 도 13에 도시된 바와 같이, 본 발명의 일 실시예에 따른 스커트 특성이 향상된 필터 칩 패키지는 캡(60) 및 스페이서(70)를 더 포함할 수 있다. In addition, as shown in FIGS. 8 and 13, the filter chip package having improved skirt characteristics according to an embodiment of the present invention may further include a

캡(60)은 베이스(30)의 상부에 마련되는 기판으로서, 캡 웨이퍼로부터 절단된 구성일 수 있다. 이때, 베이스(30)와 캡(60) 사이에는 내부 공간(S)이 마련된다. 이때, 내부 공간(S)은 밀봉된 공간으로서, 필터 칩(10)이 위치한다.The

스페이서(70)는 베이스(30)의 상부 및 캡(60)의 하부 사이에 마련되는 소정 높이의 벽으로서, 내부 공간(S)을 형성한다. 즉, 스페이서(70)는 필터 칩(10, 20)의 주변을 폐곡선 형태로 둘러쌈으로써 밀봉된 내부 공간(S)이 형성되는 가스켓(gasket) 구조를 형성한다. 스페이서(70)는 베이스(30) 또는 캡(60)으로부터 돌출된 베이스(30) 또는 캡(60)의 연장부일 수 있으며, 소정 높이를 갖는 별도 구성인 기둥부일 수 있다. 이때, 스페이서(60)는 접합층을 통해 베이스(30) 및 캡(60)과 접합된다. 이때, 접합층은 다양한 접합 재료로 이루어질 수 있으며, 예를 들어, 접합 재료로는 유테틱 접합(EutecticBonding) 재료일 수 있다.The

이하, 본 발명의 일 실시예에 따른 고주파 프론트 엔드 모듈에 대하여 설명하도록 한다.Hereinafter, a high frequency front end module according to an embodiment of the present invention will be described.

도 15는 본 발명의 일 실시예에 따른 고주파 프론트 엔드 모듈(RF front-end module)의 전체적인 구성을 나타낸다.FIG. 15 shows the overall configuration of an RF front-end module according to an embodiment of the present invention.

본 발명의 일 실시예에 따른 고주파 프론트 엔드 모듈은 이동통신 단말기에 필수적으로 포함되는 구성으로서, 고주파 신호처리 칩(RFIC)과 안테나(ANT) 사이에 구비되어 송신 신호와 수신 신호와 분리하는 역할을 한다. 즉, 본 발명의 일 실시예에 따른 고주파 프론트 엔드 모듈은, 도 15에 도시된 바와 같이, 송신 필터부(110), 수신 필터부(120), RF 스위치(130) 및 전력 증폭기(140)를 포함한다.The high frequency front end module according to an embodiment of the present invention is an element included in a mobile communication terminal, and is provided between a high frequency signal processing chip (RFIC) and an antenna (ANT) to separate a transmission signal from a reception signal. do. That is, the high frequency front end module according to an embodiment of the present invention, as shown in Figure 15, the

송신 필터부(110) 및 수신 필터부(120)는 각각 송신용 고주파 신호 대역과 수신용 고주파 신호 대역을 필터링하는 구성이다. 즉, 송신 필터부(110)는 고주파 신호처리 칩(RFIC)로부터 전달된 각 채널 신호를 필터링하여 전력 증폭기(140)를 거쳐 RF 스위치(130)로 전달한다. 또한, 수신 필터부(110)는 안테나(ANT)를 통해 수신되어 RF 스위치(130)를 거친 수신 신호를 필터링하여 고주파 신호처리 칩(RFIC)으로 전달한다. 다만, 송신 필터부(110)와 수신 필터부(120)는 하나의 구성으로 구현될 수 있다. The

특히, 각 필터부(110, 120)는 하나 이상의 채널 필터부(111, 121)를 포함한다. 이때, 각 채널 필터부(111, 121)는 이동 통신 표준에 따라 서로 다른 주파수 대역을 통과시킨다. 즉, 각 송신 채널 필터부(111a, 111b, …)는 서로 다른 주파수 대역을 통과시키며, 각 수신 채널 필터부(121a, 121b, …)는 서로 다른 주파수 대역을 통과시킨다. 이에 따라, 각 채널은 서로 다른 이동 통신 표준에 따른 신호가 전달될 수 있다.In particular, each

RF 스위치(130)는 다양한 이동 통신 표준에 맞는 신호를 선택하는 기능을 수행하며, 전력 증폭기(140)는 송신 필터부(110)의 출력에 연결되어 신호를 증폭하는 기능을 수행한다. 각 채널 마다 서로 다른 전력 증폭기(140)가 연결될 수 있으며, 이에 따라, 각 채널의 이동 통신 표준에 맞는 신호를 생성할 수 있다.The

특히, 본 발명의 일 실시예에 따른 고주파 프론트 엔드 모듈은 인쇄회로기판(PCB)(미도시)을 포함할 수 있다. 이에 따라, 각각이 모듈화된 송신 필터부(110), 수신 필터부(120), RF 스위치(130) 및 전력 증폭기(140)가 인쇄회로기판에 실장될 수 있다. In particular, the high frequency front end module according to the embodiment of the present invention may include a printed circuit board (PCB) (not shown). Accordingly, the

이 경우, 송신 필터부(110) 또는 수신 필터부(120)의 어느 한 채널 필터부(111, 121)는 도 1 내지 도 13에 따라 상술한 벌크 탄성파 필터 칩(10) 및 표면 탄성파 필터 칩(20)로 이루어진 구조체에 해당할 수 있다. 또한, 인쇄회로기판은 도 1 내지 도 13에 따라 상술한 베이스(30)에 해당할 수 있다. 이에 따라, 인쇄회로기판은 제1 베이스 전극(31), 제2 베이스 전극(32), 제1 베이스 연결층(33), 제2 베이스 연결층(34), 제1 도전 와이어(35), 제2 도전 와이어(36) 등을 구비할 수 있으며, 인쇄회로기판에는 도 1 내지 도 13에 따라 상술한 매칭부(40)가 구비될 수 있다.In this case, any of the channel filter units 111 and 121 of the

본 발명의 상세한 설명에서는 구체적인 실시 예에 관하여 설명하였으나 본 발명의 범위에서 벗어나지 않는 한도 내에서 여러 가지 변형이 가능함은 물론이다. 그러므로 본 발명의 범위는 설명된 실시 예에 국한되지 않으며, 후술되는 특허청구의 범위 및 이 특허청구의 범위와 균등한 것들에 의해 정해져야 한다.In the detailed description of the present invention, specific embodiments have been described, but various modifications may be made without departing from the scope of the present invention. Therefore, the scope of the present invention should not be limited to the described embodiments, but should be defined by the following claims and their equivalents.

10: 벌크 탄성파 필터 칩 11: 제1 벌크용 전극

12: 제2 벌크용 전극 13: 벌크용 압전층

14: 벌크용 연결층 15: 제3 벌크용 전극

16: 벌크용 기판 17: 제1 벌크용 외부 접속 단자

18: 제2 벌크용 외부 접속 단자 20: 표면 탄성파 필터 칩

21: 제1 표면용 전극 22: 제2 표면용 전극

23: 표면용 압전층 24: 표면용 기판

25: 제1 표면용 외부 접속 단자 26: 제2 표면용 외부 접속 단자

27: 제1 표면용 연결층 28: 제2 표면용 연결층

30: 베이스 31: 제1 베이스 전극

32: 제2 베이스 전극 33: 제1 베이스 연결층

34: 제2 베이스 연결층 35: 제1 도전 와이어

36: 제2 도전 와이어 40: 매칭부

50: 몰딩층 60: 캡

70: 스페이서 S: 내부 공간10: bulk acoustic wave filter chip 11: first bulk electrode

12: second bulk electrode 13: bulk piezoelectric layer

14: connecting layer for bulk 15: third electrode for bulk

16: bulk substrate 17: first external connection terminal for bulk

18: second external connection terminal for bulk 20: surface acoustic wave filter chip

21: electrode for first surface 22: electrode for second surface

23: piezoelectric layer for surface 24: substrate for surface

25: external connection terminal for first surface 26: external connection terminal for second surface

27: connection layer for first surfaces 28: connection layer for second surfaces

30: base 31: first base electrode

32: second base electrode 33: first base connection layer

34: second base connection layer 35: first conductive wire

36: second conductive wire 40: matching portion

50: molding layer 60: cap

70: spacer S: internal space

Claims (8)

제1 벌크용 전극 및 제2 벌크용 전극과, 제1 벌크용 전극 및 제2 벌크용 전극 사이의 벌크용 압전층을 각각 구비하고, 제1 벌크용 전극이 제1 베이스 전극과 연결되며, 베이스의 상부에 마련되고, 저역 차단 주파수(FCB1)와 고역 차단 주파수(FCB2)의 사이를 통과시키는 대역 통과 필터인 벌크 탄성파 필터 칩; 및

표면용 압전층과, 표면용 압전층의 상부에 서로 이격되게 구비된 제1 표면용 전극 및 제2 표면용 전극을 각각 구비하고, 제1 표면용 전극이 제2 벌크용 전극과 연결되며, 제2 표면용 전극이 제2 베이스 전극과 연결되고, 베이스의 상부에 마련되며, 제1 저역 차단 주파수(FCS1)와 제1 고역 차단 주파수(FCS2)의 사이를 차단하고 제2 저역 차단 주파수(FCS3)와 제2 고역 차단 주파수(FCS4)의 사이를 차단하는 대역 제거 필터인 표면 탄성파 필터 칩;을 포함하며,

상기 표면 탄성파 필터 칩의 차단 주파수에서 나타나는 신호 감쇠 정도는 상기 벌크 탄성파 필터 칩의 차단 주파수에서 나타나는 신호 감쇠 정도 보다 크고,

상기 FCB1은 상기 FCS2 보다 작으며, 상기 FCB2는 상기 FCS3 보다 큰 것을 특징으로 하는 스커트 특성이 향상된 필터 칩 패키지.A base having a first base electrode and a second base electrode to which an input / output signal is applied;

A bulk piezoelectric layer between the first bulk electrode and the second bulk electrode, and the first bulk electrode and the second bulk electrode, wherein the first bulk electrode is connected to the first base electrode, A bulk acoustic wave filter chip provided on an upper portion of the bulk acoustic wave filter chip which is a band pass filter passing between the low pass cutoff frequency FCB1 and the high pass cutoff frequency FCB2; And

A surface piezoelectric layer and a first surface electrode and a second surface electrode provided on the surface of the piezoelectric layer and spaced apart from each other, respectively, wherein the first surface electrode is connected to the second bulk electrode; The second surface electrode is connected to the second base electrode and is provided on the base, and cuts off between the first low pass cutoff frequency FCS1 and the first high pass cutoff frequency FCS2 and the second low pass cutoff frequency FCS3. And a surface acoustic wave filter chip, which is a band cancellation filter for blocking between the second high pass cutoff frequency FCS4.

The degree of signal attenuation at the cutoff frequency of the surface acoustic wave filter chip is greater than the amount of signal attenuation at the cutoff frequency of the bulk acoustic wave filter chip,

The FCB1 is smaller than the FCS2, and the FCB2 is larger than the FCS3.

필터 칩이 포함되는 내부 공간을 베이스와의 사이에 구비하도록 베이스 상에 마련된 캡; 및

필터 칩 주변을 폐곡선 형태로 둘러쌈으로써 밀봉된 상기 내부 공간을 형성하는 스페이서;를 더 포함하는 것을 특징으로 하는 스커트 특성이 향상된 필터 칩 패키지.The method of claim 1,

A cap provided on the base to have an inner space including the filter chip therebetween; And

The filter chip package of claim 1, further comprising a spacer forming the sealed inner space by surrounding the filter chip in a closed curve shape.

상기 FCS1과 상기 FCS2의 사이에 FCB1이 위치하며, 상기 FCS3과 상기 FCS4의 사이에 FCB2가 위치하는 것을 특징으로 하는 스커트 특성이 향상된 필터 칩 패키지.The method of claim 1,

F CB1 is positioned between the F CS1 and the F CS2 , F CB2 is positioned between the F CS3 and the F CS4 filter chip package with improved skirt characteristics, characterized in that.

상기 제2 벌크용 전극과 상기 제1 표면용 전극 사이에 연결되며, 상기 벌크 탄성파 필터 칩과 상기 표면 탄성파 필터 칩을 매칭시키는 매칭부를 더 포함하는 것을 특징으로 하는 스커트 특성이 향상된 필터 칩 패키지.The method of claim 1,

And a matching unit connected between the second bulk electrode and the first surface electrode, the matching unit matching the bulk acoustic wave filter chip and the surface acoustic wave filter chip.

상기 벌크 탄성파 필터 칩과 상기 표면 탄성파 필터 칩은 베이스 상에 나란하게 배치되는 것을 특징으로 하는 스커트 특성이 향상된 필터 칩 패키지.The method of claim 1,

And the bulk acoustic wave filter chip and the surface acoustic wave filter chip are disposed side by side on a base.

제1 벌크용 전극 및 제2 벌크용 전극과, 제1 벌크용 전극 및 제2 벌크용 전극 사이의 벌크용 압전층을 각각 구비하고, 제1 벌크용 전극이 제1 베이스 전극과 연결되며, 베이스의 상부에 마련되는 벌크 탄성파 필터 칩; 및

표면용 압전층과, 표면용 압전층의 상부에 서로 이격되게 구비된 제1 표면용 전극 및 제2 표면용 전극을 각각 구비하고, 제1 표면용 전극이 제2 벌크용 전극과 연결되며, 제2 표면용 전극이 제2 베이스 전극과 연결되고, 베이스의 상부에 마련되는 표면 탄성파 필터 칩;을 포함하며,

상기 표면 탄성파 필터 칩의 차단 주파수에서 나타나는 신호 감쇠 정도는 상기 벌크 탄성파 필터 칩의 차단 주파수에서 나타나는 신호 감쇠 정도 보다 크고,

상기 베이스 상에 벌크 탄성파 필터 칩이 배치되며, 상기 벌크 탄성파 필터 칩 상에 상기 표면 탄성파 필터 칩이 배치되는 것을 특징으로 하는 스커트 특성이 향상된 필터 칩 패키지.A base having a first base electrode and a second base electrode to which an input / output signal is applied;

A bulk piezoelectric layer between the first bulk electrode and the second bulk electrode, and the first bulk electrode and the second bulk electrode, wherein the first bulk electrode is connected to the first base electrode, A bulk acoustic wave filter chip provided at an upper portion of the bulk acoustic wave filter chip; And

A surface piezoelectric layer and a first surface electrode and a second surface electrode provided on the surface of the piezoelectric layer and spaced apart from each other, respectively, wherein the first surface electrode is connected to the second bulk electrode; A surface acoustic wave filter chip connected to the second surface electrode and connected to the second base electrode and provided on an upper portion of the base;

The degree of signal attenuation at the cutoff frequency of the surface acoustic wave filter chip is greater than the amount of signal attenuation at the cutoff frequency of the bulk acoustic wave filter chip,

The bulk acoustic wave filter chip is disposed on the base, and the surface acoustic wave filter chip is disposed on the bulk acoustic wave filter chip.

입출력 신호가 인가되는 제1 베이스 전극 및 제2 베이스 전극을 구비하는 인쇄회로기판; 및

인쇄회로기판 상에 구비되고, 각각이 서로 다른 주파수 대역을 통과시키는 하나 이상의 채널 필터부;를 포함하며,

어느 한 채널 필터부는,

제1 벌크용 전극 및 제2 벌크용 전극과, 제1 벌크용 전극 및 제2 벌크용 전극 사이의 벌크용 압전층을 각각 구비하고, 제1 벌크용 전극이 제1 베이스 전극과 연결되며, 인쇄회로기판의 상부에 마련되고, 저역 차단 주파수(FCB1)와 고역 차단 주파수(FCB2)의 사이를 통과시키는 대역 통과 필터인 벌크 탄성파 필터 칩; 및

표면용 압전층과, 표면용 압전층의 상부에 서로 이격되게 구비된 제1 표면용 전극 및 제2 표면용 전극을 각각 구비하고, 제1 표면용 전극이 제2 벌크용 전극과 연결되며, 제2 표면용 전극이 제2 베이스 전극과 연결되고, 인쇄회로기판의 상부에 마련되며, 제1 저역 차단 주파수(FCS1)와 제1 고역 차단 주파수(FCS2)의 사이를 차단하고 제2 저역 차단 주파수(FCS3)와 제2 고역 차단 주파수(FCS4)의 사이를 차단하는 대역 제거 필터인 표면 탄성파 필터 칩;을 포함하며,

상기 표면 탄성파 필터 칩의 차단 주파수에서 나타나는 신호 감쇠 정도는 상기 벌크 탄성파 필터 칩의 차단 주파수에서 나타나는 신호 감쇠 정도 보다 크고,

상기 FCB1은 상기 FCS2 보다 작으며, 상기 FCB2는 상기 FCS3 보다 큰 것을 특징으로 하는 스커트 특성이 향상된 고주파 프론트 엔드 모듈.A high frequency front end module for separating transmission and reception signals from high frequency signals.

A printed circuit board having a first base electrode and a second base electrode to which an input / output signal is applied; And

And at least one channel filter unit provided on the printed circuit board, each passing a different frequency band.

One channel filter unit,

A bulk piezoelectric layer between the first bulk electrode and the second bulk electrode, and the first bulk electrode and the second bulk electrode, respectively, wherein the first bulk electrode is connected to the first base electrode, and is printed. A bulk acoustic wave filter chip provided on an upper portion of the circuit board, the bulk acoustic wave filter chip being a band pass filter passing between the low cutoff frequency FCB1 and the high cutoff frequency FCB2; And

A surface piezoelectric layer and a first surface electrode and a second surface electrode provided on the surface of the piezoelectric layer and spaced apart from each other, respectively, wherein the first surface electrode is connected to the second bulk electrode; The second surface electrode is connected to the second base electrode, is provided on the printed circuit board, and cuts between the first low frequency cutoff frequency FCS1 and the first high frequency cutoff frequency FCS2. And a surface acoustic wave filter chip which is a band cancellation filter for blocking between FCS3) and the second high pass cutoff frequency FCS4.

The degree of signal attenuation at the cutoff frequency of the surface acoustic wave filter chip is greater than the amount of signal attenuation at the cutoff frequency of the bulk acoustic wave filter chip,

The FCB1 is smaller than the FCS2, and the FCB2 is larger than the FCS3.

입출력 신호가 인가되는 제1 베이스 전극 및 제2 베이스 전극을 구비하는 인쇄회로기판; 및

인쇄회로기판 상에 구비되고, 각각이 서로 다른 주파수 대역을 통과시키는 하나 이상의 채널 필터부;를 포함하며,

어느 한 채널 필터부는,

제1 벌크용 전극 및 제2 벌크용 전극과, 제1 벌크용 전극 및 제2 벌크용 전극 사이의 벌크용 압전층을 각각 구비하고, 제1 벌크용 전극이 제1 베이스 전극과 연결되며, 인쇄회로기판의 상부에 마련되는 벌크 탄성파 필터 칩; 및

표면용 압전층과, 표면용 압전층의 상부에 서로 이격되게 구비된 제1 표면용 전극 및 제2 표면용 전극을 각각 구비하고, 제1 표면용 전극이 제2 벌크용 전극과 연결되며, 제2 표면용 전극이 제2 베이스 전극과 연결되고, 인쇄회로기판의 상부에 마련되는 표면 탄성파 필터 칩;을 포함하며,

상기 표면 탄성파 필터 칩의 차단 주파수에서 나타나는 신호 감쇠 정도는 상기 벌크 탄성파 필터 칩의 차단 주파수에서 나타나는 신호 감쇠 정도 보다 크고,

상기 인쇄회로기판 상에 벌크 탄성파 필터 칩이 배치되며, 상기 벌크 탄성파 필터 칩 상에 상기 표면 탄성파 필터 칩이 배치되는 것을 특징으로 하는 스커트 특성이 향상된 고주파 프론트 엔드 모듈.A high frequency front end module for separating transmission and reception signals from high frequency signals.

A printed circuit board having a first base electrode and a second base electrode to which an input / output signal is applied; And

And at least one channel filter unit provided on the printed circuit board, each passing a different frequency band.

One channel filter unit,

A bulk piezoelectric layer between the first bulk electrode and the second bulk electrode, and the first bulk electrode and the second bulk electrode, respectively, wherein the first bulk electrode is connected to the first base electrode, and is printed. A bulk acoustic wave filter chip provided on the circuit board; And

A surface piezoelectric layer and a first surface electrode and a second surface electrode provided on the surface of the piezoelectric layer and spaced apart from each other, respectively, wherein the first surface electrode is connected to the second bulk electrode; And a surface acoustic wave filter chip connected to the second surface electrode and connected to the second base electrode and provided on the printed circuit board.

The degree of signal attenuation at the cutoff frequency of the surface acoustic wave filter chip is greater than the amount of signal attenuation at the cutoff frequency of the bulk acoustic wave filter chip,

A bulk acoustic wave filter chip is disposed on the printed circuit board, and the surface acoustic wave filter chip is disposed on the bulk acoustic wave filter chip.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020180018327A KR102009188B1 (en) | 2018-02-14 | 2018-02-14 | Filter chip package and RF front-end module having improved skirt feature |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020180018327A KR102009188B1 (en) | 2018-02-14 | 2018-02-14 | Filter chip package and RF front-end module having improved skirt feature |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR102009188B1 true KR102009188B1 (en) | 2019-08-09 |

Family

ID=67613781

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020180018327A KR102009188B1 (en) | 2018-02-14 | 2018-02-14 | Filter chip package and RF front-end module having improved skirt feature |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR102009188B1 (en) |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06310978A (en) * | 1993-04-26 | 1994-11-04 | Murata Mfg Co Ltd | Surface acoustic wave resonance filter |

| KR100719123B1 (en) * | 2006-07-27 | 2007-05-18 | 삼성전자주식회사 | Multi band filter module and manufacture method of the same |

| JP2012028976A (en) * | 2010-07-22 | 2012-02-09 | Murata Mfg Co Ltd | Piezoelectric device |

-

2018

- 2018-02-14 KR KR1020180018327A patent/KR102009188B1/en active IP Right Grant

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06310978A (en) * | 1993-04-26 | 1994-11-04 | Murata Mfg Co Ltd | Surface acoustic wave resonance filter |

| KR100719123B1 (en) * | 2006-07-27 | 2007-05-18 | 삼성전자주식회사 | Multi band filter module and manufacture method of the same |

| JP2012028976A (en) * | 2010-07-22 | 2012-02-09 | Murata Mfg Co Ltd | Piezoelectric device |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US11476226B2 (en) | Radio-frequency module and communication device | |

| CN111355495B (en) | High frequency module | |

| US7944325B2 (en) | Electrical module with specified ground-side connection of filter circuit shunt arms | |

| US10181829B2 (en) | Amplification circuit | |

| JP6508920B2 (en) | Elastic wave device and transmission / reception device | |

| US10873352B2 (en) | Radio-frequency module and communication apparatus | |

| US11757429B2 (en) | Hybrid filter device and multiplexer | |

| JP6809994B2 (en) | Electronic filters and filter devices | |

| WO2021002296A1 (en) | High frequency module and communication device | |

| JPH10126213A (en) | Branching filter package | |

| KR102059285B1 (en) | Multiplexer | |

| WO2021044691A1 (en) | High frequency module and communication device | |

| CN106888001B (en) | Acoustic wave device and wafer level packaging method thereof | |

| US11658641B2 (en) | High-frequency module | |

| US9941859B2 (en) | Ladder-type filter, duplexer, and module | |

| CN213585766U (en) | High-frequency module and communication device | |

| CN106888002B (en) | Acoustic wave device and wafer level packaging method thereof | |

| KR102009188B1 (en) | Filter chip package and RF front-end module having improved skirt feature | |

| US11127686B2 (en) | Radio-frequency module and communication device | |

| US11621739B2 (en) | Radio-frequency module and communications device | |

| KR101983972B1 (en) | Side-mounting type of filter chip package and RF front-end module having the same | |

| KR100306630B1 (en) | Composite Surface Acoustic Wave Filter | |

| KR100986470B1 (en) | Ceramic Package | |

| JPH09232910A (en) | Flat plate multi-layered branch filter package | |

| KR100489825B1 (en) | Flip chip type surface acoustic wave apparatus |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| GRNT | Written decision to grant |