KR101842177B1 - Light emitting device - Google Patents

Light emitting device Download PDFInfo

- Publication number

- KR101842177B1 KR101842177B1 KR1020100072831A KR20100072831A KR101842177B1 KR 101842177 B1 KR101842177 B1 KR 101842177B1 KR 1020100072831 A KR1020100072831 A KR 1020100072831A KR 20100072831 A KR20100072831 A KR 20100072831A KR 101842177 B1 KR101842177 B1 KR 101842177B1

- Authority

- KR

- South Korea

- Prior art keywords

- electrode

- layer

- light emitting

- semiconductor layer

- emitting device

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 claims abstract description 89

- 230000000903 blocking effect Effects 0.000 claims description 13

- 238000000034 method Methods 0.000 claims description 9

- 238000009792 diffusion process Methods 0.000 claims description 2

- 238000005286 illumination Methods 0.000 abstract description 12

- 239000000758 substrate Substances 0.000 description 32

- 230000007480 spreading Effects 0.000 description 15

- 238000003892 spreading Methods 0.000 description 15

- 239000000463 material Substances 0.000 description 12

- 229910052751 metal Inorganic materials 0.000 description 11

- 239000002184 metal Substances 0.000 description 11

- 229910052782 aluminium Inorganic materials 0.000 description 9

- 229910052709 silver Inorganic materials 0.000 description 9

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 8

- 150000004767 nitrides Chemical class 0.000 description 7

- 239000002019 doping agent Substances 0.000 description 6

- 229910052759 nickel Inorganic materials 0.000 description 6

- PXHVJJICTQNCMI-UHFFFAOYSA-N nickel Substances [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 6

- 239000007789 gas Substances 0.000 description 5

- 239000010931 gold Substances 0.000 description 5

- 239000011777 magnesium Substances 0.000 description 5

- 229910002704 AlGaN Inorganic materials 0.000 description 4

- 150000001875 compounds Chemical class 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 229910052737 gold Inorganic materials 0.000 description 4

- 238000004519 manufacturing process Methods 0.000 description 4

- 238000000465 moulding Methods 0.000 description 4

- 239000011347 resin Substances 0.000 description 4

- 229920005989 resin Polymers 0.000 description 4

- 239000011787 zinc oxide Substances 0.000 description 4

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 3

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 3

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 3

- 229910045601 alloy Inorganic materials 0.000 description 3

- 239000000956 alloy Substances 0.000 description 3

- 230000004888 barrier function Effects 0.000 description 3

- JAONJTDQXUSBGG-UHFFFAOYSA-N dialuminum;dizinc;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Al+3].[Al+3].[Zn+2].[Zn+2] JAONJTDQXUSBGG-UHFFFAOYSA-N 0.000 description 3

- 229910001873 dinitrogen Inorganic materials 0.000 description 3

- 238000000605 extraction Methods 0.000 description 3

- 229910052732 germanium Inorganic materials 0.000 description 3

- 239000012535 impurity Substances 0.000 description 3

- 239000007769 metal material Substances 0.000 description 3

- 229920000139 polyethylene terephthalate Polymers 0.000 description 3

- 239000005020 polyethylene terephthalate Substances 0.000 description 3

- 230000008569 process Effects 0.000 description 3

- XCZXGTMEAKBVPV-UHFFFAOYSA-N trimethylgallium Chemical compound C[Ga](C)C XCZXGTMEAKBVPV-UHFFFAOYSA-N 0.000 description 3

- 229910000980 Aluminium gallium arsenide Inorganic materials 0.000 description 2

- 229910005191 Ga 2 O 3 Inorganic materials 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 239000010949 copper Substances 0.000 description 2

- VRIVJOXICYMTAG-IYEMJOQQSA-L iron(ii) gluconate Chemical compound [Fe+2].OC[C@@H](O)[C@@H](O)[C@H](O)[C@@H](O)C([O-])=O.OC[C@@H](O)[C@@H](O)[C@H](O)[C@@H](O)C([O-])=O VRIVJOXICYMTAG-IYEMJOQQSA-L 0.000 description 2

- 229910052749 magnesium Inorganic materials 0.000 description 2

- 229910001092 metal group alloy Inorganic materials 0.000 description 2

- 239000000203 mixture Substances 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 229910052697 platinum Inorganic materials 0.000 description 2

- 229920003229 poly(methyl methacrylate) Polymers 0.000 description 2

- 229920000515 polycarbonate Polymers 0.000 description 2

- 239000004417 polycarbonate Substances 0.000 description 2

- -1 polyethylene terephthalate Polymers 0.000 description 2

- 239000004926 polymethyl methacrylate Substances 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000004332 silver Substances 0.000 description 2

- SKRWFPLZQAAQSU-UHFFFAOYSA-N stibanylidynetin;hydrate Chemical compound O.[Sn].[Sb] SKRWFPLZQAAQSU-UHFFFAOYSA-N 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- 229910052725 zinc Inorganic materials 0.000 description 2

- 239000011701 zinc Substances 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- OMKCMEGHMLKVPM-UHFFFAOYSA-N CC=CC=C[Mg] Chemical compound CC=CC=C[Mg] OMKCMEGHMLKVPM-UHFFFAOYSA-N 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 229910000881 Cu alloy Inorganic materials 0.000 description 1

- 229910002601 GaN Inorganic materials 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 1

- 229910000990 Ni alloy Inorganic materials 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- 229910001069 Ti alloy Inorganic materials 0.000 description 1

- DZLPZFLXRVRDAE-UHFFFAOYSA-N [O--].[O--].[O--].[O--].[Al+3].[Zn++].[In+3] Chemical compound [O--].[O--].[O--].[O--].[Al+3].[Zn++].[In+3] DZLPZFLXRVRDAE-UHFFFAOYSA-N 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- 125000000484 butyl group Chemical group [H]C([*])([H])C([H])([H])C([H])([H])C([H])([H])[H] 0.000 description 1

- 229910052791 calcium Inorganic materials 0.000 description 1

- 239000011575 calcium Substances 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000003486 chemical etching Methods 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 229920001577 copolymer Polymers 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- SBYXRAKIOMOBFF-UHFFFAOYSA-N copper tungsten Chemical compound [Cu].[W] SBYXRAKIOMOBFF-UHFFFAOYSA-N 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 238000001125 extrusion Methods 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- YZZNJYQZJKSEER-UHFFFAOYSA-N gallium tin Chemical compound [Ga].[Sn] YZZNJYQZJKSEER-UHFFFAOYSA-N 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 238000000227 grinding Methods 0.000 description 1

- 229910052735 hafnium Inorganic materials 0.000 description 1

- 230000017525 heat dissipation Effects 0.000 description 1

- 238000002248 hydride vapour-phase epitaxy Methods 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- HRHKULZDDYWVBE-UHFFFAOYSA-N indium;oxozinc;tin Chemical compound [In].[Sn].[Zn]=O HRHKULZDDYWVBE-UHFFFAOYSA-N 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 229910052741 iridium Inorganic materials 0.000 description 1

- 238000010030 laminating Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000001465 metallisation Methods 0.000 description 1

- 229910003465 moissanite Inorganic materials 0.000 description 1

- 238000001451 molecular beam epitaxy Methods 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- XIKYYQJBTPYKSG-UHFFFAOYSA-N nickel Chemical compound [Ni].[Ni] XIKYYQJBTPYKSG-UHFFFAOYSA-N 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 238000002161 passivation Methods 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Substances [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 1

- 229920003207 poly(ethylene-2,6-naphthalate) Polymers 0.000 description 1

- 239000011112 polyethylene naphthalate Substances 0.000 description 1

- 229920000915 polyvinyl chloride Polymers 0.000 description 1

- 239000004800 polyvinyl chloride Substances 0.000 description 1

- 239000002096 quantum dot Substances 0.000 description 1

- 238000009877 rendering Methods 0.000 description 1

- 229910052703 rhodium Inorganic materials 0.000 description 1

- 229910052711 selenium Inorganic materials 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- 239000002210 silicon-based material Substances 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 229910052712 strontium Inorganic materials 0.000 description 1

- 229920003002 synthetic resin Polymers 0.000 description 1

- 239000000057 synthetic resin Substances 0.000 description 1

- 229910052714 tellurium Inorganic materials 0.000 description 1

- 229910052718 tin Inorganic materials 0.000 description 1

- 229910001887 tin oxide Inorganic materials 0.000 description 1

- 239000012780 transparent material Substances 0.000 description 1

- IBEFSUTVZWZJEL-UHFFFAOYSA-N trimethylindium Chemical compound C[In](C)C IBEFSUTVZWZJEL-UHFFFAOYSA-N 0.000 description 1

- 238000000927 vapour-phase epitaxy Methods 0.000 description 1

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/36—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/14—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a carrier transport control structure, e.g. highly-doped semiconductor layer or current-blocking structure

- H01L33/145—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a carrier transport control structure, e.g. highly-doped semiconductor layer or current-blocking structure with a current-blocking structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/36—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes

- H01L33/38—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes with a particular shape

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/36—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes

- H01L33/40—Materials therefor

- H01L33/405—Reflective materials

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Led Devices (AREA)

Abstract

실시예는 발광소자, 발광소자 패키지 및 조명시스템에 관한 것이다.

실시예에 따른 발광소자는 제2 도전형 반도체층, 상기 제2 도전형 반도체층 상에 활성층 및 상기 활성층 상에 제1 도전형 반도체층을 포함하는 발광구조물; 상기 제1 도전형 반도체층 하부와 접하면서 상기 발광구조물 내에 형성된 하부 제1 전극; 상기 활성층 및 상기 제2 도전형 반도체층과 상기 하부 제1 전극 사이에 절연층; 및 상기 제1 도전형 반도체층 상부에 형성된 상부 제1 전극;을 포함한다.Embodiments relate to a light emitting device, a light emitting device package, and an illumination system.

The light emitting device includes a light emitting structure including a second conductive semiconductor layer, an active layer on the second conductive semiconductor layer, and a first conductive semiconductor layer on the active layer. A lower first electrode formed in the light emitting structure and contacting the lower portion of the first conductive semiconductor layer; An insulating layer between the active layer and the second conductive type semiconductor layer and the lower first electrode; And an upper first electrode formed on the first conductive type semiconductor layer.

Description

실시예는 발광소자, 발광소자 패키지 및 조명시스템에 관한 것이다.Embodiments relate to a light emitting device, a light emitting device package, and an illumination system.

발광소자(Light Emitting Device)는 전기에너지가 빛에너지로 변환되는 특성의 p-n 접합 다이오드를 주기율표상에서 Ⅲ족과 Ⅴ족의 원소가 화합하여 생성될 수 있다. LED는 화합물 반도체의 조성비를 조절함으로써 다양한 색상구현이 가능하다. A light emitting device can be produced by combining p-n junction diodes having the characteristic that electric energy is converted into light energy by elements of Group III and Group V on the periodic table. LEDs can be implemented in various colors by controlling the composition ratio of compound semiconductors.

발광소자는 순방향전압 인가 시 n층의 전자와 p층의 정공(hole)이 결합하여 전도대(Conduction band)와 가전대(Valance band)의 에너지 갭에 해당하는 만큼의 에너지를 발산하는데, 이 에너지는 주로 열이나 빛의 형태로 방출되며, 빛의 형태로 발산되면 발광소자가 되는 것이다.When a forward voltage is applied to a light emitting device, the electrons in the n-layer and the holes in the p-layer are coupled to emit energy corresponding to the energy gap between the conduction band and the valance band. It emits mainly in the form of heat or light, and emits in the form of light.

예를 들어, 질화물 반도체는 높은 열적 안정성과 폭넓은 밴드갭 에너지에 의해 광소자 및 고출력 전자소자 개발 분야에서 큰 관심을 받고 있다. 특히, 질화물 반도체를 이용한 청색(Blue) 발광소자, 녹색(Green) 발광소자, 자외선(UV) 발광소자 등은 상용화되어 널리 사용되고 있다.For example, nitride semiconductors have received great interest in the development of optical devices and high power electronic devices due to their high thermal stability and wide bandgap energy. Particularly, blue light emitting devices, green light emitting devices, ultraviolet (UV) light emitting devices, and the like using nitride semiconductors have been commercialized and widely used.

한편, 종래기술에 의하면 수직형 발광소자(LED)의 경우 n-GaN의 수직(vertical) 저항이 낮아 전류가 n-전극(n-electrode)의 주변으로 집중되는 현상(current crowding)이 발생되고, 이러한 전류밀집으로 인한 수명 및 신뢰성이 저하하는 문제가 있다. Meanwhile, according to the related art, in the case of a vertical type light emitting device (LED), the vertical resistance of the n-GaN is low and current crowding occurs around the n-electrode, There is a problem that the lifetime and reliability due to such current density are deteriorated.

종래기술은 전류밀집 현상을 완화하기 위해 p-GaN 표면에 전류차단층(CBL)을 배치하고 있으나, 전류차단층은 전류의 흐름을 일부 분산시켜주는 기능을 하나 전류 공급원의 차원에서 전류의 흐름을 효과적으로 확산(spreading) 시켜주는데 한계가 있다.In the prior art, the current blocking layer (CBL) is disposed on the surface of the p-GaN layer to mitigate the current crowding phenomenon. However, the current blocking layer partially diffuses the current flow. However, There is a limit to effective spreading.

실시예는 효과적인 전류 확산(current spreading)을 할 수 있는 발광소자, 발광소자 패키지 및 조명시스템을 제공하고자 한다.Embodiments provide a light emitting device, a light emitting device package, and an illumination system capable of effective current spreading.

실시예에 따른 발광소자는 제 1 도전형 반도체층, 제 2 도전형 반도체층, 상기 제 1 도전형 반도체층과 상기 제 2 도전형 반도체층 사이에 배치되는 활성층을 포함하고 상기 제 2 도전형 반도체층 및 상기 활성층을 관통하여 상기 제 1 도전형 반도체층의 일부 영역까지 배치되는 적어도 하나 이상의 트렌치를 포함하는 발광 구조물과 상기 제 1 도전형 반도체층의 상부에 배치되는 상부 제 1 전극과 상기 트렌치 내부에 배치되는 하부 제 1 전극과 상기 제 2 도전형 반도체층 하부에 배치되는 전류 차단층과 상기 제 2 도전형 반도체층 하부에 배치되며 상기 전류 차단층을 감싸며 배치되는 제2 전극층을 포함하고, 상기 전류 차단층은 상기 상부 제 1 전극과 수직으로 중첩되며 상기 하부 제1 전극과 상기 상부 제1 전극은 수직으로 중첩되지 않을 수 있다.The light emitting device according to an embodiment may include a first conductivity type semiconductor layer, a second conductivity type semiconductor layer, and an active layer disposed between the first conductivity type semiconductor layer and the second conductivity type semiconductor layer, And at least one trench extending through the active layer to a portion of the first conductive semiconductor layer, an upper first electrode disposed on the first conductive semiconductor layer, A current blocking layer disposed under the second conductive semiconductor layer, and a second electrode layer disposed under the second conductive semiconductor layer and disposed to surround the current blocking layer, The current blocking layer is vertically overlapped with the upper first electrode, and the lower first electrode and the upper first electrode may not overlap vertically.

삭제delete

삭제delete

또한, 실시예에 따른 조명시스템은 상기 발광소자 패키지를 구비하는 발광유닛을 포함한다.Further, the illumination system according to the embodiment includes a light emitting unit having the light emitting device package.

실시예에 따른 발광소자, 발광소자 패키지 및 조명시스템에 의하면, 발광구조물(110)의 위에 상부 제1 전극(132)을 형성할 뿐만아니라, 발광구조물(110)의 아래에 하부 제1 전극(131)을 형성시켜, 수직방향(vertical) 뿐만 아니라 수평방향(lateral)으로도 전류가 원활히 흐르게 하여 발광소자 칩 전체의 전류 확산(spreading)을 개선할 수 있다.According to the light emitting device, the light emitting device package and the illumination system according to the embodiment, not only the upper

도 1은 실시예에 따른 발광소자의 상면 예시도.

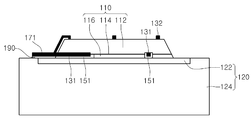

도 2는 실시예에 따른 발광소자의 제1 단면 예시도.

도 3a은 실시예에 따른 발광소자의 제2 단면 예시도이며, 도 3b는 실시예에 따른 발광소자의 제3 단면 예시도.

도 4는 실시예에 따른 발광소자의 효과 예시도.

도 5 내지 도 10은 실시예에 따른 발광소자 제조방법의 공정 단면 예시도.

도 11은 실시예에 따른 발광소자 패키지의 단면도.

도 12는 실시예에 따른 조명 유닛의 사시도.

도 13은 실시예에 따른 백라이트 유닛의 사시도.1 is an exemplary top view of a light emitting device according to an embodiment.

FIG. 2 is a first exemplary sectional view of a light emitting device according to an embodiment. FIG.

FIG. 3A is a cross-sectional view illustrating a light emitting device according to an embodiment of the present invention, and FIG. 3B is a cross-sectional view illustrating a third exemplary embodiment of the light emitting device according to the embodiment.

4 is a view illustrating an example of the effect of the light emitting device according to the embodiment.

FIG. 5 to FIG. 10 illustrate exemplary process cross sections of a method of manufacturing a light emitting device according to an embodiment.

11 is a cross-sectional view of a light emitting device package according to an embodiment.

12 is a perspective view of a lighting unit according to an embodiment;

13 is a perspective view of a backlight unit according to an embodiment.

실시 예의 설명에 있어서, 각 층(막), 영역, 패턴 또는 구조물들이 기판, 각 층(막), 영역, 패드 또는 패턴들의 "상/위(on/over)"에 또는 "아래(under)"에 형성되는 것으로 기재되는 경우에 있어, "상/위(on/over)"와 "아래(under)"는 "직접(directly)" 또는 "다른 층을 개재하여 (indirectly)" 형성되는 것을 모두 포함한다. 또한 각 층의 상/위 또는 아래에 대한 기준은 도면을 기준으로 설명한다.In the description of the embodiments, it is to be understood that each layer (film), area, pattern or structure may be referred to as being "on" or "under" the substrate, each layer Quot; on "and" under "are intended to include both" directly "or" indirectly " do. Also, the criteria for top, bottom, or bottom of each layer will be described with reference to the drawings.

도면에서 각층의 두께나 크기는 설명의 편의 및 명확성을 위하여 과장되거나 생략되거나 또는 개략적으로 도시되었다. 또한 각 구성요소의 크기는 실제크기를 전적으로 반영하는 것은 아니다.The thickness and size of each layer in the drawings are exaggerated, omitted, or schematically shown for convenience and clarity of explanation. Also, the size of each component does not entirely reflect the actual size.

(실시예)(Example)

실시예는 효과적인 전류 확산(current spreading)을 할 수 있는 발광소자, 발광소자 패키지 및 조명시스템을 제공하고자 한다.Embodiments provide a light emitting device, a light emitting device package, and an illumination system capable of effective current spreading.

도 1은 실시예에 따른 발광소자의 상면 예시도이며, 도 2는 실시예에 따른 발광소자의 제1 단면 예시도(도 1의 I-I'선을 따른 단면)이며, 도 3a은 실시예에 따른 발광소자의 제2 단면 예시도(도 1의 II-II'선을 따른 단면)이고, 도 3b은 실시예에 따른 발광소자의 제3 단면 예시도(도 1의 III-III'선을 따른 단면)이고, 도 4는 실시예에 따른 발광소자의 효과 예시도이다. 도 4는 도 2의 A 부분 확대 예시도이다.FIG. 1 is a top view of a light emitting device according to an embodiment of the present invention. FIG. 2 is a first cross-sectional view (a cross-sectional view taken along line I-I 'of FIG. 1) (A cross-sectional view taken along a line II-II 'in FIG. 1), and FIG. 3B is a cross-sectional view of a third embodiment of the light emitting device according to the embodiment And FIG. 4 is a view illustrating an example of the effect of the light emitting device according to the embodiment. 4 is an enlarged view of a portion A in Fig.

상기 과제를 해결하기 위해 실시예에 따른 발광소자(100)는 제2 도전형 반도체층(116), 상기 제2 도전형 반도체층(116) 상에 형성된 활성층(114) 및 상기 활성층(114) 상에 형성된 제1 도전형 반도체층(112)을 포함하는 발광구조물(110) 및 상기 제1 도전형 반도체층(112)과 접하면서 상기 발광구조물(110) 내에 하부 제1 전극(131)을 포함할 수 있다.A

이에 따라, 실시예에 따른 발광소자에 의하면, 도 4와 같이, 제1 도전형 반도체층의 상부 제1 전극(132) 뿐만 아니라, 하부(bottom) 영역에 하부 제1 전극(131)을 배치함으로써 발광소자의 전류확산(current spreading)을 효과적으로 개선할 수 있다.4, by disposing the lower

예를 들어, 실시예는 발광구조물(110)의 위에 상부 제1 전극(132)을 형성할 뿐만아니라, 발광구조물(110)의 아래에 하부 제1 전극(131)을 형성시켜, 수직방향(vertical) 뿐만 아니라 수평방향(lateral)으로도 전류가 원활히 흐르게 하여 발광소자 칩 전체의 전류 확산(spreading)을 개선할 수 있다.For example, in the embodiment, the upper

구체적으로, 실시예에서, 상기 하부 제1 전극(131)은 상기 제1 도전형 반도체층(112)과 전기적으로 연결되며, 상기 활성층(114), 상기 제2 도전형 반도체층(116)과는 전기적으로 격리될 수 있다.Specifically, in the embodiment, the lower

이를 위해, 상기 하부 제1 전극(131)과 상기 활성층(114) 및 상기 제2 도전형 반도체층(116) 사이에 절연층(151)을 포함할 수 있다. 상기 절연층(151)은 산화막, 질화막 등의 유전체층으로 형성될 수 있으나 이에 한정되는 것은 아니다.For this, an

실시예는 상기 제2 도전형 반도체층(116) 하부에 상기 제2 도전형 반도체층(116)과 전기적으로 연결되는 제2 전극층(120)을 구비하며, 상기 하부 제1 전극(131)은 상기 제2 전극층(120)과 전기적으로 격리될 수 있다. 이를 위해, 상기 제2 전극층(120)과 상기 하부 제1 전극(131) 사이에 절연층(151)을 포함할 수 있고, 상기 절연층(151)은 산화막, 질화막 등의 유전체층으로 형성될 수 있으나 이에 한정되는 것은 아니다.The second

상기 하부 제1 전극(131)은 발광구조물의 내부, 예를 들어, 상기 제1 도전형 반도체층(112)의 하부면에 위치함으로써 전류가 수평(lateral) 방향으로 흐르도록 하여, 상부 제1 전극(132)과 더불어 발광소자 칩 전체의 전류 확산(spreading)을 개선할 수 있다.The lower

상기 하부 제1 전극(131)은 반사 금속을 포함하여 발광된 빛의 외부 추출 효율을 증대시킬 수 있다. 예를 들어, 상기 하부 제1 전극(131)은 Al, Ag, 혹은 Al이나 Ag를 포함하는 합금을 포함하는 금속층을 포함할 수 있으나 이에 한정되는 것은 아니다.The lower

실시예는 상기 제1 도전형 반도체층(112) 상부에 형성된 상부 제1 전극(132)을 포함할 수 있다. 이를 통해, 실시예는 발광구조물(110)의 위에 상부 제1 전극(132)을 형성할 뿐만아니라, 발광구조물(110)의 아래에 하부 제1 전극(131)을 형성시켜, 수직방향(vertical) 뿐만 아니라 수평방향(lateral)으로도 전류가 원활히 흐르게 하여 발광소자 칩 전체의 전류 확산(spreading)을 개선할 수 있다.The exemplary embodiment may include an upper

상기 상부 제1 전극(132)은 상기 하부 제1 전극(131)과 공간적으로 상하 간에 오버랩되지 않도록 형성될 수 있다. 예를 들어, 상부 제1 전극(132)은 상기 하부 제1 전극(131)과 교차할 수는 있으나, 상하간에 동일 선상에 위치하지 않을 수 있으나 이에 한정되는 것은 아니다.The upper

실시예는, 상기 상부 제1 전극(132)과 공간적으로 상하 간에 오버랩되는 전류차단층(160)을 더 포함할 수 있고 이에 따라 수직 방향의 전류의 확산(spreading)에 기여할 수 있다. 예를 들어, 상기 전류차단층(160)은 상기 제2 도전형 반도체층(116)과 접하여 형성될 수 있으나 이에 한정되는 것은 아니다.The embodiment may further include a

실시예에서, 상기 상부 제1 전극(132)과 상기 하부 제1 전극(131)은 같은 패드에 연결될 수 있다. 예를 들어, 도 1과 같이 상기 상부 제1 전극(132)과 상기 하부 제1 전극(131)은 모두 제1 패드(171), 제2 패드(172)에 전기적으로 연결될 수 있으나 이에 한정되는 것은 아니다. 예를 들어, 상기 상부 제1 전극(132)은 제1 패드(171)에, 상기 하부 제1 전극(131)은 제2 패드(172)에 각각 전기적으로 연결될 수도 있다.In an embodiment, the upper

실시예에 따른 발광소자, 발광소자 패키지 및 조명시스템에 의하면, 발광구조물(110)의 위에 상부 제1 전극(132)을 형성할 뿐만아니라, 발광구조물(110)의 아래에 하부 제1 전극(131)을 형성시켜, 수직방향(vertical) 뿐만 아니라 수평방향(lateral)으로도 전류가 원활히 흐르게 하여 발광소자 칩 전체의 전류 확산(spreading)을 개선할 수 있다.According to the light emitting device, the light emitting device package and the illumination system according to the embodiment, not only the upper

이하, 도 5 내지 도 10을 참조하여, 실시예에 따른 발광소자 제조방법을 설명한다. 이하의 설명에서, 도 2의 A 부분 확대 예시도를 기준으로 제조방법을 설명하나 실시예가 이에 한정되는 것은 아니다.Hereinafter, a method of manufacturing a light emitting device according to an embodiment will be described with reference to FIGS. 5 to 10. FIG. In the following description, the manufacturing method will be described based on the example of the enlarged portion A in Fig. 2, but the embodiment is not limited thereto.

우선, 도 5와 같이 제1 기판(105)을 준비한다.First, the

상기 제1 기판(105)은 전도성 기판 또는 절연성 기판을 포함하며, 예컨대 상기 제1 기판(105)은 사파이어(Al2O3), SiC, Si, GaAs, GaN, ZnO, Si, GaP, InP, Ge, and Ga203. 중 적어도 하나를 사용할 수 있다. 상기 제1 기판(105) 위에는 요철 구조가 형성될 수 있으며, 이에 대해 한정하지는 않는다. 상기 제1 기판(105)에 대해 습식세척을 하여 표면의 불순물을 제거할 수 있다.The

이후, 상기 제1 기판(105) 상에 제1 도전형 반도체층(112), 활성층(114) 및 제2 도전형 반도체층(116)을 포함하는 발광구조물(110)을 형성할 수 있다.A

이때, 실시예에서 상기 제1 기판(105) 위에는 버퍼층(미도시)이 형성될 수 있다. 상기 버퍼층(미도시)은 상기 발광구조물(110)의 재료와 제1 기판(105)의 격자 부정합을 완화시켜 줄 수 있으며, 버퍼층의 재료는 3족-5족 화합물 반도체 예컨대, GaN, InN, AlN, InGaN, AlGaN, InAlGaN, AlInN 중 적어도 하나로 형성될 수 있다. 상기 버퍼층 위에는 언도프드(undoped) 반도체층이 형성될 수 있으며, 이에 대해 한정하지는 않는다. In this embodiment, a buffer layer (not shown) may be formed on the

상기 제1 도전형 반도체층(112)은 제1 도전형 도펀트가 도핑된 3족-5족 화합물 반도체로 구현될 수 있으며, 상기 제1 도전형 반도체층(112)이 N형 반도체층인 경우, 상기 제1도전형 도펀트는 N형 도펀트로서, Si, Ge, Sn, Se, Te를 포함할 수 있으나 이에 한정되지 않는다.The first

상기 제1 도전형 반도체층(112)은 InxAlyGa1 -x- yN (0≤x≤1, 0≤y≤1, 0≤x+y≤1)의 조성식을 갖는 반도체 물질을 포함할 수 있다. The first

상기 제1 도전형 반도체층(112)은 GaN, InN, AlN, InGaN, AlGaN, InAlGaN, AlInN,AlGaAs, InGaAs, AlInGaAs, GaP, AlGaP, InGaP, AlInGaP, InP 중 어느 하나 이상으로 형성될 수 있다.The first

상기 제1 도전형 반도체층(112)은 화학증착방법(CVD) 혹은 분자선 에피택시 (MBE) 혹은 스퍼터링 혹은 수산화물 증기상 에피택시(HVPE) 등의 방법을 사용하여 N형 GaN층을 형성할 수 있다. 또한, 상기 제1 도전형 반도체층(112)은 챔버에 트리메틸 갈륨 가스(TMGa), 암모니아 가스(NH3), 질소 가스(N2), 및 실리콘(Si)와 같은 n 형 불순물을 포함하는 실란 가스(SiH4)가 주입되어 형성될 수 있다.The first

상기 활성층(114)은 제1 도전형 반도체층(112)을 통해서 주입되는 전자와 이후 형성되는 제2 도전형 반도체층(116)을 통해서 주입되는 정공이 서로 만나서 활성층(발광층) 물질 고유의 에너지 밴드에 의해서 결정되는 에너지를 갖는 빛을 방출하는 층이다. Electrons injected through the first conductive

상기 활성층(114)은 단일 양자 우물 구조, 다중 양자 우물 구조(MQW: Multi Quantum Well), 양자 선(Quantum-Wire) 구조, 또는 양자 점(Quantum Dot) 구조 중 적어도 어느 하나로 형성될 수 있다. 예를 들어, 상기 활성층(114)은 트리메틸 갈륨 가스(TMGa), 암모니아 가스(NH3), 질소 가스(N2), 및 트리메틸 인듐 가스(TMIn)가 주입되어 다중 양자우물구조가 형성될 수 있으나 이에 한정되는 것은 아니다.The

상기 활성층(114)의 우물층/장벽층은 InGaN/GaN, InGaN/InGaN, AlGaN/GaN, InAlGaN/GaN , GaAs,/AlGaAs(InGaAs), GaP/AlGaP(InGaP) 중 어느 하나 이상의 페어 구조로 형성될 수 있으나 이에 한정되지 않는다. 상기 우물층은 상기 장벽층의 밴드 갭보다 낮은 밴드 갭을 갖는 물질로 형성될 수 있다.The well layer / barrier layer of the

상기 활성층(114)의 위 또는/및 아래에는 도전형 클래드층이 형성될 수 있다. 상기 도전형 클래드층은 AlGaN계 반도체로 형성될 수 있으며, 상기 활성층(114)의 밴드 갭보다는 높은 밴드 갭을 갖을 수 있다.A conductive clad layer may be formed on and / or below the

상기 제2 도전형 반도체층(116)은 제2 도전형 도펀트가 도핑된 3-족-5족 화합물 반도체 예컨대, InxAlyGa1 -x- yN (0≤x≤1, 0≤y≤1, 0≤x+y≤1)의 조성식을 갖는 반도체 물질을 포함할 수 있다. 상기 제2 도전형 반도체층(116)이 P형 반도체층인 경우, 상기 제2도전형 도펀트는 P형 도펀트로서, Mg, Zn, Ca, Sr, Ba 등을 포함할 수 있다.The second

상기 제2 도전형 반도체층(116)은 챔버에 트리메틸 갈륨 가스(TMGa), 암모니아 가스(NH3), 질소 가스(N2), 및 마그네슘(Mg)과 같은 p 형 불순물을 포함하는 비세틸 사이클로 펜타디에닐 마그네슘(EtCp2Mg){Mg(C2H5C5H4)2}가 주입되어 p형 GaN층이 형성될 수 있으나 이에 한정되는 것은 아니다.The second conductive

실시예에서 상기 제1 도전형 반도체층(112)은 N형 반도체층, 상기 제2 도전형 반도체층(116)은 P형 반도체층으로 구현할 수 있으나 이에 한정되지 않는다. 또한 상기 제2 도전형 반도체층(116) 위에는 상기 제2 도전형과 반대의 극성을 갖는 갖는 반도체 예컨대 N형 반도체층(미도시)을 형성할 수 있다. 이에 따라 발광구조물(110)은 N-P 접합 구조, P-N 접합 구조, N-P-N 접합 구조, P-N-P 접합 구조 중 어느 한 구조로 구현할 수 있다.In an exemplary embodiment, the first

다음으로, 도 6과 같이 상기 발광구조물(110)을 일부를 제거하여 제1 도전형 반도체층(112)을 노출하는 트렌치(T)를 형성할 수 있다. Next, as shown in FIG. 6, a part of the

예를 들어, 소정의 마스크 패턴(미도시)을 식각 마스크로 하여 제2 도전형 반도체층(116)과 활성층(114)을 관통하여 제1 도전형 반도체층(112)을 노출하도록 트렌치(T)를 형성할 수 있다. 상기 노출된 제1 도전형 반도체층(112)도 일부 제거될 수 있으나 이에 한정되는 것은 아니다.For example, a trench T is formed through the second

다음으로, 도 7과 같이 마스크 패턴을 제거하고, 상기 트렌치 내에 상기 노출된 제1 도전형 반도체층(112)과 접하는 하부 제1 전극(131)을 형성할 수 있다.Next, as shown in FIG. 7, the lower

이때, 상기 하부 제1 전극(131)은 상기 제1 도전형 반도체층(112)과 전기적으로 연결되며, 상기 활성층(114), 상기 제2 도전형 반도체층(116)과는 전기적으로 격리될 수 있다.The lower

이를 위해, 상기 하부 제1 전극(131)과 상기 활성층(114) 및 상기 제2 도전형 반도체층(116) 사이에 절연층(151)을 포함할 수 있다. 상기 절연층(151)은 산화막, 질화막 등의 유전체층으로 형성될 수 있으나 이에 한정되는 것은 아니다.For this, an insulating

상기 하부 제1 전극(131)은 발광구조물의 내부, 예를 들어, 상기 제1 도전형 반도체층(112)의 하부면에 위치함으로써 전류가 수평(lateral) 방향으로 흐르도록 하여, 상부 제1 전극(132)과 더불어 발광소자 칩 전체의 전류 확산(spreading)을 개선할 수 있다.The lower

상기 하부 제1 전극(131)은 반사 금속을 포함하여 발광된 빛의 외부 추출 효율을 증대시킬 수 있다. 예를 들어, 상기 하부 제1 전극(131)은 Al, Ag, 혹은 Al이나 Ag를 포함하는 합금을 포함하는 금속층을 포함할 수 있으나 이에 한정되는 것은 아니다.The lower

또한, 실시예는, 이후 형성된 상부 제1 전극(132)과 공간적으로 상하 간에 오버랩되는 전류차단층(160)을 더 포함할 수 있고 이에 따라 수직 방향의 전류의 확산(spreading)에 기여할 수 있다. 예를 들어, 상기 전류차단층(160)은 상기 제2 도전형 반도체층(116)과 접하여 형성될 수 있으나 이에 한정되는 것은 아니다. In addition, the embodiment may further include a

상기 전류차단층(160)은 절연층, 비정질 영역, 비도전형 영역, 제1 도전형 이온주입층 등으로 형성할 수 있으나 이에 한정되는 것은 아니다.The

다음으로, 도 8과 같이 상기 제2 도전형 반도체층(116) 상에 제2 전극층(120)을 형성할 수 있다.Next, the

한편, 실시예는 상기 하부 제1 전극(131)은 상기 제2 전극층(120)과 전기적으로 격리될 수 있다. 이를 위해, 상기 제2 전극층(120)과 상기 하부 제1 전극(131) 사이에 절연층(151)을 포함할 수 있고, 상기 절연층(151)은 산화막, 질화막 등의 유전체층으로 형성될 수 있으나 이에 한정되는 것은 아니다.Meanwhile, in the embodiment, the lower

상기 제2 전극층(120)은 오믹층(122), 반사층(미도시), 결합층(미도시), 전도성 기판(124) 등을 포함할 수 있다. 상기 제2 전극층(120)은 티탄(Ti), 크롬(Cr), 니켈(Ni), 알루미늄(Al), 백금(Pt), 금(Au), 텅스텐(W), 몰리브덴(Mo) 또는 불순물이 주입된 반도체 기판 중 적어도 어느 하나로 형성될 수도 있다.The

예를 들어, 상기 제2 전극층(120)은 오믹층(122)을 포함할 수 있으며, 정공주입을 효율적으로 할 수 있도록 단일 금속 혹은 금속합금, 금속산화물 등을 다중으로 적층하여 형성할 수 있다. 예를 들어, 상기 오믹층(122)은 ITO(indium tin oxide), IZO(indium zinc oxide), IZTO(indium zinc tin oxide), IAZO(indium aluminum zinc oxide), IGZO(indium gallium zinc oxide), IGTO(indium gallium tin oxide), AZO(aluminum zinc oxide), ATO(antimony tin oxide), GZO(gallium zinc oxide), IZON(IZO Nitride), AGZO(Al-Ga ZnO), IGZO(In-Ga ZnO), ZnO, IrOx, RuOx, NiO, RuOx/ITO, Ni/IrOx/Au, 및 Ni/IrOx/Au/ITO, Ag, Ni, Cr, Ti, Al, Rh, Pd, Ir, Ru, Mg, Zn, Pt, Au, Hf 중 적어도 하나를 포함하여 형성될 수 있으며, 이러한 재료에 한정되는 않는다.For example, the

또한, 상기 제2 전극층(120)이 반사층(미도시)을 포함하는 경우 Al, Ag, 혹은 Al이나 Ag를 포함하는 합금을 포함하는 금속층으로 이루어질 수 있다. 알루미늄이나 은 등은 활성층에서 발생된 빛을 효과적으로 반사하여 발광소자의 광추출 효율을 크게 개선할 수 있다.When the

또한, 상기 제2 전극층(120)은 층간 확산(Inter diffusion)을 방지하는 Ni, Ni-Alloy, Ti, Ti-Alloy, Cu, Cu-Alloy 등을 포함하는 확산방지층(Diffusion barrier layer)(미도시)를 더 포함할 수 있으나 이에 한정되는 것은 아니다.The

또한, 상기 제2 전극층(120)이 결합층을 포함하는 경우 상기 반사층(미도시)이 결합층의 기능을 하거나, 니켈(Ni), 금(Au) 등을 이용하여 결합층을 형성할 수 있다.In addition, when the

또한, 제2 전극층(120)은 전도성 기판(124)을 포함할 수 있다. 상기 전도성 기판(124)은 효율적으로 정공을 주입할 수 있도록 전기 전도성이 우수한 금속, 금속합금, 혹은 전도성 반도체 물질로 이루어질 수 있다. 예를 들어, 상기 전도성 기판(124)은 구리(Cu), 금(Au), 구리합금(Cu Alloy), 니켈(Ni-nickel), 구리-텅스텐(Cu-W), 캐리어 웨이퍼(예: GaN, Si, Ge, GaAs, ZnO, SiGe, SiC, Ga2O3 등) 등을 선택적으로 포함할 수 있다. 상기 전도성 기판(124)을 형성시키는 방법은 전기화학적인 금속증착방법이나 유테틱 메탈을 이용한 본딩 방법 등을 사용할 수 있다.In addition, the

다음으로, 도 9와 같이, 상기 제1 도전형 반도체층(112)이 노출되도록 상기 제1 기판(105)을 제거한다. 상기 제1 기판(105)을 제거하는 방법은 고출력의 레이저를 이용하여 제1 기판을 분리하거나 화학적 식각 방법을 사용할 수 있다. 또한, 상기 제1 기판(105)은 물리적으로 갈아냄으로써 제거할 수도 있다. Next, as shown in FIG. 9, the

예를 들어, 레이저 리프트 오프 방법은 상온에서 소정의 에너지를 가해주게 되면 상기 제1 기판(105)과 발광구조물(110)의 계면에서 에너지가 흡수되어 발광구조물의 접합표면이 열분해 되어 제1 기판(105)과 발광구조물을 분리할 수 있으나 이에 한정되는 것은 아니다.For example, when a predetermined energy is applied at room temperature, energy is absorbed at the interface between the

이후, 실시예는 상기 제1 도전형 반도체층(112) 상부에 형성된 상부 제1 전극(132)을 형성할 수 있다. 이를 통해, 실시예는 발광구조물(110)의 위에 상부 제1 전극(132)을 형성할 뿐만아니라, 발광구조물(110)의 아래에 하부 제1 전극(131)을 형성시켜, 수직방향(vertical) 뿐만 아니라 수평방향(lateral)으로도 전류가 원활히 흐르게 하여 발광소자 칩 전체의 전류 확산(spreading)을 개선할 수 있다.Hereinafter, the first

상기 상부 제1 전극(132)은 상기 하부 제1 전극(131)과 공간적으로 상하 간에 오버랩되지 않도록 형성될 수 있다. 예를 들어, 상부 제1 전극(132)은 상기 하부 제1 전극(131)과 교차할 수는 있으나, 상하간에 동일 선상에 위치하지 않을 수 있으나 이에 한정되는 것은 아니다.The upper

이를 통해, 도 10과 같이 실시예에 따른 발광소자(100)의 제조공정이 완료될 수 있다. 이후, 상기 하부 제1 전극(131)과 상기 상부 제1 전극(132)과 패드와의 전기적인 연결공정이 진행될 수 있다. 이를 위해, 패드와 발광구조물(110) 사이에 패시베이션층(190)이 절연층 등으로 형성될 수 있다.Thus, the manufacturing process of the

실시예에서, 상기 상부 제1 전극(132)과 상기 하부 제1 전극(131)은 같은 패드에 연결될 수 있다. 예를 들어, 도 1과 같이 상기 상부 제1 전극(132)과 상기 하부 제1 전극(131)은 모두 제1 패드(171), 제2 패드(172)에 전기적으로 연결될 수 있으나 이에 한정되는 것은 아니다. 예를 들어, 상기 상부 제1 전극(132)은 제1 패드(171)에, 상기 하부 제1 전극(131)은 제2 패드(172)에 각각 전기적으로 연결될 수도 있다.In an embodiment, the upper

실시예에 따른 발광소자, 발광소자 패키지 및 조명시스템에 의하면, n-GaN 표면의 n-전극(n-electrode) 뿐만 아니라, 하부(bottom) 영역에 매립된 n-전극(buried n-electrode)을 배치함으로써 수직형 LED 칩(chip)의 전류확산(current spreading)을 효과적으로 개선할 수 있다.According to the light emitting device, the light emitting device package and the illumination system according to the embodiment, the buried n-electrode buried in the bottom region as well as the n-electrode on the n-GaN surface The current spreading of the vertical type LED chip can be effectively improved.

도 11은 실시예에 따른 발광소자 패키지(200)의 단면도이다.11 is a cross-sectional view of a light emitting

도 11을 참조하면, 실시예에 따른 발광 소자 패키지는 패키지 몸체부(205)와, 상기 패키지 몸체부(205)에 설치된 제3 전극층(213) 및 제4 전극층(214)과, 상기 패키지 몸체부(205)에 설치되어 상기 제3 전극층(213) 및 제4 전극층(214)과 전기적으로 연결되는 발광 소자(100)와, 상기 발광 소자(100)를 포위하는 몰딩부재(240)가 포함된다.Referring to FIG. 11, a light emitting device package according to an embodiment includes a

상기 패키지 몸체부(205)는 실리콘 재질, 합성수지 재질, 또는 금속 재질을 포함하여 형성될 수 있으며, 상기 발광 소자(100)의 주위에 경사면이 형성될 수 있다.The

상기 제3 전극층(213) 및 제4 전극층(214)은 서로 전기적으로 분리되며, 상기 발광 소자(100)에 전원을 제공하는 역할을 한다. 또한, 상기 제3 전극층(213) 및 제4 전극층(214)은 상기 발광 소자(100)에서 발생된 빛을 반사시켜 광 효율을 증가시키는 역할을 할 수 있으며, 상기 발광 소자(100)에서 발생된 열을 외부로 배출시키는 역할을 할 수도 있다.The

상기 발광 소자(100)는 도 1 에 예시된 수직형 타입의 발광 소자가 적용될 수 있으나 이에 한정되는 것은 아니며, 수평형 발광소자도 적용될 수 있다.The

상기 발광 소자(100)는 상기 패키지 몸체부(205) 상에 설치되거나 상기 제3 전극층(213) 또는 제4 전극층(214) 상에 설치될 수 있다.The

상기 발광 소자(100)는 와이어(230)를 통해 상기 제3 전극층(213) 및/또는 제4 전극층(214)과 전기적으로 연결될 수 있으며, 실시예에서는 수직형 타입의 발광 소자(100)가 예시되어 있으며, 한 개의 와이어(230)가 사용된 것이 예시되어 있으나 이에 한정되는 것은 아니다.The

상기 몰딩부재(240)는 상기 발광 소자(100)를 포위하여 상기 발광 소자(100)를 보호할 수 있다. 또한, 상기 몰딩부재(240)에는 형광체가 포함되어 상기 발광 소자(100)에서 방출된 광의 파장을 변화시킬 수 있다.The

실시예에 따른 발광소자 패키지는 조명시스템에 적용될 수 있다. 상기 조명시스템은 도 12에 도시된 조명유닛, 도 13에 도시된 백라이드 유닛을 포함하고, 신호등, 차량 전조등, 간판 등이 포함될 수 있다.The light emitting device package according to the embodiment can be applied to the illumination system. The illumination system includes the illumination unit shown in Fig. 12, the back-ride unit shown in Fig. 13, and may include a traffic light, a vehicle headlight, a signboard, and the like.

도 12는 실시예에 따른 조명 유닛의 사시도(1100)이다.12 is a

도 12를 참조하면, 상기 조명 유닛(1100)은 케이스몸체(1110)와, 상기 케이스몸체(1110)에 설치된 발광모듈부(1130)과, 상기 케이스몸체(1110)에 설치되며 외부 전원으로부터 전원을 제공받는 연결 단자(1120)를 포함할 수 있다.12, the

상기 케이스몸체(1110)는 방열 특성이 양호한 재질로 형성되는 것이 바람직하며, 예를 들어 금속 재질 또는 수지 재질로 형성될 수 있다.The

상기 발광모듈부(1130)은 기판(1132)과, 상기 기판(1132)에 탑재되는 적어도 하나의 발광소자 패키지(200)를 포함할 수 있다.The light emitting

상기 기판(1132)은 절연체에 회로 패턴이 인쇄된 것일 수 있으며, 예를 들어, 일반 인쇄회로기판(PCB: Printed Circuit Board), 메탈 코아(Metal Core) PCB, 연성(Flexible) PCB, 세라믹 PCB 등을 포함할 수 있다. The

또한, 상기 기판(1132)은 빛을 효율적으로 반사하는 재질로 형성되거나, 표면이 빛이 효율적으로 반사되는 컬러, 예를 들어 백색, 은색 등으로 형성될 수 있다.Further, the

상기 기판(1132) 상에는 상기 적어도 하나의 발광소자 패키지(200)가 탑재될 수 있다. 상기 발광소자 패키지(200) 각각은 적어도 하나의 발광 다이오드(LED: Light Emitting Diode)(100)를 포함할 수 있다. 상기 발광 다이오드(100)는 적색, 녹색, 청색 또는 백색의 유색 빛을 각각 발광하는 유색 발광 다이오드 및 자외선(UV, UltraViolet)을 발광하는 UV 발광 다이오드를 포함할 수 있다.The at least one light emitting

상기 발광모듈부(1130)는 색감 및 휘도를 얻기 위해 다양한 발광소자 패키지(200)의 조합을 가지도록 배치될 수 있다. 예를 들어, 고 연색성(CRI)을 확보하기 위해 백색 발광 다이오드, 적색 발광 다이오드 및 녹색 발광 다이오드를 조합하여 배치할 수 있다.The light emitting

상기 연결 단자(1120)는 상기 발광모듈부(1130)와 전기적으로 연결되어 전원을 공급할 수 있다. 도 12에 도시된 것에 따르면, 상기 연결 단자(1120)는 소켓 방식으로 외부 전원에 돌려 끼워져 결합되지만, 이에 대해 한정하지는 않는다. 예를 들어, 상기 연결 단자(1120)는 핀(pin) 형태로 형성되어 외부 전원에 삽입되거나, 배선에 의해 외부 전원에 연결될 수도 있는 것이다.The

도 13는 실시예에 따른 백라이트 유닛의 분해 사시도(1200)이다. 13 is an exploded

실시예에 따른 백라이트 유닛(1200)은 도광판(1210)과, 상기 도광판(1210)에 빛을 제공하는 발광모듈부(1240)와, 상기 도광판(1210) 아래에 반사 부재(1220)와, 상기 도광판(1210), 발광모듈부(1240) 및 반사 부재(1220)를 수납하는 바텀 커버(1230)를 포함할 수 있으나 이에 한정되지 않는다.The

상기 도광판(1210)은 빛을 확산시켜 면광원화 시키는 역할을 한다. 상기 도광판(1210)은 투명한 재질로 이루어지며, 예를 들어, PMMA(polymethyl metaacrylate)와 같은 아크릴 수지 계열, PET(polyethylene terephthlate), PC(poly carbonate), COC(cycloolefin copolymer) 및 PEN(polyethylene naphthalate) 수지 중 하나를 포함할 수 있다. The

상기 발광모듈부(1240)은 상기 도광판(1210)의 적어도 일 측면에 빛을 제공하며, 궁극적으로는 상기 백라이트 유닛이 설치되는 디스플레이 장치의 광원으로써 작용하게 된다.The light emitting

상기 발광모듈부(1240)은 상기 도광판(1210)과 접할 수 있으나 이에 한정되지 않는). 구체적으로는, 상기 발광모듈부(1240)은 기판(1242)과, 상기 기판(1242)에 탑재된 다수의 발광소자 패키지(200)를 포함하는데, 상기 기판(1242)이 상기 도광판(1210)과 접할 수 있으나 이에 한정되지 않는다.The

상기 기판(1242)은 회로패턴(미도시)을 포함하는 인쇄회로기판(PCB, Printed Circuit Board)일 수 있다. 다만, 상기 기판(1242)은 일반 PCB 뿐 아니라, 메탈 코어 PCB(MCPCB, Metal Core PCB), 연성 PCB(FPCB, Flexible PCB) 등을 포함할 수도 있으며, 이에 대해 한정하지는 않는다.The

그리고, 상기 다수의 발광소자 패키지(200)는 상기 기판(1242) 상에 빛이 방출되는 발광면이 상기 도광판(1210)과 소정 거리 이격되도록 탑재될 수 있다.The plurality of light emitting device packages 200 may be mounted on the

상기 도광판(1210) 아래에는 상기 반사 부재(1220)가 형성될 수 있다. 상기 반사 부재(1220)는 상기 도광판(1210)의 하면으로 입사된 빛을 반사시켜 위로 향하게 함으로써, 상기 백라이트 유닛의 휘도를 향상시킬 수 있다. 상기 반사 부재(1220)는 예를 들어, PET, PC, PVC 레진 등으로 형성될 수 있으나, 이에 대해 한정하지는 않는다.The

상기 바텀 커버(1230)는 상기 도광판(1210), 발광모듈부(1240) 및 반사 부재(1220) 등을 수납할 수 있다. 이를 위해, 상기 바텀 커버(1230)는 상면이 개구된 박스(box) 형상으로 형성될 수 있으나, 이에 대해 한정하지는 않는다.The

상기 바텀 커버(1230)는 금속 재질 또는 수지 재질로 형성될 수 있으며, 프레스 성형 또는 압출 성형 등의 공정을 이용하여 제조될 수 있다.The

실시예에 따른 발광소자, 발광소자 패키지 및 조명시스템에 의하면, n-GaN 표면의 n-전극(n-electrode) 뿐만 아니라, 하부(bottom) 영역에 매립된 n-전극(buried n-electrode)을 배치함으로써 수직형 LED 칩(chip)의 전류확산(current spreading)을 효과적으로 개선할 수 있다.According to the light emitting device, the light emitting device package and the illumination system according to the embodiment, the buried n-electrode buried in the bottom region as well as the n-electrode on the n-GaN surface The current spreading of the vertical type LED chip can be effectively improved.

이상에서 실시예들에 설명된 특징, 구조, 효과 등은 적어도 하나의 실시예에 포함되며, 반드시 하나의 실시예에만 한정되는 것은 아니다. 나아가, 각 실시예에서 예시된 특징, 구조, 효과 등은 실시예들이 속하는 분야의 통상의 지식을 가지는 자에 의해 다른 실시예들에 대해서도 조합 또는 변형되어 실시 가능하다. 따라서 이러한 조합과 변형에 관계된 내용들은 실시예의 범위에 포함되는 것으로 해석되어야 할 것이다.The features, structures, effects, and the like described in the embodiments are included in at least one embodiment and are not necessarily limited to only one embodiment. Furthermore, the features, structures, effects and the like illustrated in the embodiments can be combined and modified by other persons skilled in the art to which the embodiments belong. Accordingly, the contents of such combinations and modifications should be construed as being included in the scope of the embodiments.

이상에서 실시예를 중심으로 설명하였으나 이는 단지 예시일 뿐 실시예를 한정하는 것이 아니며, 실시예가 속하는 분야의 통상의 지식을 가진 자라면 본 실시예의 본질적인 특성을 벗어나지 않는 범위에서 이상에 예시되지 않은 여러 가지의 변형과 응용이 가능함을 알 수 있을 것이다. 예를 들어, 실시예에 구체적으로 나타난 각 구성 요소는 변형하여 실시할 수 있는 것이다. 그리고 이러한 변형과 응용에 관계된 차이점들은 첨부된 청구 범위에서 설정하는 실시예의 범위에 포함되는 것으로 해석되어야 할 것이다.While the present invention has been particularly shown and described with reference to exemplary embodiments thereof, it will be understood by those skilled in the art that various changes in form and details may be made therein without departing from the spirit and scope of the invention. It can be seen that the modification and application of branches are possible. For example, each component specifically shown in the embodiments can be modified and implemented. It is to be understood that the present invention may be embodied in many other specific forms without departing from the spirit or essential characteristics thereof.

Claims (10)

상기 제 1 도전형 반도체층의 상부에 배치되는 상부 제 1 전극;

상기 트렌치 내부에 배치되는 하부 제 1 전극;

상기 제 2 도전형 반도체층 하부에 배치되는 전류 차단층; 및

상기 제 2 도전형 반도체층 하부에 배치되며 상기 전류 차단층을 감싸며 배치되는 제2 전극층을 포함하고,

상기 전류 차단층은 상기 상부 제 1 전극과 수직으로 중첩되며 상기 하부 제1 전극과 상기 상부 제1 전극은 수직으로 중첩되지 않는 발광소자.A first conductivity type semiconductor layer, a first conductivity type semiconductor layer, a first conductivity type semiconductor layer, and an active layer disposed between the first conductivity type semiconductor layer and the second conductivity type semiconductor layer and through the second conductivity type semiconductor layer and the active layer A light emitting structure including at least one trench disposed to a partial region of the first conductive semiconductor layer;

An upper first electrode disposed on the first conductive semiconductor layer;

A lower first electrode disposed inside the trench;

A current blocking layer disposed under the second conductive semiconductor layer; And

And a second electrode layer disposed under the second conductive semiconductor layer and surrounding the current blocking layer,

Wherein the current blocking layer is vertically overlapped with the upper first electrode, and the lower first electrode and the upper first electrode are not vertically overlapped.

상기 제 2 전극층은 확산방지층을 포함하며,

상기 하부 제 1 전극은 상기 제 1 도전형 반도체층과 맞닿고,

상기 하부 제 1 전극의 측면 및 하부에 배치되어 상기 제 2 도전형 반도체층과 상기 활성층 및 상기 제 2 전극층을 전기적으로 격리시키는 절연층을 더 포함하는 발광소자.The method according to claim 1,

Wherein the second electrode layer includes a diffusion preventing layer,

The lower first electrode is in contact with the first conductive semiconductor layer,

And an insulating layer disposed on a side surface and a lower surface of the lower first electrode to electrically isolate the second conductive type semiconductor layer from the active layer and the second electrode layer.

상기 하부 제1 전극은,

상기 제1 도전형 반도체층의 하부면에 위치하며 반사금속을 포함하고,

상기 제2전극층은 오믹층을 포함하는 발광소자.3. The method according to claim 1 or 2,

Wherein the lower first electrode comprises:

A first conductive semiconductor layer disposed on the lower surface of the first conductive semiconductor layer,

And the second electrode layer includes an ohmic layer.

상기 상부 제 1 전극과 상기 하부 제 1 전극은 상하간에 서로 엇갈리게 배치되며,

상기 상부 제1 전극은 제1 패드에, 상기 하부 제1 전극은 제2 패드에 각각 연결된 발광소자.6. The method of claim 5,

Wherein the upper first electrode and the lower first electrode are offset from each other in the upper and lower sides,

Wherein the upper first electrode is connected to the first pad and the lower first electrode is connected to the second pad.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020100072831A KR101842177B1 (en) | 2010-07-28 | 2010-07-28 | Light emitting device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020100072831A KR101842177B1 (en) | 2010-07-28 | 2010-07-28 | Light emitting device |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20120011176A KR20120011176A (en) | 2012-02-07 |

| KR101842177B1 true KR101842177B1 (en) | 2018-03-26 |

Family

ID=45835448

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020100072831A KR101842177B1 (en) | 2010-07-28 | 2010-07-28 | Light emitting device |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR101842177B1 (en) |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100818466B1 (en) * | 2007-02-13 | 2008-04-02 | 삼성전기주식회사 | Light emitting devices |

-

2010

- 2010-07-28 KR KR1020100072831A patent/KR101842177B1/en active IP Right Grant

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100818466B1 (en) * | 2007-02-13 | 2008-04-02 | 삼성전기주식회사 | Light emitting devices |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20120011176A (en) | 2012-02-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101114191B1 (en) | Light emitting device, method for fabricating the light emitting device | |

| US9287460B2 (en) | Light emitting device, light emitting device package and lighting system including the same | |

| US8669586B2 (en) | Light emitting device, light emitting device package, and lighting system | |

| KR101894025B1 (en) | Light emitting device | |

| US20120119254A1 (en) | Light emitting device, light emitting device package and lighting system including the same | |

| KR101836122B1 (en) | Light emitting device | |

| KR101701510B1 (en) | Light emitting device | |

| US8421106B2 (en) | Light emitting device, system and package | |

| EP2355182A2 (en) | Light emitting device | |

| EP2315272B1 (en) | Light emitting diode, light emitting diode package, and lighting system | |

| KR20120138275A (en) | Light emitting device | |

| KR101798238B1 (en) | Light emitting device | |

| KR101973608B1 (en) | Light emitting device | |

| KR101803573B1 (en) | Light emitting device | |

| KR101842177B1 (en) | Light emitting device | |

| KR101886153B1 (en) | Light emitting device | |

| KR101734544B1 (en) | Light emitting device package | |

| KR101701507B1 (en) | Light emitting device, method for fabricating the same and light emitting device package and lighting system including the same | |

| KR101871498B1 (en) | Light emitting device | |

| KR101829798B1 (en) | Light emitting device | |

| KR101856213B1 (en) | Light emitting device and method for fabricating the same | |

| KR20130079867A (en) | Light emitting device | |

| KR101823682B1 (en) | Light emitting device | |

| KR101880451B1 (en) | Light emitting device | |

| KR20130016945A (en) | Light emitting device and method for fabricating the same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E90F | Notification of reason for final refusal | ||

| E90F | Notification of reason for final refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant |