KR101157759B1 - 집적 레지스터를 가진 고전압 트랜지스터 장치 - Google Patents

집적 레지스터를 가진 고전압 트랜지스터 장치 Download PDFInfo

- Publication number

- KR101157759B1 KR101157759B1 KR1020100079694A KR20100079694A KR101157759B1 KR 101157759 B1 KR101157759 B1 KR 101157759B1 KR 1020100079694 A KR1020100079694 A KR 1020100079694A KR 20100079694 A KR20100079694 A KR 20100079694A KR 101157759 B1 KR101157759 B1 KR 101157759B1

- Authority

- KR

- South Korea

- Prior art keywords

- region

- regions

- voltage

- buried

- well region

- Prior art date

Links

- 239000000758 substrate Substances 0.000 claims abstract description 27

- 238000000034 method Methods 0.000 claims description 24

- 230000005669 field effect Effects 0.000 claims description 10

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 9

- 229920005591 polysilicon Polymers 0.000 claims description 9

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 6

- 239000000463 material Substances 0.000 claims description 5

- 235000012239 silicon dioxide Nutrition 0.000 claims description 3

- 239000000377 silicon dioxide Substances 0.000 claims description 3

- 239000010410 layer Substances 0.000 description 23

- 239000004065 semiconductor Substances 0.000 description 16

- 239000011229 interlayer Substances 0.000 description 5

- 210000000746 body region Anatomy 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 230000005684 electric field Effects 0.000 description 3

- 239000007943 implant Substances 0.000 description 3

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- 239000002800 charge carrier Substances 0.000 description 2

- 239000003989 dielectric material Substances 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- OQCFWECOQNPQCG-UHFFFAOYSA-N 1,3,4,8-tetrahydropyrimido[4,5-c]oxazin-7-one Chemical compound C1CONC2=C1C=NC(=O)N2 OQCFWECOQNPQCG-UHFFFAOYSA-N 0.000 description 1

- WYTGDNHDOZPMIW-RCBQFDQVSA-N alstonine Natural products C1=CC2=C3C=CC=CC3=NC2=C2N1C[C@H]1[C@H](C)OC=C(C(=O)OC)[C@H]1C2 WYTGDNHDOZPMIW-RCBQFDQVSA-N 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- 238000004804 winding Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/80—Field effect transistors with field effect produced by a PN or other rectifying junction gate, i.e. potential-jump barrier

- H01L29/808—Field effect transistors with field effect produced by a PN or other rectifying junction gate, i.e. potential-jump barrier with a PN junction gate, e.g. PN homojunction gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/06—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration

- H01L27/0611—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration integrated circuits having a two-dimensional layout of components without a common active region

- H01L27/0617—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration integrated circuits having a two-dimensional layout of components without a common active region comprising components of the field-effect type

- H01L27/0629—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration integrated circuits having a two-dimensional layout of components without a common active region comprising components of the field-effect type in combination with diodes, or resistors, or capacitors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L28/00—Passive two-terminal components without a potential-jump or surface barrier for integrated circuits; Details thereof; Multistep manufacturing processes therefor

- H01L28/20—Resistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0607—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration

- H01L29/0611—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices

- H01L29/0615—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE]

- H01L29/063—Reduced surface field [RESURF] pn-junction structures

- H01L29/0634—Multiple reduced surface field (multi-RESURF) structures, e.g. double RESURF, charge compensation, cool, superjunction (SJ), 3D-RESURF, composite buffer (CB) structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/10—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode not carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/1025—Channel region of field-effect devices

- H01L29/1029—Channel region of field-effect devices of field-effect transistors

- H01L29/1058—Channel region of field-effect devices of field-effect transistors with PN junction gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/10—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode not carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/1066—Gate region of field-effect devices with PN junction gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/73—Bipolar junction transistors

- H01L29/737—Hetero-junction transistors

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Chemical & Material Sciences (AREA)

- Composite Materials (AREA)

- Manufacturing & Machinery (AREA)

- Semiconductor Integrated Circuits (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Abstract

고전압 장치 구조가 구조 중 JFET를 포함하는 탭 트랜지스터에 결합된 레지스터를 포함하고, JFET의 터미널에 제공된 전압은 외부 전압이 JFET의 핀치-오프 전압보다 작을 때 외부 전압에 실질적으로 비례한다. 터미널에 제공된 전압은 외부 전압이 핀치-오프 전압보다 클 때 실질적으로 일정하다. 레지스터의 일단은 외부 전압이 핀치-오프 전압보다 클 때 실질적으로 외부 전압에 있다. 외부 전압이 음일 때, 레지스터는 기판에 주입되는 전류를 제한한다. 상기 요약은 검색자 또는 다른 독자가 본 기술 개시의 주제를 빠르게 확인하도록 요약을 규정하는 규칙에 부합하게 제공되었음을 강조한다.

Description

본 개시는 일반적으로 고전압 장치 구조의 분야에 관한 것이다.

고전압, 전계-효과 트랜지스터(HVFETs;High-Voltage, Field-Effect Transistor)는 반도체 분야에 잘 알려져 있다. 많은 HVFETs는 장치가 "오프(off) 상태"에 있을 때 적용된 고전압(예, 200V 또는 그 이상)을 지지하거나 "차단(block)"하는 확장된 드레인 영역을 포함하는 장치 구조를 채용한다. 상기 타입의 HVFETs는 오프라인 전원, 모터 제어 등등을 위한 AC/DC 변환기(converter)와 같은 파워 변환 애플리케이션에서 주로 사용된다. 상기 장치는 고전압에서 스위치될 수 있고, "온(on)" 상태에서 레지스터가 흐르는 전류를 최소화하는 반면 오프 상태에서 고 차단 전압을 달성할 수 있다. 전형적인 HVFET의 확장된 드레인 영역은 일반적으로 장치가 오프일 때 드레인에 적용되는 고전압을 지지하기에 약하게 도핑된다. 확장된 드레인 영역의 길이는 더 넓은 구역에 전기장을 펼치는 전형적인 저전압 MOSFET에 비해 증가되어, 상기 장치는 고전압을 지탱할 수 있다. 상기 장치가 온(즉 도전성)일 때, 전류는 확장된 드레인 영역을 통해 흐른다.

수직 HVFET 구조에서, 반도체 물질의 메사(mesa)는 온 상태의 전류 흐름을 위한 연장된 드레인(drain) 또는 드리프트(drift) 영역을 형성한다. 트렌치 게이트(trench gate) 구조는 몸체 영역이 배치된 메사의 측벽 영역에 인접한, 기판의 정상 가까이 형성된다. 게이트에 대한 적절한 전압 전위(potential)의 적용은, 전류가 반도체 물질, 즉 소스 영역이 배치된 기판의 정상 표면(top surface)으로부터 드레인 영역이 위치한 기판의 바닥까지를 통하여 수직 방향으로 흐르도록, 도전 채널을 몸체 영역의 수직 측벽 부분을 따라 형성되게 한다.

전형적인 파워 집적 회로(IC; Integrated Circuit) 장치는 트렌지스터의 드레인이 외부 핀에 직접 결합되는 구조의 큰 수직 고전압 출력 트랜지스터를 종종 채용한다. IC는 반도체 다이(semiconductor die) 또는 고전압 출력 트랜지스터를 포함하는 반도체 다이로부터 분리된 칩 상에 형성되는 제어기 회로를 포함한다. 두 개의 반도체 칩(제어기 및 출력 트랜지스터)는 동일 IC 패키지에 일반적으로 수용된다. IC의 제어기 회로를 위한 시동 전류(start-up)를 제공하기 위해, 외부 고전압이 외부 핀에 적용될 수 있다. 제어기는 접합 전계-효과 트랜지스터(JFET; Junction Field-Effect Transistor) "탭(tap)" 구조에 의해 제한되는 외부-적용 고전압으로부터 전형적으로 보호된다. 예를 들어, 고전압 출력 트랜지스터의 드레인이 550V가 취해지면, 탭 트랜지스터는 제어기에 결합되는 최대 전압을 대략 50V로 제한하여 장치의 시동을 위한 작은 전류(2-3mA)를 제공한다. 하지만, 상기 형태의 회로 배치의 문제는 어떤 전원 배치에서 일반적으로 일어나는 바와 같이, 드레인 핀이 음(negative)으로 갈 때 발생한다. 수직 출력 HVFET의 드레인 상의 음의 스윙(negative swing)은 다량의 소수 캐리어를 기판에 주입할 수 있는데, 이는 제어기의 잠금(latch-up)을 초래할 수 있다.

다음의 설명에서 본 발명의 명료한 이해를 제공하기 위해, 물질 타입, 크기, 구조 특징, 프로세싱 단계 등과 같은 구체적인 상세를 설명한다. 하지만, 본 기술 분야에 당업자는 상기 구체적인 상세가 설명된 실시예를 실행하는데 필요하지 않을 수도 있다는 것을 이해할 것이다.

도면의 구성요소는 표시를 위한 것이며 명확성의 관점에서 치수를 맞춘 것은 아님을 이해해야 한다. 비록 IC 이용 N-채널 트랜지스터 장치가 개시되더라도, P-채널 트랜지스터가 모든 적합한 도핑된 영역을 위한 반대의 도전성 타입을 이용함으로써 제작될 수도 있다는 것이 이해된다. 또한, 고전압 반도체 장치의 당업자는 도면에 예시로 보인 것들과 같은 트랜지스터 구조가 다른 트랜지스터 장치 구조와 집적되거나 상이한 장치가 공통 연결과 반도체 영역(예, N-웰(well), 기판 등)을 공유하도록 제작될 수 있다.

본 출원의 본문에서, 고전압 또는 파워 트랜지스터는 "오프" 상태 또는 조건에서 대략 150V 또는 그 이상을 지지할 수 있는 반도체 트랜지스터 구조이다. 일 실시예에서, 고전압 출력 트랜지스터는 소스와 드레인 영역 사이에 제공되는 고전압을 가지는 N-채널 금속-산화물-반도체 전계-효과 트랜지스터(MOSFET; Metal-Oxide-Semiconductor Field-Effect Transistor)로서 도시된다. 다른 실시예에서, 고전압 출력 트랜지스터는 쌍극 접합 트랜지스터(BJT; Bipolar Junction Transistor), 절연 게이트 전계 효과 트랜지스터(IGFET; Insulated Gate Field Effect Transistor) 또는 트랜지스터 기능을 제공하는 다른 장치 구조를 포함할 수 있다.

상기 개시의 목적으로, "접지(ground)" 또는 "접지 전위(ground potential)"는 회로 또는 IC의 모든 다른 전압 또는 전위가 정의되거나 측정되는데 대한 참조 전압 또는 전위를 말한다.

본 개시의 본문에서, 탭 트랜지스터는, 적용된 전압이 트랜지스터 장치의 핀치-오프 전압(pinch-off voltage) 보다 작을 때, 제1 또는 탭 터미널에서 전압이 상기 제2 및 제3 터미널을 가로질러 적용되는 전압에 실질적으로 비례하는 트랜지스터 장치 구조이다. 상기 제2 및 제3 터미널을 가로질러 적용된 전압이 핀치 오프 전압을 초과할 때, 탭 터미널에 제공된 전압은 증가된 적용 전압에 대해 실질적으로 일정하거나 변화하지 않는다. 일 실시예에서, 탭 트랜지스터는 접합 전계 효과 트랜지스터(JFET)를 포함한다.

본 발명의 일 실시예에서 탭 트랜지스터는, 적용된 전압이 트랜지스터 장치의 핀치-오프 전압(pinch-off voltage) 보다 작을 때, 제1 또는 탭 터미널에서 전압이 상기 제2 및 제3 터미널을 가로질러 적용되는 전압에 실질적으로 비례하는 트랜지스터 장치 구조이다. 상기 제2 및 제3 터미널을 가로질러 적용된 전압이 핀치 오프 전압을 초과할 때, 탭 터미널에 제공된 전압은 증가된 적용 전압에 대해 실질적으로 일정하거나 변화하지 않는다. 일 실시예에서, 탭 트랜지스터는 접합 전계 효과 트랜지스터(JFET)를 포함한다.

본 발명은 첨부 도면에 의해 제한되지 않으며 실시예에 의해 설명된다.

도 1은 파워 집적 회로(IC)의 출력 섹션의 예시적 회로의 개략도를 보인다.

도 2는 도 1의 파워 IC의 사용을 위한 대체적 집적 고전압 장치 구조의 예시적 균등 회로 개략도를 보인다.

도 3은 도 1&2에 도시된 집적 고전압 장치 구조의 예시적 단면을 보인다.

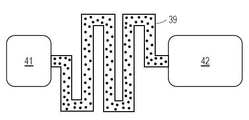

도 4는 도 3에 도시된 집적 고전압 장치 구조의 예시적 정상(top), 배치도를 보인다.

도 1은 파워 집적 회로(IC)의 출력 섹션의 예시적 회로의 개략도를 보인다.

도 2는 도 1의 파워 IC의 사용을 위한 대체적 집적 고전압 장치 구조의 예시적 균등 회로 개략도를 보인다.

도 3은 도 1&2에 도시된 집적 고전압 장치 구조의 예시적 단면을 보인다.

도 4는 도 3에 도시된 집적 고전압 장치 구조의 예시적 정상(top), 배치도를 보인다.

도 1은 게이트, 접지된 소스 및, 외부 핀 또는 노드(VEXTERNAL)(13)에 결합된 드레인을 가진 큰, 수직 N-채널 HVFET(11)을 포함하는 파워 집적 회로(IC)의 출력 섹션(10)의 예시적 회로의 개략도를 보인다. 게이트에 적용된 제어 전압은 노드(13)에서 전압 상태(예, 높거나 낮음)을 결정한다. 전류는 HVFET(11)가 도전성, 즉 온-상태에 있을 때 노드(13)에 연결되는 하나 또는 그 이상의 외부 로드(load)에 흐를 수 있다. 스위치 모드에서, 전원 IC, 예를 들어 출력 트랜지스터(11)는 트랜스포머의 제1와인딩을 통해 전류를 제어할 수 있어, 전원에 의해 전달되는 파워를 제어한다.

도 1은 접지된 게이트를 가지는 탭 트랜지스터(15)와 집적 고전압 레지스터(14)에 결합된 그 드레인(노드 17)을 포함하는, 도시된 실시예에서, 집적 고전압 장치 구조(12)를 보인다. 탭 트랜지스터(15)의 소스(노드 16)는 일 실시예에 따라 대략 50V에 제한될 수 있는 IC의 내부 제어기에 탭 전압을 제공한다. 내부 제어기 회로(미도시)와 장치 구조(12)는 출력 트랜지스터(11)를 포함하는 반도체 다이(die)로부터 분리된 반도체 다이 상에 형성될 수 있다.

도 1의 예에서, 레지스터(14)는 탭 트랜지스터(15)를 포함하는 고전압 장치 구조 내 집적된 작은(예. ~100 ohm) 레지스터를 포함한다. 레지스터(14)는 필드 산화물의 두꺼운 층의 정상(top)에 형성된 폴리실리콘으로 이루어진다. 고전압을 견디기 위하여, 레지스터(14)는 탭 트랜지스터(15)의 N-웰 영역 바로 위의 필드 산화물 상에 배치된다(도 3 참조). 탭 트랜지스터(15)의 드레인 패드 금속은 레지스터(14)의 일단, 즉 노드(17)에 연결되고, 레지스터(14)의 타단은 HVFET(11)의 드레인, 즉 노드(13)에 연결된다.

파워 IC 장치의 조작 중, 수직 HVFET(11)의 드레인(노드 13)이 음의 전압으로 전환될 때, 레지스터(14)는 제어기로 흐르는 전류를 제한하여, 내부 제어기 회로의 잠금(latch-up)을 방지한다. 레지스터(14)의 값은 잠금이 일어나기 전 IC의 제어기 섹션에 허용할 수 있는 최대 전류에 기반하여 결정될 수 있다. 예를 들어, 파워 IC 장치가 10mA에 달하도록 전류를 허용할 수 있다면, 그리고 HVFET(11)의 드레인이 약 -1V의 음의 전압으로 전환할 수 있다는 최악의 케이스 시나리오를 가정하면, 레지스터(14)는 100 ohms의 저항값을 가져야 한다.

본 기술 분야의 실시자(practitioner)는 노드(13)가 양의 전압, 즉 550V로 전환될 때, 레지스터(14)의 두 터미널 단부(즉, 노드 13 & 17)이 실질적으로 동일한 고전압 레벨로 상승하는 것을 이해할 것이다. 즉, 단지 비교적 작은 전압 전위 차이만 노드 13 및 17 사이의 레지스터(14)를 가로질러 나타난다. 예를 들어 노드(13)에 결합된 레지스터(14)의 일단은 550V 일 수 있다; 반면 노드(17)에 결합된 레지스터(14)의 타단은 약 549.8V 일 수 있다. HVFET(11)의 드레인 금속 전극과 기저(underlying) 탭 트랜지스터 구조의 N-웰은 또한 노드(13)에 결합된 레지스터(14)의 단부와 실질적으로 동일한 전위이다. 상기 상태(즉, 오프-상태)에서, N-웰 하부 기판과 탭 트랜지스터의 게이트는 접지 전위에 또는 접지 전위에 가까이 있다.

제어 회로는 탭 트랜지스터(15)와 레지스터(14)를 통과하여 노드(13)으로부터 시동 전류(예, ~2mA)를 이끈다. 이것이 일어날 때, 레지스터(14)(100 ohm 저항으로 가정)를 가로질러 떨어지는 전압은 약 0.2V 이고, 이는 이용가능한 전압에 비해 무시할 정도이다.

도 2는 대체 집적 장치 구조(20)의 예시적 동등 회로의 개략도를 보인다. 장치 구조(20)는 도 1의 파워 IC 중 장치 구조(12)에 대한 대체안으로서 사용될 수 있다. 장치 구조(20)는 도 1에 도시된 동일 기본 회로 구조 중 집적 레지스터(14)를 가진 노드(17)에 연결되는 탭 트랜지스터(15)를 포함한다. 노드(16)은 트랜지스터(15)의 소스이고, 파워 IC의 제어기 섹션에 탭 전압을 제공한다. 노드(17)은 탭 트랜지스터(15)의 드레인이고, 이것은 레지스터(14)의 일단에 연결된다.

또한 노드(17)에 연결된 것은 고전압 MOSFET(22)의 드레인으로서, 이것은 그 소스, 바디 영역(body region) 및 접지 게이트가 배치된 것으로 도시된다. 정상 작동 조건에서, 트랜지스터(22)는 오프, 즉 비전도성(non-conducting)이다. 일 실시예에서, 고전압 MOSFET(22)와 탭 트랜지스터(15)는 두 장치가 P-타입 기판에 형성된 동일 N-웰 영역을 공유하도록 제작된다. 도 2의 실시예에서, 트랜지스터(15), 레지스터(14) 및, 전압 MOSFET(22)가 출력 트랜지스터(11)를 포함하는 반도체 다이로부터 분리된 반도체 다이 상에 배치된다는 것이 이해되어야 한다.

도 3은 도 1 & 2에 도시된 집적 고전압 장치 구조의 예시적 횡단면(30)을 보인다. 상기 실시예에서, 탭 트랜지스터는 고전압 레지스터(39)로 집적되고, 후자는 P-타입 매립 영역(buried region)을 포함하지 않는 N-웰 영역(33)의 구역을 덮는 필드 산화물 영역(38)의 섹션 상에 형성된 폴리실리콘층을 포함한다. 즉, 레지스터(39)는 P-타입 매립 영역이 결여된 N-웰(33)의 영역 상에 직접 배치된다. 상기 구조 배열은, 고전압 전위가 고전압 출력 트랜지스터(11)의 드레인에 결합되는, 전극 또는 터미널(41)에 적용될 때, 레지스터(39)의 바로 아래 필드 산화물(38)을 가로질러 나타나는 전압을 제한한다.

도시된 대로, 실질적으로 평행한 이격된 복수의 P-타입 매립 영역(34)은 레지스터(39)의 바로 아래 구역에 수평 방향으로 인접한 N-웰(33)의 왼쪽 구역에 배치되는 것으로 보인다. 최상부 매립 영역(34)은 필드 산화물 영역(38)과 일치하는 것으로 보인다. N-웰(33)의 오른쪽 구역은 탭 JFET 구조를 포함하고, 이것은 N+ 영역(36 및 37) 사이에 형성된 필드 산화물 영역(38)의 섹션 아래 배치된 실질적으로 평행하게 이격된 복수의 P-타입 매립 영역(35)을 포함한다.

상기 실시예에서, P-타입 매립 영역(34 및 35)는 N+ 영역(36 및 37) 아래로 연장하지 않는다는 것을 유의한다. 중간층 유전층(40)은 필드 산화물 영역(38)과 레지스터층(39)의 부분에 형성된다. 전극(41)은 중간층 유전층(40)을 통해 층(39)의 일단에 전기적 연결을 제공한다. 중간층 유전층(40)의 개방을 통해(Via opening) 전극(32)이 층(39)의 일단과 또한 N+ 영역(36)(도 1 & 2의 노드 17)에 전기적으로 연결되는 것을 허용한다. 전극(43)은 중간층 유전층(40)과 필드 산화물 영역(38) 내 개방을 통해 N+ 영역(37)(노드 16)에 전기적 연결을 제공한다.

반도체 분야의 실시자는 P 타입 매립 영역(35)이 JFET 구조의 게이트를 포함하는 것을 이해할 것이다. 깊은 임플랜트(implant)(미도시) 또는 다른 타입의 균등 구조는 각 매립 영역(35)의 일단에 전기적으로 연결하는데 사용될 수 있다. 예를 들어, 도 3에서, P 타입 매립 영역(35)의 좌측 최단부가 접지된다. 유사한 구조가 매립 영역(34)의 각각에 전기적으로 연결되는데 사용될 수 있다. 이것은 탭 트랜지스터를 포함하는 JFET 구조의 게이트가, 도 1 & 2에 도시된 접지에서의 전위 또는 접지에 가까운 전위에 전기적으로 연결되는 것을 허용한다.

오프 상태에서, 접지되지 않은 P 타입 매립 영역(35)의 각 단부(즉 영역(37)에 가장 근접한 단부)는 최대 전압, 예를 들어 출력 트랜지스터(11)의 드레인인 전극(43)에 나타나는 실질적으로 동일한 전압까지 상승한다. 상기 배치에서, 노드(13)에 적용되는 외부 고전압은 P 타입 매립층(35)의 각각을 수평 방향으로 가로질러 떨어진다. 따라서, JFET 게이트(P 타입 매립 영역)의 실제 전압은 JFET 구조의 드레인(영역 37)로부터 소스(영역 36)까지 수평 방향으로 변한다.

도 3에 도시된 장치 구조의 일 실시예에서, 필드 산화물(38)은 N-웰 영역(33)과 P-기판 영역(31)에 걸쳐 대략 5000-10000 angstroms 의 두께로 형성된다. 본 기술 분야의 실시자는 폴리실리콘 레지스터층(39)이 전극(41)에서 적용된 최대 고전압 전위(>500V)까지 상승할 때, 필드 산화물(38)의 두께는 장기간 전압을 신뢰성있게 지지하기에 부족하다는 것을 이해할 것이다. 폴리실리콘층(39)이 고전압(예, 500-700V)에 있을 때, 기저 P 기판 영역(31)은 전형적으로 접지되는 것이 더 이해된다. 상기 상태에서, 폴리실리콘 레지스터 아래 N-웰 영역(33)이 폴리실리콘 레지스터층(39)의 전압 전위와 실질적으로 동일한 전압 전위까지 상승하도록, 전압은 P 타입 매립층(34 & 35)를 가로질러 떨어진다. 이것은 필드 산화물(폴리실리콘층(39)과 기저 N-웰 영역(33) 사이)을 가로질러 전압 전위가 비교적 작은 것을 보장한다.

도 3의 횡단면 예에서, 전극 또는 터미널(41, 42 및 43)은 도 1 및 2의 노드(13, 17 및 16)에 각각 대응한다. 상술한 바와 같이, P 기판(31)과 P 매립 영역(34 & 35)이 접지되고, 전극(43)(탭)에서의 전압은 어떤 핀치-오프 전압까지 전극(42)에서의 전압에 비례한다. 만약 전극(42)에서의 전압이 핀치-오프 전압을 초과하면, 전극(43)에서의 전압은 전극(41 및 42)에 나타날 수 있는 최대 전압보다 상당히 작은 탭 전위에서 비교적 일정하게 유지된다. 이런 식으로, 도 3에 도시된 집적 고전압 장치 구조는 파워 트랜지스터 IC의 저전압 전기망(예, 제어기 섹션)을 전극(41)에서 나타나는 고전압으로부터 보호한다.

반도체 분야의 당업자는 도 3에 도시된 집적 고전압 장치 구조의 탭 트랜지스터 부분은 드레인(전극(42)에 연결된 N+ 영역(36)), 전형적으로 접지되는(연결을 통함, 미도시) 게이트(P 타입 매립 영역(35) 및 P 기판(31)) 및, P-기판(31)에 배치된 다른 전기망에 전압을 제공하는, 탭 터미널 또는 노드로서 작동하는 소스(전극(43)에 연결된 N+ 영역(37))을 가지는 접합 전계 효과 트랜지스터(JFET)를 포함한다는 것을 이해할 것이다. 도 2에 도시된 실시예에서, 탭 트랜지스터(15)를 포함하는 JFET는 고전압 MOSFET(22)로 집적된다; 즉, 탭 트랜지스터(15)와 고전압 MOSFET(22)는 공통 N-웰 영역을 공유한다.

도 3의 예시적 실시예에 계속하여, P-타입 매립 영역(34 및 35)의 각각의 최상부는 기판의 표면에서 N-웰(33) 내 임베드, 즉 필드 산화물(38)과 일치하거나 인접하는 것으로 도시된다. P-타입 매립 영역(34 & 35)의 잔여분의 각각은 N-웰(33) 내 복수의 JFET 도전 채널을 생성하도록 수직 방향으로 분리된다. 도 3의 실시예에서, JFET 채널수는 P-타입 매립 영역(35)의 수와 같다.

영역(34 & 35)는 예를 들어 고에너지 이온 임플랜테이션(implantation)에 의해 형성될 수 있다. 이것은 P-매립 영역(34)(층(39) 아래)과 P 매립 영역(35)(N+ 영역(36 & 37) 사이)와 인터리브된(interleave) 복수의 JFET 도전 채널로 나뉘는 N-웰 영역(33)을 만든다. N-웰(33)은 또한 고에너지 이온 임플랜테이션에 의해 형성될 수 있다는 것이 이해된다. 애벌란치 브레이크다운(avalanche breakdown)이 일어나는 임계 전기장(critical electric field) 아래 N-웰 P 매립층 접합에서 최대 전기장을 유지하기 위해, 임플랜트 에너지와 양(dose)이 선택될 수 있다. 일 실시예에서, P 매립 영역(34 & 35)와 각 JFET 채널에서의 최대 전하는 약 1-2×1012/cm2 이다. 당업자는 복수의 JFET 도전 채널을 가진 N-웰 영역(33)을 형성하기 위해, N-웰 및 복수의 P 매립 영역의 도핑과 임플랜트 에너지가 상술한 전하 레벨에 근사하기 위해 선택될 수 있다는 것을 이해할 것이다.

도 1의 파워 IC의 정상 조작 중, 전극(42 & 43) 사이의 전압차가 작을 때, 전류는 터미널(42)로부터 N-웰(33) 내 JFET 도전 채널을 통해 터미널(43)까지 흐른다. 터미널(43)에서의 전압이 증가할 때, N-웰(33)의 자유 전하 캐리어 농도(concentration)는 P-타입 기판(31)과 P-타입 매립 영역(35)까지 역 바이어스에 의해 크게 감소된다(deplete). 전극(42)과 P-타입 기판(31) 사이의 전압차가 어떤 전압(즉 핀치-오프 전압)에 도달할 때, JFET 도전 채널은 역 바이어스에 의해 자유 전하 캐리어가 완전히 없어진다. 상기 핀치-오프 전압을 넘어서면, 전극(42 및 43) 사이의 N-웰(33)의 저항은 크게 증가하여, 전극(43)에서의 전압은 핀치-오프 전압에서 실질적으로 고정된다. 일 실시예에서, 핀치-오프는 약 40-50V 에서 일어난다.

전극(41)이 고전압, 즉 550V 이면, 폴리실리콘 레지스터층(39)(즉 전극(41 및 42))의 양 단부는 실질적으로 동일한 고전압까지 상승한다. 예를 들어, 550V 전압이 전극(41)에 나타날 때, 전극(42)은 레지스터층(39)의 저항값에 의존하여 약 549.8V의 전압 전위에 있을 수 있고, 전류는 레지스터층(39) 및 트랜지스터(15)를 통해 흐른다. 레지스터층(39)의 바로 아래 N-웰 영역(33)은 전극(42)과 실질적으로 동일한 고전위에 있다. IC의 제어기 섹션이 시동 전류(예, 2mA)를 전극(41)으로부터 이끌 때, 작은 무시할만한 전압 강하(예, ~0.2V)가 전극(41 & 42) 사이의 레지스터층(39)을 가로질러 일어난다.

비록 최상부의 P-타입 매립 영역(34 & 35)가 N-웰 영역(33)의 상부면에 배치된 대로 도 3에 도시되어 있지만, 다른 실시예에서 최상부 P-타입 매립 영역은 N-웰 영역(33)의 상부면의 바로 아래에 형성될 수 있어서, 필드 산화물(38)의 바로 아래 표면에서 JFET 도전 채널을 생성한다.

다른 실시예에서, 복수의 P-타입 매립 영역을 가지는 대신, 단지 단일 P-타입 매립 영역(34)과 단일 P-타입 매립 영역(35)이 N-웰(33)의 반대쪽에 형성된다.

일 실시예에서, 필드 산화물 영역(38)은 열성장(thermal growth)과 화학 기상 증착법(chemical vapor deposition)을 포함하는 다양한 공지의 방법을 사용하여 형성된 이산화규소(silicon dioxide)를 포함한다. 다른 실시예에서 필드 산화물 영역(38)은 질화규소(silicon nitride) 또는 다른 적합한 유전 물질을 포함할 수 있다. 유사하게 중간층 유전층(40)은 이산화규소, 질화규소 또는 다른 적합한 유전 물질을 포함할 수 있다.

도 4는 도 3에 도시된 집적 고전압 장치 구조의 예시적 정상(top), 배치도를 보인다. 레지스터(39)가 터미널(41 & 42) 사이의 간격을 최소화하는 서펜타인(serpentine) 배치로 형성되는 것에 유의한다.

비록 본 발명이 특정 실시예와 연결하여 설명되어졌으나, 본 기술분야의 당업자는 많은 수정예와 변형예가 본 발명의 범위에서 잘 이루어질 수 있음을 이해할 것이다. 따라서, 명세서와 도면은 제한의 의미가 아닌 도시의 의미로 이해되어야 한다.

Claims (27)

- 고전압 장치로서,

제1 도전 타입의 기판(31);

상기 기판(31)에 배치된 제2 도전 타입의 웰(well) 영역(33);

상기 웰 영역에 배치된 제2 도전 타입의 +영역들(36, 37) - 상기 +영역들(36, 37)은 상기 웰 영역의 한 구역에 의해 분리됨 -;

상기 +영역들을 분리하는 상기 웰 영역(33)의 상기 한 구역 내 배치된 제1 도전 타입의 하나 이상의 매립 영역(35) - 상기 매립 영역(35)은 상기 +영역들을 분리하는 상기 웰 영역(33)의 상기 한 구역 내에 도전 채널들을 정의하고, 상기 하나 이상의 매립 영역(35)은 상기 두 개의 +영역(36, 37)으로부터 이격됨 -;

상기 웰 영역(33)의 다른 구역 내 배치된 제1 도전 타입의 하나 이상의 다른 매립 영역(34) - 상기 웰 영역(33)의 또 다른 구역이 상기 두 개의 +영역 중 하나의 +영역으로부터 상기 하나 이상의 다른 매립 영역(34)을 분리시킴 -;

상기 +영역들을 분리하는 상기 웰 영역(33)의 상기 한 구역 내 배치된 매립 영역들과 상기 웰 영역의 상기 다른 구역 내에 배치된 매립 영역들 상에 형성된 유전층(38);

상기 또 다른 구역의 바로 위의 상기 유전층(38) 상에 형성된 레지스터층(39) - 상기 레지스터층(39)은 제1 단부 및 제2 단부를 가짐 -;

상기 레지스터층(39)의 상기 제1 단부 및 제2 단부에 각각 전기적으로 연결된 제1 터미널(41) 및 제2 터미널(42) - 상기 제2 터미널(42)은 또한 상기 두 개의 +영역(36, 37) 중 하나의 +영역(36)에 전기적으로 연결되는데, 상기 웰 영역(33)의 상기 다른 구역 내 배치된 상기 하나 이상의 다른 매립 영역(34)은 상기 웰 영역의 상기 또 다른 구역에 의해 그 하나의 +영역(36)으로부터 분리됨 -;

상기 두 개의 +영역(36, 37) 중 다른 +영역(37)에 전기적으로 연결되는 탭 터미널(43); 및

상기 +영역들과 상기 웰 영역(33)의 상기 다른 구역 내 배치된 상기 다른 매립 영역들(34)을 분리하는, 상기 기판(31)과 상기 웰 영역(33)의 상기 한 구역 내 배치된 상기 하나 이상의 매립 영역(35)에 전기적으로 연결되는 제4 터미널 - 상기 탭 터미널(43)에 공급되는 전압은 상기 제1 터미널(41)과 상기 제4 터미널 사이의 전압차가 고전압 장치의 핀치-오프(pinch-off) 전압보다 작을 때 그 전압차에 실질적으로 비례하고, 상기 탭 터미널(43)에 공급되는 전압은 상기 전압차가 핀치-오프 전압보다 클 때 실질적으로 일정하며, 상기 레지스터층(39)은 상기 전압차가 핀치-오프 전압보다 클 때 상기 전압차와 실질적으로 동일한 전위에서 플로팅(floating)함 -

을 포함하는 고전압 장치. - 제1항에 있어서,

상기 웰 영역(33)의 상기 또 다른 구역은 상기 제1 도전 타입의 매립 영역이 없는 고전압 장치. - 제1항에 있어서,

상기 +영역들을 분리하는 상기 웰 영역(33)의 상기 한 구역 내 배치된 상기 하나 이상의 매립 영역(35)은 상기 제1 도전 타입의 수직 방향으로 이격된 복수의 매립 영역을 포함하는 고전압 장치. - 제3항에 있어서,

상기 +영역들을 분리하는 상기 웰 영역(33)의 상기 한 구역 내 배치된 상기 하나 이상의 매립 영역(35)의 최상부 영역은 상기 유전층(38)에 인접하는 고전압 장치. - 제3항에 있어서,

상기 도전 채널들은, 상기 +영역들을 분리하는 상기 웰 영역(33)의 상기 한 구역 내 배치된 상기 매립 영역들(35) 각각의 사이와, 상기 +영역들을 분리하는 상기 웰 영역(33)의 상기 한 구역 내 배치된 상기 매립 영역들(35)의 최하부 영역과 상기 기판(31) 사이에 정의되는 고전압 장치. - 제1항에 있어서,

상기 +영역들을 분리하는 상기 웰 영역(33)의 상기 한 구역 내 배치된 상기 하나 이상의 매립 영역(35)은, 상기 제1 도전 타입의 단일의 매립 영역(35)을 포함하고, 상기 단일의 매립 영역(35)의 상부와 하부에 상기 도전 채널들이 정의되는 고전압 장치. - 제1항에 있어서,

상기 웰 영역(33)의 상기 다른 구역 내 배치된 상기 하나 이상의 다른 매립 영역(34)은 상기 제1 도전 타입의 수직 방향으로 이격된 복수의 다른 매립 영역(34)을 포함하는 고전압 장치. - 제7항에 있어서,

상기 웰 영역(33)의 상기 다른 구역 내 배치된 상기 다른 매립 영역(34)의 최상부 영역은 상기 유전층(38)에 인접하는 고전압 장치. - 제1항에 있어서,

상기 웰 영역(33)의 상기 다른 구역 내 배치된 상기 하나 이상의 다른 매립 영역(34)은 상기 제1 도전 타입의 단일의 다른 매립 영역(34)을 포함하는 고전압 장치. - 파워 집적 회로(IC)로서,

드레인을 갖는 제1 트랜지스터(11) 소자; 및

제2 트랜지스터 소자

를 포함하고,

상기 제2 트랜지스터 소자는,

제1 도전 타입의 웰 영역(33)의 한 구역 내 형성된 접합 전계-효과 트랜지스터(JFET: Junction Field-Effect Transistor) - 상기 웰 영역(33)은 제2 도전 타입의 기판(31)에 배치되고, 상기 JFET는 상기 웰 영역(33)에 배치된 상기 제1 도전 타입의 +영역들(36, 37)을 가지며, 상기 +영역들은 상기 제2 도전 타입의 하나 이상의 매립 영역(35)에 의해 정의된 복수의 도전 채널에 의해 분리됨 -;

상기 웰 영역(33)의 다른 구역 상에 형성된 레지스터(39) - 상기 레지스터(39)는 유전층(38)에 의해 상기 웰 영역(33)의 상기 다른 구역으로부터 절연되고, 상기 웰 영역(33)의 상기 다른 구역은 상기 +영역들(36, 37) 중 제1 +영역(36)에 인접하며, 상기 레지스터(39)는 제1 단부 및 제2 단부를 갖고, 상기 제2 단부는 상기 JFET의 상기 +영역들(36, 37) 중 상기 제1 +영역(36)에 전기적으로 연결됨 -; 및

상기 레지스터(39)의 제1 단부와 상기 제1 트랜지스터(11)의 드레인에 전기적으로 연결된 제1 전극(41), 상기 JFET의 상기 +영역들(36, 37) 중 제2 +영역(37)에 전기적으로 연결된 탭 전극(43), 및 상기 기판(31)과 상기 매립 영역들(35)에 전기적으로 연결된 제3 전극

을 포함하고,

상기 탭 전극(43)에 공급되는 전압은 상기 제1 전극(41)과 상기 제3 전극 사이의 전압차가 상기 JFET의 핀치-오프 전압보다 작을 때 그 전압차에 실질적으로 비례하고, 상기 탭 전극(43)에 공급되는 전압은 상기 전압차가 핀치-오프 전압보다 클 때 실질적으로 일정하고, 상기 레지스터(39)는 상기 전압차가 핀치-오프 전압보다 클 때 상기 전압차와 실질적으로 동일한 전위에서 플로팅하는, 파워 IC. - 제10항에 있어서,

상기 탭 전극에 결합되는 제어 소자를 더 포함하는 파워 IC. - 제11항에 있어서,

상기 제어 회로는 상기 제1 트랜지스터(11)의 게이트에 결합되고, 상기 제어 회로는 상기 제1 트랜지스터(11)를 스위치 온 및 스위치 오프하도록 동작가능한 파워 IC. - 제10항에 있어서,

외부 핀을 더 포함하고, 상기 제1 트랜지스터(11)는 수직 고전압 출력 트랜지스터를 포함하고, 상기 드레인은 상기 외부 핀에 전기적으로 연결되는 파워 IC. - 제10항에 있어서,

상기 하나 이상의 매립 영역은 수직 방향으로 이격된 복수의 매립 영역을 포함하는 파워 IC. - 제13항에 있어서,

상기 레지스터(39)는 출력 핀이 상기 기판(31)에 대해 네가티브 전위일 때 상기 기판(31)에 투입되는 전류를 제한하도록 기능하는 파워 IC. - 제10항에 있어서,

상기 웰 영역은 상기 다른 구역에 인접하는 또 다른 구역을 포함하고, 상기 또 다른 구역은 상기 제2 도전 타입의 하나 이상의 매립 영역을 포함하는 파워 IC. - 제16항에 있어서,

상기 웰 영역(33)의 상기 또 다른 구역은 상기 제2 도전 타입의 매립 영역이 없는 파워 IC. - 고전압 장치로서,

제1 도전 타입의 기판(31);

상기 기판(31)에 배치된 제2 도전 타입의 웰 영역(33) - 상기 웰 영역(33)은 구역들을 갖고, 상기 구역들 중 제1 구역은 상기 구역들 중 제2 구역에 수평 방향으로 인접하며, 상기 구역들 중 상기 제2 구역은 상기 구역들 중 제3 구역에 수평 방향으로 인접함 -;

상기 웰 영역(33)의 상기 구역들 중 상기 제1 구역에 배치된 상기 제2 도전 타입의 +영역들(36, 37);

상기 구역들 중 상기 제1 구역에 배치된 상기 제1 도전 타입의 하나 이상의 매립 영역(35) - 상기 구역들 중 상기 제1 구역에 배치된 상기 하나 이상의 매립 영역(35)은 복수의 도전 채널을 정의하고, 상기 +영역들(36, 37)은 각각 상기 구역들 중 상기 제1 구역에 배치된 상기 하나 이상의 매립 영역(35)으로부터 수평 방향으로 분리되며, 상기 +영역들(36, 37) 중 제1 +영역(37)은 상기 도전 채널들의 일단에 배치되고, 상기 +영역들(36, 37) 중 제2 +영역(36)은 상기 도전 채널들의 반대 단부에 배치됨 -;

상기 웰 영역(33)의 상기 구역들 중 상기 제3 구역에 배치되는 상기 제1 도전 타입의 하나 이상의 다른 매립 영역;

상기 웰 영역(33)의 상기 구역들 중 적어도 상기 제2 구역 상에 형성된 유전층(38);

상기 구역들 중 상기 제2 구역의 바로 위의 상기 유전층(38) 상에 형성된 레지스터층(39) - 상기 레지스터층(39)은 제1 단부 및 제2 단부를 가짐 -;

상기 레지스터층(39)의 상기 제1 단부 및 제2 단부에 각각 전기적으로 연결된 제1 전극(41) 및 제2 전극(42) - 상기 제2 전극(42)은 상기 +영역들(36, 37) 중 상기 제2 +영역(36)에 전기적으로 연결됨 -;

상기 +영역들(36, 37) 중 상기 제1 +영역(37)에 전기적으로 연결된 탭 전극(43); 및

상기 기판(31)과, 상기 하나 이상의 매립 영역(35) 및 다른 매립 영역(34)에 전기적으로 연결된 제4 전극 - 상기 탭 전극(43)에 공급되는 전압은 상기 제1 전극(41)과 제4 전극 사이의 전압차가 상기 고전압 장치의 핀치-오프 전압보다 작을 때 그 전압차에 실질적으로 비례하고, 상기 탭 전극(43)에 공급되는 전압은 상기 전압차가 핀치-오프 전압보다 클 때 실질적으로 일정하며, 상기 제2 전극(42)은 상기 전압차가 핀치-오프 전압보다 클 때 상기 전압차와 실질적으로 동일한 전압 전위로 되어 있음 -

을 포함하는 고전압 장치. - 제18항에 있어서,

상기 구역들 중 상기 제1 구역에 배치된 상기 하나 이상의 매립 영역(35)은 수직 방향으로 이격된 복수의 매립 영역을 포함하는 고전압 장치. - 제18항에 있어서,

상기 하나 이상의 다른 매립 영역(34)은 수직 방향으로 이격된 복수의 매립 영역을 포함하는 고전압 장치. - 제18항에 있어서,

상기 웰 영역(33)의 상기 구역들 중 상기 제2 구역은 상기 제2 도전 타입의 매립 영역이 없는 고전압 장치. - 파워 집적 회로(IC)로서,

외부 전압을 수용하는 핀에 연결된 드레인을 갖는 출력 트랜지스터(11);

상기 출력 트랜지스터(11)를 구동하는 제어 회로; 및

트랜지스터 소자

를 포함하고,

상기 트랜지스터 소자는,

제1 도전 타입의 웰 영역(33)에 형성된 접합 전계-효과 트랜지스터(JFET; Junction Field-Effect Transistor) - 상기 웰 영역(33)은 제2 도전 타입의 기판(31)에 배치되고, 상기 JFET는 상기 웰 영역(33)에 배치된 제1 도전 타입의 +영역들(36, 37)을 가지며, 상기 +영역들(36, 37)은 상기 제2 도전 타입의 하나 이상의 매립 영역(35)에 의해 정의되는 복수의 도전 채널에 의해 분리됨 -;

상기 웰 영역(33) 위에 배치된 유전층(38) 상에 레지스터(39)를 형성하는 물질층 - 상기 레지스터(39)는 제1 단부 및 제2 단부를 갖고, 상기 제2 단부는 상기 JFET의 상기 +영역들(36, 37) 중 제1 +영역(36)에 전기적으로 연결됨 -; 및

상기 레지스터(39)의 상기 제1 단부와 상기 출력 트랜지스터(11)의 드레인에 전기적으로 연결된 제1 전극(41), 상기 JFET의 상기 +영역들 중 제2 +영역(37)과 상기 제어 회로에 전기적으로 연결된 탭 전극(43), 및 상기 기판(31)과 또한 상기 매립 영역들(35)에 전기적으로 연결된 제3 전극

을 포함하고,

상기 탭 전극(43)에 공급되는 내부 전압은 상기 제3 전극이 접지되고 상기 외부 전압이 상기 JFET의 핀치-오프 전압보다 작을 때 상기 외부 전압에 실질적으로 비례하고, 상기 탭 전극(43)에 공급되는 내부 전압은 상기 제3 전극이 접지되고 상기 외부 전압이 상기 핀치-오프 전압보다 클 때 실질적으로 일정하며, 상기 레지스터(39)의 제2 단부는 상기 외부 전압이 상기 핀치-오프 전압보다 크고 상기 제3 전극이 접지될 때 실질적으로 상기 외부 전압으로 되어 있는 파워 IC. - 제22항에 있어서,

상기 출력 트랜지스터(11)는 수직 고전압 전계 효과 트랜지스터를 포함하는 파워 IC. - 제22항에 있어서,

상기 유전층(38)은 이산화규소를 포함하는 파워 IC. - 제22항에 있어서,

상기 물질층은 폴리실리콘을 포함하는 파워 IC. - 제22항에 있어서,

상기 레지스터(39)는 상기 JFET의 상기 +영역들(36, 37) 중 상기 제1 영역(36)에 수평 방향으로 인접하는 상기 웰 영역(33)의 한 구역 상에 형성되고, 상기 한 구역은 상기 제2 도전 타입의 매립 영역이 없는 파워 IC. - 제26항에 있어서,

상기 웰 영역(33)의 다른 구역에 배치된 상기 제2 도전 타입의 하나 이상의 추가 매립 영역을 더 포함하고, 상기 다른 구역은 상기 한 구역에 수평 방향으로 인접하고 상기 한 구역에 의해 상기 +영역들(36, 37) 중 제1 +영역(36)으로부터 분리되는 파워 IC.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US12/583,426 US8129815B2 (en) | 2009-08-20 | 2009-08-20 | High-voltage transistor device with integrated resistor |

| US12/583,426 | 2009-08-20 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020110136721A Division KR20120002963A (ko) | 2009-08-20 | 2011-12-16 | 집적 레지스터를 가진 고전압 트랜지스터 장치 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20110019710A KR20110019710A (ko) | 2011-02-28 |

| KR101157759B1 true KR101157759B1 (ko) | 2012-06-25 |

Family

ID=43604619

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020100079694A KR101157759B1 (ko) | 2009-08-20 | 2010-08-18 | 집적 레지스터를 가진 고전압 트랜지스터 장치 |

| KR1020110136721A KR20120002963A (ko) | 2009-08-20 | 2011-12-16 | 집적 레지스터를 가진 고전압 트랜지스터 장치 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020110136721A KR20120002963A (ko) | 2009-08-20 | 2011-12-16 | 집적 레지스터를 가진 고전압 트랜지스터 장치 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US8129815B2 (ko) |

| KR (2) | KR101157759B1 (ko) |

| CN (2) | CN103094279A (ko) |

| TW (1) | TW201123450A (ko) |

Families Citing this family (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102668347B (zh) | 2009-12-23 | 2015-12-02 | 马维尔国际贸易有限公司 | 启动电源 |

| KR101312268B1 (ko) | 2010-12-24 | 2013-09-25 | 주식회사 케이티 | 클라우드 컴퓨팅 환경에서 게임 서비스 제공 방법, 클라우드 컴퓨팅 서버, 및 클라우드 컴퓨팅 시스템 |

| US8742735B2 (en) | 2011-05-16 | 2014-06-03 | Marvell World Trade Ltd. | High-voltage startup circuit |

| JP6109817B2 (ja) | 2011-05-16 | 2017-04-05 | マーベル ワールド トレード リミテッド | 高電圧スタートアップ回路を用いたシステムおよび方法 |

| US20120313692A1 (en) * | 2011-06-08 | 2012-12-13 | Sehat Sutardja | Super-high-voltage resistor on silicon |

| CN103094319B (zh) * | 2011-11-04 | 2015-10-14 | 上海华虹宏力半导体制造有限公司 | 双通道高压结型场效应管降低夹断电压的结构及制造方法 |

| CN103094124B (zh) * | 2011-11-04 | 2015-08-19 | 上海华虹宏力半导体制造有限公司 | 高压结型场效应管的结构及制造方法 |

| CN103367414B (zh) * | 2012-04-09 | 2015-10-14 | 上海华虹宏力半导体制造有限公司 | 纵向夹断的面结型场效应晶体管结构及制造方法 |

| US9024365B2 (en) * | 2012-09-10 | 2015-05-05 | Macronix International Co., Ltd. | High voltage junction field effect transistor and manufacturing method thereof |

| CN103681876B (zh) * | 2012-09-11 | 2016-04-27 | 旺宏电子股份有限公司 | 高压结场效晶体管 |

| US8963277B2 (en) * | 2013-03-13 | 2015-02-24 | Macronix International Co., Ltd. | Semiconductor structure and method of manufacturing the same |

| KR101975630B1 (ko) | 2015-04-03 | 2019-08-29 | 매그나칩 반도체 유한회사 | 접합 트랜지스터와 고전압 트랜지스터 구조를 포함한 반도체 소자 및 그 제조 방법 |

| US10784372B2 (en) | 2015-04-03 | 2020-09-22 | Magnachip Semiconductor, Ltd. | Semiconductor device with high voltage field effect transistor and junction field effect transistor |

| JP6849695B2 (ja) | 2016-04-08 | 2021-03-24 | パワー・インテグレーションズ・インコーポレーテッド | 半導体デバイスのための集積抵抗器 |

| US10297661B2 (en) | 2017-06-30 | 2019-05-21 | Taiwan Semiconductor Manufacturing Co., Ltd. | High voltage resistor device |

| TWI641132B (zh) * | 2017-08-29 | 2018-11-11 | 新唐科技股份有限公司 | 半導體裝置及其製造方法 |

| CN108493241B (zh) * | 2018-05-31 | 2020-09-29 | 电子科技大学 | 一种具有内置jfet结构的igbt器件 |

| CN108493242B (zh) * | 2018-05-31 | 2020-08-28 | 电子科技大学 | 一种优化体内电场的载流子增强型igbt器件 |

| CN108766998B (zh) * | 2018-05-31 | 2020-12-29 | 电子科技大学 | 一种具有凹槽栅型jfet结构的igbt器件 |

| JP7099158B2 (ja) * | 2018-08-09 | 2022-07-12 | 富士電機株式会社 | 模擬素子及び抵抗素子の不良検査方法 |

| CN114267717B (zh) * | 2021-11-19 | 2024-03-01 | 深圳深爱半导体股份有限公司 | 半导体器件及其制备方法 |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004357496A (ja) | 2003-05-27 | 2004-12-16 | Power Integrations Inc | タップ・エレメントを備えた電子回路制御エレメント |

Family Cites Families (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5282107A (en) | 1992-09-01 | 1994-01-25 | Power Integrations, Inc. | Power MOSFET safe operating area current limiting device |

| US5285369A (en) | 1992-09-01 | 1994-02-08 | Power Integrations, Inc. | Switched mode power supply integrated circuit with start-up self-biasing |

| US5977763A (en) | 1996-02-27 | 1999-11-02 | Micron Technology, Inc. | Circuit and method for measuring and forcing an internal voltage of an integrated circuit |

| KR100504433B1 (ko) | 1999-01-09 | 2005-07-29 | 주식회사 하이닉스반도체 | 앤티퓨즈를 이용한 메모리소자의 리페어 회로 |

| US6266291B1 (en) | 1999-02-23 | 2001-07-24 | Micron Technology, Inc. | Voltage independent fuse circuit and method |

| US6388853B1 (en) | 1999-09-28 | 2002-05-14 | Power Integrations, Inc. | Method and apparatus providing final test and trimming for a power supply controller |

| US6630724B1 (en) | 2000-08-31 | 2003-10-07 | Micron Technology, Inc. | Gate dielectric antifuse circuits and methods for operating same |

| US6468847B1 (en) * | 2000-11-27 | 2002-10-22 | Power Integrations, Inc. | Method of fabricating a high-voltage transistor |

| US6424007B1 (en) * | 2001-01-24 | 2002-07-23 | Power Integrations, Inc. | High-voltage transistor with buried conduction layer |

| US6640435B2 (en) | 2001-02-20 | 2003-11-04 | Power Integrations, Inc. | Methods for trimming electrical parameters in an electrical circuit |

| US6555873B2 (en) | 2001-09-07 | 2003-04-29 | Power Integrations, Inc. | High-voltage lateral transistor with a multi-layered extended drain structure |

| US7221011B2 (en) | 2001-09-07 | 2007-05-22 | Power Integrations, Inc. | High-voltage vertical transistor with a multi-gradient drain doping profile |

| US6635544B2 (en) | 2001-09-07 | 2003-10-21 | Power Intergrations, Inc. | Method of fabricating a high-voltage transistor with a multi-layered extended drain structure |

| FR2838233A1 (fr) | 2002-04-04 | 2003-10-10 | St Microelectronics Sa | Procede de programmation de cellules memoire par claquage d'elements antifusible |

| US6693481B1 (en) | 2002-08-20 | 2004-02-17 | Intel Corporation | Fuse circuit utilizing high voltage transistors |

| US6855985B2 (en) * | 2002-09-29 | 2005-02-15 | Advanced Analogic Technologies, Inc. | Modular bipolar-CMOS-DMOS analog integrated circuit & power transistor technology |

| US7638841B2 (en) * | 2003-05-20 | 2009-12-29 | Fairchild Semiconductor Corporation | Power semiconductor devices and methods of manufacture |

| US7002398B2 (en) | 2004-07-08 | 2006-02-21 | Power Integrations, Inc. | Method and apparatus for controlling a circuit with a high voltage sense device |

| US7102951B2 (en) | 2004-11-01 | 2006-09-05 | Intel Corporation | OTP antifuse cell and cell array |

| US7268577B2 (en) | 2004-12-17 | 2007-09-11 | International Business Machines Corporation | Changing chip function based on fuse states |

| KR101146972B1 (ko) * | 2005-03-16 | 2012-05-22 | 페어차일드코리아반도체 주식회사 | 고내압 다이오드를 갖는 고전압 집적회로 장치 |

| CN2836242Y (zh) * | 2005-10-14 | 2006-11-08 | 西安电子科技大学 | 可集成的高压vdmos晶体管结构 |

| KR20100079705A (ko) * | 2008-12-31 | 2010-07-08 | 주식회사 동부하이텍 | 수평형 디모스 소자 |

| US8207580B2 (en) * | 2009-05-29 | 2012-06-26 | Power Integrations, Inc. | Power integrated circuit device with incorporated sense FET |

| US8164125B2 (en) * | 2010-05-07 | 2012-04-24 | Power Integrations, Inc. | Integrated transistor and anti-fuse as programming element for a high-voltage integrated circuit |

| US7932738B1 (en) | 2010-05-07 | 2011-04-26 | Power Integrations, Inc. | Method and apparatus for reading a programmable anti-fuse element in a high-voltage integrated circuit |

| US8854065B2 (en) | 2012-01-13 | 2014-10-07 | Infineon Technologies Austria Ag | Current measurement in a power transistor |

-

2009

- 2009-08-20 US US12/583,426 patent/US8129815B2/en active Active

-

2010

- 2010-08-18 KR KR1020100079694A patent/KR101157759B1/ko not_active IP Right Cessation

- 2010-08-19 TW TW099127649A patent/TW201123450A/zh unknown

- 2010-08-20 CN CN2013100098842A patent/CN103094279A/zh active Pending

- 2010-08-20 CN CN2010102631109A patent/CN101997020B/zh not_active Expired - Fee Related

-

2011

- 2011-12-16 KR KR1020110136721A patent/KR20120002963A/ko not_active Application Discontinuation

-

2012

- 2012-02-10 US US13/385,264 patent/US8866201B2/en not_active Expired - Fee Related

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004357496A (ja) | 2003-05-27 | 2004-12-16 | Power Integrations Inc | タップ・エレメントを備えた電子回路制御エレメント |

Also Published As

| Publication number | Publication date |

|---|---|

| US8866201B2 (en) | 2014-10-21 |

| KR20120002963A (ko) | 2012-01-09 |

| KR20110019710A (ko) | 2011-02-28 |

| US20120146105A1 (en) | 2012-06-14 |

| CN103094279A (zh) | 2013-05-08 |

| CN101997020B (zh) | 2013-01-02 |

| CN101997020A (zh) | 2011-03-30 |

| TW201123450A (en) | 2011-07-01 |

| US20110042726A1 (en) | 2011-02-24 |

| US8129815B2 (en) | 2012-03-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101157759B1 (ko) | 집적 레지스터를 가진 고전압 트랜지스터 장치 | |

| US10229993B2 (en) | LDMOS transistors including resurf layers and stepped-gates, and associated systems and methods | |

| EP0788660B1 (en) | Semiconductor device of hv-ldmost type | |

| US8174070B2 (en) | Dual channel trench LDMOS transistors and BCD process with deep trench isolation | |

| EP1256985B1 (en) | Lateral power MISFET | |

| US9768160B2 (en) | Semiconductor device, electronic circuit and method for switching high voltages | |

| CN1667838B (zh) | 具有改进的开态电阻性能的横向绝缘栅fet结构 | |

| US7982248B2 (en) | Junction field effect transistor, integrated circuit for switching power supply, and switching power supply | |

| US9190535B2 (en) | Bootstrap MOS for high voltage applications | |

| CN110176488B (zh) | 具有击穿电压钳位的ldmos晶体管 | |

| TWI548029B (zh) | 半導體元件及其操作方法以及抑制漏電的結構 | |

| US20110115019A1 (en) | Cmos compatible low gate charge lateral mosfet | |

| EP2924723B1 (en) | Integrated circuit | |

| JP4971848B2 (ja) | 低スイッチング損失、低ノイズを両立するパワーmos回路 | |

| JP2007134588A (ja) | 半導体装置 | |

| CN108257950B (zh) | 高压集成电路的高电压终端结构 | |

| KR101297440B1 (ko) | Pn접합 및 모스 커패시터 하이브리드 리설프 트랜지스터 | |

| US7714407B2 (en) | Semiconductor device and method of forming a semiconductor device | |

| JP2004031519A (ja) | 半導体装置 | |

| US20090206402A1 (en) | Lateral Trench MOSFET with Bi-Directional Voltage Blocking | |

| US11677033B2 (en) | Passive element on a semiconductor base body | |

| US20180286860A1 (en) | Cmos compatible low gate charge high voltage pmos | |

| US20230246068A1 (en) | Field effect transistor having a dielectric structure |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| A107 | Divisional application of patent | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20150527 Year of fee payment: 4 |

|

| LAPS | Lapse due to unpaid annual fee |