KR101076794B1 - Method of fabricating semiconductor device - Google Patents

Method of fabricating semiconductor device Download PDFInfo

- Publication number

- KR101076794B1 KR101076794B1 KR1020100007469A KR20100007469A KR101076794B1 KR 101076794 B1 KR101076794 B1 KR 101076794B1 KR 1020100007469 A KR1020100007469 A KR 1020100007469A KR 20100007469 A KR20100007469 A KR 20100007469A KR 101076794 B1 KR101076794 B1 KR 101076794B1

- Authority

- KR

- South Korea

- Prior art keywords

- pattern

- hard mask

- forming

- layer

- pad

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 27

- 238000004519 manufacturing process Methods 0.000 title description 2

- 238000000034 method Methods 0.000 claims abstract description 53

- 229920002120 photoresistant polymer Polymers 0.000 claims abstract description 25

- 238000005530 etching Methods 0.000 claims abstract description 22

- 125000006850 spacer group Chemical group 0.000 claims abstract description 20

- 238000005520 cutting process Methods 0.000 claims description 8

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 4

- 238000000151 deposition Methods 0.000 claims description 4

- 229910052710 silicon Inorganic materials 0.000 claims description 4

- 239000010703 silicon Substances 0.000 claims description 4

- 229910003481 amorphous carbon Inorganic materials 0.000 claims description 3

- 238000000206 photolithography Methods 0.000 abstract description 9

- 238000000059 patterning Methods 0.000 description 6

- 239000000463 material Substances 0.000 description 5

- 230000000694 effects Effects 0.000 description 3

- 238000001459 lithography Methods 0.000 description 3

- BPQQTUXANYXVAA-UHFFFAOYSA-N Orthosilicate Chemical compound [O-][Si]([O-])([O-])[O-] BPQQTUXANYXVAA-UHFFFAOYSA-N 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 238000004088 simulation Methods 0.000 description 2

- 239000000758 substrate Substances 0.000 description 2

- 238000007796 conventional method Methods 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 239000011295 pitch Substances 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31144—Etching the insulating layers by chemical or physical means using masks

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/70—Microphotolithographic exposure; Apparatus therefor

- G03F7/70425—Imaging strategies, e.g. for increasing throughput or resolution, printing product fields larger than the image field or compensating lithography- or non-lithography errors, e.g. proximity correction, mix-and-match, stitching or double patterning

- G03F7/70433—Layout for increasing efficiency or for compensating imaging errors, e.g. layout of exposure fields for reducing focus errors; Use of mask features for increasing efficiency or for compensating imaging errors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/027—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34

- H01L21/033—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers

- H01L21/0334—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane

- H01L21/0337—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane characterised by the process involved to create the mask, e.g. lift-off masks, sidewalls, or to modify the mask, e.g. pre-treatment, post-treatment

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/027—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34

- H01L21/033—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers

- H01L21/0334—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane

- H01L21/0338—Process specially adapted to improve the resolution of the mask

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3205—Deposition of non-insulating-, e.g. conductive- or resistive-, layers on insulating layers; After-treatment of these layers

- H01L21/321—After treatment

- H01L21/3213—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer

- H01L21/32139—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer using masks

Landscapes

- Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Inorganic Chemistry (AREA)

- Chemical & Material Sciences (AREA)

- Semiconductor Memories (AREA)

- Photosensitive Polymer And Photoresist Processing (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

본 발명은 반도체 소자의 형성방법에 관한 것으로, 특히 셀 패턴의 선폭이 주위 환경의 영향을 덜 받도록 하여 포토 리소그래피 공정의 마진을 향상시키는 반도체 소자의 형성방법에 관한 것이다.

본 발명의 반도체 소자의 형성방법은, 피식각층 상부에 하드마스크층 및 감광막을 형성하는 단계, 상기 감광막이 패드 패턴, 상기 패드 패턴과 연결된 라인 패턴 및 패드 패턴의 중심에 위치하는 더미 패턴을 포함하도록 노광 및 현상하는 단계, 상기 패드 패턴, 라인 패턴 및 더미 패턴을 포함하는 감광막 패턴 측벽에 스페이서를 형성하는 단계, 상기 스페이서를 마스크로 하드마스크층을 식각하여 하드마스크 패턴을 형성하는 단계 및 상기 하드마스크 패턴을 마스크로 상기 피식각층을 식각하여 피식각층 패턴을 형성하는 단계를 포함하는 것을 특징으로 한다.BACKGROUND OF THE INVENTION 1. Field of the Invention The present invention relates to a method of forming a semiconductor device, and more particularly, to a method of forming a semiconductor device in which the line width of a cell pattern is less affected by the surrounding environment, thereby improving the margin of the photolithography process.

The method of forming a semiconductor device of the present invention may include forming a hard mask layer and a photoresist layer on an etched layer, wherein the photoresist includes a pad pattern, a line pattern connected to the pad pattern, and a dummy pattern positioned at the center of the pad pattern. Exposing and developing, forming a spacer on a photoresist pattern sidewall including the pad pattern, a line pattern, and a dummy pattern, forming a hard mask pattern by etching the hard mask layer using the spacer as a mask, and the hard mask. And etching the etched layer using a pattern as a mask to form an etched layer pattern.

Description

본 발명은 반도체 소자의 형성방법에 관한 것이다. 보다 상세하게는 SPT 공정이 적용되는 각종 반도체 소자의 형성방법에 관한 것이다.The present invention relates to a method of forming a semiconductor device. More specifically, the present invention relates to a method of forming various semiconductor devices to which the SPT process is applied.

최근 반도체 소자의 미세화 및 고집적화가 진행됨에 따라 메모리 용량의 증가에 비례하여 전체적인 칩(chip) 면적은 증가되고 있지만 실제로 반도체 소자의 패턴이 형성되는 셀(cell) 영역의 면적은 감소되고 있다. 따라서 원하는 메모리 용량을 확보하기 위해서는 한정된 셀 영역 내에 보다 많은 패턴이 형성되어야만 하므로, 패턴의 선폭(critical dimension)은 감소되면서 점점 미세해 지고 있다. 이와 같이 선폭이 미세한 패턴을 형성하기 위해서 리소그래피 공정(Lithography Process)의 발전이 요구된다.In recent years, as semiconductor devices become more compact and have higher integration, the overall chip area is increased in proportion to the increase in memory capacity, but the area of the cell area in which the pattern of the semiconductor device is formed is decreasing. Therefore, in order to secure a desired memory capacity, more patterns have to be formed in a limited cell area, and thus, the critical dimension of the pattern is getting smaller and smaller. In order to form a pattern having a fine line width, the development of a lithography process is required.

리소그래피 공정이란, 기판 상부에 감광막(photoresist)을 도포하고, 365㎚, 248㎚, 193㎚ 및 153㎚ 등의 파장 길이를 가지는 광원을 이용하여 미세 패턴이 정의된 노광 마스크를 사용하여 감광막에 노광 공정을 수행한 다음, 현상(development) 공정을 수행하여 미세 패턴을 정의하는 감광막 패턴을 형성하는 공정이다.A lithography process is a photoresist applied to an upper part of a board | substrate, and it exposes to a photosensitive film using the exposure mask in which the micro pattern was defined using the light source which has wavelength lengths, such as 365 nm, 248 nm, 193 nm, and 153 nm. After the process, a development process is performed to form a photoresist pattern defining a fine pattern.

이와 같은 리소그래피 공정은 R = k1×λ / NA와 같이 광원의 파장(λ)과 개구수(Numerical Aperture : NA)에 따라 그 해상도(R)가 정해진다. 위 식에서 k1은 공정 상수를 의미하는데, 이는 물리적인 한계를 가지므로 통상적인 방법으로 그 값을 감소시키는 것을 거의 불가능하며, 단파장을 이용하는 노광 장치와 함께 상기 단파장에 대해 반응성이 높은 감광막 물질을 새로 개발해야 하므로, 단파장 이하의 선폭을 갖는 미세 패턴을 형성하는 것이 어렵다.In such a lithography process, the resolution R is determined according to the wavelength λ and the numerical aperture NA of the light source, such as R = k1 × λ / NA. In the above equation, k1 means a process constant, which has a physical limit, so it is almost impossible to reduce the value by a conventional method, and newly developed a photoresist material which is highly reactive to the short wavelength together with an exposure apparatus using the short wavelength. Since it is necessary, it is difficult to form a fine pattern having a line width of short wavelength or less.

따라서 노광 장치의 공정 능력을 고려한 패턴을 이중으로 중첩시킴으로써 노광 장치나 노광 조건의 변경 없이 미세한 패턴이 형성될 수 있도록 하는 더블 패터닝 공정(Double Patterning Technology; 이하 'DPT'라 한다)이 개발되었다. 나아가 이 더블 패터닝 공정과 유사하나 이중 노광이나 이중 패터닝이 필요 없는 스페이서 패터닝 공정(Spacer Patterning Technology; 이하 ‘SPT'라 한다)이 개발되어 연구되고 있는 실정이다.Therefore, a double patterning process (hereinafter, referred to as 'DPT') has been developed in which a fine pattern can be formed without changing the exposure apparatus or exposure conditions by overlapping a pattern considering the process capability of the exposure apparatus. Furthermore, a Spacer Patterning Technology (hereinafter referred to as 'SPT'), which is similar to the double patterning process but does not require double exposure or double patterning, has been developed and studied.

SPT 공정이란 두 피치(pitch) 당 하나의 패턴을 형성한 후 그 패턴의 측벽에 스페이서(spacer)를 형성하면, 한 패턴의 측벽에 두 개의 스페이서가 형성되는 원리를 이용한 공정이다. 이 스페이서를 마스크로 사용하게 되면 1회의 노광 공정만으로 선폭이 미세한 패턴을 형성할 수 있게 된다.The SPT process is a process using a principle of forming two spacers on one sidewall of a pattern after forming one pattern per two pitches and then forming a spacer on the sidewall of the pattern. When the spacer is used as a mask, a pattern having a fine line width can be formed by only one exposure process.

도 1은 종래 반도체 소자 중 플래시 메모리 공정에서 SPT 공정이 사용되는 X-decoder 영역을 촬영한 SEM 사진으로, 다수의 패드 패턴(10)과 라인 패턴(20)이 연결되어 형성되어 있다. 이와 같이 패턴 구조가 복잡한 패턴은 SPT 공정으로 구현하기도 용이하지 않고, 면적이 넓은 패드 패턴(10) 때문에 그 주변의 포토리소그래피 공정 마진이 매우 적다.FIG. 1 is a SEM photograph of an X-decoder region in which a SPT process is used in a flash memory process of a conventional semiconductor device. A plurality of

이 결과 도 1의 ‘A'로 표시된 바와 같이 일부 패드 패턴(10)이 예정보다 넓게 형성되면서 인접한 라인 패턴(20)과 접속되어 버리는 브릿지(bridge) 현상이 발생하는 문제점이 있다.As a result, as indicated by 'A' in FIG. 1, there is a problem in that a bridge phenomenon in which some

본 발명은 상기한 바와 같은 종래의 문제점을 해결하기 위한 것으로, 패드 패턴과 라인 패턴을 포함하는 반도체 소자에서 패드 패턴 중심에 더미 패턴을 형성함으로써, 셀 패턴의 선폭이 주위 환경의 영향을 덜 받도록 하여 포토 리소그래피 공정의 마진을 향상시키는 반도체 소자의 형성방법을 제공하는 것을 목적으로 한다.The present invention is to solve the conventional problems as described above, by forming a dummy pattern in the center of the pad pattern in the semiconductor device including the pad pattern and the line pattern, so that the line width of the cell pattern is less affected by the surrounding environment It is an object of the present invention to provide a method for forming a semiconductor device that improves the margin of a photolithography process.

상기 목적을 달성하기 위해, 본 발명은 피식각층 상부에 하드마스크층 및 감광막을 형성하는 단계, 상기 감광막이 패드 패턴, 상기 패드 패턴과 연결된 라인 패턴 및 패드 패턴의 중심에 위치하는 더미 패턴을 포함하도록 노광 및 현상하는 단계, 상기 패드 패턴, 라인 패턴 및 더미 패턴을 포함하는 감광막 패턴 측벽에 스페이서를 형성하는 단계, 상기 스페이서를 마스크로 하드마스크층을 식각하여 하드마스크 패턴을 형성하는 단계 및 상기 하드마스크 패턴을 마스크로 상기 피식각층을 식각하여 피식각층 패턴을 형성하는 단계를 포함하여, 셀 패턴의 선폭이 주위 환경의 영향을 덜 받도록 하여 포토 리소그래피 공정의 마진을 향상시키는 것을 특징으로 한다.In order to achieve the above object, the present invention provides a method for forming a hard mask layer and a photoresist layer on an etched layer, wherein the photoresist includes a pad pattern, a line pattern connected to the pad pattern, and a dummy pattern positioned at the center of the pad pattern. Exposing and developing, forming a spacer on a photoresist pattern sidewall including the pad pattern, a line pattern, and a dummy pattern, forming a hard mask pattern by etching the hard mask layer using the spacer as a mask, and the hard mask. And etching the etched layer using a pattern as a mask to form an etched layer pattern, so that the line width of the cell pattern is less affected by the surrounding environment, thereby improving the margin of the photolithography process.

나아가 상기 하드마스크층을 형성하는 단계는, 피식각층 상부에 산화막을 형성하는 단계, 상기 산화막 상부에 비정질 탄소를 포함하는 제 1 하드마스크층을 형성하는 단계 및 상기 제 1 하드마스크층의 상부에 실리콘 산화질화막을 포함하여, 인접한 물질층 간 식각선택비 차이를 두는 것을 특징으로 한다.Further, the forming of the hard mask layer may include forming an oxide film on the etched layer, forming a first hard mask layer including amorphous carbon on the oxide film, and silicon on the first hard mask layer. Including an oxynitride film, the etching selectivity difference between the adjacent material layer is characterized in that the.

또한 상기 산화막은 TEOS(tetraethly orthosilicate)를 포함하여 형성되는 것이 바람직하다.In addition, the oxide film is preferably formed to include tetraethly orthosilicate (TEOS).

아울러 상기 하드마스크층을 식각하는 단계는, 상기 스페이서를 마스크로 상기 제 2 하드마스크층을 식각하여 제 2 하드마스크 패턴을 형성하는 단계, 상기 제 2 하드마스크 패턴을 마스크로 상기 제 1 하드마스크층을 식각하여 제 1 하드마스크 패턴을 형성하는 단계 및 상기 제 1 하드마스크 패턴을 마스크로 상기 산화막을 식각하여 산화막 패턴을 형성하는 단계를 포함하는 것을 특징으로 한다.The etching of the hard mask layer may include forming a second hard mask pattern by etching the second hard mask layer using the spacer as a mask and the first hard mask layer using the second hard mask pattern as a mask. Etching to form a first hard mask pattern, and etching the oxide layer using the first hard mask pattern as a mask to form an oxide layer pattern.

그리고 상기 제 1 하드마스크 패턴을 형성하는 단계 후, 상기 제 1 하드마스크 패턴의 상부에 패드 마스크를 형성하는 단계를 더 포함하여, 패드 형상의 패턴을 형성하는 것을 특징으로 한다.And after forming the first hard mask pattern, further comprising forming a pad mask on the first hard mask pattern to form a pad-shaped pattern.

나아가 상기 패드 마스크를 형성하는 단계는 트랜지스터 마스크를 형성하는 단계와 동시에 이루어짐으로써, 기존 공정에 포토 리소그래피 공정이 추가되지 않는 것을 특징으로 한다.Furthermore, the forming of the pad mask is performed at the same time as forming the transistor mask, so that a photolithography process is not added to the existing process.

또한 상기 산화막 패턴은 패드 형상의 산화막 패턴, 라인 형상의 산화막 패턴, 및 상기 패드 형상의 산화막 패턴들을 연결하는 라인 형상의 패턴을 포함하는 것이 바람직하다.In addition, the oxide film pattern may include a pad-shaped oxide film pattern, a line-shaped oxide film pattern, and a line-shaped pattern connecting the pad-shaped oxide film patterns.

아울러 상기 산화막 패턴 중 상기 패드 형상의 산화막 패턴을 연결하는 라인 형상의 산화막 패턴을 식각하여 제거함으로써, 각 패드 형상의 산화막 패턴을 분리하는 단계를 더 포함하는 것을 특징으로 한다.The method may further include separating each pad-shaped oxide film pattern by etching and removing a line-shaped oxide film pattern connecting the pad-shaped oxide film pattern among the oxide film patterns.

그리고 상기 패드 형상의 산화막 패턴을 분리하는 단계는, 상기 패드 형상의 산화막 패턴을 연결하는 라인 형상의 산화막 패턴을 노출시키는 커팅 마스크를 형성하는 단계 및 상기 커팅 마스크로 상기 산화막 패턴을 식각하는 단계를 포함하는 것이 바람직하다.The separating of the pad-shaped oxide pattern may include forming a cutting mask exposing a line-shaped oxide pattern connecting the pad-shaped oxide pattern and etching the oxide pattern with the cutting mask. It is desirable to.

나아가 상기 스페이서를 형성하는 단계는, 상기 감광막 패턴을 포함한 하드마스크층 상부에 ULTO(Ultra Low Temperature Oxide) 산화막을 증착하는 단계 및 상기 ULTO 산화막을 에치백으로 제거하면서, 상기 감광막 패턴의 측벽에만 ULTO 산화막을 잔류시키는 단계를 포함하는 것이 바람직하다.Further, the forming of the spacer may include depositing an ultra low temperature oxide (ULTO) oxide layer on the hard mask layer including the photoresist pattern, and removing the ULTO oxide layer with an etch back, and removing only the ULTO oxide layer on the sidewall of the photoresist pattern. It is preferred to include the step of remaining.

본 발명의 반도체 소자의 형성방법은 셀 패턴의 선폭이 주위 환경의 영향을 덜 받도록 하여 포토 리소그래피 공정의 마진을 향상시키는 효과를 제공한다.The method of forming a semiconductor device of the present invention provides an effect of improving the margin of the photolithography process by making the line width of the cell pattern less affected by the surrounding environment.

도 1은 종래 반도체 소자를 촬영한 SEM 사진;

도 2는 본 발명에 따르는 반도체 소자의 구조를 개략적으로 도시한 도면;

도 3 내지 도 10은 본 발명에 따르는 반도체 소자의 형성방법를 순차적으로 도시한 평면도 및 단면도; 그리고,

도 11은 본 발명에 따르는 반도체 소자 및 그 형성방법의 효과를 나타내는 실험 데이터이다.1 is a SEM photograph of a conventional semiconductor device;

2 schematically shows the structure of a semiconductor device according to the invention;

3 to 10 are plan and cross-sectional views sequentially illustrating a method of forming a semiconductor device according to the present invention; And,

11 is experimental data showing the effects of the semiconductor device and its formation method according to the present invention.

이하 첨부된 도면을 참조하여 본 발명에 따른 반도체 소자의 형성방법의 일실시예에 대해 상세히 설명하기로 한다.Hereinafter, an embodiment of a method of forming a semiconductor device according to the present invention will be described in detail with reference to the accompanying drawings.

도 2는 본 발명에 따르는 반도체 소자의 구조를 개략적으로 도시한 도면이다. 본 발명에 따르는 반도체 소자는 패드 패턴(10)과 라인 패턴(20)을 포함하는 반도체 소자에서 면적이 큰 패드 패턴(10)의 공정마진을 확보하기 위하여 패드 패턴(10)의 중심에 더미 패턴(15; dummy pattern)을 형성하는 것을 특징으로 한다.2 is a view schematically showing the structure of a semiconductor device according to the present invention. In the semiconductor device according to the present invention, in the semiconductor device including the

즉 면적이 큰 패드 패턴(10)의 중심 공간을 비워 두는 셈이 되며, 이 결과 후술할 바와 같이 더미 패턴(15)이 없는 종래기술에 비하여 포토리소그래피 공정 마진을 향상시킬 수 있고, 패드 패턴(10) 주위에서 발생하는 브릿지 현상을 방지할 수 있게 된다.That is, the center space of the

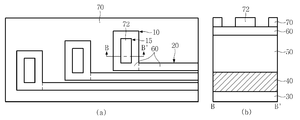

도 3 내지 도 10은 본 발명에 따르는 반도체 소자의 형성방법을 순차적으로 도시한 평면도 및 단면도이다. 도 3 내지 10에서 (a)는 평면도이고, (b)는 각 (a)에서 B-B′선을 따른 단면도이다.3 to 10 are plan and cross-sectional views sequentially illustrating a method of forming a semiconductor device according to the present invention. (A) is a top view in FIGS. 3-10, (b) is sectional drawing along the B-B 'line | wire in each (a).

먼저 도 3 (b)의 단면도를 참조하면, 피식각층(30), 산화막(40), 제 1 하드마스크층(50), 제 2 하드마스크층(60)을 순차적으로 형성한다. 여기서 피식각층(30)의 하부에는 실리콘 기판(Silicon substrate) 또는 소정의 반도체 소자들이 형성된 층이 존재할 수 있다. 피식각층(30)은 최종적인 패턴이 될 물질로서, 도전층인 폴리실리콘(poly silicon)층인 것이 바람직하다.First, referring to the cross-sectional view of FIG. 3B, the

산화막(40)과 제 1 및 제 2 하드마스크층(50, 60)은 피식각층(30)을 식각하기 위한 하드마스크(hard mask) 역할을 하는 층으로, 산화막(40)은 TEOS(tetraethly orthosilicate), 제 1 하드마스크층(50)은 비정질 탄소(amorphous carbon)층, 제 2 하드마스크층(60)는 실리콘 산화질화막(SiON)층을 포함하는 것이 바람직하다. 산화막(40) 내지 하드마스크층(50, 60)은 이러한 물질에 제한되지는 않고, 서로 인접한 상하부층 간 식각선택비가 서로 상이하여 한 층씩 식각하여 패터닝하는 것이 용이한 물질로 형성되면 족하다.The

그리고 제 2 하드마스크층(60)의 상부에 감광막(미도시)을 증착한 뒤, 소정 패턴이 미리 형성된 레티클(reticle)을 이용한 노광(expose) 및 현상(development) 공정을 통하여 감광막 패턴(70, 72)을 형성한다.After depositing a photoresist film (not shown) on the second

이 때 도 3 (a)의 평면도를 참조하면, 제 2 하드마스크층(60)의 상부에 감광막 패턴(70, 72)이 패드 패턴(10)과 라인 패턴(20)을 형성할 수 있도록 형성된다. 그리고 패드 패턴(10)의 중심부에는 더미 패턴(15)을 형성할 수 있는 감광막 패턴(72)이 형성된다.In this case, referring to the plan view of FIG. 3A,

다음으로 도 4를 참조하면, 감광막 패턴(70, 72)의 측벽에 스페이서(80)를 형성한다. 이 스페이서(80)는 산화막 재질이며 ULTO(Ultra Low Temperature Oxide)인 것이 바람직하다. 스페이서(80)를 형성하는 공정은, 감광막 패턴(70, 72)을 포함한 제 2 하드마스크층(60)의 상부에 산화막을 증착한 후 에치백 공정을 실시함으로써 감광막 패턴(70, 72)의 측벽에만 산화막을 잔류시키는 방식을 이용하는 것이 바람직하다.Next, referring to FIG. 4,

이후 도 5에 도시된 바와 같이, 감광막 패턴(70, 72)은 제거하고 스페이서(80)를 마스크로 제 2 하드마스크층(60)을 식각하여 제 2 하드마스크 패턴(65)을 형성한다.Subsequently, as shown in FIG. 5, the

다음으로 도 6에 도시된 바와 같이, 스페이서(80)를 먼저 제거한 후 제 2 하드마스크 패턴(65)을 마스크로 제 1 하드마스크층(50)을 식각하여, 제 1 하드마스크 패턴(55)을 형성한다.Next, as shown in FIG. 6, the

이후 도 7을 참조하면, 제 2 하드마스크 패턴(65)을 먼저 제거하고, 제 1 하드마스크 패턴(55)을 포함한 산화막(40)의 전면에 패드 마스크(74)를 형성한다. 이 패드 마스크(74)는 트랜지스터 마스크(76)를 형성하는 공정과 동시에 진행되어, 기존의 반도체 소자 제조공정에 추가적인 포토 리소그래피 공정이 불필요하도록 하는 것이 바람직하다.Subsequently, referring to FIG. 7, the second

다음으로 도 8에 도시된 바와 같이, 제 1 하드마스크 패턴(55) 및 패드 마스크(74)를 마스크로 산화막(40)을 식각하여, 산화막 패턴(45)을 형성한다. 이 산화막 패턴(45)은 패드 형상의 산화막 패턴(45a)과 라인 형상의 산화막 패턴(45b)을 포함하며, 패드 형상의 산화막 패턴(45a)들을 서로 연결하며 형성된 라인 형상의 산화막 패턴(45c) 및 트랜지스터 형상의 산화막 패턴(45d)도 포함한다. 이 중 라인 형상의 산화막 패턴(45c)은 도 9에 도시된 바와 같이 추후 제거되면서 패드 형상의 산화막 패턴(45a)들을 분리시키게 된다.Next, as shown in FIG. 8, the

이후 도 9를 참조하면, 패드 형상의 산화막 패턴(45a)을 분리시키기 위하여 산화막 패턴(45c)을 제거하기 위한 커팅 마스크(78; cutting mask)를 소정 패턴으로 형성한다. 이 커팅 마스크(78)는 감광막 패턴으로 포토리소그래피 공정에 의해 형성되는 것이 바람직하다.9, in order to separate the pad-shaped

마지막으로 도 10에 도시된 바와 같이, 커팅 마스크(78)를 마스크로 산화막 패턴(45) 중 일부의 산화막 패턴(45a)을 식각하여 제거함으로써 패드 형상의 산화막 패턴(45a)들을 분리시킨다. 이 결과 패드 형상의 산화막 패턴(45a), 라인 형상의 산화막 패턴(45b) 및 트랜지스터 형상의 산화막 패턴(45d)이 형성된다. 이후 도시하지 않았으나, 이들 산화막 패턴(45a, 45b, 45d)을 마스크로 피식각층(30)을 식각하여, 도 10에 도시된 산화막 패턴(45)과 동일한 형태의 피식각층 패턴(미도시)을 형성한다.Finally, as shown in FIG. 10, the pad pattern

도 11은 본 발명에 따르는 반도체 소자 및 그 형성방법의 효과를 나타내는 실험 데이터이다. 도 11에서 (a)는 더미 패턴이 없는 종래기술에 따른 패터닝의 시뮬레이션 결과이고, (b)는 더미 패턴이 있는 본 발명에 따른 패터닝의 시뮬레이션 결과이다. 그리고 (c)는 노광조건에 베스트 포커스(best focus)인 상태에서, 더미 패턴이 없는 종래기술과 더미 패턴이 있는 본 발명에서의 콘트라스트(contrast) 값을 측정한 데이터이고, (d)는 노광조건이 '-60 nm 디포커스(defocus)'인 상태에서 (c)와 동일하게 콘트라스트 값을 측정한 데이터이다.11 is experimental data showing the effects of the semiconductor device and its formation method according to the present invention. In FIG. 11, (a) shows a simulation result of patterning according to the prior art without a dummy pattern, and (b) shows a simulation result of patterning according to the present invention with a dummy pattern. And (c) is data obtained by measuring contrast values in the prior art without a dummy pattern and the present invention with a dummy pattern in a state where the exposure conditions are at the best focus, and (d) is an exposure condition. It is the data which measured the contrast value similarly to (c) in this "-60 nm defocus" state.

먼저 (a)와 (b)를 참조하면 종래기술인 (c)에서는 패드 패턴이 (d)에서의 패드 패턴보다 더 크게 형성되는 점을 확인할 수 있다. 그리고 (c) 및 (d)에서 본 발명 및 종래기술의 데이터는, 각각 (a)의 D-D′선을 따른 콘트라스트 값 및 (b)의 E-E′선을 따른 콘트라스트 값을 나타낸다.Referring first to (a) and (b) it can be seen that in the prior art (c), the pad pattern is formed larger than the pad pattern in (d). And in (c) and (d), the data of the present invention and the prior art represent contrast values along the line D-D 'of (a) and lines E-E' of (b), respectively.

도 11의 (c) 및 (d)를 참조하면, 본 발명에서는 (c)베스트 포커스일 경우와 (d)디포커스일 경우 모두 콘트라스트가 크게 차이가 나지 않음을 알 수 있다. 그러나 종래기술에서는 (c)베스트 포커스일 경우와 (d)디포커스일 경우 모두 좌측 영역에서 콘트라스트가 급격히 변화하는 모습을 나타낸다('C' 참조). 또한 (c) 및 (d)의 중심 영역(‘D’ 참조)에서의 콘트라스트 변화량도 종래기술에 비하여 본 발명이 더 적어 노광조건이 안정적이라는 결과를 나타낸다.Referring to (c) and (d) of FIG. 11, in the present invention, it can be seen that contrast is not significantly different in both (c) best focus and (d) defocus. However, in the prior art, in the case of (c) the best focus and (d) the defocus, the contrast rapidly changes in the left region (see 'C'). In addition, the amount of contrast change in the center region (see 'D') of (c) and (d) is smaller than that of the prior art, resulting in stable exposure conditions.

본 발명은 DRAM(Dynamic Random Access Memory), 플래시 메모리, PCRAM(Phase Change RAM) 등 SPT 공정이 적용될 수 있는 어떠한 반도체 소자에도 적용이 가능하며, 특히 플래시 메모리에서 게이트 엑스 디코더(Gate X-decoder) 영역에 직접 적용 가능한 발명이다.The present invention can be applied to any semiconductor device to which the SPT process can be applied, such as dynamic random access memory (DRAM), flash memory, and phase change RAM (PCRAM). In particular, the gate X-decoder region of the flash memory can be applied. The invention is applicable directly to.

본 발명은 기재된 실시예에 한정하는 것이 아니고, 본 발명의 사상 및 범위를 벗어나지 않는 한 다양하게 수정 및 변형을 할 수 있음은 당업자에게 자명하다고 할 수 있는 바, 그러한 변형예 또는 수정예들은 본 발명의 특허청구범위에 속하는 것이다.The present invention is not limited to the described embodiments, and various modifications and changes can be made to those skilled in the art without departing from the spirit and scope of the present invention. It belongs to the claims of the.

10 : 패드 패턴 15 : 더미 패턴

20 : 라인 패턴 30 : 피식각층

40 : 산화막 50 : 제 1 하드마스크

60 : 제 2 하드마스크 70 : 감광막

72 : 더미 감광막 74 : 패드 마스크

76 : 트랜지스터 마스크 78 : 커팅 마스크

80 : 스페이서10

20: line pattern 30: etched layer

40: oxide film 50: first hard mask

60: second hard mask 70: photosensitive film

72: dummy photosensitive film 74: pad mask

76: transistor mask 78: cutting mask

80: spacer

Claims (10)

상기 감광막이 패드 패턴, 상기 패드 패턴과 연결된 라인 패턴 및 패드 패턴의 중심에 위치하는 더미 패턴을 포함하도록 노광 및 현상하는 단계;

상기 패드 패턴, 라인 패턴 및 더미 패턴을 포함하는 감광막 패턴 측벽에 스페이서를 형성하는 단계;

상기 스페이서를 마스크로 하드마스크층을 식각하여 하드마스크 패턴을 형성하는 단계; 및

상기 하드마스크 패턴을 마스크로 상기 피식각층을 식각하여 피식각층 패턴을 형성하는 단계

를 포함하고,

상기 하드마스크층을 형성하는 단계는,

상기 피식각층 상부에 산화막을 형성하는 단계;

상기 산화막 상부에 비정질 탄소를 포함하는 제 1 하드마스크층을 형성하는 단계; 및

상기 제 1 하드마스크층의 상부에 실리콘 산화질화막을 포함하는 제 2 하드마스크층을 형성하는 단계

를 포함하며,

상기 하드마스크층을 식각하는 단계는,

상기 스페이서를 마스크로 상기 제 2 하드마스크층을 식각하여 제 2 하드마스크 패턴을 형성하는 단계;

상기 제 2 하드마스크 패턴을 마스크로 상기 제 1 하드마스크층을 식각하여 제 1 하드마스크 패턴을 형성하는 단계; 및

상기 제 1 하드마스크 패턴을 마스크로 상기 산화막을 식각하여 산화막 패턴을 형성하는 단계

를 포함하고,

상기 제 1 하드마스크 패턴을 형성하는 단계 후,

상기 제 1 하드마스크 패턴의 상부에 패드 마스크를 형성하는 단계를 더 포함하는 것을 특징으로 하는 반도체 소자의 형성방법.Forming a hard mask layer and a photoresist layer on the etched layer;

Exposing and developing the photoresist such that the photoresist includes a pad pattern, a line pattern connected to the pad pattern, and a dummy pattern positioned at the center of the pad pattern;

Forming a spacer on sidewalls of the photoresist pattern including the pad pattern, the line pattern, and the dummy pattern;

Etching the hard mask layer using the spacers as a mask to form a hard mask pattern; And

Etching the etched layer using the hard mask pattern as a mask to form an etched layer pattern

Including,

Forming the hard mask layer,

Forming an oxide film on the etched layer;

Forming a first hard mask layer including amorphous carbon on the oxide film; And

Forming a second hard mask layer including a silicon oxynitride layer on the first hard mask layer;

Including;

Etching the hard mask layer,

Etching the second hard mask layer using the spacers as a mask to form a second hard mask pattern;

Etching the first hard mask layer using the second hard mask pattern as a mask to form a first hard mask pattern; And

Etching the oxide layer using the first hard mask pattern as a mask to form an oxide layer pattern

Including,

After the forming of the first hard mask pattern,

Forming a pad mask on the first hard mask pattern, characterized in that it further comprises.

상기 패드 마스크를 형성하는 단계는,

트랜지스터 마스크를 형성하는 단계와 동시에 이루어지는 것을 특징으로 하는 반도체 소자의 형성방법.The method according to claim 5,

Forming the pad mask,

And forming a transistor mask at the same time.

상기 산화막 패턴은 패드 형상의 산화막 패턴, 라인 형상의 산화막 패턴, 및 상기 패드 형상의 산화막 패턴들을 연결하는 라인 형상의 패턴을 포함하는 것을 특징으로 하는 반도체 소자의 형성방법.The method according to claim 5,

The oxide film pattern may include a pad-shaped oxide film pattern, a line-shaped oxide film pattern, and a line-shaped pattern connecting the pad-shaped oxide film patterns.

상기 산화막 패턴 중 상기 패드 형상의 산화막 패턴을 연결하는 라인 형상의 산화막 패턴을 식각하여 제거함으로써, 각 패드 형상의 산화막 패턴을 분리하는 단계를 더 포함하는 것을 특징으로 하는 반도체 소자의 형성방법.The method according to claim 7,

And removing each pad-shaped oxide film pattern by etching and removing a line-shaped oxide film pattern connecting the pad-shaped oxide film pattern among the oxide film patterns.

상기 패드 형상의 산화막 패턴을 분리하는 단계는,

상기 패드 형상의 산화막 패턴을 연결하는 라인 형상의 산화막 패턴을 노출시키는 커팅 마스크를 형성하는 단계; 및

상기 커팅 마스크로 상기 산화막 패턴을 식각하는 단계

를 포함하는 것을 특징으로 하는 반도체 소자의 형성방법.The method according to claim 8,

Separating the pad-shaped oxide film pattern,

Forming a cutting mask exposing a line-shaped oxide film pattern connecting the pad-shaped oxide film pattern; And

Etching the oxide layer pattern with the cutting mask

Forming method of a semiconductor device comprising a.

상기 스페이서를 형성하는 단계는,

상기 감광막 패턴을 포함한 하드마스크층 상부에 ULTO(Ultra Low Temperature Oxide) 산화막을 증착하는 단계; 및

상기 ULTO 산화막을 에치백으로 제거하면서, 상기 감광막 패턴의 측벽에만 ULTO 산화막을 잔류시키는 단계

를 포함하는 것을 특징으로 하는 반도체 소자의 형성방법.The method according to claim 5,

Forming the spacers,

Depositing an ultra low temperature oxide (ULTO) oxide film on the hard mask layer including the photoresist pattern; And

Leaving the ULTO oxide on only the sidewalls of the photoresist pattern while removing the ULTO oxide with an etch back.

Forming method of a semiconductor device comprising a.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020100007469A KR101076794B1 (en) | 2010-01-27 | 2010-01-27 | Method of fabricating semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020100007469A KR101076794B1 (en) | 2010-01-27 | 2010-01-27 | Method of fabricating semiconductor device |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20110087848A KR20110087848A (en) | 2011-08-03 |

| KR101076794B1 true KR101076794B1 (en) | 2011-10-25 |

Family

ID=44926544

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020100007469A KR101076794B1 (en) | 2010-01-27 | 2010-01-27 | Method of fabricating semiconductor device |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR101076794B1 (en) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101948845B1 (en) | 2012-08-07 | 2019-02-18 | 에스케이하이닉스 주식회사 | Semiconductor device |

-

2010

- 2010-01-27 KR KR1020100007469A patent/KR101076794B1/en not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| KR20110087848A (en) | 2011-08-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7776750B2 (en) | Semiconductor device and method for forming a pattern in the same with double exposure technology | |

| KR100905157B1 (en) | Method for forming fine pattern of semiconductor device | |

| US7651950B2 (en) | Method for forming a pattern of a semiconductor device | |

| US8808971B2 (en) | Method for forming fine patterns of semiconductor device | |

| KR101031465B1 (en) | Method for Forming Fine Contact Hole Pattern of Semiconductor Device | |

| TWI483288B (en) | Method for manufacturing a semiconductor device | |

| US20110256723A1 (en) | Method for forming semiconductor device | |

| US20080160767A1 (en) | Semiconductor Device And Method For Forming Pattern In The Same | |

| JP2011176150A (en) | Method of manufacturing semiconductor device | |

| US20080160763A1 (en) | Semiconductor Device And Method For Forming Pattern In The Same | |

| US10734284B2 (en) | Method of self-aligned double patterning | |

| US7510973B2 (en) | Method for forming fine pattern in semiconductor device | |

| US20160365311A1 (en) | Method of manufacturing semiconductor devices with combined array and periphery patterning in self-aligned double patterning | |

| US9218984B2 (en) | Method for manufacturing a semiconductor device | |

| KR20120126442A (en) | Method for forming pattern of Semiconductor Device | |

| KR101061316B1 (en) | Method of forming fine pattern of semiconductor device | |

| KR101095076B1 (en) | Method of fabricating semiconductor apparatus | |

| KR101076794B1 (en) | Method of fabricating semiconductor device | |

| KR20100071402A (en) | Exposure mask and method for forming semiconductor device by using the same | |

| TWI447886B (en) | Multiple patterning method | |

| US20090305505A1 (en) | Method for manufacturing a semiconductor device | |

| KR20120081653A (en) | Method for manufacturing mask of semiconductor device | |

| TWI822307B (en) | Double patterning method of manufacturing select gates and word lines | |

| TWI576966B (en) | Semiconductor device and manufacturing method thereof | |

| TW202437862A (en) | Method of fabricating semiconductor device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| LAPS | Lapse due to unpaid annual fee |