KR100249974B1 - Semiconductor integrated circuit - Google Patents

Semiconductor integrated circuit Download PDFInfo

- Publication number

- KR100249974B1 KR100249974B1 KR1019970016029A KR19970016029A KR100249974B1 KR 100249974 B1 KR100249974 B1 KR 100249974B1 KR 1019970016029 A KR1019970016029 A KR 1019970016029A KR 19970016029 A KR19970016029 A KR 19970016029A KR 100249974 B1 KR100249974 B1 KR 100249974B1

- Authority

- KR

- South Korea

- Prior art keywords

- circuit

- signal

- potential

- output

- input

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0555—Shape

- H01L2224/05552—Shape in top view

- H01L2224/05554—Shape in top view being square

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48135—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/48137—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being arranged next to each other, e.g. on a common substrate

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Semiconductor Integrated Circuits (AREA)

- Logic Circuits (AREA)

- Dram (AREA)

Abstract

소비 전력을 가급적 적게 하는 것을 가능하게 한다.It is possible to make the power consumption as small as possible.

제 1 전원의 전위와 제 2 전원의 전위 사이의 소정 전위를 발생하는 바이어스 회로(1)와, 제 l 전원의 전위와 제 2 전원의 전위의 사이에서 진동하는 정전 및 반전 입력 신호를 수신하여 바이어스 회로의 출력 전위와 제 l 전원의 전위사이에서 진동하는 신호로 변환하고, 이 변환된 신호로 전송로를 구동하는 구동기 회로(5)와, 바이어스 회로의 출력 전위를 분압하는 분압 회로(9)와, 분압 회로의 출력을 기준 전위로 하여 전송로를 구동하는 신호를 검출하고, 제 1 전원의 전위와 제 2 전원의 전위의 사이에서 진동하는 신호로 변환하는 수신기 회로(10)를 구비하는 것을 특징으로 한다.The bias circuit 1 generates a predetermined potential between the potential of the first power supply and the potential of the second power supply, and receives and biases the electrostatic and inverted input signals oscillating between the potential of the first power supply and the potential of the second power supply. A driver circuit 5 for converting a signal oscillating between the output potential of the circuit and the potential of the first power supply, and driving the transmission path with the converted signal, and a voltage divider circuit 9 for dividing the output potential of the bias circuit; And a receiver circuit 10 for detecting a signal for driving the transmission path using the output of the voltage dividing circuit as a reference potential and converting the signal to a signal oscillating between the potential of the first power supply and the potential of the second power supply. It is done.

Description

본 발명은 버스, 클록선 또는 반도체칩의 입출력선을 구동하는 구동기 회로를 구비한 반도체 집적회로 장치에 관한 것이다.The present invention relates to a semiconductor integrated circuit device having a driver circuit for driving a bus, a clock line, or an input / output line of a semiconductor chip.

CM0S 회로의 소비전력 P 는 다음식에서 제공된다.The power consumption P of the CM0S circuit is given by the following equation.

[수학식 1][Equation 1]

P=pt·f·CL·Vs·VDD P = pt, f, CL, Vs, V DD

여기서, Vs 는 신호진폭, V 는 전원전압, pt 는 스위칭 확률, f 는 클록 주파수, CL 은 부하 용량이다.Where Vs is the signal amplitude, V is the supply voltage, pt is the switching probability, f is the clock frequency, and CL is the load capacity.

종래, 일반적인 회로에서는 신호는 전원 전압의 사이에서 진폭하기 때문에,In the conventional circuit, since the signal is amplitude between the power supply voltage,

[수학식 2][Equation 2]

P=pt·f·CL·VDD 2 P = pt, f, CL, V DD 2

가 된다.Becomes

버스나 클록선 또는 반도체칩의 입출력선에는 통상 큰 기생 용량이 존재하기 때문에, 이들의 선을 구동하는 구동기 회로는 큰 전력을 소비한다. 이 문제는 근래 반도체 집적회로 장치의 저소비 전력화가 요청되고 있는 동안 점점 더 중요한 문제로 되어 왔다.Since large parasitic capacitances are usually present in buses, clock lines, and input / output lines of semiconductor chips, the driver circuits that drive these lines consume large power. This problem has become an increasingly important problem in recent years when low power consumption of semiconductor integrated circuit devices has been called for.

그러므로, 소비 전력을 저감하는 방법의 한 가지는 수학식 1 로부터도 알 수 있는 바와 같이, 신호 진폭을 작게 하는 것이다. 그러나, 이것은 용이하지 않다. 우선, 소진폭 신호를 출력하는 구동기 회로를 저전력으로 실현하는 것이 어렵다. 혹은, 소진폭 신호를 수신하여 통상의 신호로 복귀시키는 수신기 회로를 저전력으로 실현하는 것도 어렵다.Therefore, one method of reducing power consumption is to reduce the signal amplitude, as can be seen from Equation (1). However, this is not easy. First, it is difficult to realize a driver circuit for outputting a small amplitude signal at low power. Alternatively, it is difficult to realize at low power a receiver circuit that receives a small amplitude signal and returns it to a normal signal.

또, 소진폭 신호로 하면 노이즈 여유가 작아지기 때문에, 잘못된 신호 전송을 하지 않도록 하는 것도 어렵다. 특히 칩의 입출력선에는 신호 반사등의 영향을 받기 쉽다. 통상의 진폭의 신호와의 크로스토크도 문제가 된다.In addition, since the noise margin becomes small when a small amplitude signal is used, it is also difficult to prevent wrong signal transmission. In particular, the input and output lines of the chip are susceptible to signal reflections. Crosstalk with signals of normal amplitude is also a problem.

또는, 온도 변화나 디바이스의 격차에 의한 수신기 회로의 임계치의 변동도 문제가 된다.Alternatively, variations in the threshold of the receiver circuit due to temperature changes and device variations are also a problem.

이상의 이유에 의해, 종래 소진폭 신호는 메모리의 비트선 신호등의 성질을 잘 알 수 있는 회로의 일부에 사용되고 있을 뿐이고, 일반의 반도체 회로 장치에는 전원 전압 사이에서 진폭하는 신호를 사용하고 있었다.For the above reason, the conventional small amplitude signal is only used in a part of the circuit which can know the characteristics of the bit line signal of a memory well, and the signal which amplifies between power supply voltages is used for the general semiconductor circuit device.

이 때문에, 상기 구동기 회로를 구비한 반도체 집적회로 장치의 저소비 전력화가 진전되지 않는다는 문제가 있다.For this reason, there is a problem that low power consumption of the semiconductor integrated circuit device including the driver circuit is not advanced.

본 발명은 상기 사정을 고려하여 이루어진 것으로, 소비 전력이 가급적 적은 구동기 회로를 구비한 반도체 집적회로 장치를 제공하는 것을 목적으로 한다.The present invention has been made in view of the above circumstances, and an object thereof is to provide a semiconductor integrated circuit device having a driver circuit with as little power consumption as possible.

도 1은 본 발명에 따른 반도체 집적회로 장치의 제 1 실시 형태의 구성도.1 is a configuration diagram of a first embodiment of a semiconductor integrated circuit device according to the present invention.

도 2는 본 발명에 따른 반도체 집적회로 장치의 제 2 실시 형태의 구성도.2 is a configuration diagram of a second embodiment of a semiconductor integrated circuit device according to the present invention;

도 3은 제 1 및 제 2 실시 형태의 반도체 집적회로 장치에 관한 분압 회로의 구체예를 도시하는 회로도.3 is a circuit diagram showing a specific example of a voltage divider circuit according to the semiconductor integrated circuit devices of the first and second embodiments.

도 4는 본 발명에 따른 반도체 집적회로 장치의 제 3 실시 형태의 구성도.4 is a configuration diagram of a third embodiment of a semiconductor integrated circuit device according to the present invention.

도 5는 본 발명에 따른 반도체 집적회로 장치의 제 4 실시 형태의 구성도.5 is a configuration diagram of a fourth embodiment of a semiconductor integrated circuit device according to the present invention.

도 6은 본 발명에 따른 구동기 회로의 입력 신호를 발생하는 회로도.6 is a circuit diagram for generating an input signal of a driver circuit according to the present invention.

도 7은 본 발명에 관한 수신기 회로내의 감지증폭 회로의 일구체예를 도시하는 회로도.Fig. 7 is a circuit diagram showing one specific example of the sense amplifier circuit in the receiver circuit according to the present invention.

도 8은 본 발명에 관한 수신기 회로내의 감지증폭 회로의 다른 일구체예를 도시하는 회로도.Fig. 8 is a circuit diagram showing another embodiment of the sense amplifier circuit in the receiver circuit according to the present invention.

도 9는 본 발명에 따른 반도체 집적회로 장치의 제 5 실시 형태의 구성도.9 is a configuration diagram of a fifth embodiment of a semiconductor integrated circuit device according to the present invention.

도 10은 제 5 실시 형태에 이용되는 버스 터미네이터 회로의 구체예를 도시하는 회로도.FIG. 10 is a circuit diagram showing a specific example of the bus terminator circuit used in the fifth embodiment. FIG.

도 11은 본 발명에 따른 반도체 집적회로 장치의 제 6 실시 형태의 구성도.11 is a configuration diagram of a sixth embodiment of a semiconductor integrated circuit device according to the present invention.

도 12는 본 발명에 따른 반도체 집적회로 장치의 제 7 실시 형태의 구성도.12 is a configuration diagram of a seventh embodiment of a semiconductor integrated circuit device according to the present invention.

도 13은 본 발명에 따른 반도체 집적회로 장치의 제 8 실시 형태의 구성도.13 is a configuration diagram of an eighth embodiment of a semiconductor integrated circuit device according to the present invention.

도 14는 본 발명에 따른 반도체 집적회로 장치의 제 9 실시 형태의 구성도.14 is a configuration diagram of a ninth embodiment of a semiconductor integrated circuit device according to the present invention.

도 15a 및 도 15b는 제 9 실시 형태의 반도체 집적회로 장치에 관한 반도체칩에 대한 스위치 회로의 구성도.15A and 15B are diagrams showing the configuration of a switch circuit for a semiconductor chip according to the semiconductor integrated circuit device of the ninth embodiment.

도 16a 내지 도 16c는 도 15에 도시된 반도체칩의 스위치 회로의 구성도.16A to 16C are configuration diagrams of a switch circuit of the semiconductor chip shown in FIG. 15.

도 17은 제 9 실시 형태의 제 l 변형예의 구성도.17 is a configuration diagram of a first modification of the ninth embodiment.

도 18은 제 9 실시 형태의 제 2 변형예의 구성도.18 is a configuration diagram of a second modification example of the ninth embodiment.

도 19는 본 발명에 따른 반도체 집적회로 장치의 제 10 실시 형태의 구성도.19 is a configuration diagram of a tenth embodiment of a semiconductor integrated circuit device according to the present invention.

도 20은 본 발명에 따른 반도체 집적회로 장치의 제 11 실시 형태의 구성도.20 is a configuration diagram of an eleventh embodiment of a semiconductor integrated circuit device according to the present invention.

도 21은 본 발명에 따른 반도체 집적회로 장치의 제 12 실시 형태의 구성도.21 is a configuration diagram of a twelfth embodiment of a semiconductor integrated circuit device according to the present invention.

도 22는 본 발명에 따른 반도체 집적회로 장치의 제 13 실시 형태의 구성도.22 is a configuration diagram of a thirteenth embodiment of a semiconductor integrated circuit device according to the present invention.

도 23a 및 도 23b는 제 13 실시 형태에 관한 반도체칩의 구성도.23A and 23B are diagrams of the semiconductor chip according to the thirteenth embodiment.

도 24는 기판 배선의 설명도.24 is an explanatory diagram of substrate wiring;

도 25는 본 발명에 따른 반도체 집적회로 장치의 제 14 실시 형태의 구성도.25 is a configuration diagram of a fourteenth embodiment of a semiconductor integrated circuit device according to the present invention;

도 26은 본 발명에 따른 반도체 집적회로 장치의 제 15 실시 형태의 구성도.Fig. 26 is a configuration diagram of a fifteenth embodiment of a semiconductor integrated circuit device according to the present invention.

* 도면의 주요부분에 대한 부호의 설명* Explanation of symbols for main parts of the drawings

1 : 바이어스 회로 2 : 전류원1: bias circuit 2: current source

3 : N 채널 MOS 트랜지스터 4 : 커패시터3: N-channel MOS transistor 4: capacitor

5 : 구동기 회로 9 : 분압 회로5

10 : 수신기 회로 40 : 버스 터미네이터10: receiver circuit 40: bus terminator

5lA,51B,52A,52B,53A,53B,54A,54B: 패드5l A , 51 B , 52 A , 52 B , 53 A , 53 B , 54 A , 54 B : Pad

61,62,63,64 : 본딩 배선 92a,92b : 셀렉터61, 62, 63, 64:

92c : 버스 101,l02,103 : 스위치 소자92c:

141,142,143,144 : 소진폭 입출력 회로141,142,143,144: Low amplitude input / output circuit

본 발명에 의한 반도체 집적회로 장치의 제 1 양태는, 제 1 전원의 전위와 제 2 전원의 전위 사이의 소정 전위를 발생하는 바이어스 회로와, 상기 제 1 전원의 전위와 상기 제 2 전원의 전위 사이에서 진동하는 정전 및 반전 입력 신호를 수신하고, 상기 바이어스 회로의 출력 전위와 상기 제 1 전원의 전위 사이에서 진동하는 신호로 변환하여 이 변환된 신호로 전송로를 구동하는 구동기 회로와, 상기 바이어스 회로의 출력 전위를 분압하는 분압 회로와, 상기 분압 회로의 출력을 기준전위로 하고, 상기 전송로를 구동하는 신호를 검출하며, 상기 제 1 전원의 전위와 상기 제 2 전원의 전위 사이에서 진동하는 신호로 변환하는 수신기 회로를 구비하는 것을 특징으로 한다.A first aspect of a semiconductor integrated circuit device according to the present invention is a bias circuit for generating a predetermined potential between a potential of a first power source and a potential of a second power source, and between a potential of the first power source and a potential of the second power source. A driver circuit for receiving an electrostatic and inverting input signal oscillating at a signal, converting the signal into a vibration signal between an output potential of the bias circuit and a potential of the first power supply, and driving the transmission path with the converted signal; A voltage dividing circuit for dividing the output potential of the signal; and a signal for driving the transmission path by setting the output of the voltage dividing circuit as a reference potential, and oscillating between the potential of the first power supply and the potential of the second power supply. It characterized in that it comprises a receiver circuit for converting to.

또한, 본 발명에 의한 반도체 집적회로 장치의 제 2 양태는 제 1 전원의 전위와 제 2 전원의 전위 사이의 소정 전위를 발생하는 바이어스 회로와, 상기 제 1 전원의 전위와 상기 제 2 전원의 전위의 사이에서 진동하는 정전 및 반전 입력신호를 수신하고, 인에이블 신호에 기초하여 상기 바이어스 회로의 출력 전위와 상기 제 1 전원의 전위 사이에서 진동하는 신호로 변환하여 이 변환된 신호로 전송로를 구동하거나 또는 출력이 고임피던스가 되는 구동기 회로와, 상기 바이어스 회로의 출력 전위를 분압하는 분압 회로와, 상기 분압 회로의 출력을 기준 전위로 하여 상기 전송로를 구동하는 신호를 검출하며, 상기 제 1 전원의 전위와 상기 제 2 전원의 전위 사이에서 진동하는 신호로 변환하는 수신기 회로를 구비하고 있는 것을 특징으로 한다.Further, a second aspect of the semiconductor integrated circuit device according to the present invention is a bias circuit for generating a predetermined potential between the potential of the first power supply and the potential of the second power supply, and the potential of the first power supply and the potential of the second power supply. Receives an electrostatic and inverting input signal oscillating between and converts the signal into a signal oscillating between the output potential of the bias circuit and the potential of the first power source based on the enable signal to drive the transmission path with the converted signal. Or a signal for driving the transmission path using a driver circuit whose output is high impedance, a voltage divider circuit for dividing the output potential of the bias circuit, an output of the voltage divider circuit as a reference potential, and the first power supply. And a receiver circuit for converting a signal oscillating between the potential of and the potential of the second power supply.

또한, 본 발명에 의한 반도체 집적회로 장치의 제 3 양태는, 제 1 전원의 전위와 제 2 전원의 전위 사이의 소정 전위를 발생하는 바이어스 회로와, 상기 제 1 전원의 전위와 상기 제 2 전원의 전위 사이에서 진동하는 정전 및 반전 입력 신호를 수신하고, 상기 바이어스 회로의 출력 전위와 상기 제 1 전원의 전위 사이에서 진동하는 차동 신호로 변환하여, 이 차동 신호로 전송로를 구동하는 구동기 회로와, 상기 전송로를 구동하는 차동 신호를 검출하고, 상기 제 1 전원의 전위와 상기 제 2 전원의 전위 사이에서 진동하는 신호로 변환하는 수신기 회로를 구비하고 있는 것을 특징으로 한다.Further, a third aspect of the semiconductor integrated circuit device according to the present invention is a bias circuit for generating a predetermined potential between the potential of the first power source and the potential of the second power source, the potential of the first power source and the second power source. A driver circuit for receiving an electrostatic and inverting input signal oscillating between the potentials, converting it into a differential signal oscillating between the output potential of the bias circuit and the potential of the first power supply, and driving the transmission path with the differential signal; And a receiver circuit for detecting a differential signal for driving said transmission path and converting it into a signal oscillating between the potential of said first power source and said potential of said second power source.

또한, 본 발명에 의한 반도체 집적회로 장치의 제 4 양태는, 제 1 전원의 전위와 제 2 전원의 전위 사이의 소정 전위를 발생하는 바이어스 회로와, 상기 제 1 전원의 전위와 상기 제 2 전원의 전위 사이에서 진동하는 정전 및 반전 입력 신호를 수신하고, 인에이블 신호에 기초하여 상기 바이어스 회로의 출력 전위와 상기 제 1 전원의 전위 사이에서 진동하는 차동 신호로 변환하여 이 차동 신호로 전송로를 구동하거나 또는 출력이 고임피던스가 되는 구동기 회로와, 상기 전송로를 구동하는 차동 신호를 검출하고, 상기 제 1 전원의 전위와 상기 제 2 전원의 전위 사이에서 진동하는 신호로 변환하는 수신기 회로를 구비하고 있는 것을 특징으로 한다.Further, a fourth aspect of the semiconductor integrated circuit device according to the present invention is a bias circuit for generating a predetermined potential between the potential of the first power supply and the potential of the second power supply, and the potential of the first power supply and the second power supply. Receives an electrostatic and inverting input signal oscillating between the potentials, converts the differential signal oscillating between the output potential of the bias circuit and the potential of the first power source based on the enable signal to drive the transmission path with this differential signal. Or a receiver circuit for outputting high impedance and a receiver circuit for detecting a differential signal for driving said transmission path and converting it into a signal oscillating between the potential of said first power supply and said potential of said second power source. It is characterized by being.

또한 본 발명에 의한 반도체 집적회로 장치의 제 5 양태는, 제 2 또는 제 4 양태의 반도체 집적회로 장치에 있어서, 상기 구동기 회로의 출력이 고임피던스가 되었을 때에 상기 전송로의 전위를 소정치로 유지하는 버스 터미네이터 회로를 구비하고 있는 것을 특징으로 한다.A fifth aspect of the semiconductor integrated circuit device according to the present invention is the semiconductor integrated circuit device according to the second or fourth aspect, wherein the potential of the transmission path is maintained at a predetermined value when the output of the driver circuit becomes high impedance. A bus terminator circuit is provided.

또한, 본 발명에 의한 반도체 집적회로 장치의 제 6 양태는, 제 1 전원의 전위와 제 2 전원의 전위 사이의 소정 전위를 발생하는 바이어스 회로, 상기 제 1 전원의 전위와 상기 제 2 전원의 전위 사이에서 진동하는 제 1 정전 및 반전 입력 신호를 수신하고, 제 l 인에이블 신호에 기초하여 상기 바이어스 회로의 출력 전위와 상기 제 1 전원의 전위 사이에서 진동하는 신호로 변환하여 이 신호로 출력하거나 또는 출력이 고임피던스가 되는 제 1 구동기 회로, 상기 바이어스 회로의 출력 전위를 분압하는 제 l 분압 회로 및 제 1 수신기 회로를 갖는 제 1 반도체칩과, 입력단이 배선을 통해 상기 제 1 분압 회로의 입력단에 접속되어 상기 바이어스 회로의 출력 전위를 분압하는 제 2 분압 회로, 상기 제 1 전원의 전위와 상기 제 2 전원의 전위 사이에서 진동하는 제 2 정전 및 반전 입력 신호를 수신하고, 제 2 인에이블 신호에 기초하여 상기 바이어스 회로의 출력 전위와 상기 제 l 전원 전위 사이에서 진동하는 신호로 변환하여 이 신호를 출력하거나 또는 출력이 고임피던스가 되도록 동작하며, 출력단이 전송용 배선을 통해 상기 제 l 구동기 회로의 출력단에 접속되는 제 2 구동기 회로 및 제 2 수신기 회로를 갖는 제 2 반도체칩을 구비하며, 상기 제 1 수신기 회로는 상기 제 1 구동기 회로의 출력이 고임피던스일 때에 동작하여 상기 전송용 배선을 통해 전송되는 상기 제 2 구동기 회로부터의 신호를 검출하여 상기 제 1 전원의 전위와 상기 제 2 전원의 전위 사이에서 진동하는 신호로 변환하며, 상기 제 2 수신기 회로는 상기 제 2 구동기 회로의 출력이 고임피던스일 때에 동작하여 상기 전송용 배선을 통해 전송되는 상기 제 1 구동기 회로부터의 신호를 검출하고 상기 제 l 전원의 전위와 상기 제 2 전원의 전위 사이에서 진동하는 신호로 변환하는 것을 특징으로 한다.Further, a sixth aspect of the semiconductor integrated circuit device according to the present invention is a bias circuit for generating a predetermined potential between the potential of the first power source and the potential of the second power source, the potential of the first power source and the potential of the second power source. Receiving a first electrostatic and inverting input signal oscillating therebetween, converting the signal into an oscillating signal between the output potential of the bias circuit and the potential of the first power source based on the first enable signal, and outputting the signal; or A first semiconductor chip having a first driver circuit having an output of high impedance, a first voltage divider circuit for dividing an output potential of the bias circuit, and a first receiver circuit, and an input terminal connected to an input terminal of the first voltage divider circuit through wiring; A second voltage divider circuit connected to divide the output potential of the bias circuit, and a second vibrating between the potential of the first power supply and the potential of the second power source. Receives electrostatic and inverting input signals and converts the signals into oscillating signals between the output potential of the bias circuit and the first power supply potential based on a second enable signal to output these signals or to make the outputs high impedance And a second semiconductor chip having a second driver circuit and a second receiver circuit, the output terminal of which is connected to the output terminal of the first driver circuit through a transmission line, wherein the first receiver circuit is a portion of the first driver circuit. Operates when the output is high impedance, detects a signal from the second driver opportunity transmitted through the transmission wiring, and converts the signal into a vibrating signal between the potential of the first power source and the potential of the second power source; The second receiver circuit operates when the output of the second driver circuit is high impedance and is transmitted through the transmission wiring. Detecting a signal of the group from the first driver circuit, and is characterized in that conversion into a signal that oscillates between the first l potential of the power source and the potential of the second power source.

또한, 본 발명에 의한 반도체 집적회로 장치의 제 7 양태는, 제 1 또는 제 6 양태 중 어느 하나의 반도체 집적회로 장치에 있어서, 상기 바이어스 회로는 각각의 게이트와 드레인이 접속된 동일 도전형의 복수의 M0S 트랜지스터가 직렬로 접속된 직렬 회로와, 상기 도전형과 동일한 도전형의 다른 MOS 트랜지스터를 가지며, 상기 직렬 회로의 소스측이 되는 일단은 상기 제 1 전원에 접속되고, 상기 직렬 회로의 드레인측이 되는 타단은 전류원 및 상기 다른 M0S 트랜지스터의 게이트에 접속되며, 상기 다른 M0S 트랜지스터의 드레인이 상기 제 2 전원에 접속되고, 상기 다른 M0S 트랜지스터의 소스로부터 바이어스 전위가 출력되는 것을 특징으로 한다.A seventh aspect of a semiconductor integrated circuit device according to the present invention is the semiconductor integrated circuit device according to any one of the first and sixth aspects, wherein the bias circuit includes a plurality of the same conductivity type each gate and drain are connected to each other. Has a series circuit in which the M0S transistors are connected in series, and another MOS transistor of the same conductivity type as the conductivity type, and one end which becomes the source side of the series circuit is connected to the first power supply, and the drain side of the series circuit is provided. The other end is connected to a current source and a gate of the other M0S transistor, a drain of the other M0S transistor is connected to the second power source, and a bias potential is output from the source of the other M0S transistor.

또한, 본 발명에 의한 반도체 집적회로 장치의 제 8 양태는, 제 1 전원의 전위와 제 2 전원의 전위 사이의 소정 전위를 발생하는 제 1 바이어스 회로, 상기 제 1 전원의 전위와 상기 제 2 전원의 전위 사이에서 진동하는 제 1 정전 및 반전 입력 신호를 수신하고, 제 1 인에이블 신호에 기초하여 상기 제 1 바이어스 회로의 출력 전위와 제 1 전원의 전위 사이에서 진동하는 차동 신호로 변환하여 이 차동 신호를 출력하거나 또는 출력이 고임피던스가 되는 제 l 구동기 회로 및 제 1 수신기 회로를 갖는 제 l 반도체칩과; 제 3 전원의 전위와 제 4 전원의 전위 사이의 소정전압을 발생하는 제 2 바이어스 회로, 상기 제 3 전원의 전위와 상기 제 4 전원의 전위 사이에서 진동하는 제 2 정전 및 반전 입력 신호를 수신하고, 제 2 인에이블 신호에 기초하여 상기 제 2 바이어스 회로의 출력 전위와 상기 제 3 전원의 전위 사이에서 진동하는 차동 신호로 변환하여 이 차동 신호를 출력하거나 또는 출력이 고임피던스가 되는 제 2 구동기 회로 및 제 2 수신기 회로를 갖는 제 2 반도체칩을 구비하며, 상기 제 1 및 제 2 구동기 회로의 출력단은 전송용 배선에 의해서 접속되고, 상기 제 1 수신기 회로는 상기 제 1 구동기 회로의 출력이 고임피던스일 때에 동작하여 상기 전송용 배선을 통해 전송되는 상기 제 2 구동기 회로부터의 차동 신호를 검출하여 상기 제 1 전원의 전위와 상기 제 2 전원의 전위 사이에서 진동하는 신호로 변환하고, 상기 제 2 수신기 회로는 상기 제 2 구동기 회로의 출력이 고임피던스일 때에 동작하여 상기 전송용 배선을 통해 전송되는 상기 제 1 구동기 회로로부터의 차동 신호를 검출하여 상기 제 3 전원의 전위와 상기제 4 전원의 전위 사이에서 진동하는 신호로 변환하는 것을 특징으로 한다.Moreover, the 8th aspect of the semiconductor integrated circuit device by this invention is the 1st bias circuit which generate | occur | produces the predetermined electric potential between the electric potential of a 1st power supply, and the electric potential of a 2nd power supply, the electric potential of the said 1st power supply, and said 2nd power supply. Receiving a first electrostatic and inverting input signal oscillating between a potential of and converting it into a differential signal oscillating between an output potential of the first bias circuit and a potential of a first power source based on the first enable signal; An first semiconductor chip having a first driver circuit and a first receiver circuit which output a signal or whose output is high impedance; Receiving a second bias circuit for generating a predetermined voltage between the potential of the third power source and the potential of the fourth power source, a second electrostatic and inverting input signal oscillating between the potential of the third power source and the potential of the fourth power source; A second driver circuit which converts the differential signal oscillating between the output potential of the second bias circuit and the potential of the third power source based on the second enable signal and outputs the differential signal or the output becomes high impedance. And a second semiconductor chip having a second receiver circuit, wherein output terminals of the first and second driver circuits are connected by a transmission line, and the first receiver circuit has a high impedance output of the first driver circuit. Is detected when the differential signal from the second driver circuit transmitted through the transmission wiring is detected and the potential of the first power supply and the second power supply are detected. Converts into a signal oscillating between the potentials, and the second receiver circuit operates when the output of the second driver circuit is high impedance to detect a differential signal from the first driver circuit transmitted through the transmission wiring And converting the signal into a vibrating signal between the potential of the third power source and the potential of the fourth power source.

또한, 본 발명에 의한 반도체 집적회로 장치의 제 9 양태는, 제 8 양태의 반도체 집적회로 장치에 있어서, 상기 제 l 바이어스 회로는 각각의 게이트와 드레인이 접속된 제 1 도전형의 복수의 M0S 트랜지스터가 직렬로 접속된 직렬 회로와, 상기 제 1 도전형의 다른 MOS 트랜지스터를 가지며, 상기 직렬 회로의 소스측이 되는 일단은 상기 제 l 전원에 접속되고, 상기 직렬 회로의 드레인측이 되는 타단은 전류원 및 상기 제 1 도전형의 다른 M0S 트랜지스터의 게이트에 접속되며, 상기 제 l 도전형의 다른 M0S 트랜지스터의 드레인이 상기 제 2 전원에 접속되고, 상기 제 l 도전형의 다른 MOS 트랜지스터의 소스로부터 바이어스 전위가 출력되고, 상기 제 2 바이어스 회로는 각각의 게이트와 드레인이 접속된 제 2 도전형의 복수의 M0S 트랜지스터가 직렬로 접속된 직렬 회로와, 상기 제 2 도전형의 다른 M0S 트랜지스터를 가지며, 상기 직렬 회로의 소스측이 되는 일단은 상기 제 3 전원에 접속되고, 상기 직렬 회로의 드레인측이 되는 타단은 전류원 및 상기 제 2 도전형의 다른 M0S 트랜지스터의 게이트에 접속되며, 상기 제 2 도전형의 다른 M0S 트랜지스터의 드레인이 상기 제 4 전원에 접속되고, 상기 제 2 도전형의 다른 M0S 트랜지스터의 소스로부터 바이어스 전위가 출력되는 것을 특징으로 한다.A ninth aspect of the semiconductor integrated circuit device according to the present invention is the semiconductor integrated circuit device according to the eighth aspect, wherein the first bias circuit includes a plurality of first conductive type M0S transistors having respective gates and drains connected thereto. Has a series circuit connected in series and another MOS transistor of the first conductivity type, one end serving as the source side of the series circuit is connected to the first power supply, and the other end serving as the drain side of the series circuit is a current source. And a drain of the other M0S transistor of the first conductivity type, the drain of the other M0S transistor of the first conductivity type is connected to the second power supply, and a bias potential from a source of the other MOS transistor of the first conductivity type. The second bias circuit is a series in which a plurality of M0S transistors of a second conductivity type each gate and drain are connected are connected in series. And another M0S transistor of the second conductivity type, one end of which is the source side of the series circuit is connected to the third power supply, and the other end of which is the drain side of the series circuit is a current source and the second conductivity type. Is connected to a gate of another M0S transistor of, wherein a drain of the other M0S transistor of the second conductivity type is connected to the fourth power source, and a bias potential is output from a source of the other M0S transistor of the second conductivity type. do.

또한, 본 발명에 의한 반도체 집적회로 장치의 제 10 양태는, 매트릭스형으로 배치된 복수의 반도체칩을 갖고, 각 반도체칩은 데이터 전송용의 입출력단을 가지며, 이 입출력단은 인접하는 다른 반도체칩의 입출력단과 본딩배선 또는 기판배선으로 이루어지는 전송용 배선에 의해서 접속되어 있으며, 또 반도체칩의 전부 또는 일부의 상기 데이터 전송용의 입출력단에는 소진폭 입출력 회로가 설치되어 있고, 이 소진폭 입출력 회로는 이 소진폭 입출력 회로가 설치되어 있는 반도체칩에 대응한 제 l 전원의 제 1 전위와 제 2 전원의 제 2 전위 사이에서 진동하는 정전 및 반전 신호를 수신하고, 상기 제 1 전위와 제 2 전위 사이의 소정 전위와 상기 제 1 전위와의 사이에서 진동하는 소진폭 신호로 변환하여 이 변환된 신호를 상기 전송용 배선을 통해 인접하는 다른 반도체칩의 입출력단에 송출하는 동시에, 상기 전송용 배선을 통해 전송되는 소진폭 신호를 상기 제 1 전위와 상기 제 2 전위 사이에서 진동하는 신호로 변환하는 것을 특징으로 한다.Further, a tenth aspect of a semiconductor integrated circuit device according to the present invention has a plurality of semiconductor chips arranged in a matrix, each semiconductor chip has an input / output terminal for data transmission, and the other input / output terminal is adjacent to another semiconductor chip. Is connected to the input / output terminals of the input / output terminals and the transmission wirings formed of the bonding wirings or the substrate wirings. Also, a small amplitude input / output circuit is provided at the input / output terminals for data transfer of all or part of the semiconductor chip. Receive an electrostatic and inverted signal oscillating between the first potential of the first power supply and the second potential of the second power supply corresponding to the semiconductor chip provided with the small amplitude input / output circuit, and between the first potential and the second potential. The signal is converted into a small amplitude signal oscillating between the predetermined potential of the first potential and the first potential, and the converted signal is adjacent through the transmission wiring. At the same time to transmit the input and output terminals of the other semiconductor chip, characterized in that for converting a small amplitude signal transmitted through the wiring for the signal transmitted to the vibration between the first potential and the second potential.

또한, 본 발명에 의한 반도체 집적회로 장치의 제 11 양태는, 제 10 양태의 반도체 집적회로 장치에 있어서, 상기 소진폭 입출력 회로는 상기 제 1 전위와 상기 제 2 전위 사이의 소정 전위를 발생하는 바이어스 회로와, 상기 제 1 전위와 상기 제 2 전위 사이에서 진동하는 정전 및 반전 입력 신호를 수신하고, 인에이블 신호에 기초하여 상기 바이어스 회로의 출력 전위와 상기 제 l 전위 사이에서 진동하는 신호로 변환하여 이 변환된 신호로 상기 전송용 배선을 구동하거나 또는 출력이 고임피던스가 되는 구동기 회로와, 상기 바이어스 회로의 출력 전위를 분압하는 분압 회로와, 상기 분압 회로의 출력을 기준 전위로 하여 상기 전송용 배선을 통해 전송되는 신호를 검출하고, 상기 제 1 전위와 상기 제 2 전위 사이에서 진동하는 신호로 변환하는 수신기 회로를 구비하고 있는 것을 특징으로 한다.An eleventh aspect of a semiconductor integrated circuit device according to the present invention is the semiconductor integrated circuit device of the tenth aspect, wherein the small amplitude input / output circuit includes a bias for generating a predetermined potential between the first potential and the second potential. A circuit and receives an electrostatic and inverting input signal oscillating between the first potential and the second potential, and converts the signal into a signal oscillating between the output potential of the bias circuit and the first potential based on an enable signal. The driver circuit which drives the said transmission wiring with this converted signal, or the output becomes high impedance, the voltage divider circuit which divides the output potential of the said bias circuit, and the said transmission wiring using the output of the voltage divider circuit as a reference potential. The receiver circuit detects a signal transmitted through the signal and converts the signal into a vibrating signal between the first potential and the second potential. Characterized in that the offers.

또한, 본 발명에 의한 반도체 집적회로 장치의 제 12 양태는, 제 10 양태의 반도체 집적회로 장치에 있어서, 상기 소진폭 입출력 회로는 상기 제 1 전위와 상기 제 2 전위 사이의 소정 전위를 발생하는 바이어스 회로와, 상기 제 1 전위와 상기 제 2 전위 사이에서 진동하는 정전 및 반전 입력 신호를 수신하고, 인에이블 신호에 기초하여 상기 바이어스 회로의 출력 전위와 상기 제 l 전원의 전위 사이에서 진동하는 차동 신호로 변환하여 이 차동 신호로 상기 전송용 배선을 구동하거나 또는 출력이 고임피던스가 되는 구동기 회로와, 상기 전송용 배선을 통해 보내져오는 차동 신호를 검출하여 상기 제 1 전위와 상기 제 2 전위 사이에서 진동하는 신호로 변환하는 수신기 회로를 구비하고 있는 것을 특징으로 한다.A twelfth aspect of the semiconductor integrated circuit device according to the present invention is the semiconductor integrated circuit device of the tenth aspect, wherein the small amplitude input / output circuit includes a bias for generating a predetermined potential between the first potential and the second potential. A differential signal receiving a circuit and an electrostatic and inverting input signal oscillating between the first potential and the second potential and oscillating between the output potential of the bias circuit and the potential of the first power source based on an enable signal Drive circuit for transmission with this differential signal, or output a high impedance, and detect a differential signal sent through the transmission wiring to oscillate between the first potential and the second potential. And a receiver circuit for converting the signal into a signal.

또한, 본 발명에 의한 반도체 집적회로 장치의 제 l3 양태는, 일렬로 배열된 제 1 내지 제 n 반도체칩을 갖고, 상기 제 1 반도체칩은 소정의 처리 기능을 갖는 제 l 기능 수단과, 데이터 전송용의 제 1 입출력단과, 상기 제 1 기능 수단의 출력을 이 출력보다도 작은 진폭을 갖는 소진폭 신호로 변환하여 상기 제 1 입출력단을 통해 인접하는 제 2 반도체칩에 송출하는 동시에, 상기 제 2 반도체칩으로부터 상기 제 l 입출력단을 통해 전송되는 소진폭 신호를 이 소진폭 신호보다도 큰 진폭을 갖는 대진폭 신호로 변환하여 상기 제 l 기능 수단에 송출하는 제 1 소진폭 입출력 회로를 구비하고, 상기 제 i(i=2,…,n-1)의 반도체칩은 소정의 처리기능을 갖는 제 i 기능 수단과, 데이터 전송용의 제 2(i-1) 및 제 2i-1의 입출력단과, 제 2(i-1) 및 제 2i-l의 소진폭 입출력 회로와, 제 i-1의 스위치 회로를 구비하고, 상기 제 i-1의 스위치 회로는 제 i의 기능 수단의 출력을 상기 제 2(i-1)의 소진폭 입출력 회로 또는 상기 제 2i-1의 소진폭 입출력 회로로 제어 신호에 기초하여 송출하는 동시에, 상기 제 2(i-1)의 소진폭 입출력 회로 또는 상기 제 2i-l의 소진폭 입출력 회로의 출력을, 상기 제 i의 기능 수단에 송출하거나 또는 바이패스하여 상기 제 2(i-1) 또는 제 2i-1의 소진폭 입출력 회로 중 다른쪽의 소진폭 입출력 회로에 송출하도록 상기 제어 신호에 기초하여 선택하며, 상기 제 2(i-1)의 소진폭 입출력 회로는 상기 제 i-1의 스위치 회로의 출력을 이 출력보다도 작은 진폭의 소진폭 신호로 변환하여 상기 제 2(i-1)의 입출력단을 통해 상기 제 i-1의 반도체칩에 송출하는 동시에, 상기 제 2(i-1)의 입출력단을 통해 상기 제 i-1의 반도체칩으로부터 전송되는 소진폭 신호를 이 소진폭 신호보다도 큰 진폭을 갖는 대진폭 신호로 변환하여 상기 제 i-1의 스위치 회로에 송출하고, 상기 제 2i-1의 소진폭 입출력 회로는 상기 제 i-1의 스위치 회로의 출력을 이 출력보다도 작은 진폭의 소진폭 신호로 변환하여 상기 제 2i-1의 입출력단을 통해 상기 제 I+1 반도체칩에 송출하는 동시에, 상기 제 2i-1의 입출력단을 통해 상기 제 i+1의 반도체칩으로부터 전송되는 소진폭 신호를 이 소진폭 신호보다도 큰 진폭의 대진폭 신호로 변환하여 상기 제 i-l의 스위치 회로에 송출하고, 상기 제 n 반도체칩은 소정의 처리 기능을 갖는 제 n 기능 수단과, 데이터 전송용의 제 2(n-1)의 입출력단과, 상기 제 n 기능 수단의 출력을 이 출력보다도 작은 진폭을 갖는 소진폭 신호로 변환하여 상기 제 2(n-1)의 입출력단을 통해 인접하는 제 n-1의 반도체칩에 송출하는 동시에, 상기 제 n-1의 반도체칩으로부터 상기 제 2(n-1)의 입출력단을 통해 전송되는 소진폭 신호를 이 소진폭 신호보다도 큰 진폭을 갖는 대진폭 신호로 변환하여 상기 제 n 기능 수단에 송출하는 제 2(n-1)의 소진폭 입출력 회로를 구비하고, 상기 제 i(i=l,…,n-1)의 반도체칩의 제 2i-1의 입출력단은 상기 제 i+1의 반도체칩의 제 2i의 입출력단과, 본딩배선 또는 기판배선으로 이루어지는 전송용 배선에 의해서 접속되어 있는 것을 특징으로 한다.Further, a third aspect of the semiconductor integrated circuit device according to the present invention has first to nth semiconductor chips arranged in a row, the first semiconductor chip having first processing means having a predetermined processing function, and data transfer. The first input / output terminal and the output of the first functional means are converted into a small amplitude signal having an amplitude smaller than this output, and are sent to the adjacent second semiconductor chip through the first input / output terminal, And a first small amplitude input / output circuit for converting the small amplitude signal transmitted from the chip through the first input / output terminal into a large amplitude signal having an amplitude greater than that of the small amplitude signal and sending it to the first functional means. The semiconductor chip of i (i = 2, ..., n-1) includes an i-th functional means having a predetermined processing function, input / output terminals of the second (i-1) and second i-1 for data transfer, and the second the small amplitude input / output circuit of (i-1) and 2i-l, and a switch circuit of i-1, wherein the switch circuit of i-1 receives the output of the i-th functional means from the small amplitude input / output circuit of the second (i-1) or the small amplitude input / output of the second i-1. Send out the output based on the control signal to the circuit and send the output of the second amplitude i / o circuit or the second amplitude input / output circuit to the i < th > Selects based on the control signal to pass to the other small amplitude input / output circuit of the second (i-1) or the second amplitude input / output circuit of the second i-1, and exhausts the second (i-1) The width input / output circuit converts the output of the switch circuit of the i-1 into a small amplitude signal having an amplitude smaller than this output and sends it to the semiconductor chip of the i-1 through the input / output terminal of the second (i-1). At the same time, through the input and output terminals of the second (i-1) to the semiconductor chip of the i-1 The small amplitude signal to be transmitted is converted into a large amplitude signal having an amplitude greater than that of the small amplitude signal, and sent to the switch circuit of the i-1. The output of the switch circuit is converted into a small amplitude signal having a smaller amplitude than this output and sent to the I + 1 semiconductor chip through the input / output terminal of the second i-1, and through the input / output terminal of the second i-1. The small amplitude signal transmitted from the i + 1th semiconductor chip is converted into a large amplitude signal having an amplitude larger than that of the small amplitude signal and sent to the switch circuit of the il. The nth semiconductor chip has a predetermined processing function. The second (n-1) by converting the nth functional means, the second (n-1) input / output terminal for data transmission, and the output of the nth functional means into a small amplitude signal having an amplitude smaller than this output; Adjacent to each other through the input and output The large amplitude signal which is sent to the n-1 semiconductor chip and is transmitted from the nth-1 semiconductor chip through the second (n-1) input / output terminal has a larger amplitude than the small amplitude signal. And a second (n-1) small amplitude input / output circuit which converts the signal to the nth function means and sends it to the i < th > The input / output terminal of the second i-1 of the semiconductor chip of n-1) is connected to the input / output terminal of the second i of the semiconductor chip of the i + 1 by a transmission wiring including bonding wiring or substrate wiring. do.

또한, 본 발명에 의한 반도체 집적회로 장치의 제 14 양태는, 제 13 양태의 반도체 집적회로 장치에 있어서, 상기 제 i(i=1,…,n-2)의 스위치 회로는 상기 제 2i의 소진폭 입출력 회로 및 상기 제 i+l의 기능 블록을 제 1 제어 신호에 기초하여 도동시키는 제 1 스위치 소자와, 상기 제 i+l의 기능 블록과 상기 제 2i+1의 소진폭 입출력 회로를 제 2 제어 신호에 기초하여 도통시키는 제 2 스위치 소자와, 상기 제 2i 의 소진폭 입출력 회로 및 제 2i+1의 소진폭 입출력 회로를 제 3 제어 신호에 기초하여 도통시키는 제 3 스위치 소자를 가지며, 상기 제j(j=1,…,3)의 스위치 소자는 상기 제 j의 제어 신호를 게이트에서 수신하는 N채널 MOS 트랜지스터와 상기 제 j의 제어 신호의 반전 신호를 수신하는 P채널 M0S 트랜지스터로 이루어지는 트랜스퍼 게이트를 가지며, 상기 제 1 내지 제 3 제어 신호는 이들 중의 1개의 제어 신호의 값이「H」레벨이면 다른 2개의 제어 신호는「L」레벨인 것을 특징으로 한다.A fourteenth aspect of the semiconductor integrated circuit device according to the present invention is the semiconductor integrated circuit device of the thirteenth aspect, wherein the switch circuit of the i th (i = 1, ..., n-2) is exhausted in the second i. A first switch element for guiding the width input / output circuit and the function block of the i + l based on a first control signal, the function block of the i + l and the small amplitude input / output circuit of the second i + 1; A second switch element for conducting on the basis of a control signal, and a third switch element for conducting the second amplitude input / output circuit of the second i and the small amplitude input / output circuit of 2i + 1 based on a third control signal; The switch element of j (j = 1, ..., 3) is a transfer gate comprising an N-channel MOS transistor for receiving the j-th control signal at the gate and a P-channel M0S transistor for receiving an inverted signal of the j-th control signal. Has a, from the first to The third control signal is characterized in that if the value of one of the control signals is "H" level, the other two control signals are "L" level.

또한, 본 발명에 의한 반도체 집적회로 장치의 제 15 양태는, 일렬로 배열된 제 l 내지 제 n 반도체칩을 가지며, 상기 제 1 반도체칩은 소정의 처리 기능을 갖는 제 1 기능 수단과, 데이터 전송용의 제 1 입출력단과, 상기 제 1 기능 수단의 출력을 이 출력보다도 작은 진폭을 갖는 소진폭 신호로 변환하여 상기 제 1 입출력단을 통해 인접하는 제 2 반도체칩에 송출하는 동시에, 상기 제 2 반도체칩으로부터 상기 제 1 입출력단을 통해 전송되는 소진폭 신호를 이 소진폭 신호보다도 큰 진폭을 갖는 대진폭 신호로 변환하여 상기 제 l 기능 수단에 송출하는 제 1 소진폭 입출력 회로를 구비하고, 상기 제 i(i=2,…,n-1)의 반도체칩은 소정의 처리 기능을 갖는 제 i 기능 수단과, 데이터 전송용의 제 2(i-1) 및 제 2i-1의 입출력단과, 제 2(i-1) 및 제 2i-1의 소진폭 입출력 회로와, 제 2(i-1) 및 제 2i-1의 선택기 회로를 구비하며, 상기 제 2(i-1)의 소진폭 입출력 회로는 상기 제 2(i-1)의 입출력단을 통해 인접하는 제 i-1의 반도체칩으로부터 전송되는 소진폭 신호를 이 소진폭 신호보다도 큰 진폭을 갖는 대진폭 신호로 변환하여 상기 제 2(i-1)의 선택기 회로에 송출하는 동시에 상기 제 2(i-1)의 선택기 회로로부터 신호를 이 신호보다도 진폭이 작은 신호로 변환하여 상기 제 2(i-1)의 입출력단을 통해 상기 제 i-1의 반도체칩에 송출하고, 상기 제 2i-l의 소진폭 입출력 회로는 상기 제 2i-1의 입출력단을 통해 인접하는 제 i+1의 반도체칩으로부터 전송되는 소진폭 신호를 이 소진폭 신호보다도 큰 진폭을 갖는 대진폭 신호로 변환하여 상기 제 2i-1의 선택기 회로에 송출하는 동시에, 상기 제 2i-1의 선택기 회로부터의 신호를 이 신호보다도 진폭이 작은 신호로 변환하여 상기 제 2i-1의 입출력단을 통해 상기 제 i+l의 반도체칩에 송출하고, 상기 제 2(i-1)의 선택기 회로는 상기 제 i의 기능 수단의 출력 및 상기 제 2i-1의 선택기 회로부터의 신호를 상기 제 2(i-1)의 소진폭 입출력 회로에 송출하는 동시에, 상기 제 2(i-1)의 소진폭 입출력 회로부터의 신호를 제어 신호에 기초하여 선택하고 상기 제 i의 기능 수단 또는 상기 제 2i-1의 선택기 회로에 송출하며, 상기 제 2i-1의 선택기 회로는 상기 제 i의 기능 수단의 출력 및 상기 제 2(i-1)의 선택기 회로부터의 신호를 상기 제 2i-1의 소진폭 입출력 회로에 송출하는 동시에, 상기 제 2i-l의 소진폭 입출력 회로부터의 신호를 상기 제어 신호에 기초하여 선택하고 상기 제 i의 기능 수단 또는 상기 제 2(i-1)의 선택기 회로에 송출하고, 상기 제 n 반도체칩은 소정의 처리 기능을 갖는 제 n 기능 수단과, 데이터 전송용의 제 2(n-1)의 입출력단과, 상기 제 n 기능 수단의 출력을 이 출력보다도 작은 진폭을 갖는 소진폭 신호로 변환하여 상기 제 2(n-1)의 입출력단을 통해 인접하는 제 n-1의 반도체칩에 송출하는 동시에, 상기 제 n-l의 반도체칩으로부터 상기 제 2(n-1)의 입출력단을 통해 전송되는 소진폭 신호를 이 소진폭 신호보다도 큰 진폭을 갖는 대진폭 신호로 변환하여 상기 제 n 기능 수단에 송출하는 제 2(n-1)의 소진폭 입출력 회로를 구비하고 있는 것을 특징으로 한다.Further, a fifteenth aspect of a semiconductor integrated circuit device according to the present invention has first to nth semiconductor chips arranged in a row, the first semiconductor chip having first functional means having a predetermined processing function, and data transfer. The first input / output terminal and the output of the first functional means are converted into a small amplitude signal having an amplitude smaller than this output, and are sent to the adjacent second semiconductor chip through the first input / output terminal, And a first small amplitude input / output circuit for converting the small amplitude signal transmitted from the chip through the first input / output terminal into a large amplitude signal having an amplitude greater than that of the small amplitude signal and sending it to the first functional means. The semiconductor chip of i (i = 2, ..., n-1) includes an i-th functional means having a predetermined processing function, input / output terminals of the second (i-1) and second i-1 for data transfer, and the second Small amplitude input / output circuit of (i-1) and 2i-1 And a selector circuit of second (i-1) and second i-1, wherein the small amplitude input / output circuit of the second (i-1) is adjacent to the second (i-1) input / output terminal. The small amplitude signal transmitted from the semiconductor chip of i-1 is converted into a large amplitude signal having an amplitude larger than that of the small amplitude signal, and sent to the selector circuit of the second (i-1). Signal is converted into a signal having a smaller amplitude than that of this signal and sent to the semiconductor chip of the i-1 through the input / output terminal of the second (i-1), and the small amplitude of the second i-1 The input / output circuit converts the small amplitude signal transmitted from the semiconductor chip of the i + 1 adjacent through the input / output terminal of the second i-1 into a large amplitude signal having an amplitude larger than that of the small amplitude signal. The signal from the selector of the second i-1 is amplitude greater than that of the signal The signal is converted into a small signal and sent to the semiconductor chip of the i + l through the input / output terminal of the second i-1, and the selector circuit of the second (i-1) outputs the output of the i < th > The signal from the selector of 2i-1 is sent to the small amplitude input / output circuit of the second (i-1), and the signal from the small amplitude input / output circuit of the second (i-1) is based on the control signal. Selects and outputs to the i-th functional means or the selector circuit of the second i-1, wherein the selector circuit of the second i-1 outputs the output of the i-th functional means and the selector circuit of the second (i-1). Outputs a signal from the second amplitude input / output circuit to the second i-1, and simultaneously selects a signal from the second amplitude input / output circuit of the second i-1 based on the control signal; Is sent to the selector circuit of 2 (i-1), and the nth semiconductor chip is The second (n-1) input / output terminals for data transmission, the output of the nth function means and the second amplitude means having a smaller amplitude than the output to convert the second ( The small amplitude signal transmitted through the input / output terminal of n-1) to the adjacent nth-1 semiconductor chip and transmitted through the input / output terminal of the second (n-1) from the semiconductor chip of nl And a second (n-1) small amplitude input / output circuit which is converted to a large amplitude signal having an amplitude larger than that of the small amplitude signal and sent to the nth function means.

또한, 본 발명에 의한 반도체 집적회로 장치의 제 16 양태는, 제 13 내지 제15 중 어느 하나의 양태의 반도체 집적회로 장치에 있어서, 상기 제 1 반도체칩은 CPU를 구비하고 있고, 상기 제 2 내지 제 n 반도체칩은 각각 메모리를 구비하고 있는 것을 특징으로 한다.A sixteenth aspect of the semiconductor integrated circuit device according to the present invention is the semiconductor integrated circuit device according to any one of the thirteenth to fifteenth aspects, wherein the first semiconductor chip includes a CPU, and the second to second aspects. The nth semiconductor chip is characterized by including a memory.

또한, 본 발명에 의한 반도체 집적회로 장치의 제 17 양태는, 제 13 내지 제15 중 어느 하나의 양태의 반도체 집적회로 장치에 있어서, 상기 제 1 내지 제 n-1의 반도체칩은 각각 CPU를 구비하고 있고, 상기 제 n 반도체칩은 메모리를 구비하고 있는 것을 특징으로 한다.A seventeenth aspect of a semiconductor integrated circuit device according to the present invention is the semiconductor integrated circuit device according to any one of the thirteenth to fifteenth aspects, wherein the semiconductor chips of the first to n-1 are each provided with a CPU. The nth semiconductor chip is characterized by including a memory.

본 발명에 따른 반도체 집적회로 장치의 제 1 실시 형태를 도 1에 나타낸다. 본 실시 형태의 반도체 집적회로 장치는 소진폭 출력 회로와, 분압 회로(9)와, 감지증폭 회로를 갖는 수신기 회로(10)를 구비하고 있다. 소진폭 출력 회로는 바이어스 회로(1)와 구동기 회로(5)를 포함하고 있다.1 shows a first embodiment of a semiconductor integrated circuit device according to the present invention. The semiconductor integrated circuit device of this embodiment includes a

바이어스 회로(l)는 소정의 전위를 발생하는 것으로, 전류원(2)과, 동일 사이즈의 n개의 N 채널 MOS 트랜지스터(Ml,…,Mn)을 직렬로 접속한 직렬 회로와, N 채널 MOS 트랜지스터(3)와, 커패시터(4)를 구비하고 있다. 각 트랜지스터 Mi(i=1,…,n)의 게이트 단자는 드레인 단자에 접속되고, 트랜지스터 Mn의 드레인 단자는 전류원(2)의 출력 단자에 접속되며, 트랜지스터 M1의 소스는 접지된다. 한편, 트랜지스터(3)의 드레인 단자는 구동 전원 VDD에 접속되고, 게이트 단자는 트랜지스터 Mn의 드레인 단자에 접속되며, 소스 단자는 커패시터(4)를 통해 접지된다.The

따라서, 각 트랜지스터 Mi(i=1,…,n)의 임계치 전압을 Vth로 하면 트랜지스터 Mn의 드레인 단자의 전위는 n·Vth가 된다.Therefore, when the threshold voltage of each transistor M i (i = 1, ..., n) is set to V th , the potential of the drain terminal of the transistor M n becomes n · V th .

또한, 트랜지스터(3)의 임계치 전압도 Vth로 하는 것이 가능해지기 때문에 트랜지스터(3)의 소스 단자, 즉 바이어스 회로(1)의 출력 단자 Nv의 전위는 일정 전위 (n-1)·Vth가 된다. 또, 커패시터(4)는 바이어스 회로(1)의 출력단의 전위를 보다 안정하게 하기 위해서 설치한 것으로, 이것에 의해 구동기 회로(5)의 출력 과도응답이 양호하게 된다. 커패시터(4)는 없어도 좋다.In addition, since the threshold voltage of the

구동기 회로(5)는 구동 전위 VDD와 접지 전위 GND 의 사이에서 진동하는 정전 입력 신호 및 반전 입력 신호를 수신하여 바이어스 회로(1)의 출력 전위와 접지 전위 GND 와의 사이에서 진동하는 소진폭 신호로 변환하고 이 소진폭 신호에 의해서 버스나 클록선 등의 전송로(100)를 구동하는 것으로, 직렬로 접속된 N 채널 MOS 트랜지스터(61,62)를 구비하고 있다. 트랜지스터(61)는 드레인이 바이어스 회로의 출력 단자 NV에 접속되고, 게이트에서 정전 입력 신호를 수신하며, 소스가 트랜지스터(62)의 드레인에 접속되어 있다. 또한, 트랜지스터(62)는 게이트에서 반전 입력 신호를 수신하고, 소스가 접지되어 있다. 그리고 트랜지스터(61)와 트랜지스터(62)의 접속점으로 부터 출력 신호가 전송로(100)에 송출된다.The

분압 회로(9)는 바이어스 회로(1)의 출력 전압을 분압하는 것으로, 예컨대, 도 3에 도시된 바와 같이 직렬로 접속된 복수(도면상에서는 2개)의 저항 Rl,R2로 구성된다.The

수신기 회로(10)는 분압 회로(9)의 출력 전위를 기준 전위로 하여 전송로(100)를 통해 전송되는 소진폭 신호를 감지증폭 회로에서 검출하고, 구동 전위 VDD와 접지 전위 GND 사이에서 진동하는 신호로 변환하는 것이다.The

이상 설명한 바와 같이, 제 1 실시 형태의 반도체 집적회로 장치에 의하면, 버스나 블록선 등의 전송로(100)를 구동하는 구동기 회로(5)의 출력은 소진폭 신호로 하는 것이 가능해진다. 일반적으로, 구동기 회로의 소비 전력은 출력 신호의 진폭에 비례한다. 이 때문에, 본 실시 형태의 반도체 집적회로 장치는 소비 전력을 종래의 경우에 비교하여 적게 할 수 있다.As described above, according to the semiconductor integrated circuit device of the first embodiment, the output of the

또, 상기 실시 형태에서는 바이어스 회로(1)내의 직렬 회로는 동일 사이즈의 N 채널 MOS 트랜지스터로 구성하였지만 다른 사이즈의 N 채널 MOS 트랜지스터로 구성하여도 좋다.In the above embodiment, the series circuit in the

이어서 본 발명에 따른 반도체 집적회로 장치의 제 2 실시 형태의 구성을 도 2에 도시한다. 본 실시 형태의 반도체 집적회로 장치는 도 1에 도시된 제 1 실시의 형태의 반도체 집적회로 장치에 있어서, 구동기 회로(5)에 NOR 게이트(71,72)를 새롭게 설치한 것이다. NOR 게이트(71)는 정전 입력 신호와 인에이블 신호에 기초하여 NOR 연산을 행하고, 연산 결과를 트랜지스터(61)의 게이트에 송출한다. NOR 게이트(72)는 반전 입력 신호와 인에이블 신호에 기초하여 NOR 연산을 행하며, 연산 결과를 트랜지스터(62)의 게이트에 출력한다.Next, the structure of 2nd Embodiment of the semiconductor integrated circuit device which concerns on this invention is shown in FIG. In the semiconductor integrated circuit device of the present embodiment, in the semiconductor integrated circuit device of the first embodiment shown in FIG. 1, NOR gates 7 1 , 7 2 are newly provided in the

따라서, 본 제 2 실시 형태에서는 인에이블 신호가 L 레벨인 경우는 도 1에 나타낸 제 1 실시 형태와 동일한 동작을 행하고, 인에이블 신호가 H 레벨인 경우는 구동기 회로(5)의 출력이 고임피던스가 된다.Therefore, in the second embodiment, when the enable signal is at the L level, the same operation as in the first embodiment shown in FIG. 1 is performed. When the enable signal is at the H level, the output of the

본 제 2 실시 형태의 반도체 집적회로 장치도 제 1 실시 형태와 동일한 효과를 발휘하는 것은 말할 필요도 없다.It goes without saying that the semiconductor integrated circuit device of the second embodiment also has the same effect as that of the first embodiment.

이어서 본 발명에 따른 반도체 집적회로 장치의 제 3 실시 형태의 구성을 도 4에 도시한다. 본 실시 형태의 반도체 집적회로 장치는 도 1에 도시된 제 1 실시 형태의 반도체 집적회로 장치에 있어서, 분압 회로(9)를 삭제하는 동시에, 구동기 회로(5)에 직렬 접속된 N 채널 MOS 트랜지스터(63,64)를 새롭게 설치한 것이다. 트랜지스터(63)는 드레인이 바이어스 회로(1)의 출력 단자에 접속되고, 게이트에서 반전 입력 신호를 수신하고, 소스가 트랜지스터(64)의 드레인에 접속되어 있다. 트랜지스터(64)는 게이트에서 정전 입력 신호를 수신하고, 소스가 접지되어 있다.Next, the structure of 3rd Embodiment of the semiconductor integrated circuit device which concerns on this invention is shown in FIG. The semiconductor integrated circuit device of the present embodiment is the semiconductor integrated circuit device of the first embodiment shown in FIG. 1, in which an N-channel MOS transistor connected in series with the

그리고, 트랜지스터(61)와 트랜지스터(62)의 접속점으로 부터 소진폭화된 정전 신호가 전송로(1001)를 통해 수신기 회로(10)에 전송된다. 또한 트랜지스터(63)와 트랜지스터(64)의 접속점으로 부터 소진폭화된 반전 신호가 전송로(1002)를 통해 수신기 회로(10)에 전송된다.Then, a small amplitude electrostatic signal from the connection point of the

따라서, 제 3 실시 형태에 있어서는, 구동기 회로(5)는 소정의 전위(n-1)·Vth와 접지 전위 GND의 사이에서 진동하는 차동 신호로 전송로(1001,1002)를 구동한다. 수신기 회로(10)는 전송로(1001,1002)를 통해 전송되는 차동 신호를 감지증폭 회로에서 검출하여 구동 전원 VDD와 접지 전원 GND 사이에서 진동하는 신호로 변환한다.Therefore, in the third embodiment, the

이상 설명한 바와 같이 본 실시 형태의 반도체 집적회로 장치도 제 l 실시 형태의 경우와 동일하게 소비 전력을 가급적 적게 할 수 있다.As described above, the semiconductor integrated circuit device of the present embodiment can reduce power consumption as much as possible in the case of the first embodiment.

또, 본 실시 형태의 반도체 집적회로 장치에서는 전송로가 제 l 실시 형태에 비해 2배 필요하지만, 감지증폭 회로의 기준 전위가 불필요하며, 또한 동상 노이즈도 강해져서 동작 여유가 넓어진다.In the semiconductor integrated circuit device of this embodiment, although the transmission path is required twice as compared with the first embodiment, the reference potential of the sense amplifier circuit is unnecessary, and the in-phase noise also becomes stronger, thereby increasing the operation margin.

이어서 본 발명에 따른 반도체 집적회로 장치의 제 4 실시 형태의 구성을 도 5에 도시한다. 본 실시 형태의 반도체 집적회로 장치는 도 4에 도시된 제 3 실시 형태의 반도체 집적회로 장치에서 구동기 회로(5)에 NOR 게이트(71,72)를 설치한 것이다.Next, the structure of 4th Embodiment of the semiconductor integrated circuit device which concerns on this invention is shown in FIG. In the semiconductor integrated circuit device of this embodiment, the NOR gates 7 1 , 7 2 are provided in the

NOR 게이트(71)는 정전 입력 신호와 인에이블 신호에 기초하여 NOR 연산을 행하고, 연산 결과를 트랜지스터(61,64)의 게이트에 송출한다. NOR 게이트(72)는 반전 입력 신호와 인에이블 신호에 기초하여 NOR 연산을 행하며, 연산 결과를 트랜지스터(62,63)의 게이트에 송출한다.The NOR gate 7 1 performs an NOR operation based on the electrostatic input signal and the enable signal, and sends the result of the operation to the gates of the

따라서, 본 실시 형태에서는 인에이블 신호가 L 레벨인 경우는 제 3 실시 형태와 동일한 동작을 행하고, 인에이블 신호가 H 레벨인 경우는 구동기 회로(5)의 출력은 고임피던스가 된다.Therefore, in the present embodiment, when the enable signal is at the L level, the same operation as in the third embodiment is performed. When the enable signal is at the H level, the output of the

이상 설명한 바와 같이, 본 실시 형태의 반도체 집적회로 장치도 소비 전력을 가급적 작게 할 수가 있다.As described above, the semiconductor integrated circuit device of this embodiment can also reduce power consumption as much as possible.

또, 제 1 내지 제 4 실시 형태에서 이용되는 정전 입력 신호와 반전 입력 신호는 도 6에 도시된 바와 같이 반전 게이트(21,22)와, P 채널 MOS 트랜지스터 및 N 채널 MOS 트랜지스터로 구성된 트랜스퍼 게이트(23)로 이루어진 회로에 의해 생성할 수 있다.In addition, the electrostatic input signal and the inverted input signal used in the first to fourth embodiments are inverted

또한, 제 1 내지 제 4 실시 형태에 이용되는 감지증폭 회로는 도 7에 도시된 바와 같이 전류원(25)과, 차동 입력 신호를 게이트에서 수신하는 2개의 P 채널 MOS 트랜지스터(261,262)와, 2개의 N 채널 MOS 트랜지스터(271,272)로 구성하는 것이 가능하다. 또, 제 1 및 제 2 실시 형태에 있어서는 트랜지스터(262)의 게이트에 분압 회로(9)의 출력이 입력된다.In addition, the sense amplifier circuits used in the first to fourth embodiments include a

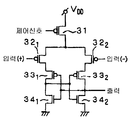

또한, 상술한 감지증폭 회로는 도 8에 도시된 바오 같이 제어 신호를 게이트에서 수신하는 P 채널 MOS 트랜지스터(31)와, 차동 입력 신호를 게이트에서 수신하는 2개의 P 채널 MOS 트랜지스터(321,322)와, 직렬로 접속되는 동시에 게이트가 공통으로 접속되는 P 채널 MOS 트랜지스터(331) 및 N 채널 MOS 트랜지스터(341)와, 직렬로 접속되는 동시에 게이트가 공통으로 접속되는 P 채널 MOS 트랜지스터(332) 및 N 채널 MOS 트랜지스터(342)로 구성하는 것이 가능하다.In addition, the sensing amplifier circuit described above includes a P-

이어서 본 발명에 따른 반도체 집적회로 장치의 제 5 실시 형태의 구성을 도 9에 도시한다. 본 실시 형태의 반도체 집적회로 장치는 도 2에 도시된 제 2 실시 형태의 반도체 집적회로 장치에 있어서, 바이어스 회로(1)의 출력 단자와 전송로(100)와의 사이에 버스 터미네이터 회로(40)를 새롭게 설치한 것이다. 이 버스 터미네이터 회로(40)는 구동기 회로(5)의 출력이 고임피던스가 되었을 때에 버스 등의 전송로(100)의 전위를 유지하기 위한 것이다.Next, the structure of 5th Embodiment of the semiconductor integrated circuit device which concerns on this invention is shown in FIG. The semiconductor integrated circuit device of the present embodiment is the semiconductor integrated circuit device of the second embodiment shown in Fig. 2, wherein the

이 버스 터미네이터 회로(40)는 도 10에 도시된 바와 같이, 2개의 P 채널 MOS 트랜지스터(411,412)와, 2개의 N 채널 MOS 트랜지스터(421,422)로 구성된다. 트랜지스터(41i)(i=1,2)는 소스가 바이어스 회로(1)의 출력 단자 NV에 접속되고, 게이트가 트랜지스터(42i)의 게이트에 접속되며, 드레인이 트랜지스터(42i)의 드레인에 접속된다. 그리고, 트랜지스터(42i)(i=1,2)의 소스는 접지된다. 트랜지스터(411,421)의 드레인은 트랜지스터(4l2,422)의 게이트에 접속되고, 트랜지스터(412,422)의 드레인은 트랜지스터(411,421)의 게이트에 접속된다. 그리고 트랜지스터(411,421)의 드레인은 전송로(100)에 접속된다.This

이상 설명한 것에 의해 본 제 5 실시 형태의 반도체 집적회로 장치도 제 2 실시 형태와 같이 소비 전력을 가급적 적게 할 수 있다. 또한, 구동기 회로(5)의 출력이 고임피던스가 되었을 때에 전송로(100)의 전위를 소정의 전위로 유지할 수가 있다.As described above, the semiconductor integrated circuit device of the fifth embodiment can have as little power consumption as in the second embodiment. In addition, when the output of the

이어서 본 발명에 따른 반도체 집적회로 장치의 제 6 실시 형태의 구성을 도 11에 도시한다. 본 실시 형태의 반도체 집적회로 장치는 도 5에 도시된 제 4 실시 형태의 반도체 집적회로 장치에 있어서, 바이어스 회로(2)의 출력 단자 NV와 전송로(1001,1002)와의 사이에 버스 터미네이터 회로(40)를 설치한 것이다. 이 버스 터미네이터 회로(40)는 제 5 실시 형태의 경우와 동일하게 구동기 회로(5)의 출력이 고임피던스가 되었을 경우에 전송로(1001,1002)의 전위를 소정의 전위로 유지하기 위한 것으로, 도 10에 도시된 회로에 의해서 실현된다. 이 경우, 도 10에 도시된 트랜지스터(411,421)의 드레인에 전송로(1001)가 접속되고, 트랜지스터(4l2,422)의 드레인에는 전송로(1002)가 접속된다.Next, the structure of 6th Embodiment of the semiconductor integrated circuit device which concerns on this invention is shown in FIG. The semiconductor integrated circuit device of the present embodiment is a semiconductor integrated circuit device of the fourth embodiment shown in Fig. 5, wherein the bus is connected between the output terminal N V of the

이상 설명한 바와 같이, 본 제 6 실시 형태의 반도체 집적회로 장치도 제 4 실시 형태의 경우와 동일하게 소비 전력을 가급적 적게 할 수 있다. 또한 구동기 회로(5)의 출력이 고임피던스가 되었을 경우에 전송로(1001,1002)의 전위를 소정의 전위로 유지할 수 있다.As described above, the semiconductor integrated circuit device of the sixth embodiment can reduce power consumption as much as possible in the case of the fourth embodiment. In addition, when the output of the

또, 제 1 내지 제 6 실시 형태에서, 구동기 회로(5)와 수신기 회로(10)는 동일 전원에 의해서 구동하여도 좋고, 다른 전원에 의해서 구동하는 것도 가능하다.In the first to sixth embodiments, the

이어서 본 발명에 따른 반도체 집적회로 장치의 제 7 실시 형태의 구성을 도 12에 도시한다. 본 실시 형태의 반도체 집적회로 장치는 2개의 반도체칩중의 반도체칩A 에 바이어스 회로(1A)와, 구동기 회로(5A)와, 분압 회로(9A)와, 수신기 회로(10A)를 설치하고, 반도체칩B 에 커패시터(4B)와, 구동기 회로(5B)와, 분압 회로(9B)와, 수신기 회로(10B)를 설치한 것이다.Next, the structure of 7th Embodiment of the semiconductor integrated circuit device which concerns on this invention is shown in FIG. The semiconductor integrated circuit device of this embodiment is two and a bias circuit (1 A) on the semiconductor chip A of the semiconductor chip, the driver circuit (5 A) and a voltage dividing circuit (9 A) and a receiver circuit (10 A) installation, and will have installed a capacitor (4 B), and a driver circuit (5 B), and a divider circuit (9 B), and a receiver circuit (10 B) on the semiconductor chip B.

바이어스 회로(1A), 구동기 회로(5A,5B), 및 분압 회로(9A,9B)는 도 2에 도시된 제 2 실시 형태에 관한 바이어스 회로(l), 구동기 회로(5), 및 분압 회로(9)와 각각 동일한 구성이다.The

바이어스 회로(1A)의 출력단 NV는 분압 회로(9A)의 입력단에 접속되어 있는 동시에 반도체칩A 에 설치되어 있는 패드(51A)에도 접속되어 있다. 또한, 분압 회로(9B)의 입력단 및 커패시터의 일단은 칩B 상에 설정된 패드(51B)에 접속되어 있다. 그리고 이들 칩 A,B 는 매우 인접한 거리로 배치되고, 패드(51A,51B)는 본딩 배선(61)에 의해서 접속된다. 따라서 바이어스 회로(1A)의 출력 전위는 칩B 에도 패드(51A), 본딩 배선(61), 및 패드(51B)를 통해 분압 회로(9B) 및 커패시터(4B)에 인가된다. 또, 커패시터(4B)는 분압 회로(9B)의 입력단의 전위를 안정하게 유지하기 위해서 설정된 것이다. 커패시터(4B)는 없어도 좋다.The output terminal N V of the

또한 구동기 회로(5A)의 출력단은 칩A 상에 설정된 패드(52A)에 접속되고, 구동기 회로(5B)의 출력단은 칩B 상에 설정된 패드(52B)에 접속되어 있다. 그리고 이들 패드(52A,52B)는 본딩 배선(62)에 의해서 접속되어 있다. 또, 구동기 회로(5B)를 구성하는 트랜지스터(61)의 드레인은 패드(51B)에 접속되어 있다.The output end of the

한편, 수신기 회로(10A)는 분압 회로(9A)의 출력 전위를 기준 전위로 하여 본딩 배선(62)을 통해 전송되는 구동기 회로(5B)의 출력을 감지증폭 회로에서 검출하여 구동 전위 VDD와 접지 전위의 사이에서 진동하는 신호로 변환한다. 또한 수신기 회로(10B)는 분압 회로(9B)의 출력 전위를 기준 전위로 하여 본딩 배선(62)을 통해 전송되는 구동기 회로(5A)의 출력을 감지증폭 회로에서 검출하여 구동 전위 VDD와 접지 전위의 사이에서 진동하는 신호로 변환한다.On the other hand, the

따라서, 본 실시 형태의 반도체 집적회로 장치는 구동기 회로(5)가 동작하고 있을 때는 수신기 회로(10B)도 동작하고 있지만 구동기 회로(5B)와 수신기 회로(10A)는 동작을 정지하고 있다. 또한, 구동기 회로(5B)가 동작하고 있을 때는 수신기 회로(10A)도 동작하고 있지만 구동기 회로(5A)와 수신기 회로(10B)는 동작을 정지하고 있게 된다.Therefore, in the semiconductor integrated circuit device of the present embodiment, when the

이상 설명한 바와 같이 본 실시 형태의 반도체 집적회로 장치에 있어서는 칩사이에서 전송되는 신호는 소진폭이므로 구동기 회로의 전력을 삭감할 수 있으며, 소비 전력을 가급적 적게 할 수 있다.As described above, in the semiconductor integrated circuit device of the present embodiment, since the signal transmitted between the chips is small amplitude, the power of the driver circuit can be reduced and the power consumption can be reduced as much as possible.

또, 본 실시 형태에 있어서는, 칩A 에 바이어스 회로(1A) 및 구동기 회로(5A)로 이루어지는 소진폭 출력 회로와, 분압 회로(9A) 및 수신기 회로(10A)로 이루어지는 소진폭 입력 회로가 설치되고, 칩B 에는 구동기 회로로 이루어지는 소진폭 출력 회로와, 분압 회로(9B) 및 수신기 회로(10B)로 이루어지는 소진폭 입력 회로가 설치되어 있게 된다.In addition, a small amplitude input consisting of In, chip A bias circuit (1 A) and a driver circuit (5 A) small amplitude output circuit, and a voltage dividing circuit (9 A) and a receiver circuit (10 A) formed of a the embodiment and the circuit is installed, the chips B, it is possible with a small amplitude output circuit comprising a driver circuit, a voltage dividing circuit (9 B) and a receiver circuit (10 B) a small amplitude input circuit consisting of are provided.

또한, 본 실시 형태에 있어서는 2개의 칩이 매우 인접한 거리로 배치되고, 그 사이를 본딩 배선으로 접속함으로써 출력 용량은 삭감되며, 또한 칩간 배선과 구동기 회로는 임피던스 정합을 취하지는 않아도 큰 신호 반사는 나타나지 않는다.In this embodiment, the two chips are arranged at very close distances, and the connection capacitance is reduced by connecting them therebetween, so that the signal reflection between the chip-to-chip wiring and the driver circuit does not occur even if impedance matching is not achieved. Do not.

또, 상기 실시 형태에 있어서, 칩B 상에 바이어스 회로를 설치하는 것이 가능하다. 이 경우 본딩 배선(61)은 불필요해진다. 그리고 이 경우, 칩A 와 칩B 는 동일 전원을 사용하여도 좋고, 다른 전원을 사용하는 것도 가능하다.In the above embodiment, it is possible to provide a bias circuit on the chip B. In this case, the

또한, 상기 실시 형태에 있어서는 칩사이를 본딩 배선으로 접속하였지만, 기판 배선으로 직접 접속하여도 좋다.In addition, in the said embodiment, although the chip was connected by the bonding wiring, you may connect directly by the board wiring.

이어서 본 발명에 따른 반도체 집적회로 장치의 제 8 실시 형태의 구성을 도 13에 도시한다. 본 실시 형태의 반도체 집적회로 장치는 매우 인접한 거리로 배치된 2개의 반도체칩 A,B 에 각각 소진폭 입력 회로 및 소진폭 출력 회로를 설치한 것이다. 칩A 의 소진폭 출력 회로는 바이어스 회로(1A) 및 구동기 회로(5A)로 이루어져 있고, 소진폭 입력 회로는 수신기 회로(10A)로 이루어져 있다. 또한 칩B 의 소진폭 출력 회로는 바이어스 회로(1B) 및 구동기 회로로 이루어져 있고, 소진폭 입력 회로는 수신기 회로(10B)로 이루어져 있다.Next, the structure of 8th Embodiment of the semiconductor integrated circuit device which concerns on this invention is shown in FIG. In the semiconductor integrated circuit device of this embodiment, a small amplitude input circuit and a small amplitude output circuit are provided on two semiconductor chips A and B arranged at very close distances, respectively. The small amplitude output circuit of chip A consists of a

바이어스 회로(1A,1B) 및 구동기 회로(5A,5B)는 도 5에 도시되는 제 4 실시 형태의 바이어스 회로(1) 및 구동기 회로(5)와 동일한 구성으로 되어 있다. 그리고 구동기 회로(5A)의 2개의 출력은 칩A 에 설치된 패드(53A,54A)에 각각 접속된다. 또한 구동기 회로(5B)의 2개의 출력은 칩B 에 설치된 패드(53B,54B)에 각각 접속된다. 또한 칩A 의 패드(53A)와 칩B 의 패드(53B)는 본딩 배선(63)에 의해서 접속되고, 칩A 의 패드(54A)와 칩B 의 패드(54B)는 본딩 배선(64)에 의해 접속되어 있다.The

한편 수신기 회로(10A)는 본딩 배선(63,64)을 통해 전송되는 구동기 회로(5B)의 소진폭화된 차동 출력을 감지증폭 회로에서 검출하여 구동 전위 VDD와 접지 전위 GND 사이에서 진동하는 신호로 변환한다. 또한, 수신기 회로(10B)는 본딩 배선(63,64)을 통해 전송되는 구동기 회로(5A)의 소진폭화된 차동 출력을 감지증폭 회로에서 검출하여, 구동 전위 VDD와 접지 전위 GND 사이에서 진동하는 신호로 변환한다.On the other hand, the

따라서, 본 실시 형태의 반도체 집적회로 장치는 구동기 회로(5A)가 동작하고 있을 때는 수신기 회로(10B)도 동작하고 있지만 구동기 회로(5B)와 수신기 회로(10A)는 동작을 정지하고 있다. 또한, 구동기 회로(5B)가 동작하고 있을 때는 수신기 회로(10A)도 동작하고 있지만 구동기 회로(5A)와 수신기 회로(10B)는 동작을 정지하게 된다.Therefore, the semiconductor integrated circuit device of this embodiment also operates the

이상 설명한 바와 같이 본 실시 형태의 반도체 집적회로 장치에 있어서는 칩사이에서 전송되는 신호는 소진폭이므로 구동기 회로의 전력을 삭감하는 것이 가능해지고, 소비 전력을 가급적 적게 할 수 있다.As described above, in the semiconductor integrated circuit device of the present embodiment, the signal transmitted between the chips has a small amplitude, so that the power of the driver circuit can be reduced, and the power consumption can be reduced as much as possible.

또한, 본 실시 형태에 있어서는 2개의 칩이 매우 인접한 거리로 배치되고 그 사이를 본딩 배선으로 접속함으로써, 출력 용량은 삭감되며, 또한 칩간 배선과 구동기 회로는 임피던스 정합을 취하지 않아도 큰 신호 반사가 나타나지 않는다.In this embodiment, the two chips are arranged at very close distances and connected therebetween by bonding wiring, so that the output capacitance is reduced, and the large signal reflection does not appear even when the chip-to-chip wiring and the driver circuit do not have impedance matching. .

또한, 상기 제 8 실시 형태에 있어서는 칩A 와 칩B 는 동일한 전원을 사용하였지만 다른 전원을 사용하는 것도 가능하다.In addition, in the eighth embodiment, although the chip A and the chip B used the same power source, it is also possible to use different power sources.

또, 제 7 및 제 8 실시 형태의 반도체 집적회로 장치에 있어서는 본딩 배선이 이루어진 반도체칩 A, B 는 동일한 리드 프레임대에 얹어 놓은 후 수지 밀봉할 수도 있다.In the semiconductor integrated circuit devices of the seventh and eighth embodiments, the semiconductor chips A and B having the bonding wirings may be resin-sealed after being placed on the same lead frame stage.

이어서 본 발명에 따른 반도체 집적회로 장치의 제 9 실시 형태를 도 14 내지 도 15를 참조하여 설명한다.Next, a ninth embodiment of a semiconductor integrated circuit device according to the present invention will be described with reference to FIGS. 14 to 15.

이 제 9 실시 형태의 반도체 집적회로 장치의 전체의 구성을 도 14에 도시한다. 본 실시 형태의 반도체 집적회로 장치는 일렬로 배치된 복수의 반도체칩(721,…,72n)을 본딩 배선(77)으로 접속한 것이다. 반도체칩(721)은 패드(74)를 갖고, 반도체칩(72i)(i=2,…,n-1)은 패드(74,75)를 가지며, 반도체칩(72n)은 패드(75)를 갖고 있다. 그리고, 인접하는 반도체칩(72i)(1=2,…,n-1)와 반도체칩(72i+1)은 매우 인접한 거리로 놓여지고, 반도체칩(72i)의 패드(74)와 반도체칩(72i+1)의 패드(75)는 본딩 배선(77)에 의해 접속되어 있다.The whole structure of the semiconductor integrated circuit device of this ninth embodiment is shown in FIG. In the semiconductor integrated circuit device of this embodiment, a plurality of

그리고, 단부의 반도체칩(721과 72n)에는 각각 도 15a에 도시된 바와 같은 반도체칩(85)의 구성을 가지고 있고, 이 칩(85)에는 기능 블록(86)과, 소진폭 입출력 회로(87)와, 패드(88)가 설치되어 있다. 소진폭 입출력 회로(87)는 도 12 또는 도 13에 도시된 제 7 또는 제 8 실시 형태의 소진폭 입력 회로 및 소진폭 출력 회로로 이루어져 있다. 또, 제 8 실시 형태의 소진폭 입력 회로 및 소진폭 출력 회로가 사용되는 경우는 패드(88)는 2개 필요해진다.The semiconductor chips 72 1 and 72 n at the end each have a structure of a

또한 도 14에 도시된 단부 이외의 각 반도체칩(72i)(i=2,…,n-1)는 도 15b에 도시된 바와 같은 반도체칩(90)의 구성을 가지고 있고, 이 칩(90)은 소진폭 입출력 회로(91)와 스위치 회로(92)와, 기능 블록(93)과, 소진폭 입출력 회로(94)와, 패드(95,95)를 갖고 있다. 소진폭 입출력 회로(91 및 94)는 각각 도 15a 에 도시된 소진폭 입출력 회로(87)와 동일한 구성으로 되어 있다.Each semiconductor chip 72 i (i = 2, ..., n-1) other than the end shown in FIG. 14 has the configuration of the

이어서 본 실시 형태의 구성과 동작을 설명한다. 우선, 단부의 반도체칩(721또는 72n)에 있어서는 도 15a에 도시된 바와 같이, 기능 블록(86)의 출력 신호는 소진폭 입출력 회로(87)에 의해서 소진폭 신호로 변환되어, 패드(88), 본딩 배선(89)을 통해 인접하는 반도체칩으로 송출된다. 또한 인접하는 반도체칩으로부터 본딩 배선(89)을 통해 전송된 소진폭 신호는 패드(88)를 통해 소진폭 입출력 회로(87)에 입력 증폭되고 대진폭 신호로 변환되어 기능 블록(86)으로 송출된다.Next, the structure and operation | movement of this embodiment are demonstrated. First, in the

또한, 단부 이외의 각 반도체칩(72i)(i=2,…,n-1)에 있어서는, 도 15b 에 도시된 바와 같이, 인접하는 반도체칩으로부터 예컨대 패드(95)를 통해 전송되는 소진폭 신호는 소진폭 입출력 회로(91)에 의해 증폭되며, 대진폭 신호로 변환되어 스위치 회로(92)로 전송된다. 그리고 이 대진폭 신호는 도시하지 않은 제어 신호에 기초하여 스위치 회로(92)에 의해 기능 블록(93)으로 전송되거나 또는 바이패스되어 소진폭 입출력 회로(94)로 전송되도록 선택된다. 소진폭 입출력 회로(94)에 전송되는 대진폭 신호는 소진폭 신호로 변환되어 패드(96),본딩 배선(99)을 통해 인접하는 반도체칩으로 송출된다.In addition, in each semiconductor chip 72 i (i = 2, ..., n-1) other than the end portion, as shown in FIG. 15B, the small amplitude transmitted from the adjacent semiconductor chip through the

또, 상기 제어 신호는 외부 또는 다른 반도체칩으로부터 전송된다.The control signal is also transmitted from an external or other semiconductor chip.

또한 기능 블록(93)에 대진폭 신호가 전송되는 경우는 소정의 처리가 행해지고, 이 처리의 결과에 기초하여 다른 반도체칩에 신호를 송출할 필요가 있는 경우는 스위치 회로(92)를 통해 소진폭 입출력 회로(91) 또는 소진폭 입출력 회로(94)로 전송된다. 그리고 소진폭 입출력 회로(91) 또는 소진폭 입출력 회로(94)에 의해서 소진폭 신호로 변환되어 본딩 배선(98) 또는 본딩 배선(99)을 통해 인접하는 반도체칩에 송출된다. 또, 기능 블록은 CPU 또는 메모리 등에 상당하는 것으로 소정의 처리 기능을 갖고 있다.When a large amplitude signal is transmitted to the

또한, 패드(96)를 통해 인접하는 반도체칩으로부터 전송되는 소진폭 신호는 소진폭 입출력 회로(94)에 의해서 대진폭 신호에 변환된다. 그리고 이 대진폭 신호는 도시하지 않은 제어 신호에 기초하여 스위치 회로(92)에 의해 기능 블록(93)에 전송되거나 또는 바이패스되어 소진폭 입출력 회로(9l)에 보내어지도록 선택된다. 소진폭 입출력 회로(91)에 보내어진 대진폭 신호는 소진폭 신호로 변환되고, 패드(95), 본딩 배선(98)을 통해 인접하는 반도체칩으로 송출된다.Further, the small amplitude signal transmitted from the adjacent semiconductor chip via the

이상 설명한 바와 같이 제 9 실시 형태의 반도체 집적회로 장치에 따르면, 반도체칩 사이에서 전송되는 신호는 소진폭 신호이므로 소진폭 입출력 회로내의 구동기 회로의 전력을 삭감하는 것이 가능해지고, 소비 전력을 가급적 적게 할 수 있다.As described above, according to the semiconductor integrated circuit device of the ninth embodiment, since the signal transmitted between the semiconductor chips is a small amplitude signal, it is possible to reduce the power of the driver circuit in the small amplitude input / output circuit and to reduce the power consumption as much as possible. Can be.

또, 본 실시 형태의 반도체 집적회로 장치에 있어서는, 복수의 반도체칩은 본딩 배선이 이루어진 후, 동일한 리드 프레임 대에 얹어 놓고 수지 밀봉하는 것도 가능하다.In the semiconductor integrated circuit device of the present embodiment, the plurality of semiconductor chips can be placed on the same lead frame stage and resin-sealed after bonding wiring has been made.

이 제 9 실시 형태의 반도체 집적회로 장치에 이용되는 스위치 회로(92)의 구체적인 구성의 일례를 도 16에 도시한다. 이 스위치 회로(92)는 도 16a에 도시된 바와 같이 3개의 스위치 소자(101,102,103)로 이루어져 있다. 스위치 소자(101)는 제어 신호 S12에 기초하여 노드 N1과 노드 N2를 접속하고, 스위치 소자(102)는 제어 신호 S23에 기초하여 노드 N2과 노드 N3을 접속하며, 스위치 소자(103)는 제어 신호 S31에 기초하여 노드 N3과 노드 N1을 접속한다.An example of the specific structure of the

그리고 각 스위치 소자는 도 16b에 도시된 바와 같이 인버터 회로(105)와, P 채널 MOS 트랜지스터(106) 및 N 채널 MOS 트랜지스터(107)로 이루어진 트랜스퍼 게이트를 갖고 있다. 제어 신호 S는 N 채널 MOS 트랜지스터(107)의 게이트로 전송되는 동시에 인버터 회로(105)를 통해 P 채널 MOS 트랜지스터(106)의 게이트로 전송된다.Each switch element has an

따라서, 도 16a에 있어서, 제어 신호 S12의 값이 「1」이고 다른 제어 신호 S23, S31의 값이「0」인 경우에는 노드 N1과 노드 N2가 접속되고, 제어 신호 S23의 값이 「l」이고 다른 제어 신호 S31, S12의 값이 「0」인 경우에는 노드 N2와 노드 N3이 접속되며, 제어 신호 S31의 값이 「1」이고 다른 제어 신호 S12, S23의 값이 「0」인 경우는 노드 N3과 노드 N1이 접속된다.(도 16c 참조).Therefore, in FIG. 16A, when the value of the control signal S 12 is "1" and the values of the other control signals S 23 and S 31 are "0", the node N 1 and the node N 2 are connected, and the control signal S 23. When the value of "l" and the value of the other control signals S 31 and S 12 are "0", the node N 2 and the node N 3 are connected, and the value of the control signal S 31 is "1" and the other control signal S is When the values of 12 and S 23 are "0", the node N 3 and the node N 1 are connected (see FIG. 16C).

이어서 상기 제 9 실시 형태의 반도체 집적회로 장치의 제 1 변형예의 구성을 도 17에 도시한다. 이 변형예의 반도체 집적회로 장치는 CPU로 이루어진 반도체칩(81)과, 복수의 메모리(821,…,82n)를 일렬로 근접하여 배치하고, 본딩 배선으로 접속한 것이다.Next, FIG. 17 shows a configuration of a first modification of the semiconductor integrated circuit device of the ninth embodiment. In the semiconductor integrated circuit device of this modification, a

이 제 1 변형예의 반도체 집적회로 장치에 있어서는, 소비 전력을 적게 할 수 있는 동시에, CPU가 대용량의 데이터를 고속으로 액세스하는 것이 가능해진다.In the semiconductor integrated circuit device of the first modification, the power consumption can be reduced and the CPU can access a large amount of data at high speed.

이어서 상기 제 9 실시 형태의 반도체 집적회로 장치의 제 2 변형예의 구성을 도 18에 도시한다. 이 변형예의 반도체 집적회로 장치는 멀티 CPU 구성의 반도체 집적회로 장치로서, 복수의 CPU(811,…,81n)과 메모리(82)를 일렬로 근접하여 배치하고, 본딩 배선에 의해 접속되어 있다.Next, FIG. 18 shows a configuration of a second modification of the semiconductor integrated circuit device of the ninth embodiment. The semiconductor integrated circuit device of this modified example is a semiconductor integrated circuit device having a multi-CPU configuration, where a plurality of

이 제 2 변형예의 반도체 집적회로 장치도 소비 전력을 적게 할 수 있는 것은 말할 필요도 없다.It goes without saying that the semiconductor integrated circuit device of this second modification can also reduce power consumption.

이어서 본 발명에 따른 반도체 집적회로 장치의 제 10 실시 형태를 도 19를 참조하여 설명한다. 본 실시 형태의 반도체 집적회로 장치는 도 14에 도시된 제 9 실시 형태의 반도체 집적회로 장치에 있어서, 단부 이외의 각 반도체칩(72i)(i=2, …,n-1)이 도 19에 도시된 바와 같은 구성으로 되어 있다. 즉, 이 반도체칩은 소진폭 입출력 회로(91)와, 셀렉터(92a,92b)와, 버스(92c)와, 기능 블록(93)과, 소진폭 입출력 회로(94)와, 패드(95,95)를 구비하고 있다.Next, a tenth embodiment of a semiconductor integrated circuit device according to the present invention will be described with reference to FIG. In the semiconductor integrated circuit device of this embodiment, in the semiconductor integrated circuit device of the ninth embodiment shown in FIG. 14, each semiconductor chip 72i (i = 2, ..., n-1) other than the end portion is shown in FIG. It is configured as shown. That is, the semiconductor chip includes the small amplitude input /

이 소진폭 입출력 회로(91,94)는 도 15a에 도시된 소진폭 입출력 회로(87)와 동일한 구성으로 되어 있다.The small amplitude input /

도 19에 있어서, 본딩 배선(98)을 통해 인접하는 반도체칩으로부터 전송되는 소진폭 신호는 소진폭 입출력 회로(91)에 의해서 검출되고, 예컨대 구동 전위 VDD와 접지 전위 GND와의 사이에서 진동하는 대진폭 신호로 변환되어 셀렉터(92)로 전송된다. 이 대진폭 신호는 셀렉터(92)에 의해서 기능 블록(93)으로 전송되거나 또는 바이패스되어 버스(92c), 셀렉터(92b)를 통해 소진폭 입출력 회로(94)에 전송되도록 도시하지 않은 제어 신호에 기초하여 선택된다. 그리고 소진폭 입출력 회로(94)에 전송되는 대진폭 신호는 소진폭 입출력 회로(94)에 의해서 소진폭 신호로 변화되어 패드(96), 본딩 배선(99)을 통해 인접하는 반도체칩으로 송출된다.In Fig. 19, the small amplitude signal transmitted from the adjacent semiconductor chip via the

또한, 본딩 배선(99)을 통해 인접하는 반도체칩으로부터 전송되는 소진폭 신호는 소진폭 입출력 회로(94)에 의해 검출되어 대진폭 신호로 변환되며, 셀렉터(92b)로 전송된다. 이 대진폭 신호는 셀렉터(92b)에 의해서 기능 블록(93)으로 보내어지거나 또는 바이패스되어 버스(92c), 셀렉터(92a)를 통해 소진폭 입출력 회로(91)에 전송되도록 도시하지 않은 제어 신호에 기초하여 선택된다. 그리고 소진폭 입출력 회로(91)에 보내어진 대진폭 신호는 소진폭 입출력 회로(91)에 의해서 소진폭 신호로 변환되어 패드(95), 본딩 배선(98)을 통해 인접하는 반도체칩으로 송출된다.Further, the small amplitude signal transmitted from the adjacent semiconductor chip through the

이 제 10 실시 형태의 반도체 집적회로 장치에 따르면 전송되는 신호는 소진폭 신호이므로, 소진폭 입출력 회로내의 구동기 회로의 전력을 삭감하는 것이 가능해지며, 소비 전력을 가급적 적게 할 수 있다.According to the semiconductor integrated circuit device of the tenth embodiment, since the transmitted signal is a small amplitude signal, it is possible to reduce the power of the driver circuit in the small amplitude input / output circuit, and to reduce the power consumption as much as possible.

이어서 본 발명에 따른 반도체 집적회로 장치의 제 11 실시 형태를 도 20에 도시한다. 본 실시 형태의 반도체 집적회로 장치는 도 19에 도시된 제 10 실시 형태의 반도체 집적회로 장치에 있어서, 바이패스용 버스(92c)의 양단에 소진폭 입출력 회로(110,111)를 설치한 것으로, 버스(92c)의 용량이 클 경우에 사용된다. 이러한 구성으로 함으로써 더욱 소비 전력을 적게 할 수 있다.Next, an eleventh embodiment of a semiconductor integrated circuit device according to the present invention is shown in FIG. The semiconductor integrated circuit device of the present embodiment is the semiconductor integrated circuit device of the tenth embodiment shown in FIG. 19, in which small amplitude input /

이어서 본 발명에 따른 반도체 집적회로 장치의 제 12 실시 형태의 구성을 도 21에 도시한다. 본 실시 형태의 반도체 집적회로 장치는 매트릭스형으로 배치된 4개의 반도체칩(l2011,12012,12021,12022)을 본딩 배선으로 접속한 것이다.Next, the structure of 12th Embodiment of the semiconductor integrated circuit device which concerns on this invention is shown in FIG. In the semiconductor integrated circuit device of this embodiment, four semiconductor chips l20 11 , 120 12 , 120 21 , and 120 22 arranged in a matrix form are connected by bonding wiring.

각 반도체칩(l20ij)(i,j=1,2)은 예컨대 도 15b에 도시된 구성을 갖고 있다. 즉, 각 반도체칩은 소진폭 입출력 회로(91,94)와, 스위치 회로(92)와, 기능 블록(93)과, 패드(95,96)를 구비하고 있다. 따라서, 반도체칩 사이에서 전송되는 신호는 소진폭 신호이므로, 소진폭 입출력 회로내의 구동기 회로의 전력을 삭감하는 것이 가능해지며, 소비 전력을 가급적 적게 할 수 있다.Each semiconductor chip l20 ij (i, j = 1,2) has the configuration shown in Fig. 15B, for example. That is, each semiconductor chip includes the small amplitude input /

또, 본 실시 형태의 반도체 집적회로 장치에 있어서는, 복수의 반도체칩은 본딩 배선이 이루어진 후, 동일한 리드 프레임 대에 놓고 수지 밀봉할 수도 있다.In the semiconductor integrated circuit device of the present embodiment, the plurality of semiconductor chips may be placed on the same lead frame band and resin-sealed after bonding wiring is formed.

이어서 본 발명에 따른 반도체 집적회로 장치의 제 13 실시 형태의 구성을 도 22에 도시한다. 본 실시 형태의 반도체 집적회로 장치는 매트릭스형으로 배치된 복수(m·n개)의 반도체칩(13011,l3012,…,l30mn)을 본딩 배선으로 접속한 것이다. 4각으로 배치된 반도체칩(13011,1301n,…,130ml,130mn)은 각각 전술한 도 15b에 도시된 구성을 갖고 있다.Next, the structure of 13th Embodiment of the semiconductor integrated circuit device which concerns on this invention is shown in FIG. In the semiconductor integrated circuit device of the present embodiment, a plurality of (m · n)

또한, 인접 배치된 반도체칩(130il(i=2,…,m-1), 1301j(j=2,…,n-1), 130mk(k=2,…,n-1), 및 130gn(g=2,…,m-1))은 도 23b에 도시된 구성을 갖고 있다. 즉, 각 반도체칩은 3개의 소진폭 입출력 회로(151,152,153)과, 스위치 회로(155)와, 기능 블록(156)과, 3개의 패드(1571,…,1573)를 갖고 있다. 패드(1571)는 소진폭 입출력 회로(151)에 접속되고, 패드(1572)는 소진폭 입출력 회로(152)에 접속되며, 패드(1573)는 소진폭 입출력 회로(153)에 접속되어 있다. 그리고 이들 패드(157i)(i=1,2,3)는 본딩 배선을 통해 인접하는 반도체칩에 접속되어 있다.In addition, adjacent semiconductor chips 130 il (i = 2, ..., m-1), 130 1j (j = 2, ..., n-1), 130 mk (k = 2, ..., n-1), And 130 gn (g = 2, ..., m-1) have the configuration shown in Fig. 23B. That is, each of the semiconductor chips has a three-amplitude input and output circuit (151 152 153), a switch circuit 155, and a

패드(1571,1572,1573)를 통해 인접하는 반도체칩으로부터 전송되는 소진폭 신호는 소진폭 입출력 회로(151,152,153)에 의해 검출되고, 예컨대 구동 전위 VDD와 접지 전원과의 사이에서 진동하는 신호(대진폭 신호)로 변환되어 스위치 회로(155)로 전송된다. 그리고 이 대진폭 신호는 스위치 회로(155)에 의해 기능 블록(156)으로 전송되거나 또는 바이패스되어 다른 소진폭 입출력 회로로 전송되도록 도시하지 않은 제어 신호에 기초하여 선택된다. 소진폭 입출력 회로로 보내어진 대진폭 신호는 이 소진폭 입출력 회로에 의해서 소진폭 신호로 변환되고, 대응하는 패드, 본딩 배선을 통해 인접하는 반도체칩으로 송출된다.The small amplitude signals transmitted from the adjacent semiconductor chips through the pads 157 1 , 157 2 , and 157 3 are detected by the small amplitude input /

또한 기능 블록(156)으로 대진폭 신호가 전송되는 경우는 소정의 처리가 행해진다. 기능 블록(156)의 출력은 스위치 회로(155)를 통해 소진폭 입출력 회로로 전송되고, 소진폭 신호로 변환되어 대응하는 패드를 통해 인접하는 반도체칩으로 송출된다.In addition, when a large amplitude signal is transmitted to the