JP7299836B2 - Iii-v族材料を含む素子およびシリコン処理工程と互換性を有する接触部を形成する処理 - Google Patents

Iii-v族材料を含む素子およびシリコン処理工程と互換性を有する接触部を形成する処理 Download PDFInfo

- Publication number

- JP7299836B2 JP7299836B2 JP2019528511A JP2019528511A JP7299836B2 JP 7299836 B2 JP7299836 B2 JP 7299836B2 JP 2019528511 A JP2019528511 A JP 2019528511A JP 2019528511 A JP2019528511 A JP 2019528511A JP 7299836 B2 JP7299836 B2 JP 7299836B2

- Authority

- JP

- Japan

- Prior art keywords

- contact

- forming

- opening

- iii

- dielectric

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000000463 material Substances 0.000 title claims description 182

- 238000000034 method Methods 0.000 title claims description 171

- 230000008569 process Effects 0.000 title claims description 150

- 229910052710 silicon Inorganic materials 0.000 title claims description 71

- 239000010703 silicon Substances 0.000 title claims description 70

- 238000012545 processing Methods 0.000 title claims description 60

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 title description 69

- 239000002184 metal Substances 0.000 claims description 156

- 238000001465 metallisation Methods 0.000 claims description 152

- 229910052751 metal Inorganic materials 0.000 claims description 150

- 238000000151 deposition Methods 0.000 claims description 125

- 230000008021 deposition Effects 0.000 claims description 99

- 230000004888 barrier function Effects 0.000 claims description 69

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 50

- 229910000765 intermetallic Inorganic materials 0.000 claims description 48

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 claims description 44

- 229910052759 nickel Inorganic materials 0.000 claims description 42

- 230000015572 biosynthetic process Effects 0.000 claims description 39

- 238000010438 heat treatment Methods 0.000 claims description 39

- 239000000758 substrate Substances 0.000 claims description 39

- 229910004541 SiN Inorganic materials 0.000 claims description 34

- 229920000642 polymer Polymers 0.000 claims description 33

- 229910045601 alloy Inorganic materials 0.000 claims description 30

- 239000000956 alloy Substances 0.000 claims description 30

- 229910052719 titanium Inorganic materials 0.000 claims description 28

- 229910052681 coesite Inorganic materials 0.000 claims description 25

- 229910052906 cristobalite Inorganic materials 0.000 claims description 25

- 238000009792 diffusion process Methods 0.000 claims description 25

- 239000000377 silicon dioxide Substances 0.000 claims description 25

- 235000012239 silicon dioxide Nutrition 0.000 claims description 25

- 229910052682 stishovite Inorganic materials 0.000 claims description 25

- 229910052905 tridymite Inorganic materials 0.000 claims description 25

- 238000005538 encapsulation Methods 0.000 claims description 23

- 229910052802 copper Inorganic materials 0.000 claims description 22

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 claims description 21

- 229910016570 AlCu Inorganic materials 0.000 claims description 19

- 229910000789 Aluminium-silicon alloy Inorganic materials 0.000 claims description 19

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 claims description 19

- 229910052593 corundum Inorganic materials 0.000 claims description 19

- 229910001845 yogo sapphire Inorganic materials 0.000 claims description 19

- 229910052721 tungsten Inorganic materials 0.000 claims description 18

- 229910006137 NiGe Inorganic materials 0.000 claims description 17

- 239000004065 semiconductor Substances 0.000 claims description 17

- 229910052738 indium Inorganic materials 0.000 claims description 14

- 239000007769 metal material Substances 0.000 claims description 14

- 229910003266 NiCo Inorganic materials 0.000 claims description 13

- 229910001000 nickel titanium Inorganic materials 0.000 claims description 13

- 239000003989 dielectric material Substances 0.000 claims description 12

- 229910001218 Gallium arsenide Inorganic materials 0.000 claims description 10

- 229910052782 aluminium Inorganic materials 0.000 claims description 9

- 229910005542 GaSb Inorganic materials 0.000 claims description 7

- 229910000673 Indium arsenide Inorganic materials 0.000 claims description 7

- 239000000945 filler Substances 0.000 claims description 7

- RPQDHPTXJYYUPQ-UHFFFAOYSA-N indium arsenide Chemical compound [In]#[As] RPQDHPTXJYYUPQ-UHFFFAOYSA-N 0.000 claims description 7

- 239000010410 layer Substances 0.000 description 130

- 238000005530 etching Methods 0.000 description 61

- 238000005229 chemical vapour deposition Methods 0.000 description 44

- 238000005240 physical vapour deposition Methods 0.000 description 43

- 238000001312 dry etching Methods 0.000 description 40

- 150000002739 metals Chemical class 0.000 description 34

- 238000005755 formation reaction Methods 0.000 description 33

- 238000000231 atomic layer deposition Methods 0.000 description 30

- 239000011347 resin Substances 0.000 description 25

- 229920005989 resin Polymers 0.000 description 25

- 239000012071 phase Substances 0.000 description 23

- 230000006641 stabilisation Effects 0.000 description 22

- 238000011105 stabilization Methods 0.000 description 22

- 238000000206 photolithography Methods 0.000 description 21

- 238000000137 annealing Methods 0.000 description 20

- 229910004298 SiO 2 Inorganic materials 0.000 description 18

- 230000010354 integration Effects 0.000 description 17

- 238000001039 wet etching Methods 0.000 description 17

- 238000003746 solid phase reaction Methods 0.000 description 15

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 14

- 230000006911 nucleation Effects 0.000 description 14

- 238000010899 nucleation Methods 0.000 description 14

- 238000010671 solid-state reaction Methods 0.000 description 14

- 238000001211 electron capture detection Methods 0.000 description 13

- -1 NiPt Inorganic materials 0.000 description 12

- 150000001875 compounds Chemical class 0.000 description 11

- RQKYYWBMXHYBAP-UHFFFAOYSA-N 4-(chloromethyl)-2,2-dimethyl-1,3,2-dioxasilolane Chemical compound C[Si]1(C)OCC(CCl)O1 RQKYYWBMXHYBAP-UHFFFAOYSA-N 0.000 description 10

- 230000009977 dual effect Effects 0.000 description 10

- 235000012431 wafers Nutrition 0.000 description 8

- 229910000530 Gallium indium arsenide Inorganic materials 0.000 description 7

- 230000007547 defect Effects 0.000 description 7

- 238000001459 lithography Methods 0.000 description 7

- 239000010970 precious metal Substances 0.000 description 7

- 230000008439 repair process Effects 0.000 description 7

- 238000012876 topography Methods 0.000 description 7

- 230000005684 electric field Effects 0.000 description 5

- 239000011521 glass Substances 0.000 description 5

- 238000010521 absorption reaction Methods 0.000 description 4

- 238000005119 centrifugation Methods 0.000 description 4

- 239000013078 crystal Substances 0.000 description 4

- 230000003287 optical effect Effects 0.000 description 4

- 238000005498 polishing Methods 0.000 description 4

- 239000000243 solution Substances 0.000 description 3

- 229910000980 Aluminium gallium arsenide Inorganic materials 0.000 description 2

- BYFGZMCJNACEKR-UHFFFAOYSA-N aluminium(i) oxide Chemical compound [Al]O[Al] BYFGZMCJNACEKR-UHFFFAOYSA-N 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 230000007246 mechanism Effects 0.000 description 2

- 230000005012 migration Effects 0.000 description 2

- 238000013508 migration Methods 0.000 description 2

- 239000013307 optical fiber Substances 0.000 description 2

- 230000005855 radiation Effects 0.000 description 2

- 239000007787 solid Substances 0.000 description 2

- 238000012546 transfer Methods 0.000 description 2

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 239000007795 chemical reaction product Substances 0.000 description 1

- 230000001627 detrimental effect Effects 0.000 description 1

- 238000000407 epitaxy Methods 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 229910001092 metal group alloy Inorganic materials 0.000 description 1

- 239000011259 mixed solution Substances 0.000 description 1

- 229910000510 noble metal Inorganic materials 0.000 description 1

- 229910052762 osmium Inorganic materials 0.000 description 1

- 239000002243 precursor Substances 0.000 description 1

- 238000012958 reprocessing Methods 0.000 description 1

- 238000012552 review Methods 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/285—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation

- H01L21/28506—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers

- H01L21/28575—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising AIIIBV compounds

- H01L21/28581—Deposition of Schottky electrodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01S—DEVICES USING THE PROCESS OF LIGHT AMPLIFICATION BY STIMULATED EMISSION OF RADIATION [LASER] TO AMPLIFY OR GENERATE LIGHT; DEVICES USING STIMULATED EMISSION OF ELECTROMAGNETIC RADIATION IN WAVE RANGES OTHER THAN OPTICAL

- H01S5/00—Semiconductor lasers

- H01S5/04—Processes or apparatus for excitation, e.g. pumping, e.g. by electron beams

- H01S5/042—Electrical excitation ; Circuits therefor

- H01S5/0421—Electrical excitation ; Circuits therefor characterised by the semiconducting contacting layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/02227—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process

- H01L21/0223—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by oxidation, e.g. oxidation of the substrate

- H01L21/02233—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by oxidation, e.g. oxidation of the substrate of the semiconductor substrate or a semiconductor layer

- H01L21/02241—III-V semiconductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/285—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation

- H01L21/28506—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers

- H01L21/28575—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising AIIIBV compounds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/482—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of lead-in layers inseparably applied to the semiconductor body

- H01L23/485—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of lead-in layers inseparably applied to the semiconductor body consisting of layered constructions comprising conductive layers and insulating layers, e.g. planar contacts

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/45—Ohmic electrodes

- H01L29/452—Ohmic electrodes on AIII-BV compounds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/005—Processes

- H01L33/0062—Processes for devices with an active region comprising only III-V compounds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/50—Wavelength conversion elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/50—Wavelength conversion elements

- H01L33/501—Wavelength conversion elements characterised by the materials, e.g. binder

- H01L33/502—Wavelength conversion materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01S—DEVICES USING THE PROCESS OF LIGHT AMPLIFICATION BY STIMULATED EMISSION OF RADIATION [LASER] TO AMPLIFY OR GENERATE LIGHT; DEVICES USING STIMULATED EMISSION OF ELECTROMAGNETIC RADIATION IN WAVE RANGES OTHER THAN OPTICAL

- H01S5/00—Semiconductor lasers

- H01S5/02—Structural details or components not essential to laser action

- H01S5/022—Mountings; Housings

- H01S5/0233—Mounting configuration of laser chips

- H01S5/02345—Wire-bonding

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01S—DEVICES USING THE PROCESS OF LIGHT AMPLIFICATION BY STIMULATED EMISSION OF RADIATION [LASER] TO AMPLIFY OR GENERATE LIGHT; DEVICES USING STIMULATED EMISSION OF ELECTROMAGNETIC RADIATION IN WAVE RANGES OTHER THAN OPTICAL

- H01S5/00—Semiconductor lasers

- H01S5/10—Construction or shape of the optical resonator, e.g. extended or external cavity, coupled cavities, bent-guide, varying width, thickness or composition of the active region

- H01S5/18—Surface-emitting [SE] lasers, e.g. having both horizontal and vertical cavities

- H01S5/183—Surface-emitting [SE] lasers, e.g. having both horizontal and vertical cavities having only vertical cavities, e.g. vertical cavity surface-emitting lasers [VCSEL]

- H01S5/18344—Surface-emitting [SE] lasers, e.g. having both horizontal and vertical cavities having only vertical cavities, e.g. vertical cavity surface-emitting lasers [VCSEL] characterized by the mesa, e.g. dimensions or shape of the mesa

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01S—DEVICES USING THE PROCESS OF LIGHT AMPLIFICATION BY STIMULATED EMISSION OF RADIATION [LASER] TO AMPLIFY OR GENERATE LIGHT; DEVICES USING STIMULATED EMISSION OF ELECTROMAGNETIC RADIATION IN WAVE RANGES OTHER THAN OPTICAL

- H01S5/00—Semiconductor lasers

- H01S5/30—Structure or shape of the active region; Materials used for the active region

- H01S5/34—Structure or shape of the active region; Materials used for the active region comprising quantum well or superlattice structures, e.g. single quantum well [SQW] lasers, multiple quantum well [MQW] lasers or graded index separate confinement heterostructure [GRINSCH] lasers

- H01S5/343—Structure or shape of the active region; Materials used for the active region comprising quantum well or superlattice structures, e.g. single quantum well [SQW] lasers, multiple quantum well [MQW] lasers or graded index separate confinement heterostructure [GRINSCH] lasers in AIIIBV compounds, e.g. AlGaAs-laser, InP-based laser

- H01S5/3434—Structure or shape of the active region; Materials used for the active region comprising quantum well or superlattice structures, e.g. single quantum well [SQW] lasers, multiple quantum well [MQW] lasers or graded index separate confinement heterostructure [GRINSCH] lasers in AIIIBV compounds, e.g. AlGaAs-laser, InP-based laser with a well layer comprising at least both As and P as V-compounds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/53204—Conductive materials

- H01L23/53209—Conductive materials based on metals, e.g. alloys, metal silicides

- H01L23/53214—Conductive materials based on metals, e.g. alloys, metal silicides the principal metal being aluminium

- H01L23/53223—Additional layers associated with aluminium layers, e.g. adhesion, barrier, cladding layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/53204—Conductive materials

- H01L23/53209—Conductive materials based on metals, e.g. alloys, metal silicides

- H01L23/53228—Conductive materials based on metals, e.g. alloys, metal silicides the principal metal being copper

- H01L23/53238—Additional layers associated with copper layers, e.g. adhesion, barrier, cladding layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/53204—Conductive materials

- H01L23/53209—Conductive materials based on metals, e.g. alloys, metal silicides

- H01L23/53257—Conductive materials based on metals, e.g. alloys, metal silicides the principal metal being a refractory metal

- H01L23/53266—Additional layers associated with refractory-metal layers, e.g. adhesion, barrier, cladding layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/1443—Devices controlled by radiation with at least one potential jump or surface barrier

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01S—DEVICES USING THE PROCESS OF LIGHT AMPLIFICATION BY STIMULATED EMISSION OF RADIATION [LASER] TO AMPLIFY OR GENERATE LIGHT; DEVICES USING STIMULATED EMISSION OF ELECTROMAGNETIC RADIATION IN WAVE RANGES OTHER THAN OPTICAL

- H01S5/00—Semiconductor lasers

- H01S5/02—Structural details or components not essential to laser action

- H01S5/0206—Substrates, e.g. growth, shape, material, removal or bonding

- H01S5/021—Silicon based substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01S—DEVICES USING THE PROCESS OF LIGHT AMPLIFICATION BY STIMULATED EMISSION OF RADIATION [LASER] TO AMPLIFY OR GENERATE LIGHT; DEVICES USING STIMULATED EMISSION OF ELECTROMAGNETIC RADIATION IN WAVE RANGES OTHER THAN OPTICAL

- H01S5/00—Semiconductor lasers

- H01S5/10—Construction or shape of the optical resonator, e.g. extended or external cavity, coupled cavities, bent-guide, varying width, thickness or composition of the active region

- H01S5/1028—Coupling to elements in the cavity, e.g. coupling to waveguides adjacent the active region, e.g. forward coupled [DFC] structures

- H01S5/1032—Coupling to elements comprising an optical axis that is not aligned with the optical axis of the active region

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01S—DEVICES USING THE PROCESS OF LIGHT AMPLIFICATION BY STIMULATED EMISSION OF RADIATION [LASER] TO AMPLIFY OR GENERATE LIGHT; DEVICES USING STIMULATED EMISSION OF ELECTROMAGNETIC RADIATION IN WAVE RANGES OTHER THAN OPTICAL

- H01S5/00—Semiconductor lasers

- H01S5/10—Construction or shape of the optical resonator, e.g. extended or external cavity, coupled cavities, bent-guide, varying width, thickness or composition of the active region

- H01S5/18—Surface-emitting [SE] lasers, e.g. having both horizontal and vertical cavities

- H01S5/183—Surface-emitting [SE] lasers, e.g. having both horizontal and vertical cavities having only vertical cavities, e.g. vertical cavity surface-emitting lasers [VCSEL]

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Electromagnetism (AREA)

- Optics & Photonics (AREA)

- Ceramic Engineering (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Electrodes Of Semiconductors (AREA)

- Formation Of Insulating Films (AREA)

- Chemical Vapour Deposition (AREA)

Description

-少なくとも1個の誘電体による前記構造のカプセル化を含む、少なくとも1個の誘電体によるカプセル化の一連のステップと、

-前記第1のIII-V族材料および前記第2のIII-V族材料の上に接触底面領域を画定すべく、前記誘電体内に、前記第1のIII-V族材料の表面に少なくとも1個の上側開口および前記第2のIII-V族材料の表面に少なくとも1個の下側開口を形成するステップと、

-前記少なくとも上側開口および前記少なくとも下側開口において接触底面の金属化を実行するステップと、

-少なくとも1個の金属材料による、前記少なくとも上側開口の少なくとも部分的充填および前記少なくとも下側開口の少なくとも部分的充填により、少なくとも1個の上側接触パッドおよび少なくとも1個の下側接触パッドを形成するステップと、

-接触底面の金属化部分および接触パッドが、前記上側接触レベルと接触している前記第1のIII-V族材料の少なくとも1個の上側接触レベルおよび前記下側接触レベルと接触している前記第2のIII-V族材料の少なくとも1個の下側接触部を画定するステップと、

-少なくとも前記上側接触部および少なくとも前記下側接触部を、同一平面内で画定された上面を有するように誘電体に集積するステップを含んでいる。

-接触底面の金属化部分および接触パッドを含む上側開口を起点とする上側接触部と、

-接触底面の金属化部分および接触パッドを含む下側開口を起点とする下側接触部とが画定される。

-純金属、金属合金、金属と非金属元素の合金、

-金属間化合物または半金属(結晶構造である合金とは異なる)

として定義される。

-開口を形成して、当該開口の底面で接触底面の金属化を実行し、次いで前記接触底面の金属化部分と接触する接触パッドを形成すべく前記開口を充填すること、

-または、いわゆる一次開口を形成して、当該開口の底面で接触底面の金属化を実行し、次いで接触パッドを形成すべく誘電体で充填した後で二次開口を画定することにより、複数の接触パッドを一次開口で先に画定された同一の接触底面の金属化部分に接触させること、のいずれかにより2個のIII-V族材料における接触部の形成に想到し得る。

本発明の複数の変型例によれば、当該処理は、少なくとも1個の下側開口、次いで少なくとも1個の上側開口を連続的に形成するステップを含んでいる。

本発明の複数の変型例によれば、III-V族材料の構造、すなわち第1のIII-V族材料の表面に画定された少なくとも1個の上側接触レベル、および第2のIII-V族材料の表面に画定された下側接触レベルを含む構造を含む素子を基板の表面に形成する処理は、

-少なくとも1個の誘電体により前記構造をカプセル化する一連のステップと、

-前記第1のIII-V族材料および前記第2のIII-V族材料の上に接触底面領域を画定すべく誘電体内に少なくとも1個の一次上側開口および少なくとも1個の一次下側開口を形成するステップと、

-前記接触底面領域の上に接触パッドの領域を画定すべく誘電体に少なくとも1個の二次上側開口および少なくとも1個の二次下側開口を形成するステップと、

-少なくとも1個の金属材料により、前記少なくとも一次上側開口、前記少なくとも一次下側開口、前記少なくとも二次上側開口、および前記少なくとも二次下側開口を少なくとも部分的に充填することにより、

・上側接触レベルと接触していて、少なくとも1個の上側接触底面の金属化部分を含む前記第1のIII-V族材料の少なくとも1個の上側接触部および前記金属化部分と接触している少なくとも1個の上側接触パッドと、

・前記下側接触レベルと接触していて、少なくとも1個の下側接触底面の金属化部分を含む前記第2のIII-V族材料の少なくとも1個の下側接触部および前記金属化部分と接触している少なくとも1個の下側接触パッドとを形成するステップと、

-少なくとも前記上側接触部および少なくとも前記下側接触部を、同一平面内で画定された表面を有するように誘電体内に集積するステップとを含んでいる。

-金属化部分で覆われた第1のIII-V族材料および金属化部分で覆われた第2のIII-V族材料を含むアセンブリを誘電体によりカプセル化するステップと、

-第2のIII-V族材料の反対側に少なくとも1個の二次下側開口を形成するステップと、

-前記第1のIII-V族材料の上方に少なくとも1個の二次上側開口を形成して、少なくとも前記二次下側開口の上方に少なくとも1個の追加的な二次下側開口を形成するステップと、

-少なくとも前記二次上側開口、少なくとも1個の追加的な二次下側開口、および少なくとも前記二次下側開口を充填するステップとを含んでいる。

-少なくとも1個の一次上側開口、少なくとも1個の一次中間開口、少なくとも1個の一次下側開口を形成するステップと、

-少なくとも1個の二次上側開口、少なくとも1個の二次中間開口、および少なくとも1個の二次下側開口を形成するステップと、

-前記開口を充填するステップとを含んでいる。

-少なくとも前記二次下側開口は寸法が異なる3個の部分を含み、

-少なくとも前記二次中間開口は寸法が異なる2個の部分を含み、

-少なくとも前記二次上側開口は1個の部分を含んでいる。

-第1の誘電体により前記構造をカプセル化するステップと、

-前記第2のIII-V族材料の上に少なくとも1個の一次下側開口を形成するステップと、

-前記第1の誘電体の表面および前記第2の半導体材料の表面に金属化部分を堆積して、下側接触部の金属化部分および第1のアセンブリを画定するステップと、

-第2の誘電体により前記第1のアセンブリをカプセル化するステップと、

-前記カプセル化された第1のアセンブリを平坦化するステップと、

-前記下側接触底面の金属化部分の上に少なくとも1個の二次下側開口を形成するステップと、

-少なくとも1個の金属材料により前記少なくとも二次下側開口を充填して前記下側接触部の少なくとも1個の接触パッドおよび第2のアセンブリを画定するステップと、

-第3の誘電体により前記第2のアセンブリをカプセル化するステップと、

-前記第1のIII-V族材料の上方に少なくとも1個の一次上側開口を形成するステップと、

-前記第3の誘電材料および前記上側開口の表面に金属化部分を堆積して上側接触底面の金属化部分および第3のアセンブリを画定するステップと、

-第4の誘電体により前記第3のアセンブリをカプセル化するステップと、

-前記第3のアセンブリを平坦化するステップと、

-前記上側接触底面の金属化部分の上方に少なくとも1個の二次上側開口を、および前記下側接触部の少なくとも前記接触パッドの上方に少なくとも1個の上側開口を形成するステップと、

-少なくとも1個の金属材料により、前記上側接触底面の金属化部分上方の前記少なくとも二次上側開口、および前記下側接触部の少なくとも前記接触パッド上方の前記少なくとも上側開口を充填することにより、前記上側接触部および少なくとも前記下側接触部が同一平面内で画定された表面を有するように、上側接触部用の少なくとも1個の上側パッドおよび下側接触パッドの少なくとも1個の延伸部を画定するステップとを含んでいる。

-第1の誘電体により前記構造をカプセル化するステップと、

-前記第1のIII-V族材料まで貫通する少なくとも1個の一次上側開口を形成するステップと、

-前記第1の誘電体の表面、および前記第1の半導体材料の表面に金属化部分を堆積して上側接触部の金属化部分および第1のアセンブリを画定するステップと、

-第2の誘電体により前記第1のアセンブリをカプセル化するステップと、

-前記カプセル化された第1のアセンブリを平坦化するステップと、

-前記上側接触底面の金属化部分の上に少なくとも1個の二次上側開口を形成するステップと、

-少なくとも1個の金属材料により前記少なくとも二次上側開口を充填して、前記上側接触部の少なくとも1個の接触パッドおよび第2のアセンブリを画定するステップと、

-前記第2のIII-V族材料の上方に少なくとも1個の一次下側開口を形成するステップと、

-前記第1の誘電材料、および前記一次下側開口の表面に金属化部分を堆積して、下側接触部の金属化部分および第3のアセンブリを画定するステップと、

-第4の誘電体により前記第3のアセンブリをカプセル化するステップと、

-前記第3を平坦化するステップと、

-前記下側接触部最下層の上方に少なくとも1個の二次下側開口を形成するステップと、

-少なくとも1個の金属材料により前記少なくとも二次下側開口を充填して、前記上側接触部および少なくとも前記下側接触部が同一平面内で画定された表面を有するように、少なくとも1個の下側接触パッドを画定するステップとを含んでいる。

-少なくとも1個の一次上側開口と少なくとも1個の一次下側開口とを同時に形成するステップと、

-少なくとも1個の二次上側開口と少なくとも1個の二次下側開口とを同時に形成するステップとを含んでいる。

-誘電体を追加的に堆積するステップと、

-少なくとも1個の追加的な下側開口および少なくとも1個の追加的な上側開口を形成するステップと、

-少なくとも1個の金属材料により前記追加的な開口を充填して、少なくとも1個の追加的な下側接触部および少なくとも1個の追加的な上側接触部を画定するステップとを含んでいる。

-TiN、Ti/TiN、TaN、Ta/TaN、W(フッ素非含有)から選択された材料の1個以上の層を含む拡散障壁を堆積するステップと、

-W、Cu、Al、AlCu、AlSiから選択された充填金属を堆積するステップとを含んでいる。

-例えばSiチップ等、任意の種類の基板上でのウェーハへのIII-V族移動と、

-ウェーハ間移動、

-III-V族のSi基板、またはIII/Vの結晶成長を可能にする任意の永続的または一時的基板上へのIII-V族のエピタキシに適用することができる。成長させたいIII/V材料と同一の結晶構造および成長途上の層に近い格子パラメータの少なくとも1個の結晶核が存在しなければならない点に注意されたい。格子パラメータ間に5%を超える差があれば結晶は不完全である(ずれ、逆相結晶粒界または多結晶質の場合もある)。これはガラス等のアモルファス基板では不可能である。

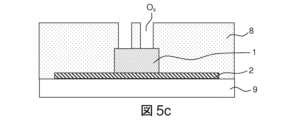

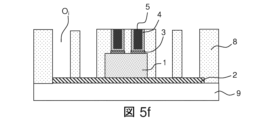

-第1のIII-V族材料:1、

-第2のIII-V族材料:2、

-基板:9、

-1個以上の誘電材料:8、

-金属化部分:3、

-拡散障壁:4、

-金属充填材:5

-第1の材料1と接触する上側開口:Os、

-第2の材料2と接触する下側開口:Oi。

下側接触部の形成に続いて本発明の第1の代替方式に従い上側接触部を形成するステップを含む本発明による処理の第1の例:

第1のステップ:

当該ステップは、基板9上のIII-V族材料2のベースの表面に第1のIII-V族材料1のメサを含む先に形成された構造のカプセル化を含んでいる。

当該ステップは、CMP動作(「化学機械平坦化」または「化学機械研磨」)または平坦化ポリマーの場合はドライエッチング(「エッチバック」)による部分的除去による誘電体の平坦化を含んでいる。

当該ステップは、下側接触部の形成を意図して第1の下側開口Oi1を形成するステップを含んでいる。

第1のドライエッチングにより誘電スタックの一部をエッチングして、障壁層(SiN、Al2O3、SiO2、BCB、SOC、好適にはSiN)で停止し、次いで材料2まで貫通するように乾式または湿式エッチングにより障壁層および任意選択的な下位層をエッチングする。

当該ステップは、シリコン処理工程と互換性を有する金属化部分を堆積して下側接触部を画定するステップを含んでいるため、貴金属、すなわちシリコン処理工程で使われない金属の使用を回避できるようになる。

(a)Ni2P、Ni3P、NiGe、TiP、TiGe等、シリコン処理工程と互換性を有する金属3の堆積を実行する。

金属堆積の後で実行される任意選択な熱処理により相安定化を行うことができる。

(b)Ni、TiおよびNiPt、NiTi、NiCo等の合金等、シリコン処理工程と互換性を有する金属3の堆積を実行する。

当該ステップは、接続パッドを形成すべく第1の下側開口を充填するステップとCMP動作とを含んでいる。下側開口は2回充填される。すなわち、

-拡散障壁/キーイングまたは核形成層4の堆積を実行する。当該層はTiN、Ti/TiN、TaN、Ta/TaN、あるいはCVD、PVDまたはALDにより堆積されたWを含んでいてよい。

-充填金属5(W、Cu、AlCu、AlSi)の堆積を実行し、堆積はCVD、ECDまたはPVDにより行われる。

当該ステップは、誘電体8の上方で画定されたアセンブリのカプセル化ステップを含んでいる。材料1上方の誘電体の厚さD5は典型的には200nm~1μm、好適には200nm~500nmの範囲にある。使用する誘電体はSiN、SiO2、Al2O3、平坦化ポリマー(例えばBCB、SOG)であってよい。堆積物は単一層または多層であってよい。これらはPVD、CVDおよび/またはALDにより堆積される。

当該ステップは、下側接触部の形成を意図して二次下側開口Oi2および上側接触部の形成を意図して開口Osを形成するステップを含んでいる。

当該ステップは、シリコン処理工程と互換性を有する金属化部分を堆積して下側接触部および上側接触部を画定するステップを含んでいるため、貴金属、すなわちシリコン処理工程で使われない金属の使用を回避できるようになる。

(a)Ni2P、Ni3P、NiGe、TiP、TiGe等、シリコン処理工程と互換性を有する金属3の堆積を実行する。

金属堆積の後で実行される任意選択な熱処理により相安定化を行うことができる。

(b)Ni、TiおよびNiPt、NiTi、NiCo等の合金等、シリコン処理工程と互換性を有する金属3の堆積を実行する。

当該ステップは、接続パッドを形成すべく下側開口および上側開口を充填するステップとCMP動作とを含んでいる。下側開口および上側開口の充填は2回行われる。すなわち、

-拡散障壁/キーイングまたは核形成層4の堆積を実行する。当該層はTiN、Ti/TiN、TaN、Ta/TaN、あるいはCVD、PVDまたはALDにより堆積されたWを含んでいてよい。

-充填金属5(W、Cu、AlCu、AlSi)の堆積を実行し、堆積はCVD、ECDまたはPVDにより行われる。

第1のステップ:

当該ステップは、基板9上のIII-V族材料2のベースの表面に第1のIII-V族材料1のメサを含む先に形成された構造のカプセル化を含んでいる。

当該ステップは、CMP動作(「化学機械平坦化」または「化学機械研磨」)または平坦化ポリマーの場合はドライエッチング(「エッチバック」)による部分的除去による誘電体の平坦化を含んでいる。

当該ステップは、上側接触部の形成を意図して上側開口OSを形成するステップを含んでいる。

第1のドライエッチングにより誘電スタックの一部をエッチングして、障壁層(SiN、Al2O3、SiO2、BCB、SOC、好適にはSiN)で停止し、次いで材料1まで貫通するように乾式または湿式エッチングにより障壁層および任意選択的な下位層をエッチングする。

当該ステップは、シリコン処理工程と互換性を有する金属化部分を堆積して下側接触部を画定するステップを含んでいるため、貴金属、すなわちシリコン処理工程で使われない金属の使用を回避できるようになる。

(a)Ni2P、Ni3P、NiGe、TiP、TiGe等、シリコン処理工程と互換性を有する金属3の堆積を実行する。

金属堆積の後で実行される任意選択な熱処理により相安定化を行うことができる。

(b)Ni、TiおよびNiPt、NiTi、NiCo等の合金等、シリコン処理工程と互換性を有する金属3の堆積を実行する。

当該ステップは、接続パッドを形成すべく上側開口を充填するステップとCMP動作とを含んでいる。上側開口の充填は2回行われる。すなわち、

-拡散障壁/キーイングまたは核形成層4の堆積を実行する。当該層はTiN、Ti/TiN、TaN、Ta/TaN、あるいはCVD、PVDまたはALDにより堆積されたWを含んでいてよい。

-充填金属5(W、Cu、AlCu、AlSi)の堆積を実行し、堆積はCVD、ECDまたはPVDにより行われる。

当該ステップは、下側接触部の形成を意図して下側開口Oiを形成するステップを含んでいる。

第1のドライエッチングにより誘電スタックの一部をエッチングして、障壁層(SiN、Al2O3、SiO2、BCB、SOC、好適にはSiN)で停止し、次いで材料2まで貫通するように乾式または湿式エッチングにより障壁層および任意選択的な下位層をエッチングする。

当該ステップは、シリコン処理工程と互換性を有する金属化部分を堆積して下側接触部を画定するステップを含んでいるため、貴金属、すなわちシリコン処理工程で使われない金属の使用を回避できるようになる。

(a)Ni2P、Ni3P、NiGe、TiP、TiGe等、シリコン処理工程と互換性を有する金属3の堆積を実行する。

金属堆積の後で実行される任意選択的な熱処理により相安定化を行うことができる。

(b)Ni、TiおよびNiPt、NiTi、NiCo等の合金等、シリコン処理工程と互換性を有する金属3の堆積を実行する。

当該ステップは、接続パッドを形成すべく下側開口充填するステップとCMP動作とを含んでいる。下側開口は2回充填される。すなわち、

-拡散障壁/キーイングまたは核形成層4の堆積を実行する。当該層はTiN、Ti/TiN、TaN、Ta/TaN、あるいはCVD、PVDまたはALDにより堆積されたWを含んでいてよい。

-充填金属5(W、Cu、AlCu、AlSi)の堆積を実行し、堆積はCVD、ECDまたはPVDにより行われる。

第1のステップ:

当該ステップは、基板9上のIII-V族材料2のベースの表面に第1のIII-V族材料1のメサを含む先に形成された構造のカプセル化を含んでいる。

当該ステップは、CMP動作(「化学機械平坦化」または「化学機械研磨」)または平坦化ポリマーの場合はドライエッチング(「エッチバック」)による部分的除去による誘電体の平坦化を含んでいる。

当該ステップは、上側接触部の形成を意図して上側開口Osを、および下側接触部の形成を意図して下側開口Oiを形成するステップを含んでいる。

第1のドライエッチングにより誘電スタックの一部をエッチングして、障壁層(SiN、Al2O3、SiO2、BCB、SOC、好適にはSiN)で停止し、次いで材料1および材料2まで貫通するように乾式または湿式エッチングにより障壁層および任意選択的な下位層をエッチングする。

当該ステップは、シリコン処理工程と互換性を有する金属化部分を堆積して上側接触部および下側接触部を画定するステップを含んでいるため、貴金属、すなわちシリコン処理工程で使われない金属の使用を回避できるようになる。

(a)Ni2P、Ni3P、NiGe、TiP、TiGe等、シリコン処理工程と互換性を有する金属3の堆積を実行する。

金属堆積の後で実行される任意選択的な熱処理により相安定化を行うことができる。

(b)Ni、TiおよびNiPt、NiTi、NiCo等の合金等、シリコン処理工程と互換性を有する金属3の堆積を実行する。

当該ステップは、接続パッドを形成すべく上側開口および下側開口を充填するステップとCMP動作とを含んでいる。上側および下側開口の同時の充填は2回行われる。すなわち、

-拡散障壁/キーイングまたは核形成層4の堆積を実行する。当該層はTiN、Ti/TiN、TaN、Ta/TaN、あるいはCVD、PVDまたはALDにより堆積されたWを含んでいてよい。

-充填金属5(W、Cu、AlCu、AlSi)の堆積を実行し、堆積はCVD、ECDまたはPVDにより行われる。

第1のドライエッチングを用いて誘電スタックの一部をエッチングして、障壁層(SiN、Al2O3、SiO2、BCB、SOC、好適にはSiN)で停止し、次いで材料1まで貫通するように乾式または湿式エッチングにより障壁層および任意選択的な下位層をエッチングする。

(a)Ni2P、Ni3P、NiGe、TiP、TiGe等、シリコン処理工程と互換性を有する金属3の堆積を実行する。

金属堆積の後で実行される任意選択的な熱処理により相安定化を行うことができる。

(b)Ni、TiおよびNiPt、NiTi、NiCo等の合金等、シリコン処理工程と互換性を有する金属3の堆積を実行する。

材料の上に下側接触部の外部パッドを露出させる誘電スタックエッチング、すなわち

・低レベルパッドの充填材までエッチングを1回実行するドライエッチング。この場合エッチストップ層の存在は任意選択的である。

・連続エッチング、すなわち第1のドライエッチングにより誘電スタックの一部をエッチングして、障壁層(SiN、Al2O3、SiO2、BCB、SOC、好適にはSiN)で停止し、次いで低レベルパッドの充填材まで貫通するように乾式または湿式エッチングにより障壁層および任意選択的な下位層をエッチングする。

-拡散障壁/キーイングまたは核形成層4の堆積を実行する。当該層はTiN、Ti/TiN、TaN、Ta/TaN、あるいはCVD、PVDまたはALDにより堆積されたWを含んでいてよい。

-充填金属5(W、Cu、AlCu、AlSi)の堆積を実行し、堆積はCVD、ECDまたはPVDにより行われる。

材料の上に下側接触部の外部パッドを開口するための誘電スタックエッチング、すなわち

・低レベルパッドの充填材までエッチングを1回実行するドライエッチング。この場合エッチストップ層の存在は任意選択的である。

・連続エッチング、すなわち第1のドライエッチングにより誘電スタックの一部をエッチングして、障壁層(SiN、Al2O3、SiO2、BCB、SOC、好適にはSiN)で停止し、次いで低レベルパッドの充填材まで貫通するように乾式または湿式エッチングにより障壁層および任意選択的な下位層をエッチングする。

-拡散障壁/キーイングまたは核形成層4の堆積を実行する。当該層はTiN、Ti/TiN、TaN、Ta/TaN、あるいはCVD、PVDまたはALDにより堆積されたWを含んでいてよい。

-充填金属5(W、Cu、AlCu、AlSi)の堆積を実行し、堆積はCVD、ECDまたはPVDにより行われる。

本発明の処理は、有利な特徴としてIII-V族材料を主体としてレーザーを生成可能にする。

-nドープInPからなる第2のIII-V族材料2のベース、およびドーピングの程度が異なるInGaAsPからなる多重量子井戸構造およびpドープInGaAsの層を含むメサ1であり、III-V族材料の特性が発光波長を決定する、

-誘電体8は、SiN、SiO2であっても、または例えばBCBを主体とする平坦化ポリマーであってもよく、

-接触底面の金属化部分3は、例えばNi、Tiまたはそれらの合金(Ni2P、Ni3P、NiGe、TiP、TiGe等)であってよく、

-Fに対する拡散障壁および/またはW4に対するキーイング層はTiN、Ti/TiN、TaN、Ta/TaN、Wであってよい。

一般に、垂直空洞面発光レーザーダイオードすなわちVCSELが、従来の端面発光半導体レーザーとは対照的に、表面に対して垂直にレーザービームを発光する種類の半導体レーザーダイオードであることが想起できよう。

上述の第2の代替方式によれば、一次開口底面の金属化部分および二次開口の接触パッドを画定する。従って接触部は少なくとも開口底面の金属化部分および前記金属化部分と接触している接触パッドを含んでいる。

第1のステップ:

当該ステップは、基板9上にIII-V族材料2のベースの表面に第1のIII-V族材料1のメサを含む先に形成された構造のカプセル化を含んでいる。

当該ステップは、CMP動作(「化学機械平坦化」または「化学機械研磨」)または平坦化ポリマーの場合はドライエッチング(「エッチバック」)による部分的除去による誘電体の平坦化を含んでいる。

当該ステップは、下側接触部の形成を意図して一次下側開口Oipを形成するステップを含んでいる。

当該ステップは、シリコン処理工程と互換性を有する金属化部分を堆積して下側接触部を画定するステップを含んでいるため、貴金属、すなわちシリコン処理工程で使われない金属の使用を回避できるようになる。

(a)Ni2P、Ni3P、NiGe、TiP、TiGe等、シリコン処理工程と互換性を有する金属3の堆積を実行する。

金属堆積の後で実行される任意選択的な熱処理により相安定化を行うことができる。

(b)Ni、TiおよびNiPt、NiTi、NiCo等の合金等、シリコン処理工程と互換性を有する金属3の堆積を実行する。

当該ステップは、誘電体8によるアセンブリE1のカプセル化ステップを含んでいる。使用する誘電体はSiN、SiO2、Al2O3、平坦化ポリマー(例えばBCB、SOG)であってよい。堆積物は単一層または多層であってよい。これらはPVD、CVDおよび/またはALDにより堆積される。

当該ステップは、CMP動作または平坦化ポリマーの場合は「エッチバック」動作による誘電体の平坦化を含んでいる。

-第4のステップで選択的除去が金属の除去まで行われなかった場合、

-第4のステップで選択的除去が行われず、且つ金属に対するCMP方式または「エッチバック」方式の動作が不可能で、金属上で停止する場合(従って金属の選択的除去ステップを実行して図13fに示すような構造が得られる)、

-図13fに示すような構造が得られるまで、第4のステップで選択的除去が実行された場合である。

当該ステップは、接続パッドの形成を意図して上部二次下側開口Ois1に行われる動作を含んでいる。このため、下部レベルで金属化部分3まで貫通するように誘電スタックのエッチングを実行する。

当該ステップは、接続パッドを形成すべく二次下側開口を充填するステップとCMP動作とを含んでいる。二次下側開口の充填は2回行われる。すなわち、

-拡散障壁/キーイングまたは核形成層4の堆積を実行する。当該層はTiN、Ti/TiN、TaN、Ta/TaN、あるいはCVD、PVDまたはALDにより堆積されたWを含んでいてよい。

-充填金属5(W、Cu、AlCu、AlSi)の堆積を実行し、堆積はCVD、ECDまたはPVDにより行われる。

当該ステップは、誘電体8によるカプセル化の動作を含んでいる。使用する誘電体はSiN、SiO2、Al2O3、平坦化ポリマー(例えばBCB、SOG)であってよい。堆積物は単一層または多層であってよい。誘電体は、PVD、CVDおよび/またはALDにより堆積される。堆積温度は450℃以下、好適には300℃以下である。典型的には、図示する誘電体の高さD7は200nm~1μm、好適には200nm~500nmの範囲にある。当該ステップを図13iに示す。

当該ステップは、上側接触部を形成すべく一次上側開口Ospを形成するステップを含んでいる。

当該ステップは、上側接触部の形成を意図してシリコン処理工程と互換性を有する金属化部分3を堆積するステップを含んでいる。シリコン処理工程と互換性を有する金属化は二通りの仕方で実行することができる。

(a)Ni2P、Ni3P、NiGe、TiP、TiGe等、シリコン処理工程と互換性を有する金属3の堆積を実行する。

金属堆積の後で実行される任意選択的な熱処理により相安定化を行うことができる。

(b)Ni、TiおよびNiPt、NiTi、NiCo等の合金等、シリコン処理工程と互換性を有する金属3の堆積を実行する。

当該ステップは、第3のアセンブリE3のカプセル化を含んでいる。使用する誘電体はSiN、SiO2、Al2O3、平坦化ポリマー(例えばBCB)、SOGであってよい。堆積物は単一層または多層であってよい。これらはPVD、CVDおよび/またはALDにより堆積される。堆積温度は450℃以下、好適には300℃以下である。

当該ステップは、平坦化動作を含んでいる。

-第11のステップで選択的除去が金属の除去まで行われなかった場合、

-第11のステップで選択的除去が行われず、且つ金属に対するCMP方式または「エッチバック」方式の動作が不可能で、金属上で停止する場合(従って金属の選択的除去ステップを実行して図4mに示すような構造が得られる)、

-図13mに示すような構造が得られるまで、第11のステップで選択的除去が実行された場合である。

当該ステップは、下側接触部の少なくとも接触パッドの最上部に二次上側開口Ossおよび追加的な上側開口Ois2を形成するステップを含んでいる。

当該ステップは、先のステップで画定された開口を充填するステップを含んでいる。

-拡散障壁/キーイングまたは核形成層の堆積を実行する。当該層はTiN、Ti/TiN、TaN、Ta/TaN、あるいはCVD、PVDまたはALDにより堆積されたWを含んでいてよい。

-充填金属(W、Cu、AlCu、AlSi等)の堆積を実行し、堆積はCVD、ECDまたはPVDにより行われる。

第1のステップ:

当該ステップは、基板9上にIII-V族材料2のベースの表面に第1のIII-V族材料1のメサを含む先に形成された構造のカプセル化を含んでいる。

当該ステップは、CMP方式または平坦化ポリマーの場合は「エッチバック」方式の動作による誘電体の平坦化を含んでいる。CMPの前にトポグラフィ上に局所的リソグラフィ/エッチング動作を行うことも可能である。当該平坦化ステップを図14bに示す。

当該ステップは、上側接触部の形成を意図して一次上側開口Ospを形成するステップを含んでいる。

当該ステップは、シリコン処理工程と互換性を有する金属化部分3をIII-V族材料1の上に堆積するステップを含んでいる。

(a)Ni2P、Ni3P、NiGe、TiP、TiGe等、シリコン処理工程と互換性を有する金属3の堆積を実行する。

金属堆積の後で実行される任意選択的な熱処理により相安定化を行うことができる。

(b)Ni、TiおよびNiPt、NiTi、NiCo等の合金等、シリコン処理工程と互換性を有する金属3の堆積を実行する。

当該ステップは、誘電体8によりアセンブリE1’のカプセル化を含んでいる。使用する誘電体はSiN、SiO2、Al2O3、平坦化ポリマー(例えばBCB、SOG)であってよい。堆積物は単一層または多層であってよい。これらは、PVD、CVDおよび/またはALDにより堆積される。

当該ステップは、CMP方式または平坦化ポリマーの場合は「エッチバック」方式の動作による誘電体の平坦化を含んでいる。これらの動作を実行できるのは、

-第4のステップで選択的除去が金属の除去まで行われなかった場合、

-第4のステップで選択的除去が行われず、且つ金属に対するCMP方式または「エッチバック」方式の動作が不可能で、金属上で停止する場合(従って金属の選択的除去ステップを実行して図14fに示すような構造が得られる)、

-図14fに示すような構造が得られるまで、第4のステップで選択的除去が実行された場合である。

当該ステップは、接続パッドの形成を意図して二次上側開口Ossに行われる動作を含んでいる。このため、上部レベルで金属化部分3まで貫通するように誘電スタックのエッチングを実行する。

当該ステップは、接続パッドを形成すべく開口Ossを充填するステップおよびCMP動作を含んでいる。

-拡散障壁/キーイングまたは核形成層の堆積を実行する。当該層はTiN、Ti/TiN、TaN、Ta/TaN、あるいはCVD、PVDまたはALDにより堆積されたWを含んでいてよい。

-充填金属(W、Cu、AlCu、AlSi等)の堆積を実行し、堆積はCVD、ECDまたはPVDにより行われる。

当該ステップは、下側接触部を形成すべく一次下側開口Oipを形成するステップを含んでいる。

当該ステップは、下側接触部の形成を意図してシリコン処理工程と互換性を有する金属化部分3を堆積するステップを含んでいる。CMOS互換性を有する金属化は、二通りの仕方で実行することができる。

(a)Ni2P、Ni3P、NiGe、TiP、TiGe等、シリコン処理工程と互換性を有する金属3の堆積を実行する。

金属堆積の後で実行される任意選択的な熱処理により相安定化を行うことができる。

(b)Ni、TiおよびNiPt、NiTi、NiCo等の合金等、シリコン処理工程と互換性を有する金属3の堆積を実行する。

当該ステップは誘電体8によるアセンブリE3’のカプセル化を含んでいる。使用する誘電体はSiN、SiO2、Al2O3、平坦化ポリマー(例えばBCB)、SOGであってよい。堆積物は単一層または多層であってよい。これらはPVD、CVDおよび/またはALDにより堆積される。

当該ステップは、CMP方式または平坦化ポリマーの場合は「エッチバック」方式の動作により誘電体を平坦化する動作を含んでいる。

当該ステップは、接続パッドの形成を意図して二次下側開口Oisに行われる動作を含んでいる。このため、下側レベルで金属化部分3まで貫通するように誘電スタックのエッチングを実行する。

当該ステップは、先のステップで画定された開口を充填するステップを含んでいる。

-拡散障壁/キーイングまたは核形成層の堆積を実行する。当該層はTiN、Ti/TiN、TaN、Ta/TaN、あるいはCVD、PVDまたはALDにより堆積されたWを含んでいてよい。

-充填金属(W、Cu)の堆積を実行し、堆積はCVD、ECDまたはPVDにより行われる。

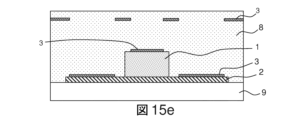

第1のステップ:

当該ステップは、基板9上にIII-V族材料2のベースの表面に第1のIII-V族材料1のメサを含む先に形成された構造のカプセル化を含んでいる。

当該ステップは、CMP方式または平坦化ポリマーの場合は「エッチバック」方式の動作による誘電体の平坦化を含んでいる。CMPの前にトポグラフィ上に局所的リソグラフィ/エッチング動作を行うことも可能である。当該平坦化ステップを図15bに示す。

当該ステップは、下側接触部の形成を意図して一次下側開口Oipおよび上側接触部の形成を意図して一次上側開口Ospを形成するステップを含んでいる。

当該ステップは、シリコン処理工程と互換性を有する金属化部分3をIII-V族材料1およびIII-V族材料2の上に堆積するステップを含んでいる。

(a)Ni2P、Ni3P、NiGe、TiP、TiGe等、シリコン処理工程と互換性を有する金属3の堆積を実行する。

金属堆積の後で実行される任意選択的な熱処理により相安定化を行うことができる。

(b)Ni、TiおよびNiPt、NiTi、NiCo等の合金等、シリコン処理工程と互換性を有する金属3の堆積を実行する。

当該ステップは、誘電体8によりアセンブリE1”のカプセル化を含んでいる。使用する誘電体は、SiN、SiO2、Al2O3、平坦化ポリマー(例えばBCB、SOG)であってよい。堆積物は単一層または多層であってよい。これらはPVD、CVDおよび/またはALDにより堆積される。

当該ステップは、CMP方式または平坦化ポリマーの場合は「エッチバック」方式の動作による誘電体の平坦化を含んでいる。これらの動作を実行できるのは、

-第4のステップで選択的除去が金属の除去まで行われなかった場合、

-第4のステップで選択的除去が行われず、且つ金属に対するCMP方式または「エッチバック」方式の動作が不可能で、金属上で停止する場合(従って金属の選択的除去ステップを実行して図15fに示すような構造が得られる)、

-図15fに示すような構造が得られるまで、第4のステップで選択的除去が実行される場合である。

当該ステップは、接続パッドの形成を意図して二次上側開口Ossおよび二次下側開口Oisに行われる動作を含んでいる。このため、上側レベルおよび下側レベルで金属化部分3まで貫通するように誘電スタックのエッチングを実行する。

当該ステップは、先のステップで画定された開口を充填するステップを含んでいる。

-拡散障壁/キーイングまたは核形成層の堆積を実行する。当該層はTiN、Ti/TiN、TaN、Ta/TaN、あるいはCVD、PVDまたはALDにより堆積されたWを含んでいてよい。

-充填金属(W、Cu)の堆積を実行し、堆積はCVD、ECDまたはPVDにより行われる。

第1のステップ:

上述のものと同一のサブステップによれば、

-基板9と、

-III-V族材料1と、

-III-V族材料2と、

-金属化部分3とを含むアセンブリが形成される。

当該ステップは、先に構成されたアセンブリの部分的エッチングにより、または誘電体8の部分的エッチングにより二次下側開口Ois1を形成するステップを含んでいる。ドライエッチングを用いてもよい。この場合エッチストップ層の存在は任意選択的である。

第2のエッチング動作は、先に形成された開口Ois1の延伸に際して開口Ois2を形成して、金属化部分3まで貫通するように二次上側開口Ossを形成することにより、二次下側開口を延伸すべく、2回実行される。

当該ステップは、先のステップで画定された開口を充填するステップを含んでいる。

-拡散障壁キーイングまたは核形成層の堆積を実行する。当該層はTiN、Ti/TiN、TaN、Ta/TaN、あるいはCVD、PVDまたはALDにより堆積されたWを含んでいてよい。

-充填金属(W、Cu、AlCu、AlSi)の堆積を実行し、堆積はCVD、ECDまたはPVDにより行われる。

本発明の処理を有利に用いてIII-V族材料を主体とするレーザーを形成することができる。

-nドープInPからなる第2のIII-V族材料2のベース、およびドーピングの程度が異なるInGaAsPからなる多重量子井戸構造およびpドープInGaAsの層を含むメサ1であり、III-V族材料の特性が発光波長を決定する、

-誘電体8は、SiN、SiO2であっても、または例えばBCBを主体とする平坦化ポリマーであってもよく、

-接触底面の金属化部分3は、例えばNi、Tiまたはそれらの合金(Ni2P、Ni3P、NiGe、TiP、TiGe等)であってよく、

-Fに対する拡散障壁および/またはW4に対するキーイング層はTiN、Ti/TiN、TaN、Ta/TaN、Wであってよい。

一般に、垂直空洞面発光レーザーダイオードすなわちVCSELが、従来の端面発光半導体レーザーとは対照的に、表面に対して垂直にレーザービームを発光する種類の半導体レーザーダイオードであることが想起できよう。

上述の素子の例はシリコン基板9を含み、その最上部に図21に示すように

-いわゆる下側レベルに位置するIII-V族材料22と、

-いわゆる中間レベルに位置するIII-V族材料21と、

-いわゆる上側レベルに位置するIII-V族材料10とが積層されている。

-材料22の接触部Cinfと、

-材料21の接触部Cintと、

-材料10の接触部Csupとを含んでいる。

-接触底面の金属化部分および充填を実行するための単一種類の開口、

-2種類の開口、すなわち金属化用の極めて大きい一次開口、および接触部の形成および充填のための二次開口について以下に説明する。

-長さLtが二次開口の寸法よりも短い(Lt<a)場合、この種の開口だけによる集積、すなわち接触底面の金属化および充填を考えればよく、

-長さLtが二次開口の寸法よりも長い(Lt>a)場合、2種類の開口、すなわち本特許出願の関連では寸法Ltよりも大きい表面の金属化、次いで充填用により小さい二次開口を採用すべきである。

Claims (30)

- 基板の表面にIII-V族材料の構造を含む素子を形成する処理であって、前記構造が、第1のIII-V族材料(1)の表面に画定された少なくとも1個の上側接触レベル(Nsup)および第2のIII-V族材料(2)の表面に画定された下側接触レベル(Ninf)を含み、

-少なくとも1個の誘電体(8)による前記構造のカプセル化を含む、少なくとも1個の誘電体によるカプセル化の一連のステップと、

-前記第1のIII-V族材料および前記第2のIII-V族材料の上に接触底面領域を画定すべく、前記誘電体(8)内に、前記第1のIII-V族材料(1)の表面に少なくとも1個の上側開口(Os)および前記第2のIII-V族材料(2)の表面に少なくとも1個の下側開口(Oi)を形成するステップと、

-少なくとも前記上側開口(Os)および少なくとも前記下側開口(Oi)において接触底面の金属化部分(3)を形成するステップと、

-少なくとも1個の金属材料(5)による、少なくとも前記上側開口(Os)の少なくとも部分的充填および少なくとも前記下側開口(Oi)の少なくとも部分的充填により、少なくとも1個の上側接触パッドおよび少なくとも1個の下側接触パッドを形成するステップと、

-接触底面の金属化部分および接触パッドが、前記上側接触レベル(Nsup)と接触している前記第1のIII-V族材料の少なくとも1個の上側接触部および前記下側接触レベル(Ninf)と接触している前記第2のIII-V族材料の少なくとも1個の下側接触部を画定するステップと、

-少なくとも前記上側接触部および少なくとも前記下側接触部を、同一平面内で画定された上面を有するように誘電体に集積するステップを含む処理であって、

前記処理はさらに、

-第1の誘電体により前記構造をカプセル化するステップと、

-前記第2のIII-V族材料(2)の上に少なくとも1個の一次下側開口(Oip)を形成するステップと、

-前記第1の誘電体の表面、および前記第2のIII-V族材料(2)の表面に金属化部分を堆積して、下側接触底面の金属化部分および第1のアセンブリ(E1)を画定するステップと、

-第2の誘電体により前記第1のアセンブリ(E1)をカプセル化するステップと、

-カプセル化された前記第1のアセンブリの平坦化するステップと、

-前記下側接触底面の金属化部分の上に少なくとも1個の二次下側開口(Ois1)を形成するステップと、

-少なくとも1個の金属材料により少なくとも前記二次下側開口を充填して前記下側接触部の少なくとも1個の接触パッドおよび第2のアセンブリ(E2)を画定するステップと、

を含むことを特徴とする、処理。 - 前記構造が、第2のIII-V族材料(2)の下側ベースと、前記ベースの上方に位置する第1のIII-V族材料(1)のメサとを有する、請求項1に記載の形成処理。

- 少なくとも1個の下側開口、次いで少なくとも1個の上側開口を連続的に形成するステップを含んでいることを特徴とする、請求項1または2のいずれか1項に記載の形成処理。

- 少なくとも前記下側開口が、互いに重ね合わされた第1の下側開口(Oi1)および第2の下側開口(Oi2)を画定する複数のステップで形成される、請求項3に記載の処理。

- 前記下側開口が、接触底面の金属化部分(3)、金属充填材、接触底面の金属化部分と同一材料で形成された金属化部分(3)、および金属充填材を、この順で重ね合わされた状態で含んでいる、請求項3に記載の処理。

- 少なくとも1個の上側開口、次いで少なくとも1個の下側開口を連続的に形成するステップを含んでいることを特徴とする、請求項1または2のいずれか1項に記載の形成処理。

- 少なくとも1個の上側開口および少なくとも1個の下側開口を同時に形成するステップを含んでいるということを特徴とする、請求項1または2に記載の形成処理。

- 少なくとも前記上側開口のおよび/または少なくとも前記下側開口の幅(D2)が0.5μm~10μm、好適には1μm~5μmの範囲である、請求項1~7のいずれか1項に記載の形成処理。

- -前記第1のIII-V族材料(1)の表面に少なくとも1個の一次上側開口(Osp)、および前記第2のIII-V族材料(2)の表面に少なくとも1個の一次下側開口(Oip)を形成するステップと、

-少なくとも前記一次上側開口および少なくとも前記一次下側開口において接触底面の金属化部分(3)を形成するステップと、

-少なくとも前記一次上側開口(Osp)および少なくとも前記一次下側開口(Oip)を少なくとも1個の誘電体(8)によりカプセル化するステップと、

-少なくとも前記一次上側開口(Osp)に位置する誘電体に少なくとも1個の二次上側開口(Oss)を形成すると共に、前記一次下側開口(Oip)に位置する誘電体に少なくとも1個の二次下側開口(Ois)を形成するステップと、

-少なくとも前記二次上側開口(Oss)および少なくとも前記二次下側開口(Ois)を少なくとも1個の金属材料(5)により充填して少なくとも1個の上側接触パッドおよび少なくとも1個の下側接触パッドを形成するステップと、

を含んでいる、請求項1または2に記載の形成処理。 - 少なくとも1個の一次上側開口、次いで少なくとも1個の一次下側開口を連続的に形成するステップを含んでいることを特徴とする、請求項9に記載の形成処理。

- 少なくとも1個の二次上側開口と少なくとも1個の二次下側開口とを同時に形成するステップを含んでいることを特徴とする、請求項9に記載の形成処理。

- -金属化部分(3)で覆われた前記III-V族材料(1)および金属化部分(3)で覆われた前記III-V族材料(2)を含むアセンブリを誘電体によりカプセル化するステップと、

-前記第2のIII-V族材料(2)の反対側に少なくとも1個の二次下側開口(Ois1)を形成するステップと、

-前記第1のIII-V族材料(1)の上方に少なくとも1個の二次上側開口(Oss)を形成して、少なくとも前記二次下側開口(Ois1)の上方に追加的な少なくとも1個の二次下側開口(Ois2)を形成するステップと、

-少なくとも前記二次上側開口(Oss)、少なくとも1個の追加的な二次下側開口(Ois2)および少なくとも前記二次下側開口(Ois1)を充填するステップとを含んでいることを特徴とする、請求項9~11のいずれか1項に記載の形成処理。 - 前記構造が少なくとも1個のいわゆる上側III-V族材料(10)、いわゆる中間III-V族材料(21)、第2のいわゆる下側III-V族材料(22)を含み、前記処理が、

-少なくとも1個の一次上側開口、少なくとも1個の一次中間開口、少なくとも1個の一次下側開口を形成するステップと、

-少なくとも1個の二次上側開口、少なくとも1個の二次中間開口、および少なくとも1個の二次下側開口を形成するステップと、

-前記開口を充填するステップとを含んでいることを特徴とする、請求項9または10のいずれか1項に記載の形成処理。 - -少なくとも前記二次下側開口が、寸法が異なる3個の部分(Ois1、Ois2、Ois3)を含み、

-少なくとも前記二次中間開口が、寸法が異なる2個の部分(Ots1、Ots2)を含み、

-少なくとも前記二次上側開口が部分(Oss)を含んでいる、請求項13に記載の形成処理。 - -第3の誘電体により前記第2のアセンブリ(E2)をカプセル化するステップと、

-前記第1のIII-V族材料(1)の上方に少なくとも1個の一次上側開口を形成するステップと、

-前記第3の誘電体および前記上側開口の表面に金属化部分を堆積して上側接触底面の金属化部分および第3のアセンブリ(E3)を画定するステップと、

-第4の誘電体により前記第3のアセンブリをカプセル化するステップと、

-前記第3のアセンブリを平坦化するステップと、

-前記上側接触底面の金属化部分の上方に少なくとも1個の二次上側開口(Oss)を、および前記下側接触部の少なくとも前記接触パッドの上方に少なくとも1個の上側開口(Ois2)を形成するステップと、

-少なくとも1個の金属材料により、前記上側接触底面の金属化部分上方の少なくとも前記二次上側開口、および前記下側接触部の少なくとも前記接触パッド上方の少なくとも前記上側開口を充填することにより、前記上側接触部(Csup)および少なくとも前記下側接触部(Cinf)が同一平面内で画定された表面を有するように、上側接触部用の少なくとも1個の上側パッドおよび下側接触パッドの少なくとも1個の延伸部を画定するステップと

を含む、請求項9に記載の形成処理。 - -第1の誘電体により前記構造をカプセル化するステップと、

-前記第1のIII-V族材料(1)まで貫通するように少なくとも1個の一次上側開口(Osp)を形成するステップと、

-前記第1の誘電体の表面、および前記第1のIII-V族材料(1)の表面に金属化部分を堆積して上側底面接触部の金属化部分および第1のアセンブリ(E1’)を画定するステップと、

-第2の誘電体により前記第1のアセンブリ(E1’)をカプセル化するステップと、

-カプセル化された前記第1のアセンブリを平坦化するステップと、

-前記上側接触底面部の金属化部分まで貫通するように少なくとも1個の二次上側開口(Oss)を形成するステップと、

-少なくとも1個の金属材料により少なくとも前記二次上側開口を充填して、前記上側接触部の少なくとも1個の接触パッドおよび第2のアセンブリ(E2’)を画定するステップと、

-前記第2のIII-V族材料(2)の上方に少なくとも1個の一次下側開口(Oip)を形成するステップと、

-前記第1の誘電体、および前記一次下側開口の表面に金属化部分を堆積して、下側接触部の金属化部分および第3のアセンブリ(E3’)を画定するステップと、

-第4の誘電体により前記第3のアセンブリをカプセル化するステップと、

-前記第3のアセンブリを平坦化するステップと、

-前記下側接触部最下層の上方に少なくとも1個の前記二次下側開口(Ois)を形成するステップと、

-前記上側接触部(Csup)および少なくとも前記下側接触部(Cinf)が同一平面内で画定された表面を有する状態で、少なくとも1個の下側接触パッドを画定する少なくとも前記二次下側開口を充填するステップとを含んでいることを特徴とする、請求項9に記載の形成処理。 - -少なくとも1個の一次上側開口および少なくとも1個の一次下側開口を同時に形成するステップと、

-少なくとも1個の二次上側開口および少なくとも1個の二次下側開口を同時に形成するステップとを含んでいることを特徴とする、請求項9に記載の形成処理。 - 少なくとも1個の前記上側接触部および少なくとも1個の前記下側接触部の表面に追加的接触レベルを形成するステップを含み、

-誘電体(8)の追加的な堆積ステップと、

-少なくとも1個の追加的な下側開口および少なくとも1個の追加的な上側開口を形成するステップと、

-追加的な前記開口を少なくとも1個の金属材料により充填して少なくとも1個の追加的な下側接触部(Cinf/supl)および少なくとも1個の追加的な上側接触部(Csup/supl)を画定するステップとを、

含んでいることを特徴とする、請求項9~17のいずれか1項に記載の形成処理。 - -前記一次下側開口が20μm~50μmの幅(D2)を有し、

-前記二次下側開口が0.5μm~5μm、好適には1μm~3μmの幅(D6)を有している、請求項9~18のいずれか1項に記載の形成処理。 - -前記一次下側開口が20μm~50μmの幅(D2)を有し、

-前記二次下側開口が0.5μm~5μm、好適には1μm~3μmの幅(D6)を有している、請求項9~18のいずれか1項に記載の形成処理。 - 前記第1のIII-V族材料および/または前記第2のIII-V族材料が、InP、In1-xGaxAs(0≦x≦1)、GaAs、InAs、GaSb、In1-xGaxSb、InxGa1-xAs1-yPy、Ga1-xInxP、InxGa1-xAs1-yNy、BxInyGa1-x-yAsから選択されることを特徴とする、請求項1~20のいずれか1項に記載の形成処理。

- 前記基板がシリコンであることを特徴とする、請求項1~21のいずれか1項に記載の形成処理。

- 前記誘電体または誘電体群が、SiN、SiO2、Al2O3、ベンゾシクロブテン(BCB)またはSOGを主体とする平坦化ポリマーから選択される、請求項1~22のいずれか1項に記載の形成処理。

- Ni2P、Ni3P、NiGe、TiP、またはTiGeである金属が少なくとも1個の前記一次上側開口および少なくとも1個の前記一次下側開口に堆積される、請求項9~17のいずれか1項に記載の形成処理。

- NiまたはTiである金属、およびNiPt、NiTi、またはNiCoである合金が少なくとも1個の前記一次上側開口および少なくとも1個の前記一次下側開口に堆積される、請求項9~17、19~20のいずれか1項に記載の形成処理。

- 金属化部分の堆積の後で1個以上の金属間化合物を形成すべく熱処理が行われる、請求項1~24のいずれか1項に記載の形成処理。

- 前記部分的充填が、

-TiN、Ti/TiN、TaN、Ta/TaN、Wから選択された材料の1個以上の層を含む拡散障壁を堆積するステップと、

-W、Cu、Al、AlCu、AlSiから選択された充填金属を堆積するステップとを含んでいる、請求項1~26のいずれか1項に記載の形成処理。 - 前記素子がレーザーであり、前記処理が、半導体材料のガイド(91)を誘電体基板(90)内に形成する動作を含んでいる、請求項1~27のいずれか1項に記載の形成処理。

- 前記半導体材料は、Siであり、前記誘電体基板はSiO2である、請求項28に記載の形成処理。

- 前記素子がレーザーであり、前記レーザーの垂直放射を可能にすべく円形の上側接触部を形成するステップを含んでいる、請求項1~27のいずれか1項に記載の形成処理。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| FR1663133A FR3061354B1 (fr) | 2016-12-22 | 2016-12-22 | Procede de realisation de composant comprenant des materiaux iii-v et des contacts compatibles de filiere silicium |

| FR1663133 | 2016-12-22 | ||

| PCT/EP2017/084529 WO2018115510A1 (fr) | 2016-12-22 | 2017-12-22 | Procede de realisation de composant comprenant des materiaux iii-v et des contacts compatibles de filiere silicium |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2020502788A JP2020502788A (ja) | 2020-01-23 |

| JP7299836B2 true JP7299836B2 (ja) | 2023-06-28 |

Family

ID=58501564

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019528511A Active JP7299836B2 (ja) | 2016-12-22 | 2017-12-22 | Iii-v族材料を含む素子およびシリコン処理工程と互換性を有する接触部を形成する処理 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US11075501B2 (ja) |

| EP (1) | EP3559981B1 (ja) |

| JP (1) | JP7299836B2 (ja) |

| CN (1) | CN110291616B (ja) |

| CA (1) | CA3047883A1 (ja) |

| FR (1) | FR3061354B1 (ja) |

| WO (1) | WO2018115510A1 (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR3084774B1 (fr) * | 2018-08-01 | 2021-08-27 | Commissariat Energie Atomique | Procede de realisation de contact ohmique stable thermiquement sur semi-conducteur inp ou ingaas |

| JP7434710B2 (ja) * | 2019-02-07 | 2024-02-21 | 富士フイルムビジネスイノベーション株式会社 | 光半導体素子、光半導体装置、光伝送システム、および光半導体装置の製造方法 |

| EP3809543A1 (en) * | 2019-10-16 | 2021-04-21 | TRUMPF Photonic Components GmbH | Method of fabricating a vcsel device and vcsel device |

| US11251042B2 (en) * | 2019-10-31 | 2022-02-15 | Taiwan Semiconductor Manufacturing Co., Ltd. | Formation of single crystal semiconductors using planar vapor liquid solid epitaxy |

| US11349280B2 (en) * | 2020-01-10 | 2022-05-31 | Newport Fab, Llc | Semiconductor structure having group III-V device on group IV substrate |

| US11581452B2 (en) * | 2020-01-10 | 2023-02-14 | Newport Fab, Llc | Semiconductor structure having group III-V device on group IV substrate and contacts with precursor stacks |

| US11929442B2 (en) | 2020-01-10 | 2024-03-12 | Newport Fab, Llc | Structure and method for process control monitoring for group III-V devices integrated with group IV substrate |

| US11296482B2 (en) | 2020-01-10 | 2022-04-05 | Newport Fab, Llc | Semiconductor structure having group III-V chiplet on group IV substrate and cavity in proximity to heating element |

| US11545587B2 (en) | 2020-01-10 | 2023-01-03 | Newport Fab, Llc | Semiconductor structure having group III-V device on group IV substrate and contacts with liner stacks |

| WO2021163823A1 (en) * | 2020-02-17 | 2021-08-26 | Yangtze Memory Technologies Co., Ltd. | Hybrid wafer bonding method and structure thereof |

| FR3109020B1 (fr) * | 2020-04-06 | 2022-02-25 | Scintil Photonics | Dispositif photonique pour etablir un rayonnement lumineux comprenant un mode optique dans un guide d'onde |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003101152A (ja) | 2001-09-27 | 2003-04-04 | Ricoh Co Ltd | 半導体発光素子の製造方法、および該製造方法を用いて製造した半導体レーザ、ならびに光通信システム |

| JP2007027343A (ja) | 2005-07-15 | 2007-02-01 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP2016046534A (ja) | 2014-08-22 | 2016-04-04 | コミサリア ア レネルジ アトミクエ オウ エネルジ アルタナティヴ | レーザ装置及びレーザ装置の製造方法 |

| US20160141329A1 (en) | 2014-11-13 | 2016-05-19 | Artilux Inc. | Light absorption apparatus |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0272303A1 (en) * | 1986-06-24 | 1988-06-29 | AT&T Corp. | Method for fabricating devices in iii-v semiconductor substrates and devices formed thereby |

| JP3216354B2 (ja) * | 1993-08-11 | 2001-10-09 | ソニー株式会社 | オーミック電極およびその形成方法ならびに半導体装置 |

| US6596616B1 (en) * | 2002-04-19 | 2003-07-22 | Motorola, Inc. | Method for forming serrated contact opening in the semiconductor device |

| US6812141B1 (en) * | 2003-07-01 | 2004-11-02 | Infineon Technologies Ag | Recessed metal lines for protective enclosure in integrated circuits |

| TWI267946B (en) * | 2005-08-22 | 2006-12-01 | Univ Nat Chiao Tung | Interconnection of group III-V semiconductor device and fabrication method for making the same |

| US8252659B2 (en) * | 2008-12-02 | 2012-08-28 | Imec | Method for producing interconnect structures for integrated circuits |

| US8941218B1 (en) * | 2013-08-13 | 2015-01-27 | Avago Technologies General Ip (Singapore) Pte. Ltd. | Passivation for group III-V semiconductor devices having a plated metal layer over an interlayer dielectric layer |

| US9595805B2 (en) * | 2014-09-22 | 2017-03-14 | International Business Machines Corporation | III-V photonic integrated circuits on silicon substrate |

| JP6267403B1 (ja) * | 2014-11-24 | 2018-01-24 | アーティラックス インコーポレイテッドArtilux Inc. | 同じ基板上でトランジスタと共に光検出器を製作するためのモノリシック集積技法 |

-

2016

- 2016-12-22 FR FR1663133A patent/FR3061354B1/fr active Active

-

2017

- 2017-12-22 JP JP2019528511A patent/JP7299836B2/ja active Active

- 2017-12-22 EP EP17822326.9A patent/EP3559981B1/fr active Active

- 2017-12-22 WO PCT/EP2017/084529 patent/WO2018115510A1/fr unknown

- 2017-12-22 US US16/472,136 patent/US11075501B2/en active Active

- 2017-12-22 CN CN201780085813.7A patent/CN110291616B/zh active Active

- 2017-12-22 CA CA3047883A patent/CA3047883A1/en active Pending

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003101152A (ja) | 2001-09-27 | 2003-04-04 | Ricoh Co Ltd | 半導体発光素子の製造方法、および該製造方法を用いて製造した半導体レーザ、ならびに光通信システム |

| JP2007027343A (ja) | 2005-07-15 | 2007-02-01 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP2016046534A (ja) | 2014-08-22 | 2016-04-04 | コミサリア ア レネルジ アトミクエ オウ エネルジ アルタナティヴ | レーザ装置及びレーザ装置の製造方法 |

| US20160141329A1 (en) | 2014-11-13 | 2016-05-19 | Artilux Inc. | Light absorption apparatus |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2020502788A (ja) | 2020-01-23 |

| CN110291616B (zh) | 2023-05-30 |

| CN110291616A (zh) | 2019-09-27 |

| US11075501B2 (en) | 2021-07-27 |

| EP3559981A1 (fr) | 2019-10-30 |

| CA3047883A1 (en) | 2018-06-28 |

| US20200274321A1 (en) | 2020-08-27 |

| FR3061354A1 (fr) | 2018-06-29 |

| EP3559981B1 (fr) | 2024-02-14 |

| FR3061354B1 (fr) | 2021-06-11 |

| WO2018115510A1 (fr) | 2018-06-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7299836B2 (ja) | Iii-v族材料を含む素子およびシリコン処理工程と互換性を有する接触部を形成する処理 | |

| KR102468071B1 (ko) | 다이렉트 뷰 디스플레이를 위한 집적 반사기를 갖는 발광 다이오드 및 이의 제조 방법 | |

| TWI518938B (zh) | 光電半導體晶片及其製造方法 | |

| JP6211176B2 (ja) | 複数の光電子半導体チップを製造する方法及び光電子半導体チップ | |

| KR102518449B1 (ko) | 유전체 dbr을 갖는 인듐 인화물 vcsel | |

| US9419176B2 (en) | Three-dimensional light-emitting device and fabrication method thereof | |

| KR20200050405A (ko) | 자기 정렬 비아를 형성하는 방법 | |

| TW201108461A (en) | Optoelectronic semiconductor body and optoelectronic semiconductor chip | |

| US11531159B2 (en) | Optical waveguide apparatus and method of fabrication thereof | |

| CN108028512A (zh) | 低阻抗vcsel | |

| US20180278025A1 (en) | Laterally grown edge emitting laser | |

| US20210359186A1 (en) | Subpixel light emitting diodes for direct view display and methods of making the same | |

| US20150263218A1 (en) | Front-side emitting mid-infrared light emitting diode fabrication methods | |

| CN105990483A (zh) | 半导体发光元件 | |

| US20210151949A1 (en) | Bonding vertical cavity surface emitting laser die onto a silicon wafer | |

| KR102724659B1 (ko) | 비활성화된 영역을 포함하는 발광 다이오드 및 이의 제조방법 | |

| US20210257510A1 (en) | Light emitting diode containing pinhole masking layer and method of making thereof | |

| US20220190026A1 (en) | Process for manufacturing a three-dimensional led-based emissive display screen | |

| KR20240141122A (ko) | 상호연결 구조물 및 이를 형성하는 방법 | |

| CN118398594A (zh) | 互连结构及其形成方法 | |

| JP2010192635A (ja) | 半導体レーザ及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20201208 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20211216 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20220208 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220425 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20220920 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20221214 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20230309 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20230523 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20230616 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7299836 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |