JP5775281B2 - Memsセンサおよびその製造方法 - Google Patents

Memsセンサおよびその製造方法 Download PDFInfo

- Publication number

- JP5775281B2 JP5775281B2 JP2010228574A JP2010228574A JP5775281B2 JP 5775281 B2 JP5775281 B2 JP 5775281B2 JP 2010228574 A JP2010228574 A JP 2010228574A JP 2010228574 A JP2010228574 A JP 2010228574A JP 5775281 B2 JP5775281 B2 JP 5775281B2

- Authority

- JP

- Japan

- Prior art keywords

- space

- weight

- frame portion

- groove

- mems sensor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 17

- 239000000758 substrate Substances 0.000 claims description 80

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 31

- 229910052710 silicon Inorganic materials 0.000 claims description 31

- 239000010703 silicon Substances 0.000 claims description 31

- 238000005530 etching Methods 0.000 claims description 12

- 239000004065 semiconductor Substances 0.000 claims description 12

- 239000012528 membrane Substances 0.000 claims description 10

- 230000002093 peripheral effect Effects 0.000 claims description 2

- 230000005484 gravity Effects 0.000 claims 1

- 230000001133 acceleration Effects 0.000 description 35

- 239000010410 layer Substances 0.000 description 23

- 238000000034 method Methods 0.000 description 11

- 238000001514 detection method Methods 0.000 description 8

- 239000011229 interlayer Substances 0.000 description 8

- 230000000694 effects Effects 0.000 description 6

- 239000006059 cover glass Substances 0.000 description 5

- 238000013016 damping Methods 0.000 description 5

- 238000005229 chemical vapour deposition Methods 0.000 description 4

- 239000002184 metal Substances 0.000 description 4

- 230000004048 modification Effects 0.000 description 4

- 238000012986 modification Methods 0.000 description 4

- 230000006835 compression Effects 0.000 description 3

- 238000007906 compression Methods 0.000 description 3

- HFGPZNIAWCZYJU-UHFFFAOYSA-N lead zirconate titanate Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ti+4].[Zr+4].[Pb+2] HFGPZNIAWCZYJU-UHFFFAOYSA-N 0.000 description 3

- 229910052451 lead zirconate titanate Inorganic materials 0.000 description 3

- 230000035945 sensitivity Effects 0.000 description 3

- 239000000853 adhesive Substances 0.000 description 2

- 230000001070 adhesive effect Effects 0.000 description 2

- 239000012790 adhesive layer Substances 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 238000001312 dry etching Methods 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 239000005368 silicate glass Substances 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- 238000005452 bending Methods 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 230000001629 suppression Effects 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Landscapes

- Micromachines (AREA)

- Pressure Sensors (AREA)

Description

たとえば、特許文献1には、カバーガラスと、このカバーガラスの一方面に形成されたシリコン層およびピエゾ抵抗素子と、カバーガラスの他方面に形成された電極パッドとを備える加速度センサが提案されている。

しかしながら、シリコン層の支持部が接着剤によりシリコン基板に完全に密着していて、錘部および可撓部直下の空隙が密閉されている。そのため、錘部および可撓部が揺れたときに空隙が圧縮されても、空隙内の空気に逃げ場がなく、錘部および可撓部がエアダンピング効果の影響を受けやすい。その結果、加速度センサに外力が加わっても、錘および可動部が外力に見合う量の変化をせず、センサの感度が低下するおそれがある。

なお、「空間の圧縮率」とは、(振動膜の振動により圧縮されたときの空間の体積V1)/(振動膜が振動する前の空間の体積V2)×100(%)のことをいう。

すなわち、本発明のMEMSセンサの製造方法は、表面および裏面を有する半導体基板を、前記裏面側から選択的にエッチングすることにより、前記表面側が密閉され前記裏面側が開放された空間を形成し、同時に、当該空間に対して内側に前記裏面を形成する底壁を有する錘と、当該空間に対して外側に前記裏面を形成する底壁および前記空間内に臨む内側面を有するフレーム部とを形成する工程と、前記フレーム部の前記底壁および前記錘の前記底壁を選択的にエッチングすることにより、前記フレーム部の前記底壁に前記内側面から外側へ向かって延びる溝を形成し、同時に、前記錘の底面と前記フレーム部の底面との間に前記溝の深さと等しい段差を形成する工程とを含む。

また、本発明のMEMSセンサでは、互いに同一形状の複数の前記溝が、前記空間を取り囲む周方向に沿って等しい間隔を空けて形成されていることが好ましい。

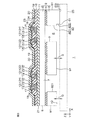

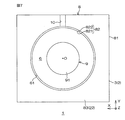

図1は、本発明の一実施形態に係る加速度センサの模式的な平面図である。図2は、図1に示す加速度センサの模式的な底面図である。図3は、図1に示す加速度センサの模式的な断面図であって、切断面A−Aにおける断面を示す。

加速度センサ1は、たとえば、三次元空間において直交する3つの軸(X軸、Y軸およびZ軸)に作用する加速度を検出するセンサであって、表面21および裏面22を有する半導体基板としての平面視矩形状のSOI(Silicon On Insulator)基板を備えている。SOI基板2の表面21は、たとえば、検出素子や検出回路などが形成される素子形成面であり、裏面22は、たとえば、支持基板25(たとえば、ガラス基板などの封止基板)が接合される実装面である。

活性層5は、空間6に臨む円形の部分が振動膜7として形成されている。この振動膜7は、その全周が、シリコン基板3、絶縁層4および活性層5の積層構造からなるSOI基板2の外枠(フレーム部8)の活性層5により一体的に支持されている。また、当該空間6に配置されたシリコン基板3および絶縁層4の積層構造からなる円柱状の部分は、振動膜7にぶら下がった錘9として活性層5に保持されている。

SOI基板2の表面21(素子形成面)には、NSG(Nondoped Silicate Glass)膜11(厚さ2500Å程度)が形成されている。

複数の圧電素子12は、錘9の周縁に沿って互いに間隔を空けて設けられたZ軸検出素子12Z、このZ軸検出素子12Zを取り囲むX軸検出素子12XおよびY軸検出素子12Yを含んでいる。X軸検出素子12Xは、X軸方向において錘9を挟んで一方側および他方側にそれぞれ1つずつ設けられている。また、Y軸検出素子12Yは、Y軸方向において錘9を挟んで一方側および他方側にそれぞれ1つずつ設けられている。

この加速度センサ1は、フレーム部8の底面83に、たとえば、支持基板25(セラミック基板、シリコン基板3、ガラス基板などが接合されることにより、空間6が封止される(図3参照)。

図4A〜図4Dは、図1に示す加速度センサの製造工程を工程順に示す図である。

以上の製造方法によれば、フレーム部8の底面83と錘9の底面91との段差S、およびフレーム部8の溝10が同一工程で同時に形成されるので(図4Dの工程)、これらを別々の工程で形成する場合に比べて工程数を減らすことができる。その結果、効率よく加速度センサ1を製造することができる。

以上、本発明の一実施形態について説明したが、本発明はさらに他の形態で実施することもできる。

たとえば、フレーム部8の溝10は、図5に示すように、底面視においてSOI基板2の対角線に沿うような十字状に形成されていてもよい。また、図6に示すように、錘9の半径方向に沿う(図6では、X軸方向に沿う)直線状に形成されていてもよい。また、図7に示すように、錘9の半径方向に沿うように(図7では、Y軸方向に沿うように)、1本のみ形成されていてもよい。また、複数の溝10の幅は、全てが同じである必要はなく、たとえば、図8に示すように、十字状をなす溝10の一方向に沿う直線部(図8では、Y軸方向に沿う溝10Y)の幅が、他方向に沿う直線部(図8では、X軸方向に沿う溝10X)の幅に比べて広くてもよい。

また、加速度センサは、図9の加速度センサ31のように、振動膜7に歪みを発生させるための錘9を有していなくてもよい。

また、前述の実施形態では、MEMSセンサの一例として、加速度センサを取り上げたが、本発明は、加速度センサに限らず、圧力センサ、ジャイロセンサなど、MEMS技術により作製される各種デバイスに適用することができる。

2 SOI基板

6 空間

7 振動膜

8 フレーム部

9 錘

10 溝

21 (SOI基板の)表面

22 (SOI基板の)裏面

61 (空間の)開放面

81 (フレーム部の)外側面

82 (フレーム部の)内側面

83 (フレーム部の)底面

91 (錘の)底面

S 段差

Claims (9)

- 表面および裏面を有し、前記表面側に形成された振動膜と、当該振動膜を支持し、当該振動膜の直下に、前記裏面側が開放された空間を区画するフレーム部とを有する半導体基板と、

前記空間内において前記振動膜に保持され、前記空間の開放面に臨む底面を有する錘とを含み、

前記フレーム部は、前記半導体基板の前記裏面を形成して支持基板に接合される底壁と、前記空間内に臨む内側面と、前記空間外に臨む外側面とを有しており、

前記フレーム部の前記底壁には、前記フレーム部の前記内側面から前記外側面に至る溝が形成されており、

前記溝は、前記外側面から前記空間の中心部に向かって延びており、

前記フレーム部の内側面は、前記錘の側面を取り囲む基準面と、前記フレーム部の底面から前記溝の深さ位置まで至り、当該基準面よりも外側にオフセットされた前記錘の側面を取り囲むオフセット面とを含む段差面を有している、MEMSセンサ。 - 前記溝の深さ位置は、前記振動膜に対する前記錘の接合位置よりも前記半導体基板の前記裏面側に配置されている、請求項1に記載のMEMSセンサ。

- 前記フレーム部の底面と前記錘の前記底面との間には、前記フレームの前記底壁が支持基板に接合されたときに、前記錘を当該支持基板に対して浮いた状態にするための段差が設けられている、請求項1または2に記載のMEMSセンサ。

- 前記段差が、前記溝の深さと等しい、請求項3に記載のMEMSセンサ。

- 前記空間の中心部が、前記錘の重心に一致している、請求項1〜4のいずれか一項に記載のMEMSセンサ。

- 前記半導体基板が、シリコン基板、絶縁層および活性層が積層された構造からなるSOI基板であり、

前記振動膜が、前記活性層からなり、前記錘が、前記シリコン基板および前記絶縁層の積層構造からなる、請求項1〜5のいずれか一項に記載のMEMSセンサ。 - 前記溝は、前記空間を取り囲む周方向に沿って等しい間隔を空けて複数形成されている、請求項1〜6のいずれか一項に記載のMEMSセンサ。

- 前記複数の溝は、前記半導体基板を前記フレーム部の底面側から見た底面視において十字状に形成されている、請求項7に記載のMEMSセンサ。

- 表面および裏面を有する半導体基板の裏面の一部のエッチング領域を取り囲むように、当該裏面に第1マスクを形成する工程と、

前記エッチング領域を取り囲むように、かつ前記第1マスクの内周側端部を覆うように第2マスクを形成する工程と、

前記第2マスクを介して前記半導体基板を、前記裏面側から選択的にエッチングすることにより、前記裏面側が開放された空間を形成し、同時に、当該空間に対して内側に前記裏面を形成する底壁を有する錘と、当該空間に対して外側に前記裏面を形成する底壁および前記空間内に臨む内側面を有するフレーム部とを形成する工程と、 前記第2マスクを除去した後、前記第1マスクを介して前記フレーム部の前記底壁および前記錘の前記底壁を選択的にエッチングすることにより、前記フレーム部の外側面から前記空間の中心部に向かって延びるように、前記フレーム部の前記底壁における前記内側面と前記外側面との間に溝を形成し、同時に、前記錘の底面と前記フレーム部の底面との間に前記溝の深さと等しい段差と、前記フレーム部の内周面に、前記錘の側面を取り囲む基準面、前記フレーム部の底面から前記溝の深さ位置まで至り、当該基準面よりも外側にオフセットされた前記錘の側面を取り囲むオフセット面を含む段差面とを形成する工程とを含む、MEMSセンサの製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010228574A JP5775281B2 (ja) | 2010-10-08 | 2010-10-08 | Memsセンサおよびその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010228574A JP5775281B2 (ja) | 2010-10-08 | 2010-10-08 | Memsセンサおよびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2012083164A JP2012083164A (ja) | 2012-04-26 |

| JP5775281B2 true JP5775281B2 (ja) | 2015-09-09 |

Family

ID=46242192

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010228574A Active JP5775281B2 (ja) | 2010-10-08 | 2010-10-08 | Memsセンサおよびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5775281B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN110577185A (zh) * | 2019-08-06 | 2019-12-17 | 西人马联合测控(泉州)科技有限公司 | Mems结构、mems结构的制作方法及胎压传感器 |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN107315081B (zh) * | 2017-06-28 | 2020-04-03 | 河海大学 | 路面混凝土减震效果测试方法 |

| CN111512185A (zh) * | 2017-09-21 | 2020-08-07 | 俄罗斯石油公司 | 地震传感器 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2892788B2 (ja) * | 1990-07-27 | 1999-05-17 | 株式会社ワコー | 物理量を検出するセンサの製造方法 |

| JPH06160417A (ja) * | 1992-11-24 | 1994-06-07 | Fujikura Ltd | 半導体加速度センサ |

| JP2003270263A (ja) * | 2002-03-19 | 2003-09-25 | Matsushita Electric Works Ltd | 半導体加速度センサ |

| JP2004177219A (ja) * | 2002-11-26 | 2004-06-24 | Matsushita Electric Works Ltd | 半導体加速度センサ |

| JP2006177675A (ja) * | 2004-12-20 | 2006-07-06 | Japan Aviation Electronics Industry Ltd | 静電容量型加速度センサ |

| JP2009264933A (ja) * | 2008-04-25 | 2009-11-12 | Kyocera Corp | 加速度センサ装置および加速度センサ装置の製造方法 |

| JP2010107486A (ja) * | 2008-10-31 | 2010-05-13 | Kyocera Corp | 加速度センサ装置 |

| JP2010160128A (ja) * | 2008-12-12 | 2010-07-22 | Yamaha Corp | 半導体センサ及び半導体センサの製造方法 |

| JP2010151765A (ja) * | 2008-12-26 | 2010-07-08 | Yamaha Corp | Memsおよびmemsの製造方法 |

-

2010

- 2010-10-08 JP JP2010228574A patent/JP5775281B2/ja active Active

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN110577185A (zh) * | 2019-08-06 | 2019-12-17 | 西人马联合测控(泉州)科技有限公司 | Mems结构、mems结构的制作方法及胎压传感器 |

| CN110577185B (zh) * | 2019-08-06 | 2021-11-16 | 西人马联合测控(泉州)科技有限公司 | Mems结构、mems结构的制作方法及胎压传感器 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2012083164A (ja) | 2012-04-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8829627B2 (en) | Dynamic quantity sensor device and manufacturing method of the same | |

| US7902615B2 (en) | Micromechanical structure for receiving and/or generating acoustic signals, method for producing a micromechanical structure, and use of a micromechanical structure | |

| EP3687192B1 (en) | Microelectromechanical electroacoustic transducer with piezoelectric actuation and corresponding manufacturing process | |

| US9908771B2 (en) | Inertial and pressure sensors on single chip | |

| JP5083369B2 (ja) | 音響センサ及びその製造方法 | |

| WO2010079574A1 (ja) | Memsデバイス | |

| IT201900007317A1 (it) | Trasduttore acustico microelettromeccanico piezoelettrico avente caratteristiche migliorate e relativo procedimento di fabbricazione | |

| US8861753B2 (en) | Acoustic transducer, and microphone using the acoustic transducer | |

| CN105874312B (zh) | 在单芯片上的惯性和压力传感器 | |

| JP2012529207A (ja) | マイクロメカニカルマイクロフォン構造体を有する素子、および、マイクロメカニカルマイクロフォン構造体を有する素子の製造方法 | |

| KR101764314B1 (ko) | 음향 센서 및 그 제조 방법 | |

| WO2021184591A1 (zh) | 一种mems麦克风的加工方法和mems麦克风 | |

| JP5083256B2 (ja) | 半導体装置およびその製造方法 | |

| JP5775281B2 (ja) | Memsセンサおよびその製造方法 | |

| JP4737535B2 (ja) | コンデンサマイクロホン | |

| JPWO2008143191A1 (ja) | Memsセンサおよびその製造方法 | |

| JP5070026B2 (ja) | コンデンサマイクロホン及びその製造方法 | |

| JP2012028900A (ja) | コンデンサマイクロホン | |

| JP5688690B2 (ja) | 振動式トランスデューサおよび振動式トランスデューサの製造方法 | |

| JP5624866B2 (ja) | Memsセンサの製造方法 | |

| JP4737720B2 (ja) | ダイヤフラム及びその製造方法並びにそのダイヤフラムを有するコンデンサマイクロホン及びその製造方法 | |

| JP6032046B2 (ja) | 半導体装置およびその製造方法 | |

| JP2009068893A (ja) | 半導体装置 | |

| JP6874943B2 (ja) | Mems素子 | |

| JP2006162354A (ja) | 慣性素子およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20131007 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140312 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140320 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140512 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20141106 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20141222 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20150604 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20150703 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5775281 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |