JP5065707B2 - 電子部品の実装構造 - Google Patents

電子部品の実装構造 Download PDFInfo

- Publication number

- JP5065707B2 JP5065707B2 JP2007045596A JP2007045596A JP5065707B2 JP 5065707 B2 JP5065707 B2 JP 5065707B2 JP 2007045596 A JP2007045596 A JP 2007045596A JP 2007045596 A JP2007045596 A JP 2007045596A JP 5065707 B2 JP5065707 B2 JP 5065707B2

- Authority

- JP

- Japan

- Prior art keywords

- electronic component

- substrate portion

- resin material

- mounting structure

- mounting

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L24/23—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process

- H01L24/24—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process of an individual high density interconnect connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L2224/23—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process

- H01L2224/24—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process of an individual high density interconnect connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1515—Shape

- H01L2924/15153—Shape the die mounting substrate comprising a recess for hosting the device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/156—Material

- H01L2924/15786—Material with a principal constituent of the material being a non metallic, non metalloid inorganic material

- H01L2924/15787—Ceramics, e.g. crystalline carbides, nitrides or oxides

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Coils Or Transformers For Communication (AREA)

- Cooling Or The Like Of Semiconductors Or Solid State Devices (AREA)

Description

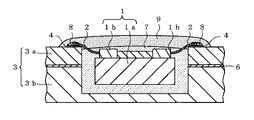

1a・・・コア

1b・・・保持部

2・・・リード端子

3・・・基板

3a・・・実装基板部

3b・・・放熱基板部

4・・・電極パッド

5・・・凹部

6・・・接着材

7・・・樹脂材

Claims (3)

- 上側の実装基板部および下側の放熱基板部からなり、前記実装基板部の上面から前記放熱基板部にかけて凹部が形成されているとともに該凹部の周囲に複数の電極パッドが形成された基板と、

複数の前記電極パッドに接続された複数のリード端子が接続されて前記凹部内に底面および側面から離れた位置に配置された、銅線が巻き付けられたボビンにフェライトから成るコアが取り付けられたトランスである電子部品と、

前記凹部内の前記電子部品の周囲に充填された、ゴム硬さが70以下である樹脂材とを具備することを特徴とする電子部品の実装構造。 - 前記凹部は、前記実装基板部に形成された貫通孔と、前記放熱基板部に形成された穴とから成り、

前記電子部品の一部は、前記穴に入り込んでいることを特徴とする請求項1に記載の電子部品の実装構造。 - 前記樹脂材の上面がゴム硬さが80以上の樹脂材で覆われていることを特徴とする請求項1または請求項2に記載の電子部品の実装構造。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007045596A JP5065707B2 (ja) | 2007-02-26 | 2007-02-26 | 電子部品の実装構造 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007045596A JP5065707B2 (ja) | 2007-02-26 | 2007-02-26 | 電子部品の実装構造 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008210959A JP2008210959A (ja) | 2008-09-11 |

| JP5065707B2 true JP5065707B2 (ja) | 2012-11-07 |

Family

ID=39787019

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007045596A Expired - Fee Related JP5065707B2 (ja) | 2007-02-26 | 2007-02-26 | 電子部品の実装構造 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5065707B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5471716B2 (ja) * | 2010-03-30 | 2014-04-16 | トヨタ自動車株式会社 | リアクトルの製造方法 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0730055A (ja) * | 1993-06-24 | 1995-01-31 | Toppan Printing Co Ltd | マルチチップモジュール実装型プリント配線板 |

| JPH07335451A (ja) * | 1994-06-03 | 1995-12-22 | Murata Mfg Co Ltd | コイル部品 |

| JPH09321182A (ja) * | 1996-05-29 | 1997-12-12 | Shiaru:Kk | 樹脂封止型半導体装置 |

| JP2000232115A (ja) * | 1999-02-10 | 2000-08-22 | Sony Corp | 半導体装置の製造方法 |

| JP2003318042A (ja) * | 2002-04-22 | 2003-11-07 | Tokyo Coil Engineering Kk | 小型トランス |

-

2007

- 2007-02-26 JP JP2007045596A patent/JP5065707B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2008210959A (ja) | 2008-09-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5383621B2 (ja) | パワー半導体装置 | |

| JP5350804B2 (ja) | 電力用半導体装置 | |

| JP5847165B2 (ja) | 半導体装置 | |

| KR101643332B1 (ko) | 초음파 웰딩을 이용한 클립 본딩 반도체 칩 패키지 및 그 제조 방법 | |

| JP5012066B2 (ja) | 電源モジュール | |

| JP2010027813A (ja) | 電力用半導体装置 | |

| JP6307093B2 (ja) | 電子制御装置、電子制御装置の製造方法 | |

| JP4882562B2 (ja) | 熱伝導基板とその製造方法及び電源ユニット及び電子機器 | |

| JP4967701B2 (ja) | 電力半導体装置 | |

| JP2006303400A (ja) | 電子部品収納用パッケージおよび電子装置ならびに電子装置の実装構造 | |

| JP4379284B2 (ja) | 電子装置 | |

| US9426887B2 (en) | Wiring board and electronic device using the same | |

| JP5065707B2 (ja) | 電子部品の実装構造 | |

| JP2010080931A (ja) | 電子部品モジュールおよびその製造方法 | |

| KR20150031029A (ko) | 반도체 패키지 및 그 제조 방법 | |

| JP6391430B2 (ja) | 電子制御装置およびその製造方法 | |

| WO2017014127A1 (ja) | Led搭載基板 | |

| US7719095B2 (en) | Lead frame and semiconductor device provided with lead frame | |

| US20050029658A1 (en) | Circuit board and semiconductor device using the same | |

| JP2001102475A (ja) | 半導体素子用パッケージおよびその実装構造 | |

| JP4667154B2 (ja) | 配線基板、電気素子装置並びに複合基板 | |

| JP3612238B2 (ja) | 混成集積回路装置 | |

| JP3879675B2 (ja) | 半導体装置 | |

| JP2019117920A (ja) | コイル部品及び電子機器 | |

| JP2005101327A (ja) | 半導体装置およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090818 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100405 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120306 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120417 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120717 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120810 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150817 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |