JP4823316B2 - 不揮発性半導体記憶装置の書き込み方法 - Google Patents

不揮発性半導体記憶装置の書き込み方法 Download PDFInfo

- Publication number

- JP4823316B2 JP4823316B2 JP2008532990A JP2008532990A JP4823316B2 JP 4823316 B2 JP4823316 B2 JP 4823316B2 JP 2008532990 A JP2008532990 A JP 2008532990A JP 2008532990 A JP2008532990 A JP 2008532990A JP 4823316 B2 JP4823316 B2 JP 4823316B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- resistance

- writing

- resistance state

- memory element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 76

- 238000000034 method Methods 0.000 title claims description 65

- 230000015654 memory Effects 0.000 claims description 274

- 239000011159 matrix material Substances 0.000 claims description 4

- 238000003860 storage Methods 0.000 claims description 4

- 239000011229 interlayer Substances 0.000 description 23

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 18

- 238000010586 diagram Methods 0.000 description 14

- 239000000463 material Substances 0.000 description 11

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 9

- 239000010410 layer Substances 0.000 description 9

- 229910052697 platinum Inorganic materials 0.000 description 9

- 229910052710 silicon Inorganic materials 0.000 description 9

- 229910052814 silicon oxide Inorganic materials 0.000 description 9

- 238000004519 manufacturing process Methods 0.000 description 8

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 7

- 238000005229 chemical vapour deposition Methods 0.000 description 7

- 230000008569 process Effects 0.000 description 7

- 239000010703 silicon Substances 0.000 description 7

- 239000000758 substrate Substances 0.000 description 7

- 230000008859 change Effects 0.000 description 6

- 238000000151 deposition Methods 0.000 description 6

- 238000001312 dry etching Methods 0.000 description 6

- 238000000206 photolithography Methods 0.000 description 6

- 238000009826 distribution Methods 0.000 description 5

- 238000002955 isolation Methods 0.000 description 5

- 229910052751 metal Inorganic materials 0.000 description 5

- 239000002184 metal Substances 0.000 description 5

- 229910052721 tungsten Inorganic materials 0.000 description 5

- 239000007772 electrode material Substances 0.000 description 4

- 238000012795 verification Methods 0.000 description 4

- 230000004888 barrier function Effects 0.000 description 3

- 230000007423 decrease Effects 0.000 description 3

- 230000010354 integration Effects 0.000 description 3

- 238000004544 sputter deposition Methods 0.000 description 3

- 230000007704 transition Effects 0.000 description 3

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 3

- 239000010937 tungsten Substances 0.000 description 3

- 229910018125 Al-Si Inorganic materials 0.000 description 2

- 229910018182 Al—Cu Inorganic materials 0.000 description 2

- 229910018520 Al—Si Inorganic materials 0.000 description 2

- 229910019001 CoSi Inorganic materials 0.000 description 2

- 241000877463 Lanio Species 0.000 description 2

- 229910016006 MoSi Inorganic materials 0.000 description 2

- 229910005883 NiSi Inorganic materials 0.000 description 2

- 229910018594 Si-Cu Inorganic materials 0.000 description 2

- 229910008465 Si—Cu Inorganic materials 0.000 description 2

- 229910004121 SrRuO Inorganic materials 0.000 description 2

- 229910002367 SrTiO Inorganic materials 0.000 description 2

- 229910004166 TaN Inorganic materials 0.000 description 2

- 229910008484 TiSi Inorganic materials 0.000 description 2

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 229910052741 iridium Inorganic materials 0.000 description 2

- 229910052748 manganese Inorganic materials 0.000 description 2

- 150000002739 metals Chemical group 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 229910052763 palladium Inorganic materials 0.000 description 2

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 229910052715 tantalum Inorganic materials 0.000 description 2

- 229910052718 tin Inorganic materials 0.000 description 2

- 229910052725 zinc Inorganic materials 0.000 description 2

- 239000000470 constituent Substances 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000000608 laser ablation Methods 0.000 description 1

- 238000002488 metal-organic chemical vapour deposition Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 229910052723 transition metal Inorganic materials 0.000 description 1

- 150000003624 transition metals Chemical class 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0007—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements comprising metal oxide memory material, e.g. perovskites

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0064—Verifying circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B69/00—Erasable-and-programmable ROM [EPROM] devices not provided for in groups H10B41/00 - H10B63/00, e.g. ultraviolet erasable-and-programmable ROM [UVEPROM] devices

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

- G11C2013/009—Write using potential difference applied between cell electrodes

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/30—Resistive cell, memory material aspects

- G11C2213/31—Material having complex metal oxide, e.g. perovskite structure

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/30—Resistive cell, memory material aspects

- G11C2213/32—Material having simple binary metal oxide structure

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/79—Array wherein the access device being a transistor

Landscapes

- Chemical & Material Sciences (AREA)

- Engineering & Computer Science (AREA)

- Materials Engineering (AREA)

- Semiconductor Memories (AREA)

- Read Only Memory (AREA)

Description

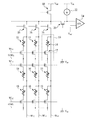

12…選択トランジスタ

14…抵抗記憶素子

16…コラムセレクタ

18…P型トランジスタ

20…N型トランジスタ

22…電流源

24…センスアンプ

26…書き込み回路

28…読み出し回路

30…ロウデコーダ

32…コラム選択信号線

34…コラムデコーダ

36…書き込み制御回路

40…シリコン基板

42…素子分離膜

44…ゲート電極

46,48…ソース/ドレイン領域

50,64,78…層間絶縁膜

52,54,66,80…コンタクトホール

56,58,68,82…コンタクトプラグ

60…グラウンド線

62…中継配線

70…下部電極

72…抵抗記憶層

74…上部電極

76…抵抗記憶素子

84…ビット線

本発明の第1実施形態による不揮発性半導体記憶装置並びにその書き込み方法及び読み出しについて図1乃至図10を用いて説明する。

本発明の第2実施形態による不揮発性半導体記憶装置及びその製造方法について図11乃至図15を用いて説明する。なお、図1に示す第1実施形態による不揮発性半導体記憶装置と同様の構成には同一の符号を付し説明を省略し或いは簡潔にする。

本発明は上記実施形態に限らず種々の変形が可能である。

Claims (9)

- 高抵抗状態と低抵抗状態とを記憶し、電圧の印加によって前記高抵抗状態と前記低抵抗状態とを切り換える抵抗記憶素子と、ドレイン端子が前記抵抗記憶素子の一方の端部に接続され、ソース端子が基準電圧に接続された第1のトランジスタとをそれぞれ有し、マトリクス状に配置された複数のメモリセルと、第1の方向に延在して並行に配された複数の信号線であって、各信号線が、前記第1の方向に並ぶ前記メモリセルの前記第1の抵抗記憶素子の他方の端部に接続された複数のビット線と、前記第1の方向と交差する第2の方向に延在して並行に配された複数の信号線であって、各信号線が、前記第2の方向に並ぶ前記メモリセルの前記第1のトランジスタのゲート電極に接続された複数のワード線と、複数の前記ビット線のそれぞれに接続された複数のトランジスタであって、ソース端子が前記ビット線を介して前記第1の方向に並ぶ前記メモリセルの前記第1の抵抗記憶素子の前記他方の端部に接続され、ドレイン端子に書き込み電圧が印加される複数の第2のトランジスタとを有する不揮発性半導体記憶装置の書き込み方法であって、

複数の前記ワード線のうちの一のワード線に接続された複数の前記メモリセルのうち、書き込み対象の複数の前記メモリセルの前記抵抗記憶素子に、一括して前記低抵抗状態を書き込む工程と、

前記低抵抗状態を書き込んだ複数の前記メモリセルのうち、前記高抵抗状態を書き込むべき前記メモリセルの前記抵抗記憶素子に、選択的に前記高抵抗状態を書き込む工程とを有し、

前記高抵抗状態を書き込む工程では、前記高抵抗状態を書き込むべき前記メモリセルに対応する前記ビット線に接続された前記第2のトランジスタのゲート端子に印加する電圧を、前記抵抗記憶素子のリセット電圧と前記第2のトランジスタの閾値電圧との合計以上、前記抵抗記憶素子のセット電圧と前記閾値電圧との合計未満の値に設定することにより、前記抵抗記憶素子に印加される電圧を、前記リセット電圧以上、前記セット電圧未満の値に制御する

ことを特徴とする不揮発性半導体記憶装置の書き込み方法。 - 請求項1記載の不揮発性半導体記憶装置の書き込み方法において、

前記高抵抗状態を書き込むべき前記メモリセルの前記抵抗記憶素子に前記高抵抗状態が書き込まれたかどうかを検証する工程と、

前記高抵抗状態を書き込むべき前記メモリセルの前記抵抗記憶素子に前記高抵抗状態が書き込まれていない場合に、前記高抵抗状態を再度書き込む工程と

を更に有することを特徴とする不揮発性半導体記憶装置の書き込み方法。 - 請求項1又は2記載の不揮発性半導体記憶装置の書き込み方法において、

前記低抵抗状態を書き込む工程では、書き込み対象の複数の前記メモリセルの前記第1のトランジスタのチャネル抵抗が、前記抵抗記憶素子が高抵抗状態のときの抵抗値よりも十分に小さく且つ前記抵抗記憶素子が低抵抗状態のときの抵抗値よりも十分に大きくなるように、前記一のワード線に印加する電圧を制御する

ことを特徴とする不揮発性半導体記憶装置の書き込み方法。 - 請求項3記載の不揮発性半導体記憶装置の書き込み方法において、

前記低抵抗状態を書き込む工程では、前記第2のトランジスタのゲート端子に、前記書き込み電圧よりも前記第2のトランジスタの閾値電圧分だけ高い駆動電圧を印加する

ことを特徴とする不揮発性半導体記憶装置の書き込み方法。 - 請求項3又は4記載の不揮発性半導体記憶装置の書き込み方法において、

前記低抵抗状態を書き込む工程では、前記書き込み電圧を電源電圧に設定し、前記第2のトランジスタの前記ゲート端子に印加する電圧を、前記電源電圧と前記第2のトランジスタの前記閾値電圧との合計の値に設定し、前記一のワード線に印加する電圧を、前記電源電圧よりも低い値に設定する

ことを特徴とする不揮発性半導体記憶装置の書き込み方法。 - 請求項1乃至5のいずれか1項に記載の不揮発性半導体記憶装置の書き込み方法において、

前記高抵抗状態を書き込む工程では、前記書き込み電圧を、前記抵抗記憶素子のリセット電圧と前記閾値電圧との合計以上の値に設定する

ことを特徴とする不揮発性半導体記憶装置の書き込み方法。 - 請求項1乃至6のいずれか1項に記載の不揮発性半導体記憶装置の書き込み方法において、

前記高抵抗状態を書き込む工程では、前記書き込み電圧、前記第2のトランジスタの前記ゲート端子に印加する電圧、及び前記一のワード線に印加する電圧を、電源電圧に設定する

ことを特徴とする不揮発性半導体記憶装置の書き込み方法。 - 請求項1乃至7のいずれか1項に記載の不揮発性半導体記憶装置の書き込み方法において、

前記高抵抗状態を書き込む工程では、前記一のワード線に印加する電圧を、前記第1のトランジスタのチャネル抵抗が、前記抵抗記憶素子が前記低抵抗状態のときの抵抗値に対して十分に小さい値となるように設定する

ことを特徴とする不揮発性半導体記憶装置の書き込み方法。 - 請求項1乃至8のいずれか1項に記載の不揮発性半導体記憶装置の書き込み方法において、

前記不揮発性半導体記憶装置は、入出力データが多ビットのメモリであり、

前記書き込み対象の複数の前記メモリセルに、前記入出力データの各ビットに対応する情報を記憶する

ことを特徴とする不揮発性半導体記憶装置の書き込み方法。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| PCT/JP2006/317529 WO2008029446A1 (fr) | 2006-09-05 | 2006-09-05 | Procédé d'écriture d'appareil de stockage a semi-conducteur non volatil |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2008029446A1 JPWO2008029446A1 (ja) | 2010-01-21 |

| JP4823316B2 true JP4823316B2 (ja) | 2011-11-24 |

Family

ID=39156891

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008532990A Expired - Fee Related JP4823316B2 (ja) | 2006-09-05 | 2006-09-05 | 不揮発性半導体記憶装置の書き込み方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7898839B2 (ja) |

| JP (1) | JP4823316B2 (ja) |

| WO (1) | WO2008029446A1 (ja) |

Families Citing this family (37)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4684297B2 (ja) * | 2005-10-19 | 2011-05-18 | 富士通株式会社 | 不揮発性半導体記憶装置の書き込み方法 |

| US7768812B2 (en) | 2008-01-15 | 2010-08-03 | Micron Technology, Inc. | Memory cells, memory cell programming methods, memory cell reading methods, memory cell operating methods, and memory devices |

| US8211743B2 (en) | 2008-05-02 | 2012-07-03 | Micron Technology, Inc. | Methods of forming non-volatile memory cells having multi-resistive state material between conductive electrodes |

| JP4469022B2 (ja) * | 2008-05-08 | 2010-05-26 | パナソニック株式会社 | 不揮発性記憶素子、不揮発性記憶装置、および不揮発性記憶素子へのデータ書込方法 |

| CN101779287B (zh) * | 2008-05-22 | 2011-12-21 | 松下电器产业株式会社 | 电阻变化型非易失性存储装置 |

| US8134137B2 (en) | 2008-06-18 | 2012-03-13 | Micron Technology, Inc. | Memory device constructions, memory cell forming methods, and semiconductor construction forming methods |

| US9343665B2 (en) * | 2008-07-02 | 2016-05-17 | Micron Technology, Inc. | Methods of forming a non-volatile resistive oxide memory cell and methods of forming a non-volatile resistive oxide memory array |

| JP5127665B2 (ja) * | 2008-10-23 | 2013-01-23 | 株式会社東芝 | 半導体記憶装置 |

| JP5406515B2 (ja) * | 2008-12-04 | 2014-02-05 | シャープ株式会社 | 可変抵抗素子並びにその製造方法 |

| JP4806046B2 (ja) * | 2009-03-16 | 2011-11-02 | 株式会社東芝 | 半導体記憶装置 |

| US8427859B2 (en) | 2010-04-22 | 2013-04-23 | Micron Technology, Inc. | Arrays of vertically stacked tiers of non-volatile cross point memory cells, methods of forming arrays of vertically stacked tiers of non-volatile cross point memory cells, and methods of reading a data value stored by an array of vertically stacked tiers of non-volatile cross point memory cells |

| US8149610B2 (en) | 2010-05-12 | 2012-04-03 | Macronix International Co., Ltd. | Nonvolatile memory device |

| US8289763B2 (en) | 2010-06-07 | 2012-10-16 | Micron Technology, Inc. | Memory arrays |

| JP5091999B2 (ja) * | 2010-09-24 | 2012-12-05 | シャープ株式会社 | 半導体記憶装置 |

| JP5149358B2 (ja) * | 2010-09-24 | 2013-02-20 | シャープ株式会社 | 半導体記憶装置 |

| US8351242B2 (en) | 2010-09-29 | 2013-01-08 | Micron Technology, Inc. | Electronic devices, memory devices and memory arrays |

| US8759809B2 (en) | 2010-10-21 | 2014-06-24 | Micron Technology, Inc. | Integrated circuitry comprising nonvolatile memory cells having platelike electrode and ion conductive material layer |

| WO2012058324A2 (en) * | 2010-10-29 | 2012-05-03 | Rambus Inc. | Resistance change memory cell circuits and methods |

| US8796661B2 (en) | 2010-11-01 | 2014-08-05 | Micron Technology, Inc. | Nonvolatile memory cells and methods of forming nonvolatile memory cell |

| US8526213B2 (en) | 2010-11-01 | 2013-09-03 | Micron Technology, Inc. | Memory cells, methods of programming memory cells, and methods of forming memory cells |

| US9454997B2 (en) | 2010-12-02 | 2016-09-27 | Micron Technology, Inc. | Array of nonvolatile memory cells having at least five memory cells per unit cell, having a plurality of the unit cells which individually comprise three elevational regions of programmable material, and/or having a continuous volume having a combination of a plurality of vertically oriented memory cells and a plurality of horizontally oriented memory cells; array of vertically stacked tiers of nonvolatile memory cells |

| US8431458B2 (en) | 2010-12-27 | 2013-04-30 | Micron Technology, Inc. | Methods of forming a nonvolatile memory cell and methods of forming an array of nonvolatile memory cells |

| US8791447B2 (en) | 2011-01-20 | 2014-07-29 | Micron Technology, Inc. | Arrays of nonvolatile memory cells and methods of forming arrays of nonvolatile memory cells |

| JP5723253B2 (ja) * | 2011-01-31 | 2015-05-27 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP5598363B2 (ja) | 2011-02-15 | 2014-10-01 | ソニー株式会社 | 記憶装置およびその動作方法 |

| US8488365B2 (en) | 2011-02-24 | 2013-07-16 | Micron Technology, Inc. | Memory cells |

| US8933491B2 (en) * | 2011-03-29 | 2015-01-13 | Micron Technology, Inc. | Arrays of memory cells and methods of forming an array of vertically stacked tiers of memory cells |

| US8537592B2 (en) | 2011-04-15 | 2013-09-17 | Micron Technology, Inc. | Arrays of nonvolatile memory cells and methods of forming arrays of nonvolatile memory cells |

| US9166598B1 (en) * | 2012-05-08 | 2015-10-20 | Altera Corporation | Routing and programming for resistive switch arrays |

| TWI549325B (zh) * | 2013-11-06 | 2016-09-11 | 華邦電子股份有限公司 | 電阻式記憶元件及其操作方法 |

| CN104659203B (zh) * | 2013-11-21 | 2018-01-05 | 华邦电子股份有限公司 | 电阻式存储元件及其操作方法 |

| TWI585902B (zh) * | 2015-04-28 | 2017-06-01 | 華邦電子股份有限公司 | 記憶體裝置及其製造方法 |

| EP3282449B1 (en) * | 2015-06-02 | 2019-08-07 | Huawei Technologies Co. Ltd. | Signal processing circuit |

| TWI579849B (zh) * | 2015-07-15 | 2017-04-21 | 華邦電子股份有限公司 | 記憶元件及其製造方法 |

| CN106356450B (zh) | 2015-07-15 | 2019-03-12 | 华邦电子股份有限公司 | 存储元件及其制造方法 |

| WO2018057014A1 (en) * | 2016-09-24 | 2018-03-29 | Intel Corporation | Asymmetric selectors for memory cells |

| CN115910155A (zh) * | 2021-09-30 | 2023-04-04 | 威比特纳诺有限公司 | 用于复位和置位电流的优化电阻随机存取存储器(ReRAM)单元 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004234707A (ja) * | 2002-12-04 | 2004-08-19 | Sharp Corp | 半導体記憶装置及びメモリセルの書き込み並びに消去方法 |

| JP2005025914A (ja) * | 2003-06-12 | 2005-01-27 | Sharp Corp | 不揮発性半導体記憶装置及びその制御方法 |

| JP2005092912A (ja) * | 2003-09-12 | 2005-04-07 | Sharp Corp | 不揮発性半導体記憶装置 |

| JP2005216387A (ja) * | 2004-01-29 | 2005-08-11 | Sony Corp | 記憶装置 |

| JP2005267837A (ja) * | 2004-02-20 | 2005-09-29 | Renesas Technology Corp | 半導体装置 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4124635B2 (ja) * | 2002-12-05 | 2008-07-23 | シャープ株式会社 | 半導体記憶装置及びメモリセルアレイの消去方法 |

| US7646630B2 (en) * | 2004-11-08 | 2010-01-12 | Ovonyx, Inc. | Programmable matrix array with chalcogenide material |

| JP4684297B2 (ja) * | 2005-10-19 | 2011-05-18 | 富士通株式会社 | 不揮発性半導体記憶装置の書き込み方法 |

| JP4781431B2 (ja) * | 2006-05-16 | 2011-09-28 | 富士通株式会社 | 不揮発性半導体記憶装置及びその書き込み方法 |

-

2006

- 2006-09-05 JP JP2008532990A patent/JP4823316B2/ja not_active Expired - Fee Related

- 2006-09-05 WO PCT/JP2006/317529 patent/WO2008029446A1/ja active Application Filing

-

2009

- 2009-03-05 US US12/398,342 patent/US7898839B2/en not_active Expired - Fee Related

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004234707A (ja) * | 2002-12-04 | 2004-08-19 | Sharp Corp | 半導体記憶装置及びメモリセルの書き込み並びに消去方法 |

| JP2005025914A (ja) * | 2003-06-12 | 2005-01-27 | Sharp Corp | 不揮発性半導体記憶装置及びその制御方法 |

| JP2005092912A (ja) * | 2003-09-12 | 2005-04-07 | Sharp Corp | 不揮発性半導体記憶装置 |

| JP2005216387A (ja) * | 2004-01-29 | 2005-08-11 | Sony Corp | 記憶装置 |

| JP2005267837A (ja) * | 2004-02-20 | 2005-09-29 | Renesas Technology Corp | 半導体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US7898839B2 (en) | 2011-03-01 |

| US20090168495A1 (en) | 2009-07-02 |

| JPWO2008029446A1 (ja) | 2010-01-21 |

| WO2008029446A1 (fr) | 2008-03-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4823316B2 (ja) | 不揮発性半導体記憶装置の書き込み方法 | |

| JP4781431B2 (ja) | 不揮発性半導体記憶装置及びその書き込み方法 | |

| KR101002612B1 (ko) | 불휘발성 반도체 기억 장치 및 그 기입 방법, 판독 방법 및 소거 방법 | |

| JP4684297B2 (ja) | 不揮発性半導体記憶装置の書き込み方法 | |

| JP4880101B1 (ja) | 不揮発性記憶装置及びその駆動方法 | |

| TWI618064B (zh) | 電阻式隨機存取記憶體陣列的操作方法與積體電路晶片 | |

| US8467229B2 (en) | Variable resistance nonvolatile memory device | |

| JP4563511B2 (ja) | 不揮発性記憶装置 | |

| US7532497B2 (en) | Nonvolatile semiconductor memory device and method of writing into the same | |

| JP2008065953A (ja) | 不揮発性半導体記憶装置及びその読み出し方法 | |

| JP4774109B2 (ja) | 不揮発性可変抵抗素子のフォーミング処理の制御回路、並びにフォーミング処理の制御方法 | |

| JPWO2007023569A1 (ja) | 不揮発性半導体記憶装置及びその書き込み方法 | |

| JPWO2006137111A1 (ja) | 不揮発性半導体記憶装置及びその書き込み方法 | |

| JP5157448B2 (ja) | 抵抗記憶素子及び不揮発性半導体記憶装置 | |

| JP2007258533A (ja) | 半導体記憶装置及びその駆動方法 | |

| JP5108672B2 (ja) | 不揮発性メモリセル、不揮発性半導体記憶装置及びその駆動方法 | |

| JP6556435B2 (ja) | 半導体集積回路 | |

| JP2014063549A (ja) | 半導体記憶装置 | |

| JP2013254539A (ja) | 半導体記憶装置 | |

| WO2008050398A1 (fr) | Mémoire à changement de résistance | |

| JP5062176B2 (ja) | 半導体記憶装置、半導体記憶装置の製造方法、半導体記憶装置の書き込み方法及び半導体記憶装置の読み出し方法 | |

| KR20080040734A (ko) | 불휘발성 반도체 기억 장치 및 그 기입 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110524 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110719 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110906 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110906 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140916 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |