JP4785268B2 - 半導体素子を内蔵した多層プリント配線板 - Google Patents

半導体素子を内蔵した多層プリント配線板 Download PDFInfo

- Publication number

- JP4785268B2 JP4785268B2 JP2001123875A JP2001123875A JP4785268B2 JP 4785268 B2 JP4785268 B2 JP 4785268B2 JP 2001123875 A JP2001123875 A JP 2001123875A JP 2001123875 A JP2001123875 A JP 2001123875A JP 4785268 B2 JP4785268 B2 JP 4785268B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- resin

- wiring board

- printed wiring

- chip

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/04105—Bonding areas formed on an encapsulation of the semiconductor or solid-state body, e.g. bonding areas on chip-scale packages

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/12105—Bump connectors formed on an encapsulation of the semiconductor or solid-state body, e.g. bumps on chip-scale packages

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L2224/19—Manufacturing methods of high density interconnect preforms

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/45099—Material

- H01L2224/451—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof

- H01L2224/45138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/45144—Gold (Au) as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73267—Layer and HDI connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/91—Methods for connecting semiconductor or solid state bodies including different methods provided for in two or more of groups H01L2224/80 - H01L2224/90

- H01L2224/92—Specific sequence of method steps

- H01L2224/922—Connecting different surfaces of the semiconductor or solid-state body with connectors of different types

- H01L2224/9222—Sequential connecting processes

- H01L2224/92242—Sequential connecting processes the first connecting process involving a layer connector

- H01L2224/92244—Sequential connecting processes the first connecting process involving a layer connector the second connecting process involving a build-up interconnect

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01013—Aluminum [Al]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1515—Shape

- H01L2924/15153—Shape the die mounting substrate comprising a recess for hosting the device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/156—Material

- H01L2924/15786—Material with a principal constituent of the material being a non metallic, non metalloid inorganic material

- H01L2924/15787—Ceramics, e.g. crystalline carbides, nitrides or oxides

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Non-Metallic Protective Coatings For Printed Circuits (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

Description

【発明の属する技術分野】

本発明は、ビルドアップ多層プリント配線板に関し、特にICチップなどの電子部品を内蔵する多層プリント配線板に関するのもである。

【0002】

【従来の技術】

ICチップは、ワイヤーボンディング、TAB、フリップチップなどの実装方法によって、プリント配線板との電気的接続を取っていた。

ワイヤーボンディングは、プリント配線板にICチップを接着剤によりダイボンディングさせて、該プリント配線板のパッドとICチップのパッドとを金線などのワイヤーで接続させた後、ICチップ並びにワイヤーを守るために熱硬化性樹脂あるいは熱可塑性樹脂などの封止樹脂を施していた。

TABは、ICチップのバンプとプリント配線板のパッドとをリードと呼ばれる線を半田などによって一括して接続させた後、樹脂による封止を行っていた。

フリップチップは、ICチップとプリント配線板のパッド部とをバンプを介して接続させて、バンプとの隙間に樹脂を充填させることによって行っていた。

【0003】

【発明が解決しようとする課題】

しかしながら、それぞれの実装方法は、ICチップとプリント配線板の間に接続用のリード部品(ワイヤー、リード、バンプ)を介して電気的接続を行っている。それらの各リード部品は、切断、腐食し易く、これにより、ICチップとの接続が途絶えたり、誤作動の原因となることがあった。

また、それぞれの実装方法は、ICチップを保護するためにエポキシ樹脂等の熱可塑性樹脂によって封止を行っているが、その樹脂を充填する際に気泡を含有すると、気泡が起点となって、リード部品の破壊やICパッドの腐食、信頼性の低下を招いてしまう。熱可塑性樹脂による封止は、それぞれの部品に合わせて樹脂装填用プランジャー、金型を作成する必要が有り、また、熱硬化性樹脂であってもリード部品、ソルダーレジストなどの材質などを考慮した樹脂を選定しなくては成らないために、それぞれにおいてコスト的にも高くなる原因にもなった。

【0004】

このため基板内に半導体素子を埋め込む技術が種々提案されている。基板に半導体素子を埋め込んで、その上層にビルドアップ層を形成させることにより電気的接続を取る技術としては、特開平9−321408号(USP5875100)、特開平10−256429号、特開平11−126978号、などが提案されている。

【0005】

特開平9−321408号(USP5875100)では、ダイパッド上にスタッドバンプを形成した半導体素子をプリント配線板に内蔵して、スタッドバンプ上に配線を形成して電気的接続を取っていた。しかし、このスタッドバンプの高さのばらつきが大きいため、接続性に問題があった。また、このスタッドバンプをボンディングにより一つ一つ植設しており、生産性にも問題があった。

【0006】

特開平10−256429号では、セラミック基板に半導体素子を内蔵して、フリップチップ形態により電気的接続を取っていた。しかし、セラミックは外形加工性が悪く、半導体素子の納まりがよくない。また、該バンプの高さのばらつきが大きいため、接続性に問題があった。

【0007】

特開平11−126978号では、バイアホールを介して積蔵された多層プリント配線板の空隙の収容部に半導体素子を内蔵して、導体回路と接続を取っていた。しかし、収容部が空隙であるため、位置ずれを引き起こしやすく、接続性に問題があった。また、ダイパッドと導体回路とを直接接続させているため、ダイパッドに酸化被膜ができやすく、絶縁抵抗が上昇する問題もあった。

【0008】

また、半導体素子を内蔵した基板で構成された多層プリント配線板をパッケージ基板、チップセットなどとして用いる場合には、外部基板(いわゆるマザーボード、ドータボードと呼ばれるもの)と電気接続させることによって、機能を発揮することができる。そのため、該多層プリント配線板には、BGAや導電性接続ピン(PGA)を配設することが必要となる。このBGA、PGAは、多層プリント配線板の表層のソルダーレジスト層に、半田パッドを配設することで形成される。

【0009】

しかしながら、半導体素子を埋め込んだ基板で表層に半田バンプを配設して、外部基板と電気的に接続させて機能試験や信頼性試験を行うと、層間絶縁層、ソルダーレジスト層、層間樹脂絶縁層やソルダーレジスト、半田バンプおよび半田バンプの周囲(半田層や耐食金属などを意図する)にクラック、剥離が発生して、半田バンプの脱落や位置ずれが確認された。特に、層間絶縁層を貫通して、半導体素子のパッドにクラックが発生しているものも確認された。したがって、半導体素子を内蔵する多層プリント配線板においては、半田バンプと導体回路との電気的接続性や信頼性の低下が明らかになった。

【0010】

本発明は上述した課題を解決するためになされたものであり、その目的とするところは、電気的接続性や信頼性の高い多層プリント配線板、特に、半導体素子が内蔵された多層プリント配線板を提案することを目的とする。

【0011】

【課題を解決するための手段】

上記した目的を達成するため、請求項1に記載の多層プリント配線板では、半導体素子を内蔵した基板上に層間絶縁層と導体層とが繰り返し形成され、前記層間絶縁層には、バイアホールが形成され、前記バイアホールを介して電気的接続される多層プリント配線板において、前記基板内の半導体素子の直上以外の領域において、前記バイアホールに接続された複数の外部接続端子(BGA/PGA)が、グリッド状または千鳥状に形成され、前記バイアホールは銅で構成され、前記半導体素子のパッド部分には、銅で構成された層を含む複数の層を有し、最下層の前記層間絶縁層に形成された前記バイアホールと接続するための、前記半導体素子のパッドの径よりも径の大きな仲介層が形成され、前記銅で構成された層と前記バイアホールとが接続されていることを技術的特徴とする。

【0012】

請求項1の発明では、多層プリント配線板の半導体素子が内蔵された基板上の領域と、半導体素子が内蔵されていない基板上の領域とを区別する。そして、半導体素子が内蔵されていない基板上の領域に外部接続端子(BGA/PGA)を配設する。

上述した外部接続端子(BGA/PGA)の周囲などに発生した剥離、クラックは、半導体素子、外部基板、層間絶縁層およびソルダーレジスト層の熱膨張係数の差から生じている。即ち、セラミックから成る半導体素子および外部基板は、熱膨張係数が小さく、熱膨張による伸びは小さい。一方、樹脂から成る層間絶縁層およびソルダーレジスト層は、半導体素子および外部基板と比較して熱膨張係数が大きいため、熱膨張による伸びは大きい。この熱膨張係数の差によって、外部接続端子(BGA/PGA)の周囲などに応力が集中して剥離、クラックが発生する。

つまり、半導体素子の内蔵されていない基板上の領域に外部接続端子(BGA/PGA)を配設することによって、熱膨張による影響を小さくできるため、外部接続端子(BGA/PGA)の周囲などに発生する剥離、クラックを防止できる。したがって、外部接続端子(BGA/PGA)の脱落や位置ずれを防止して、電気的接続性や信頼性を向上させることが可能となる。

【0013】

ここで、外部接続端子とは、ICチップを実装した基板において、外部基板、いわゆるマザーボード、ドータボードとの接続を取るための端子を意味する。懸案の端子とは、BGA、PGA及び半田バンプを言う。

【0015】

また、請求項1の発明では、半導体素子のパッドを覆うようにして仲介層を形成させている。ICチップのパッドに仲介層を設ける理由は、次の通りである。ICチップのパッドは一般的にアルミニウムなどで製造されている。仲介層を形成させていないパッドのままで、フォトエッチングにより層間絶縁層のバイアホールを形成させた時、パッドのままであれば露光、現像後にパッドの表層に樹脂が残りやすかった。それに、現像液の付着によりパッドの変色を引き起こした。一方、レーザの場合、ビア径がパッド径より大きいときには、パッド及びパシベーション(ICの保護膜)がレーザによって破壊される。また、後工程に、酸や酸化剤あるいはエッチング液に浸漬させたり、種々のアニール工程を経ると、ICチップのパッドの変色、溶解が発生した。更に、ICチップのパッドは、20〜60μm程度の径で作られており、バイアホールはそれより大きいので位置ずれの際に未接続が発生しやすい。

【0016】

これに対して、パッド上に銅等からなる仲介層を設けることで、溶剤の使用が可能となりパッド上の樹脂残りを防ぐことができる。また、後工程の際に酸や酸化剤あるいはエッチング液に浸漬させたり、種々のアニール工程を経てもパッドの変色、溶解が発生しない。パッドの酸化皮膜の形成を防げる。これにより、パッドとバイアホールとの接続性や信頼性を向上させる。更に、ICチップのパッド上に20μmよりも大きな径の仲介層を介在させることで、バイアホールを確実に接続させることができる。望ましいのは、仲介層は、バイアホール径と同等以上のものがよい。

【0017】

また、パッドより大きい仲介層を形成させることによって、検査用プローブピンが接触しやすくなり、検査を容易に行える。即ち、半導体素子を基板に内蔵する前もしくはその後に検査を行えるため、予め製品の可否を判定することができる。したがって、生産性の向上やコストの低減が可能となる。つまり、仲介層を備える半導体素子は、プリント配線板に内蔵するための半導体素子であるといえる。

【0018】

本発明で定義されている仲介層について説明する。仲介層は、半導体素子であるICチップとプリント配線板とを直接に接続を取るため、設けられた中間の仲介層を意味する。その特徴として、パッド上に薄膜層を形成し、その上に厚付け層が形成されてなる、少なくとも2層以上の金属層で形成されている。そして、半導体素子であるICチップのパッドよりも大きくさせる。それによって、電気的接続や位置合わせ性を向上させるものであり、かつ、パッドにダメージを与えることなくレーザやフォトエッチングによるバイアホール加工を可能にするものである。そのため、ICチップのプリント配線板への内蔵や接続を確実にすることができる。また、仲介層には、直接、プリント配線板の導体回路である金属を形成することを可能にする。その導体回路の一例としては、層間絶縁層のバイアホールや基板上のスルーホールなどがある。

【0019】

仲介層は、次のように形成される。ICチップの全面に蒸着、スパッタリングなどを行い、全面に導電性の金属膜(第1薄膜層)を形成させる。その金属としては、スズ、クロム、チタン、ニッケル、亜鉛、コバルト、金、銅などがよい。厚みとしては、0.001〜2.0μmの間で形成させるのがよい。0.001μm未満では、全面に均一に積層できない。2.0μmを越えるものを形成させることは困難であり、効果が高まるのもでもなかった。クロムの場合には0.1μmの厚みが望ましい。特に、0.01〜1.0μmが望ましい。特に、ニッケル、クロム、チタンで形成するのがよい。界面から湿分の侵入がなく、金属密着性に優れるからである。

【0020】

第1薄膜層により、パッドの被覆を行い、仲介層とICチップにパッドとの界面の密着性を高めることができる。また、これら金属でパッドを被覆することで、界面への湿分の侵入を防ぎ、パッドの溶解、腐食を防止し、信頼性を高めることができる。また、この第1薄膜層によって、リードのない実装方法によりICチップとの接続を取ることができる。ここで、クロム、チタンを用いることが、界面への湿分の侵入を防ぐために望ましい。

【0021】

第1薄膜層上に、スパッタ、蒸着、又は、無電解めっきにより第2薄膜層を形成させる。その金属としてはニッケル、銅、金、銀などがある。電気特性、経済性、また、後程で形成される厚付け層は主に銅であることから、銅を用いるとよい。

【0022】

ここで第2薄膜層を設ける理由は、第1薄膜層では、後述する厚付け層を形成するための電解めっき用のリードを取ることができないためである。第2薄膜層36は、厚付けのリードとして用いられる。その厚みは0.01〜5μmの範囲で行うのがよい。0.01μm未満では、リードとしての役割を果たし得ず、5μmを越えると、エッチングの際、下層の第1薄膜層がより多く削れて隙間ができてしまい、湿分が侵入し易くなり、信頼性が低下するからである。

【0023】

第2薄膜層上に、無電解あるいは電解めっきにより厚付けさせる。形成される金属の種類としては銅、ニッケル、金、銀、亜鉛、鉄などがある。電気特性、経済性、仲介層としての強度や構造上の耐性、また、後程で形成されるビルドアップである導体層は主に銅であることから、銅を用い電解めっきで形成するのが望ましい。その厚みは1〜20μmの範囲で行うのがよい。1μmより薄いと、上層のバイアホールとの接続信頼性が低下し、20μmよりも厚くなると、エッチングの際にアンダーカットが起こってしまい、形成される仲介層とバイアホールと界面に隙間が発生するからである。また、場合によっては、第1薄膜層上に直接厚付けめっきしても、さらに、多層に積層してもよい。

【0024】

その後、エッチングレジストを形成して、露光、現像して仲介層以外の部分の金属を露出させてエッチングを行い、ICチップのパッド上に第1薄膜層、第2薄膜層、厚付け層からなる仲介層を形成させる。

【0025】

また、上記仲介層の製造方法以外にも、ICチップ上に形成した金属膜上に電解めっきによって厚付けした後、ドライフィルムレジストを形成して仲介層に該当する以外の部分を除去させて、パッド上に仲介層を形成させることもできる。更に、ICチップをコア基板に取り付けた後に、同様にしてICチップのパッド上に仲介層を形成させることもできる。

【0026】

請求項2の発明では、請求項1に記載の多層プリント配線板において、前記銅で構成された層は、めっきにより形成されることを特徴とする。

請求項3の発明では、請求項2に記載のプリント配線板において、前記銅で構成された層の厚みは、1〜20μmであることを特徴とする。

請求項4の発明では、請求項1〜3のいずれかに記載の多層プリント配線板において、半導体素子を内蔵する前記基板の凹部または通孔と、前記半導体素子との間に、樹脂充填材料を充填したことを技術的特徴とする。

【0027】

請求項4の発明では、基板の凹部または通孔と、半導体素子との間に、樹脂充填材料を充填することにより、基板と半導体素子との接着性を向上させる。また、この樹脂充填材料は、熱膨張によって発生した応力を緩和するため、コア基板のクラック、層間樹脂絶縁層及びソルダーレジスト層のうねりを防止することが可能となる。このため、半田バンプの周囲などに発生する剥離、クラックを防止できる。したがって、半田パンプの脱落や位置ずれを防止できるため、電気的接続性や信頼性を向上させることが可能となる。樹脂充填材料は、熱硬化性樹脂、熱可塑性樹脂、もしくはそれらの複合体を用いることができる。

【0028】

【発明の実施の形態】

以下、本発明の実施形態について図を参照して説明する。

[第1実施形態]

先ず、本発明の第1実施形態に係る多層プリント配線板の構成について、多層プリント配線板10の断面を示す図14を参照して説明する。

【0029】

図14に示すように多層プリント配線板10は、ICチップ20を収容するコア基板30と、層間樹脂絶縁層50、層間樹脂絶縁層150、層間樹脂絶縁層250とからなる。層間樹脂絶縁層50には、バイアホール60および導体回路58が形成され、層間樹脂絶縁層150には、バイアホール160および導体回路158が形成され、層間樹脂絶縁層250には、バイアホール260および導体回路258が形成されている。

【0030】

層間樹脂絶縁層250の上には、ソルダーレジスト層70が配設されている。ソルダーレジスト層70の開口部71下の導体回路258には、図示しないドータボード、マザーボード等の外部基板と接続するためのBGA76が設けられている。BGA76は、ICチップ20の直上の領域R1以外の領域R2に配設されている。

【0031】

ICチップ20には、ICチップ20を保護するパッシベーション膜24が被覆され、該パッシベーション膜24の開口内に入出力端子を構成するパッド22が配設されている。パッド22の上には、主として銅からなる仲介層38が形成されている。

【0032】

ICチップ20と、基板30の凹部32内との間には、樹脂材料である接着材料34が充填されている。接着材料34によって、ICチップ20は基板30の凹部内で固定されている。この樹脂充填材料34は、熱膨張によって発生した応力を緩和するため、コア基板30のクラック、層間樹脂絶縁層50、150、250及びソルダーレジスト層70のうねりを防止することが可能となる。このため、BGA76の周囲などに発生する剥離、クラックを防止できる。したがって、半田パンプ76の脱落や位置ずれを防止できるため、電気的接続性や信頼性を向上させることが可能となる。

【0033】

図14中の多層プリント配線板10のE−E断面を図16に示す。図16の点線で示される内側の領域は、ICチップ20が内蔵されている領域R1である。図16の点線の外側から実線の内側の領域は、ICチップ20が内蔵されていない領域R2である。導体回路258は、放射線状に領域R1から領域R2へ広がるように形成されている。BGA76と接続するための半田パッド75は、領域R2内でグリッド状に配置されている。

【0034】

図17(A)は、図14中の多層プリント配線板10の平面図を示している。BGA76は、領域R2内でグリッド状に配置されて、図示しないドータボード、マザーボード等の外部基板と接続される。なお、BGA76は、図17(B)に示すように領域R2内で千鳥状に形成されてもよい。

【0035】

本実施形態の多層プリント配線板では、ICチップ20が内蔵されていない基板上の領域R2にBGA76を配設する。

つまり、ICチップ20の直上外の領域R2にBGA76を配設することによって、セラミックから成り熱膨張係数の小さなICチップ20と、樹脂から成る熱膨張係数の大きな層間絶縁層50、150、250およびソルダーレジスト層70との熱膨張による影響を小さくできるため、BGA76の周囲などに発生する剥離、クラックを防止できる。したがって、半田パンプ76の脱落や位置ずれを防止して、電気的接続性や信頼性を向上させることが可能となる。

【0036】

また、本実施例の多層プリント配線板10では、コア基板30にICチップ20を内蔵させて、該ICチップ20のパッド22には仲介層38を配設させている。このため、リード部品や封止樹脂を用いず、ICチップと多層プリント配線板(パッケージ基板)との電気的接続を取ることができる。また、ICチップ部分に仲介層38が形成されていることから、ICチップ部分には平坦化されるので、上層の層間絶縁層50も平坦化されて、膜厚みも均一になる。更に、仲介層によって、上層のバイアホール60を形成する際も形状の安定性を保つことができる。

【0037】

更に、パッド22上に銅製の仲介層38を設けることで、パッド22上の樹脂残りを防ぐことができ、また、後工程の際に酸や酸化剤あるいはエッチング液に浸漬させたり、種々のアニール工程を経てもパッド22の変色、溶解が発生しない。これにより、ICチップのパッドとバイアホールとの接続性や信頼性を向上させる。更に、40μm径パッド22上に60μm径以上の仲介層38を介在させることで、60μm径のバイアホールを確実に接続させることができる。

【0038】

A.半導体素子先ず、図18を参照して上述した多層プリント配線板10に内蔵する半導体素子(ICチップ)の構成について、半導体素子20の断面を示す図3(B)、及び、平面図を示す図4(B)を参照して説明する。

【0039】

図3(B)に示すように半導体素子20の上面には、パッド22及び配線(図示せず)が配設されており、該パッド22及び配線の上に、パッシベーション膜24が被覆され、該パッド22には、パッシベーション膜24の開口が形成されている。パッド22の上には、主として銅からなる仲介層38が形成されている。仲介層38は、薄膜層33と電解めっき膜(厚付け膜)37とからなる。言い換えると、2層以上の金属膜で形成されている。

【0040】

[第1の製造方法]

引き続き、図3(B)を参照して上述した半導体素子の第1の製造方法について、図1〜図4を参照して説明する。

【0041】

(1)先ず、図1(A)に示すシリコンウエハー20Aに、定法により配線21及びパッド22を形成する(図1(B)及び図1(B)の平面図を示す図4(A)参照、なお、図1(B)は、図4(A)のB−B断面を表している)。

(2)次に、パッド22及び配線21の上に、パッシベーション膜24を形成し、パッド22上に開口24aを設ける(図1(C))。

【0042】

(3)シリコンウエハー20Aに蒸着、スパッタリングなどの物理的な蒸着を行い、全面に導電性の金属膜(薄膜層)33を形成させる(図2(A))。その厚みは、0.001〜2μmの範囲で形成させるのがよい。その範囲よりも下の場合は、全面に薄膜層を形成することができない。その範囲よりも上の場合は、形成される膜に厚みのバラツキが生じてしまう。最適な範囲は0.01〜1.0μmである。形成する金属としては、スズ、クロム、チタン、ニッケル、亜鉛、コバルト、金、銅の中から、選ばれるものを用いることがよい。それらの金属は、パッドの保護膜となり、かつ、電気特性を劣化させることがない。第1の製造方法では、薄膜層33は、スパッタを用いてクロムにより形成される。また、クロム薄膜層33の上に銅薄膜層をスパッタを用いて形成してもよい。クロム、銅の2層を真空チャンバー内で連続して形成することもできる。このとき、クロム0.05μm−0.1μm、銅0.5μm程度の厚みである。

【0043】

(4)その後、液状レジスト、感光性レジスト、ドライフィルムのいずれかのレジスト層を薄膜層33上に形成させる。仲介層38を形成する部分が描画されたマスク(図示せず)を該レジスト層上に、載置して、露光、現像を経て、メッキレジスト35に非形成部35aを形成させる。電解メッキを施してレジスト層の非形成部35aに厚付け層(電解めっき膜)37を設ける(図2(B))。形成されるメッキの種類としては銅、ニッケル、金、銀、亜鉛、鉄などがある。電気特性、経済性、また、後程で形成されるビルドアップである導体層は主に銅であることから、銅を用いるとよく、第1の製造方法では、銅を用いる。その厚みは1〜20μmの範囲で行うのがよい。

【0044】

(5)メッキレジスト35をアルカリ溶液等で除去した後、メッキレジスト35下の金属膜33を硫酸−過酸化水素水、塩化第二鉄、塩化第二銅、第二銅錯体−有機酸塩等のエッチング液によって除去することで、ICチップのパッド22上に仲介層38を形成する(図2(C))。

【0045】

(6)次に、基板にエッチング液をスプレイで吹きつけ、仲介層38の表面をエッチングすることにより粗化面38αを形成する(図3(A)参照)。無電解めっきや酸化還元処理を用いて粗化面を形成することもできる。

【0046】

(7)最後に、仲介層38が形成されたシリコンウエハー20Aを、ダイシングなどによって個片に分割して半導体素子20を形成する(図3(B)及び図3(B)の平面図である図4(B)参照)。その後、必要に応じて、分割された半導体素子20の動作確認や電気検査を行なってもよい。半導体素子20は、パッド22よりも大きな仲介層38が形成されているので、プローブピンが当てやすく、検査の精度が高くなっている。

【0047】

[第2の製造方法]

第2の製造方法に係る半導体素子20の製造方法について図5及び図6を参照して説明する。

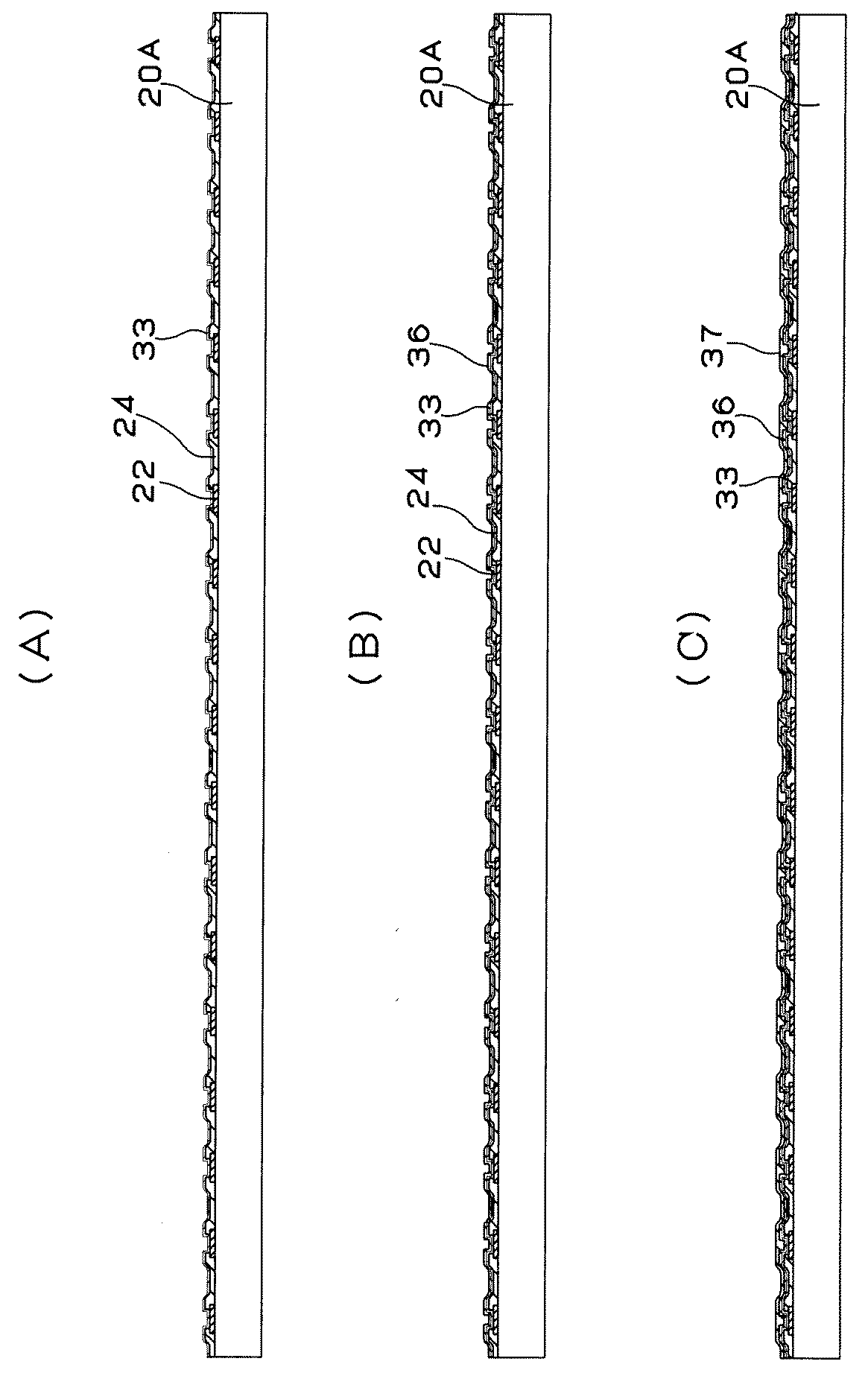

(1)第1の製造方法で図2(B)を参照して上述したように、シリコンウエハー20Aに蒸着、スパッタリングなどの物理的な蒸着を行い、全面に導電性の金属膜(第1薄膜層)33を形成させる(図5(A))。その厚みは、0.001〜2μmの範囲がよい。その範囲よりも下の場合は、全面に薄膜層を形成することができない。その範囲よりも上の場合は、形成される膜に厚みのバラツキが生じてしまう。最適な範囲は0.01〜1.0μmで形成されることがよい。形成する金属としては、スズ、クロム、チタン、ニッケル、亜鉛、コバルト、金、銅の中から、選ばれるものを用いることがよい。それらの金属は、パッドの保護膜となり、かつ、電気特性を劣化させることがない。第2の製造方法では、薄膜層33は、クロムにより形成される。

【0048】

(2)第1薄膜層33の上に、スパッタ、蒸着、無電解めっきによって第2薄膜層36を積層する(図5(B))。その場合積層できる金属は、ニッケル、銅、金、銀の中から選ばれるものがよい。特に、銅、ニッケルのいずれかで形成させることがよい。銅は、廉価であることと電気伝達性がよいからである。ニッケルは、薄膜との密着性がよく、剥離やクラックを引き起こし難い。第2の製造方法では、第2薄膜層36を無電解銅めっきにより形成する。厚みは、0.01〜5μmがよく、特に、0.1〜3μmが望ましい。

なお、望ましい第1薄膜層と第2薄膜層との組み合わせは、クロム−銅、クロム−ニッケル、チタン−銅、チタン−ニッケルである。金属との接合性や電気伝達性という点で他の組み合わせよりも優れる。

【0049】

(3)その後、レジスト層を厚付け層上に形成させる。仲介層38を形成する部分が描画されたマスク(図示せず)を該レジスト層上に、載置して、露光、現像を経て、メッキレジスト35に非形成部35aを形成させる。電解メッキを施してレジスト層の非形成部35aに厚付け層(電解めっき膜)37を設ける(図5(C))。形成されるメッキの種類としては銅、ニッケル、金、銀、亜鉛、鉄などがある。電気特性、経済性、また、後程で形成されるビルドアップである導体層は主に銅であることから、銅を用いるとよく、第2の製造方法では、銅を用いる。その厚みは1〜20μmの範囲で行うのがよい。

【0050】

(4)メッキレジスト35をアルカリ溶液等で除去した後、メッキレジスト35下の金属膜33、金属膜36を硫酸−過酸化水素水、塩化第二鉄、塩化第二銅、第二銅錯体−有機酸塩等のエッチング液によって除去することで、ICチップのパッド22上に仲介層38を形成する(図6)。

【0051】

(5)次に、基板にエッチング液をスプレイで吹きつけ、仲介層38の表面をエッチングすることにより粗化面を形成する。以降の工程は、第1の製造方法と同様であるため説明を省略する。

【0052】

[第3の製造方法]

第3の製造方法に係る半導体素子20の製造方法について図7及び図8を参照して説明する。第3の製造方法の半導体素子の構成は、図3(B)を参照して上述した第1の製造方法とほぼ同様である。但し、第1の製造方法では、セミアディテブ工程を用い、レジスト非形成部に厚付け層37を形成することで仲介層38を形成した。これに対して、第3の製造方法では、フルアディテブ工程を用い、厚付け層37を均一に形成した後、レジストを設け、レジスト非形成部をエッチングで除去することで仲介層38を形成する。

【0053】

この第3の製造方法の製造方法について参照して説明する。

(1)第1の製造方法で図2(B)を参照して上述したように、シリコンウエハー20Aに蒸着、スパッタリングなどの物理的な蒸着を行い、全面に導電性の金属膜33を形成させる(図7(A))。その厚みは、0.001〜2.0μmの範囲がよい。その範囲よりも下の場合は、全面に薄膜層を形成することができない。その範囲よりも上の場合は、形成される膜に厚みのバラツキが生じてしまう。最適な範囲は0.01〜1.0μmで形成されることがよい。形成する金属としては、スズ、クロム、チタン、ニッケル、亜鉛、コバルト、金、銅の中から、選ばれるものを用いることがよい。それらの金属は、パッドの保護膜となり、かつ、電気特性を劣化させることがない。第3の製造方法では、薄膜層33は、クロムにより形成される。さらに、その上に、薄膜層を積層してもよい。その場合積層できる金属は、ニッケル、銅、金、銀の中から選ばれるものがよい。特に、銅、ニッケルのいずれかで形成させるとことがよい。銅は、廉価であることと電気伝達性がよいからである。ニッケルは、薄膜との密着性がよく、剥離やクラックを引き起こし難い。

なお、望ましい第2薄膜層との組み合わせは、クロム−銅、クロム−ニッケル、チタン−銅、チタン−ニッケルである。金属との接合性や電気伝達性という点で他の組み合わせよりも優れる。また、薄膜の形成には、スパッタ、蒸着、無電解めっきによって行うことができる。

【0054】

ICチップ20Aの全面に蒸着、スパッタリングなどの物理的な蒸着を行い、全面に導電性の金属膜36を形成させる(図7(B))。その金属としては、スズ、クロム、チタン、ニッケル、亜鉛、コバルト、金、銅などの金属を1層以上形成させるものがよい。厚みとしては、0.001〜2.0μmの間で形成させるのがよい。

【0055】

該金属膜36の上に、更に無電解めっき等により金属膜を設けることもできる。上側の金属膜は、ニッケル、銅、金、銀などの金属を1層以上形成させるものがよい。

【0056】

その金属膜36上に、無電解あるいは電解めっきにより、厚付けしめっき膜37を形成させる(図7(C))。形成されるめっきの種類としてはニッケル、銅、金、銀、亜鉛、鉄などがある。電気特性、経済性、また、後程で形成されるビルドアップである導体層は主に銅であることから、銅を用いることがよい。その厚みは1〜20μmの範囲で行うのがよい。それより厚くなると、エッチングの際にアンダーカットが起こってしまい、形成される仲介層とバイアホールと界面に隙間が発生することがある。その後、エッチングレジストを形成して、露光、現像して仲介層以外の部分の金属を露出させてエッチングを行い、ICチップのパッド上に仲介層を形成させる。

【0057】

(3)その後、レジスト層35を厚付け層37上に形成させる(図8(A))。

【0058】

(4)メッキレジスト35の非形成部の金属膜33及び厚付け層37を硫酸−過酸化水素水、塩化第二鉄、塩化第二銅、第二銅錯体−有機酸塩等のエッチング液によって除去した後、メッキレジスト35を剥離することで、ICチップのパッド22上に仲介層38を形成する(図8(B))。以降の工程は、第1の製造方法と同様であるため説明を省略する。

【0059】

引き続き、図14を参照して上述した多層プリント配線板の製造方法について、図9〜図13を参照して説明する。

【0060】

(1)先ず、ガラスクロス等の心材にエポキシ等の樹脂を含浸させたプリプレグを積層した絶縁樹脂基板(コア基板)30を出発材料として用意する(図9(A)参照)。次に、コア基板30の片面に、ザグリ加工でICチップ内蔵用の凹部32を形成する(図9(B)参照)。ここでは、ザグリ加工により凹部を設けているが、開口を設けた絶縁樹脂基板と開口を設けない樹脂絶縁基板とを張り合わせることで、内蔵部を備えるコア基板を形成できる。

【0061】

ICチップなどの電子部品を内蔵させる樹脂製基板としては、エポキシ樹脂、BT樹脂、フェノール樹脂などにガラスエポキシ樹脂などの補強材や心材を含接続接続引用文献に対する技術的特徴は浸させた樹脂、エポキシ樹脂を含浸させたプリプレグを積層させたものなどが用いられるが、一般的にプリント配線板で使用されるものを用いることができる。それ以外にも両面銅張積層板、片面板、金属膜を有しない樹脂板、樹脂シートを用いることができる。ただし、350℃以上の温度を加えると樹脂は、溶解、炭化をしてしまう。

【0062】

(2)その後、凹部32に、印刷機を用いて接着材料34を塗布する。このとき、塗布以外にも、ポッティングなどをしてもよい。次に、図1〜図8を参照して上述した製造方法に係るICチップ20を接着材料34上に載置する(図9(C)参照)。接着材料34は、コア基板30よりも熱膨張係数の大きな樹脂を用いる。これにより、ICチップ20とコア基板30との熱膨張差を吸収させる。

【0063】

(3)そして、ICチップ20の上面を押す、もしくは叩いて凹部32内に完全に内蔵させる(図9(D)参照)。これにより、コア基板30を平滑にすることができる。この際に、接着材料34がICチップ20の上面にかかることがあるが、後述するようにICチップ20の上面の樹脂層を設けてからレーザでバイアホール用の開口を設けるため、仲介層とバイアホールとの接続に影響を与えることがない。

【0064】

(4)上記工程を経た基板30に、厚さ50μmの熱硬化型樹脂シートを温度50〜150℃まで昇温しながら圧力5kg/cm2で真空圧着ラミネートし、層間樹脂絶縁層50を設ける(図10(A)参照)。真空圧着時の真空度は、10mmHgである。

【0065】

層間樹脂絶縁層としては、熱硬化性樹脂、熱可塑性樹脂、感光性樹脂、熱硬化性樹脂の一部を感光基で置換した樹脂、熱硬化性樹脂と熱可塑性樹脂との樹脂複合体、感光性樹脂と熱可塑性樹脂との複合体などを用いることができる。

熱硬化性樹脂としては、エポキシ樹脂、フェノール樹脂、ポリイミド樹脂、ポリオレフィン樹脂、フッ素樹脂等が挙げられる。熱可塑性樹脂としては、ポリエーテルスルフォン(PES)、ポリエーテルイミド、フェノキシ樹脂などを用いることができる。またそれらの樹脂複合体として用いた時でも、各1種類以上の樹脂を混合して用いてもよい。例えば、エポキシ樹脂、フェノール樹脂、フェノキシ樹脂といった組み合わせがある。

【0066】

また、層間樹脂絶縁層50は、上述したように、半硬化状態にした樹脂をシート状にして加熱圧着する代わりに、予め粘度を調整した樹脂組成物を、ロールコータやカーテンコータなどによって塗布することで形成することもできる。

【0067】

(5)次に、波長10.4μmのCO2ガスレーザにて、ビーム径5mm、トップハットモード、パルス幅5.0μ秒、マスクの穴径0.5mm、1ショットの条件で、層間樹脂絶縁層50に直径60μmのバイアホール用開口48を設ける(図10(B)参照)。60℃の過マンガン酸を用いて、開口48内の樹脂残りを除去する。パッド22上に銅製の仲介層38を設けることで、パッド22上の樹脂残りを防ぐことができ、これにより、パッド22と後述するバイアホール60との接続性や信頼性を向上させる。更に、40μm径パッド22上に60μm以上の径の仲介層38を介在させることで、60μm径のバイアホール用開口48を確実に接続させることができる。なお、ここでは、過マンガン酸を用いて樹脂残さを除去したが、酸素プラズマを用いてデスミア処理を行うことも可能である。

【0068】

(6)次に、クロム酸、過マンガン酸塩などの酸化剤等に浸漬させることによって、層間樹脂絶縁層50の粗化面50αを設ける(図10(C)参照)。該粗化面50αは、0.05〜5μmの範囲で形成されることがよい。その一例として、過マンガン酸ナトリウム溶液50g/l、温度60℃中に5〜25分間浸漬させることによって、2〜3μmの粗化面50αを設ける。上記以外には、日本真空技術株式会社製のSV−4540を用いてプラズマ処理を行い、層間樹脂絶縁層50の表面に粗化面50αを形成することもできる。この際、不活性ガスとしてはアルゴンガスを使用し、電力200W、ガス圧0.6Pa、温度70℃の条件で、2分間プラズマ処理を実施する。

【0069】

(7)粗化面50αが形成された層間樹脂絶縁層50上に、金属層52を設ける(図11(A)参照)。金属層52は、無電解めっきによって形成させる。予め層間樹脂絶縁層50の表層にパラジウムなどの触媒を付与させて、無電解めっき液に5〜60分間浸漬させることにより、0.1〜5μmの範囲でめっき膜である金属層52を設ける。その一例として、

〔無電解めっき水溶液〕

NiSO4 0.003 mol/l

酒石酸 0.200 mol/l

硫酸銅 0.030 mol/l

HCHO 0.050 mol/l

NaOH 0.100 mol/l

α、α′−ビピルジル 100 mg/l

ポリエチレングリコール(PEG) 0.10 g/l

34℃の液温度で40分間浸漬させた。

上記以外でも上述したプラズマ処理と同じ装置を用い、内部のアルゴンガスを交換した後、Ni及びCuをターゲットにしたスパッタリングを、気圧0.6Pa、温度80℃、電力200W、時間5分間の条件で行い、Ni/Cu金属層52を層間樹脂絶縁層50の表面に形成することもできる。このとき、形成されるNi/Cu金属層52の厚さは0.2μmである。また、スパッタの代わりに、蒸着、電着等で金属膜を形成することもできる。更に、スパッタ、蒸着、電着などの物理的な方法で薄付け層を形成した後、無電解めっきを施すことも可能である。

【0070】

(8)上記処理を終えた基板30に、市販の感光性ドライフィルムを貼り付け、フォトマスクフィルムを載置して、100mJ/cm2で露光した後、0.8%炭酸ナトリウムで現像処理し、厚さ15μmのめっきレジスト54を設ける(図11(B)参照)。次に、以下の条件で電解めっきを施して、厚さ15μmの電解めっき膜56を形成する(図11(C)参照)。なお、電解めっき水溶液中の添加剤は、アトテックジャパン社製のカパラシドHLである。

【0071】

【0072】

(9)めっきレジスト54を5%NaOHで剥離除去した後、そのめっきレジスト下の金属層52を硝酸および硫酸と過酸化水素の混合液を用いるエッチングにて溶解除去し、金属層52と電解めっき膜56からなる厚さ16μmの導体回路58及びバイアホール60を形成する(図12(A)参照)。エッチング液としては、塩化第二銅、塩化第二鉄、過酸塩類、過酸化水素/硫酸、アルカリチャントなどを用いることができる。続いて、第二銅錯体と有機酸とを含有するエッチング液によって、粗化面58α、60αを形成する(図12(B)参照)。

【0073】

(10)次いで、上記(7)〜(12)の工程を、繰り返すことにより、層間樹脂絶縁層50の上層に層間樹脂絶縁層150及び導体回路158(バイアホール160を含む)を、更に、層間樹脂絶縁層250及び導体回路258(バイアホール260を含む)を形成する(図12(C)参照)。

【0074】

(11)次に、ジエチレングリコールジメチルエーテル(DMDG)に60重量%の濃度になるように溶解させた、クレゾールノボラック型エポキシ樹脂(日本化薬社製)のエポキシ基50%をアクリル化した感光性付与のオリゴマー(分子量4000)46.67重量部、メチルエチルケトンに溶解させた80重量%のビスフェノールA型エポキシ樹脂(油化シェル社製、商品名:エピコート1001)15重量部、イミダゾール硬化剤(四国化成社製、商品名:2E4MZ−CN)1.6重量部、感光性モノマーである多官能アクリルモノマー(共栄化学社製、商品名:R604)3重量部、同じく多価アクリルモノマー(共栄化学社製、商品名:DPE6A)1.5重量部、分散系消泡剤(サンノプコ社製、商品名:S−65)0.71重量部を容器にとり、攪拌、混合して混合組成物を調整し、この混合組成物に対して光重量開始剤としてベンゾフェノン(関東化学社製)2.0重量部、光増感剤としてのミヒラーケトン(関東化学社製)0.2重量部を加えて、粘度を25℃で2.0Pa・sに調整したソルダーレジスト組成物(有機樹脂絶縁材料)を得る。

なお、粘度測定は、B型粘度計(東京計器社製、DVL−B型)で60rpmの場合はローターNo.4、6rpmの場合はローターNo.3によった。なお、ソルダーレジストとして市販のソルダーレジストを用いることもできる。

【0075】

(12)次に、基板30に、上記ソルダーレジスト組成物を20μmの厚さで塗布し、70℃で20分間、70℃で30分間の条件で乾燥処理を行った後、ソルダーレジストレジスト開口部のパターンが描画された厚さ5mmのフォトマスクをソルダーレジスト層70に密着させて1000mJ/cm2の紫外線で露光し、DMTG溶液で現像処理し、200μmの直径の開口71を形成する(図13(A)参照)。

【0076】

(13)次に、ソルダーレジスト層(有機樹脂絶縁層)70を形成した基板を、塩化ニッケル(2.3×10-1mol/l)、次亞リン酸ナトリウム(2.8×10-1mol/l)、クエン酸ナトリウム(1.6×10-1mol/l)を含むpH=4.5の無電解ニッケルめっき液に20分間浸漬して、開口部71に厚さ5μmのニッケルめっき層72を形成する。さらに、その基板を、シアン化金カリウム(7.6×10-3mol/l)、塩化アンモニウム(1.9×10-1mol/l)、クエン酸ナトリウム(1.2×10-1mol/l)、次亜リン酸ナトリウム(1.7×10-1mol/l)を含む無電解めっき液に80℃の条件で7.5分間浸漬して、ニッケルめっき層72上に厚さ0.03μmの金めっき層74を形成することで、導体回路258に半田パッド75を形成する(図13(B)参照)。

【0077】

(14)この後、ソルダーレジスト層70の開口部71に、半田ペーストを印刷する。この半田ペーストには、Sn/Pb、Sn/Sb、Sn/Ag、Sn/Ag/Cuなどを用いることができる。また、低α線タイプの半田ペーストを用いてもよい。続いて、200℃でリフローすることにより、BGA76をICチップ20が内蔵されていない領域R2内にグリッド状(または千鳥状)になるように配設する(図14、図17(A)、(B)参照)。これにより、ICチップ20を内蔵し、BGA76を有する多層プリント配線板10を得ることができる(図14参照)。なお、ICチップ20は、基板30の中央部分ではなく、偏った位置に配設してもよい。図14では、BGAを外部接続端子として配設しているが、図15に示すように外部接続端子としてPGA96を取り付ける場合にも、ICチップ20が内蔵されていない領域R2内に配置することが望ましい。

【0078】

[第1実施形態の改変例]

第1実施形態の改変例に係る多層プリント配線板について説明する。上述した第1実施形態では、層間樹脂絶縁層にバイアホールを形成する際、レーザを用いて行った。これに対して、改変例では、露光することによってバイアホールを形成する。この改変例に係る多層プリント配線板の製造方法について、図18を参照して説明する。

【0079】

(4)第1実施形態と同様に、上記(1)〜(3)の工程を経た基板30に、厚さ50μmの熱硬化型エポキシ系樹脂51を塗布する(図18(A)参照)。

【0080】

(5)次に、バイアホール形成位置に対応する黒円の描かれたフォトマスクフィルム(図示せず)を層間樹脂絶縁層50に載置して、露光を行う。続いて、DMTG液でスプレー現像して、加熱処理を行うことによって直径85μmのバイアホール用開口48を設ける(図18(B)参照)。

【0081】

(6)過マンガン酸、または、クロム酸で層間樹脂絶縁層50の表面を粗化して、粗化面50αを形成する(図18(C)参照)。粗化面50αは、0.05〜5μmの範囲で形成されることが望ましい。以降の工程は、上述した第1実施形態の(7)〜(14)と同様の工程であるため説明を省略する。

【0082】

上述した実施形態では、層間樹脂絶縁層50、150、250に熱硬化型樹脂シートを用いた。この熱硬化型樹脂シート樹脂には、難溶性樹脂、可溶性粒子、硬化剤、その他の成分が含有されている。それぞれについて以下に説明する。

【0083】

第1実施形態の製造方法において使用する熱硬化型樹脂シートは、酸または酸化剤に可溶性の粒子(以下、可溶性粒子という)が酸または酸化剤に難溶性の樹脂(以下、難溶性樹脂という)中に分散したものである。

なお、第1実施形態で使用する「難溶性」「可溶性」という語は、同一の酸または酸化剤からなる溶液に同一時間浸漬した場合に、相対的に溶解速度の早いものを便宜上「可溶性」と呼び、相対的に溶解速度の遅いものを便宜上「難溶性」と呼ぶ。

【0084】

上記可溶性粒子としては、例えば、酸または酸化剤に可溶性の樹脂粒子(以下、可溶性樹脂粒子)、酸または酸化剤に可溶性の無機粒子(以下、可溶性無機粒子)、酸または酸化剤に可溶性の金属粒子(以下、可溶性金属粒子)等が挙げられる。これらの可溶性粒子は、単独で用いても良いし、2種以上併用してもよい。

【0085】

上記可溶性粒子の形状は特に限定されず、球状、破砕状等が挙げられる。また、上記可溶性粒子の形状は、一様な形状であることが望ましい。均一な粗さの凹凸を有する粗化面を形成することができるからである。

【0086】

上記可溶性粒子の平均粒径としては、0.1〜10μmが望ましい。この粒径の範囲であれば、2種類以上の異なる粒径のものを含有してもよい。すなわち、平均粒径が0.1〜0.5μmの可溶性粒子と平均粒径が1〜3μmの可溶性粒子とを含有する等である。これにより、より複雑な粗化面を形成することができ、導体回路との密着性にも優れる。なお、第1実施形態において、可溶性粒子の粒径とは、可溶性粒子の一番長い部分の長さである。

【0087】

上記可溶性樹脂粒子としては、熱硬化性樹脂、熱可塑性樹脂等からなるものが挙げられ、酸あるいは酸化剤からなる溶液に浸漬した場合に、上記難溶性樹脂よりも溶解速度が速いものであれば特に限定されない。

上記可溶性樹脂粒子の具体例としては、例えば、エポキシ樹脂、フェノール樹脂、ポリイミド樹脂、ポリフェニレン樹脂、ポリオレフィン樹脂、フッ素樹脂等からなるものが挙げられ、これらの樹脂の一種からなるものであってもよいし、2種以上の樹脂の混合物からなるものであってもよい。

【0088】

また、上記可溶性樹脂粒子としては、ゴムからなる樹脂粒子を用いることもできる。上記ゴムとしては、例えば、ポリブタジエンゴム、エポキシ変性、ウレタン変性、(メタ)アクリロニトリル変性等の各種変性ポリブタジエンゴム、カルボキシル基を含有した(メタ)アクリロニトリル・ブタジエンゴム等が挙げられる。これらのゴムを使用することにより、可溶性樹脂粒子が酸あるいは酸化剤に溶解しやすくなる。つまり、酸を用いて可溶性樹脂粒子を溶解する際には、強酸以外の酸でも溶解することができ、酸化剤を用いて可溶性樹脂粒子を溶解する際には、比較的酸化力の弱い過マンガン酸塩でも溶解することができる。また、クロム酸を用いた場合でも、低濃度で溶解することができる。そのため、酸や酸化剤が樹脂表面に残留することがなく、後述するように、粗化面形成後、塩化パラジウム等の触媒を付与する際に、触媒が付与されなたかったり、触媒が酸化されたりすることがない。

【0089】

上記可溶性無機粒子としては、例えば、アルミニウム化合物、カルシウム化合物、カリウム化合物、マグネシウム化合物およびケイ素化合物からなる群より選択される少なくとも一種からなる粒子等が挙げられる。

【0090】

上記アルミニウム化合物としては、例えば、アルミナ、水酸化アルミニウム等が挙げられ、上記カルシウム化合物としては、例えば、炭酸カルシウム、水酸化カルシウム等が挙げられ、上記カリウム化合物としては、炭酸カリウム等が挙げられ、上記マグネシウム化合物としては、マグネシア、ドロマイト、塩基性炭酸マグネシウム等が挙げられ、上記ケイ素化合物としては、シリカ、ゼオライト等が挙げられる。これらは単独で用いても良いし、2種以上併用してもよい。

【0091】

上記可溶性金属粒子としては、例えば、銅、ニッケル、鉄、亜鉛、鉛、金、銀、アルミニウム、マグネシウム、カルシウムおよびケイ素からなる群より選択される少なくとも一種からなる粒子等が挙げられる。また、これらの可溶性金属粒子は、絶縁性を確保するために、表層が樹脂等により被覆されていてもよい。

【0092】

上記可溶性粒子を、2種以上混合して用いる場合、混合する2種の可溶性粒子の組み合わせとしては、樹脂粒子と無機粒子との組み合わせが望ましい。両者とも導電性が低くいため樹脂シートの絶縁性を確保することができるとともに、難溶性樹脂との間で熱膨張の調整が図りやすく、樹脂シートからなる層間樹脂絶縁層にクラックが発生せず、層間樹脂絶縁層と導体回路との間で剥離が発生しないからである。

【0093】

上記難溶性樹脂としては、層間樹脂絶縁層に酸または酸化剤を用いて粗化面を形成する際に、粗化面の形状を保持できるものであれば特に限定されず、例えば、熱硬化性樹脂、熱可塑性樹脂、これらの複合体等が挙げられる。また、これらの樹脂に感光性を付与した感光性樹脂であってもよい。感光性樹脂を用いることにより、層間樹脂絶縁層に露光、現像処理を用いてバイアホール用開口を形成することできる。

これらのなかでは、熱硬化性樹脂を含有しているものが望ましい。それにより、めっき液あるいは種々の加熱処理によっても粗化面の形状を保持することができるからである。

【0094】

上記難溶性樹脂の具体例としては、例えば、エポキシ樹脂、フェノール樹脂、フェノキシ樹脂、ポリイミド樹脂、ポリフェニレン樹脂、ポリオレフィン樹脂、フッ素樹脂等が挙げられる。これらの樹脂は単独で用いてもよいし、2種以上を併用してもよい。

さらには、1分子中に、2個以上のエポキシ基を有するエポキシ樹脂がより望ましい。前述の粗化面を形成することができるばかりでなく、耐熱性等にも優れてるため、ヒートサイクル条件下においても、金属層に応力の集中が発生せず、金属層の剥離などが起きにくいからである。

【0095】

上記エポキシ樹脂としては、例えば、クレゾールノボラック型エポキシ樹脂、ビスフェノールA型エポキシ樹脂、ビスフェノールF型エポキシ樹脂、フェノールノボラック型エポキシ樹脂、アルキルフェノールノボラック型エポキシ樹脂、ビフェノールF型エポキシ樹脂、ナフタレン型エポキシ樹脂、ジシクロペンタジエン型エポキシ樹脂、フェノール類とフェノール性水酸基を有する芳香族アルデヒドとの縮合物のエポキシ化物、トリグリシジルイソシアヌレート、脂環式エポキシ樹脂等が挙げられる。これらは、単独で用いてもよく、2種以上を併用してもよい。それにより、耐熱性等に優れるものとなる。

【0096】

第1実施形態で用いる樹脂シートにおいて、上記可溶性粒子は、上記難溶性樹脂中にほぼ均一に分散されていることが望ましい。均一な粗さの凹凸を有する粗化面を形成することができ、樹脂シートにバイアホールやスルーホールを形成しても、その上に形成する導体回路の金属層の密着性を確保することができるからである。また、粗化面を形成する表層部だけに可溶性粒子を含有する樹脂シートを用いてもよい。それによって、樹脂シートの表層部以外は酸または酸化剤にさらされることがないため、層間樹脂絶縁層を介した導体回路間の絶縁性が確実に保たれる。

【0097】

上記樹脂シートにおいて、難溶性樹脂中に分散している可溶性粒子の配合量は、樹脂シートに対して、3〜40重量%が望ましい。可溶性粒子の配合量が3重量%未満では、所望の凹凸を有する粗化面を形成することができない場合があり、40重量%を超えると、酸または酸化剤を用いて可溶性粒子を溶解した際に、樹脂シートの深部まで溶解してしまい、樹脂シートからなる層間樹脂絶縁層を介した導体回路間の絶縁性を維持できず、短絡の原因となる場合がある。

【0098】

上記樹脂シートは、上記可溶性粒子、上記難溶性樹脂以外に、硬化剤、その他の成分等を含有していることが望ましい。

上記硬化剤としては、例えば、イミダゾール系硬化剤、アミン系硬化剤、グアニジン系硬化剤、これらの硬化剤のエポキシアダクトやこれらの硬化剤をマイクロカプセル化したもの、トリフェニルホスフィン、テトラフェニルホスフォニウム・テトラフェニルボレート等の有機ホスフィン系化合物等が挙げられる。

【0099】

上記硬化剤の含有量は、樹脂シートに対して0.05〜10重量%であることが望ましい。0.05重量%未満では、樹脂シートの硬化が不十分であるため、酸や酸化剤が樹脂シートに侵入する度合いが大きくなり、樹脂シートの絶縁性が損なわれることがある。一方、10重量%を超えると、過剰な硬化剤成分が樹脂の組成を変性させることがあり、信頼性の低下を招いたりしてしまうことがある。

【0100】

上記その他の成分としては、例えば、粗化面の形成に影響しない無機化合物あるいは樹脂等のフィラーが挙げられる。上記無機化合物としては、例えば、シリカ、アルミナ、ドロマイト等が挙げられ、上記樹脂としては、例えば、ポリイミド樹脂、ポリアクリル樹脂、ポリアミドイミド樹脂、ポリフェニレン樹脂、メラニン樹脂、オレフィン系樹脂等が挙げられる。これらのフィラーを含有させることによって、熱膨脹係数の整合や耐熱性、耐薬品性の向上などを図り多層プリント配線板の性能を向上させることができる。

【0101】

また、上記樹脂シートは、溶剤を含有していてもよい。上記溶剤としては、例えば、アセトン、メチルエチルケトン、シクロヘキサノン等のケトン類、酢酸エチル、酢酸ブチル、セロソルブアセテートやトルエン、キシレン等の芳香族炭化水素等が挙げられる。これらは単独で用いてもよいし、2種類以上併用してもよい。ただし、これらの層間樹脂絶縁層は、350℃以上の温度を加えると溶解、炭化をしてしまう。

【0102】

[第2実施形態]

引き続き、第2実施形態の多層プリント配線板の製造方法について、図19〜図21を参照して説明する。上述した第1実施形態では、ICチップ20に仲介層38を形成してからコア基板30に搭載した。これに対して、第2実施形態では、ICチップをコア基板に搭載してから仲介層を形成する。

【0103】

(1)先ず、ガラスクロス等の心材にエポキシ等の樹脂を含浸させたプリプレグを積層した絶縁樹脂基板(コア基板)30を出発材料として用意する(図19(A)参照)。次に、コア基板30の片面に、ザグリ加工でICチップ収容用の凹部32を形成する(図19(B)参照)。

【0104】

(2)その後、凹部32に、印刷機を用いて接着材料34を塗布する。このとき、塗布以外にも、ポッティングなどをしてもよい。次に、ICチップ20を接着材料34上に載置する(図19(C)参照)。

【0105】

(3)そして、ICチップ20の上面を押す、もしくは叩いて凹部32内に完全に収容させる(図20(A)参照)。これにより、コア基板30を平滑にすることができる。

【0106】

(4)その後、ICチップ20を収容させたコア基板30の全面に蒸着、スパッタリングなどの物理的な蒸着を行い、全面に導電性の金属膜33を形成させる(図20(B))。その金属としては、スズ、クロム、チタン、ニッケル、亜鉛、コバルト、金、銅などの金属を1層以上形成させるものがよい。厚みとしては、0.001〜2.0μmの間で形成させるのがよい。特に、0.01〜1.0μmが望ましい。

【0107】

金属膜33上に、無電解めっきにより、めっき膜36を形成させてもよい(図20(C))。形成されるメッキの種類としては銅、ニッケル、金、銀、亜鉛、鉄などがある。電気特性、経済性、また、後程で形成されるビルドアップである導体層は主に銅であることから、銅を用いるとよい。その厚みは1〜20μmの範囲で行うのがよい。

【0108】

(5)その後、レジストを塗布し、露光、現像してICチップ20のパッド22の上部に開口を設けるようにメッキレジスト35を設け、無電解メッキを施して無電解めっき膜37を設ける(図21(A))。メッキレジスト35を除去した後、メッキレジスト35下の無電解めっき膜36、金属膜33を除去することで、ICチップのパッド22上に仲介層38を形成する(図21(B))。ここでは、メッキレジストにより仲介層を形成したが、無電解めっき膜36の上に電解めっき膜を均一に形成した後、エッチングレジストを形成して、露光、現像して仲介層38以外の部分の金属を露出させてエッチングを行い、ICチップ20のパッド22上に仲介層38を形成させることも可能である。この場合、電解めっき膜の厚みは1〜20μmの範囲がよい。それより厚くなると、エッチングの際にアンダーカットが起こってしまい、形成される仲介層とバイアホールと界面に隙間が発生することがあるからである。

【0109】

(6)次に、基板30にエッチング液をスプレイで吹きつけ、仲介層38の表面をエッチングすることにより粗化面38αを形成する(図21(C)参照)。以降の工程は第1実施形態と同様であるため説明を省略する。

【0110】

[比較例]

比較例に係る多層プリント配線板について説明する。上述した第1実施形態では、ICチップの直上外の領域R2内にBGA76を配置させた。これに対して比較例は、図17(C)に示すようにソルダーレジスト層上に均一にBGA76が配置されている。つまり、領域R1と、領域R2とを区別せずに、ソルダーレジスト層全面にBGA76をグリッド状(フルグリッド状)に形成されている。

【0111】

第1実施形態に係る多層プリント配線板と、比較例の多層プリント配線板とのそれぞれを外部基板と接続させた後、電気接続させて以下の項目の評価を行った。

▲1▼外部基板との実装後のクラックや剥離の有無

▲2▼BGAの不具合の有無

▲3▼信頼性試験後の外部基板との実装後のクラックや剥離の有無

▲4▼信頼性試験後のBGAの不具合の有無

▲5▼接触抵抗の測定

第1実施形態に係る多層プリント配線板では、好適な結果が得られたが、比較例では、BGAの周辺におけるクラックや剥離などが発見された。また、接触抵抗の上昇も確認された。図15に示すように、BGAの代わりにPGAを用いた場合にも同様の結果が得られた。

【0112】

【発明の効果】

以上記述したように発明では、多層プリント配線板の半導体素子が内蔵された基板上の領域と、半導体素子が内蔵されていない基板上の領域とを区別する。そして、半導体素子が内蔵されていない基板上の領域に外部接続端子(BGA/PGA)を配設する。つまり、半導体素子の内蔵されていない基板上の領域に外部接続端子(BGA/PGA)を配設することによって、熱膨張による影響を小さくできるため、外部接続端子(BGA/PGA)の周囲などに発生する剥離、クラックを防止できる。したがって、外部接続端子(BGA/PGA)の脱落や位置ずれを防止して、電気的接続性や信頼性を向上させることが可能となる。

【図面の簡単な説明】

【図1】(A)、(B)、(C)は、本発明の第1実施形態に係るICチップの第1の製造方法の工程図である。

【図2】(A)、(B)、(C)は、第1実施形態に係るICチップの第1の製造方法の工程図である。

【図3】(A)、(B)は、第1実施形態に係るICチップの第1の製造方法の工程図である。

【図4】(A)は、第1実施形態に係るシリコンウエハーの平面図であり、(B)は、個片化されたICチップの平面図である。

【図5】(A)、(B)、(C)は、第1実施形態に係るICチップの第2の製造方法の工程図である。

【図6】第1実施形態に係るICチップの第2の製造方法の工程図である。

【図7】(A)、(B)、(C)は、第1実施形態に係るICチップの第3の製造方法の工程図である。

【図8】(A)、(B)は、第1実施形態に係るICチップの第3の製造方法の工程図である。

【図9】(A)、(B)、(C)、(D)は、本発明の第1実施形態に係る多層プリント配線板の製造工程図である。

【図10】(A)、(B)、(C)は、本発明の第1実施形態に係る多層プリント配線板の製造工程図である。

【図11】(A)、(B)、(C)は、本発明の第1実施形態に係る多層プリント配線板の製造工程図である。

【図12】(A)、(B)、(C)は、本発明の第1実施形態に係る多層プリント配線板の製造工程図である。

【図13】(A)、(B)は、本発明の第1実施形態に係る多層プリント配線板の製造工程図である。

【図14】第1実施形態に係る多層プリント配線板の断面図である。

【図15】第1実施形態に係る多層プリント配線板の断面図である。

【図16】図14のE−E断面図である。

【図17】(A)は、本発明の第1実施形態に係る多層プリント配線板の平面図であり、(B)は、バンプが千鳥状に配置された多層プリント配線板の平面図であり、(C)は、比較例に係る多層プリント配線板の平面図である。

【図18】(A)、(B)、(C)は、第1実施形態の改変例に係る多層プリント配線板の製造工程図である。

【図19】(A)、(B)、(C)は、本発明の第2実施形態に係る多層プリント配線板の製造工程図である。

【図20】(A)、(B)、(C)は、第2実施形態に係る多層プリント配線板の製造工程図である。

【図21】(A)、(B)、(C)は、第2実施形態に係る多層プリント配線板の製造工程図である。

【符号の説明】

20 ICチップ

22 パッド

24 パッシベーション膜

30 コア基板

32 凹部

33 金属膜

34 接着材料

36 めっき膜

37 無電解めっき膜

37 仲介層

38α 粗化面

50 層間樹脂絶縁層

50α 粗化面

52 金属層

54 めっきレジスト

56 電解めっき膜

58 導体回路

58α 粗化面

60 バイアホール

60α 粗化面

70 ソルダーレジスト層

71 開口部

72 ニッケルめっき

74 金めっき

75 半田パッド

76 半田バンプ

150 層間樹脂絶縁層

158 導体回路

160 バイアホール

250 層間樹脂絶縁層

258 導体回路

260 バイアホール

Claims (4)

- 半導体素子を内蔵した基板上に層間絶縁層と導体層とが繰り返し形成され、前記層間絶縁層には、バイアホールが形成され、前記バイアホールを介して電気的接続される多層プリント配線板において、

前記基板内の半導体素子の直上以外の領域において、前記バイアホールに接続された複数の外部接続端子が、グリッド状または千鳥状に形成され、

前記バイアホールは銅で構成され、

前記半導体素子のパッド部分には、銅で構成された層を含む複数の層を有し、最下層の前記層間絶縁層に形成された前記バイアホールと接続するための、前記半導体素子のパッドの径よりも径の大きな仲介層が形成され、

前記銅で構成された層と前記バイアホールとが接続されていることを特徴とする多層プリント配線板。 - 前記銅で構成された層は、めっきにより形成されることを特徴とする請求項1に記載の多層プリント配線板。

- 前記銅で構成された層の厚みは、1〜20μmであることを特徴とする請求項2に記載の多層プリント配線板。

- 半導体素子を内蔵する前記基板の凹部または通孔と、前記半導体素子との間に、樹脂充填材料を充填したことを特徴とする請求項1〜3のいずれかに記載の多層プリント配線板。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001123875A JP4785268B2 (ja) | 2000-12-15 | 2001-04-23 | 半導体素子を内蔵した多層プリント配線板 |

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000382814 | 2000-12-15 | ||

| JP2000-382814 | 2000-12-15 | ||

| JP2000382814 | 2000-12-15 | ||

| JP2001123875A JP4785268B2 (ja) | 2000-12-15 | 2001-04-23 | 半導体素子を内蔵した多層プリント配線板 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2002246761A JP2002246761A (ja) | 2002-08-30 |

| JP4785268B2 true JP4785268B2 (ja) | 2011-10-05 |

Family

ID=26605976

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001123875A Expired - Lifetime JP4785268B2 (ja) | 2000-12-15 | 2001-04-23 | 半導体素子を内蔵した多層プリント配線板 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4785268B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004214586A (ja) * | 2002-11-14 | 2004-07-29 | Kyocera Corp | 多層配線基板 |

| WO2011089936A1 (ja) | 2010-01-22 | 2011-07-28 | 日本電気株式会社 | 機能素子内蔵基板及び配線基板 |

| JP5998792B2 (ja) | 2012-09-21 | 2016-09-28 | Tdk株式会社 | 半導体ic内蔵基板及びその製造方法 |

| DE102020207886A1 (de) | 2020-06-25 | 2021-12-30 | Robert Bosch Gesellschaft mit beschränkter Haftung | Leistungsendstufe für eine Vorrichtung zur Energieversorgung einer elektrischen Last |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0338084A (ja) * | 1989-07-04 | 1991-02-19 | Sharp Corp | 回路基板の接続方法 |

| JP2785444B2 (ja) * | 1990-05-16 | 1998-08-13 | 松下電器産業株式会社 | 半導体装置およびその製造方法ならびに半導体装置を用いた電子回路装置 |

| US5161093A (en) * | 1990-07-02 | 1992-11-03 | General Electric Company | Multiple lamination high density interconnect process and structure employing a variable crosslinking adhesive |

| JPH0878572A (ja) * | 1994-08-31 | 1996-03-22 | Hitachi Ltd | 半導体パッケージおよび、それの製造方法および、それを実装した回路ボードと電子機器 |

| JP2842378B2 (ja) * | 1996-05-31 | 1999-01-06 | 日本電気株式会社 | 電子回路基板の高密度実装構造 |

| JPH11233678A (ja) * | 1998-02-16 | 1999-08-27 | Sumitomo Metal Electronics Devices Inc | Icパッケージの製造方法 |

| JP2000311965A (ja) * | 1999-04-27 | 2000-11-07 | Fujitsu Ltd | 半導体装置及びその製造方法 |

-

2001

- 2001-04-23 JP JP2001123875A patent/JP4785268B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2002246761A (ja) | 2002-08-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4854845B2 (ja) | 多層プリント配線板 | |

| JP4270769B2 (ja) | 多層プリント配線板の製造方法 | |

| WO2001063991A1 (fr) | Carte a circuits imprimes multicouche et procede de production d'une carte a circuits imprimes multicouche | |

| JP4108285B2 (ja) | 多層プリント配線板の製造方法 | |

| JP4869488B2 (ja) | 多層プリント配線板の製造方法 | |

| JP4248157B2 (ja) | 多層プリント配線板 | |

| JP4137389B2 (ja) | 半導体素子を内蔵する多層プリント配線板の製造方法 | |

| JP4771608B2 (ja) | プリント配線板 | |

| JP4931283B2 (ja) | プリント配線板及びプリント配線板の製造方法 | |

| JP4601158B2 (ja) | 多層プリント配線板およびその製造方法 | |

| JP4243922B2 (ja) | 多層プリント配線板 | |

| JP4957638B2 (ja) | 多層プリント配線板及び多層プリント配線板の製造方法 | |

| JP4475836B2 (ja) | 半導体素子の製造方法 | |

| JP4854846B2 (ja) | 多層プリント配線板の製造方法 | |

| JP4934900B2 (ja) | 多層プリント配線板の製造方法 | |

| JP4618919B2 (ja) | 半導体素子を内蔵する多層プリント配線板の製造方法 | |

| JP4854847B2 (ja) | 多層プリント配線板および多層プリント配線板の製造方法 | |

| JP4108270B2 (ja) | 多層プリント配線板およびその製造方法 | |

| JP4785268B2 (ja) | 半導体素子を内蔵した多層プリント配線板 | |

| JP4722961B2 (ja) | 半導体素子を内蔵する多層プリント配線板の製造方法 | |

| JP4049554B2 (ja) | 多層プリント配線板および多層プリント配線板の製造方法 | |

| JP4033639B2 (ja) | 多層プリント配線板 | |

| JP4549366B2 (ja) | 多層プリント配線板 | |

| JP4458716B2 (ja) | 多層プリント配線板および多層プリント配線板の製造方法 | |

| JP4749563B2 (ja) | 多層プリント配線板および多層プリント配線板の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20050901 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080311 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100831 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100907 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101105 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110222 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110523 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20110530 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110621 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110621 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110712 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110712 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4785268 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140722 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |