JP4734786B2 - Gallium nitride compound semiconductor substrate and manufacturing method thereof - Google Patents

Gallium nitride compound semiconductor substrate and manufacturing method thereof Download PDFInfo

- Publication number

- JP4734786B2 JP4734786B2 JP2001203956A JP2001203956A JP4734786B2 JP 4734786 B2 JP4734786 B2 JP 4734786B2 JP 2001203956 A JP2001203956 A JP 2001203956A JP 2001203956 A JP2001203956 A JP 2001203956A JP 4734786 B2 JP4734786 B2 JP 4734786B2

- Authority

- JP

- Japan

- Prior art keywords

- gallium nitride

- compound semiconductor

- nitride compound

- layer

- semiconductor layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Semiconductor Lasers (AREA)

Description

【0001】

【発明の属する技術分野】

本発明は、窒化ガリウム系化合物半導体基板、及びその製造方法であって、特に貫通転位密度を低減したn型導電性を有する窒化ガリウム系化合物半導体基板に関するものである。

【0002】

【従来の技術】

窒化ガリウム系化合物半導体は、発光波長が400nm付近の短波長領域であるため、紫外から緑色までの発光光源とすることができ、半導体レーザダイオードとして用いた場合、従来の赤色レーザダイオードに比べて数倍の大容量メディアの再生装置、又は記憶装置として使用可能となる。さらに電界効果トランジスタ(FET)のような電子デバイスへの応用も期待されている。

【0003】

このような窒化ガリウム系化合物半導体デバイスを作成するには、バルク単結晶の窒化ガリウムや窒化ガリウム系化合物半導体のホモエピタキシャル成長が可能な基板が望まれるが、このような基板等の作成は窒素の蒸気圧が高いために困難である。そのため、サファイアや炭化珪素、スピネル等の基板上に窒化ガリウム系化合物半導体をヘテロエピタキシャル成長させる。この窒化物半導体基板を基板として窒化ガリウム系化合物半導体を成長させている。

【0004】

基板と、基板上に積層される窒化ガリウム系化合物半導体との格子定数差が大きければ、基板上に積層される窒化ガリウム系化合物半導体層に貫通転位が発生する。この貫通転位が多ければリーク電流が増大し、半導体レーザダイオード等の発光素子において大幅に寿命特性を低下させることになる。サファイア等の基板上に窒化ガリウム系化合物半導体を成長させる場合、バッファー層を介することにより、貫通転位を低減させることができる。例えば、特開平7−202265号公報、特開平7−165498号公報にはZnOから成るバッファー層が報告されている。その他に、AlNやGaNバッファー層もあるものの、貫通転位密度は、108個/cm2〜1010個/cm2程度である。このようなバッファー層を介して基板上に成長させた窒化ガリウム系化合物半導体を素子とする半導体レーザダイオードや高出力発光ダイオードでは長時間の連続発振は期待できない。

【0005】

そのため、より貫通転位密度を低減できる効果を有するELO(Epitaxial Lateral Overgrowth)法が報告されている。このELO法とは、化合物半導体の横方向成長を利用した転位の低減方法である。例えば、下地層である窒化ガリウム系化合物半導体上に、開口部(窓部)を有する保護膜を例えばストライプ形状や島状に形成する。次に、この保護膜の開口部より露出した下地層の窒化ガリウム系化合物半導体を核として窒化ガリウム系化合物半導体を成長させる。下地層を核として成長させる窒化ガリウム系化合物半導体は開口部から縦方向に成長後、横方向にも成長する。この横方向成長とは、核からの連続成長であり保護膜上において横方向に成長するものである。これより貫通転位は窒化ガリウム系化合物半導体と同様に縦方向だけでなく横方向にも成長する。そのため、この横方向成長した貫通転位は、保護膜上で隣り合う核から成長した窒化ガリウム系化合物半導体同士が接合する接合部に集中する。そのため、保護膜の開口部、及び保護膜上の接合部には貫通転位は集中するものの、これらの領域を除いた横方向成長領域の表面には、低転位領域を形成することができる。その他、貫通転位密度を低減する方法として、垂直方向の成長速度が速く表面の荒れた第1の成長層を成長させ、その後、垂直方向の成長速度が第1の成長層よりも遅い第2の成長層を成長させて第1の成長層の窪みを埋める方法が特開2001−168045号公報に記載されている。また、特開平11−1399号公報には、シリコン不純物を10 18 〜10 20 cm -3 の範囲で調節して、n型窒化ガリウム半導体基板を得る方法が記載されている。このようなn型窒化ガリウム半導体基板は、窒化ガリウム成長工程と研磨工程とを繰り返して形成される。

【0006】

【発明が解決しようとする課題】

しかしながら、前記に示すELO法では保護膜のパターン形成等の工程が多く、効率よく量産するのは困難である。さらに、ELO法では保護膜に開口部を設け、その開口部から露出した窒化ガリウム系化合物半導体を核として窒化ガリウム系化合物半導体を成長させるため、横方向成長領域には、低転位領域が得られるものの、開口部である窓部上部、及び保護膜上の窒化ガリウム系化合物半導体同士の接合部には転位が多く集中する。そのため、表面に低転位領域が均一となる基板を提供することは困難であり、低転位領域内に選択的にリッジストライプを形成しなければならない。よって、反りを有するウェハー上ではリッジストライプを形成するフォトリソ工程で歩留まりを低下させてしまう。その他に、ELO法で得られる窒化物半導体基板は絶縁性の異種基板を有するものが主流であり、例えばサファイア基板上に窒化物半導体を形成したものである。そのため、放熱性が悪く高出力での長時間の連続発振は困難である。また、サファイア基板は絶縁性であるため、n型電極、p型電極を表面上に形成しなければならず、素子を成長させた後に段差を形成する工程が必要となる。これは対極面に電極を形成した素子と比較してチップ面積の節減にも不利である。また、サファイア基板にはヘキカイ性がないため、チップの分離にはダイシング工程が必要となりコスト高をまねく。

【0007】

本発明の課題は、窒化ガリウム系化合物半導体基板表面に低転位領域を均等かつ広範囲で得ることである。また、異種基板を除去したn型低抵抗単体基板とすることで、量産効率を向上させた窒化ガリウム系化合物半導体基板を提供することである。

【0008】

【課題を解決するための手段】

本発明の窒化ガリウム系化合物半導体基板は、Siドーピング濃度が1×1019/cm3以上である第1の窒化ガリウム系化合物半導体層と、該第1の窒化ガリウム系化合物半導体層上に積層された、該第1の窒化ガリウム系化合物半導体層よりもSi濃度が小さく、ノンドープ、又はSiドーピング濃度が1×1019/cm3以下である第2の窒化ガリウム系化合物半導体層と、を備え、前記第1の窒化ガリウム系化合物半導体層は、窒化ガリウム系化合物半導体の島として成長されたものであって、前記第2の窒化ガリウム系化合物半導体層は、前記窒化ガリウム系化合物半導体の島が成長し隣接する島同士が合体して形成されたものであり、貫通転位密度が1×10 8 /cm 2 以下であることを特徴とする。

【0009】

本発明における窒化ガリウム系化合物半導体基板の製造方法は、基板上に気相成長法により窒化ガリウム系化合物半導体層を成長させることにより形成される窒化ガリウム系化合物半導体基板の製造方法において、基板上にSiドーピング濃度が1×1019/cm3以上である第1の窒化ガリウム系化合物半導体層を形成する第1の工程と、第1の工程後、該第1の窒化ガリウム系化合物半導体層上に、該第1の窒化ガリウム系化合物半導体層よりもSi濃度が小さく、ノンドープ、又はSiドーピング濃度が1×1019/cm3以下である第2の窒化ガリウム系化合物半導体層を形成する第2の工程とを備え、前記第1の工程において、前記第1の窒化ガリウム系化合物半導体層は、窒化ガリウム系化合物半導体の島であって、前記第2の工程において、前記第2の工程において、前記第2の窒化ガリウム系化合物半導体層は、前記窒化ガリウム系化合物半導体の島が成長し隣接する島同士が合体して形成されることを特徴とする。

【0010】

このようにSiドーピング濃度が1×1019/cm3以上であるSiリッチ層と、このSiリッチ層上にSiドーピング濃度がノンドープ、又は1×1019/cm3以下であるSiプアー層を成長させる構成とすれば、転位の低減ができる。ここで、Siプアー層とはSiのノンドープも含むものとする。以下に転位の低減ができる理由を示す。Siリッチ層では、Siがドナーとしてだけではなく、コンタミナントとして成長層に作用する。そのためSi、又はその化合物の不着密度の高い部位の成長が遅れることになる。つまり、基板上に成長させる窒化ガリウム系化合物半導体は成長速度差を有する面内分布となる。その結果、表面全体において成長速度の速い部分では選択的に核が生成され、窒化ガリウム系化合物半導体の表面に窒化ガリウム系化合物半導体の島の成長が起こる。次に成長させるSiプアー層では、前記窒化ガリウム系化合物半導体の島同士での合体が促進される。これは成長速度が速い結晶粒が隣接する結晶粒を覆うように成長するためである。ここで、前記窒化ガリウム系化合物半導体の島は基板と窒化ガリウム系化合物半導体との成長界面から伸びた貫通転位を有するものである。この貫通転位は島が成長することにより、縦方向に伸びるだけでなく、島の表面が斜面形状であるため、成長面である斜面に対して垂直に伸びることとなる。そのため、島が成長し、隣接する島同士で合体する過程で貫通転位は屈曲し貫通転位同士がループを形成することとなる。そのため、第1の窒化ガリウム系化合物半導体層での縦方向以外に伸びた貫通転位は第2の窒化ガリウム系化合物半導体層内において、ループを形成し、低減させることができる。さらに、第1の窒化ガリウム系化合物半導体層はSiドーピング濃度を5×1019/cm3以上とすれば島同士の間隔をより大きく形成することができるため第2の窒化ガリウム系化合物半導体層を成長させた時に転位をより低減させることができる。より好ましくは第1の窒化ガリウム系化合物半導体層のSiドーピング濃度を1×1020/cm3以上とする。また、第2の窒化ガリウム系化合物半導体層はSiドーピング濃度を1×1018/cm3以下とすれば、移動度を向上することができ、さらに好ましくはSiドーピング濃度を1×1017/cm3以下とする。具体的には、前記窒化ガリウム系化合物半導体基板にバッファー層を介し、第1の窒化ガリウム系化合物半導体層を成長させ、その上に成長させる第2の窒化ガリウム系化合物半導体層で貫通転位を低減させる。バッファー層を有するのみでは、貫通転位は単位面積あたり1×108個/cm2〜1×1010個/cm2程度であるが、上記構成により前記第2の窒化ガリウム系化合物半導体層の表面での貫通転位密度を均一に低減させることができ、1×108個/cm2以下、さらに好ましくは1×106個/cm2以下とすることができる。

【0011】

さらに、第2の窒化ガリウム系化合物半導体層上に、Siドーピング濃度が1×1019/cm3以上である第3の窒化ガリウム系化合物半導体層と、該第3の窒化ガリウム系化合物半導体層上に積層され、該第3の窒化ガリウム系化合物半導体層よりもSi濃度が小さく、ノンドープ、又はSiドーピング濃度が1×1019/cm3以下である第4の窒化ガリウム系化合物半導体層と、を備えることを特徴とする。

【0012】

このように、Siリッチ層とSiプアー層とを成長させる構成を2回以上繰り返せば、さらに貫通転位同士がループを形成することにより、転位を低減させることができる。また、ハロゲン輸送法による気相成長法により厚膜成長をした場合には、サファイア等の異種基板を研削やレーザ照射により除去した窒化ガリウム系化合物半導体層のみから成る単体基板を形成することができる。そのため、サファイア基板のような絶縁体上に成長させた窒化物半導体基板であっても基板除去すること、及びSiリッチ層は高濃度でSiをドープすることで低抵抗のn型基板とすることができるため、電極を対極構造とすることが可能となる。ここで、異種基板の除去工程は窒化物半導体素子の成長前であっても、窒化物半導体素子の成長後であってもよい。

【0013】

また、前記窒化ガリウム系化合物半導体基板における第1、及び/又は第2の窒化ガリウム系化合物半導体層は、一般式InxAlyGa1−x−yN(0≦X<1、0≦Y<1、0≦X+Y<1)で示すことができる。さらに、GaNであれば2段階成長後の表面においてピットを少なくできる効果を有する。

【0014】

また、Siドーピングの原料にはシラン系化合物を用いる。このシラン系化合物はSiH4、Si2H6、SiHCl3、SiH2Cl2、SiH3Cl、SiCl4から成る群から選ばれる少なくとも1つである。これらの原料を用いれば、Siまたはそれらの化合物がコンタミナントだけではなく、効率よくドーパントにもなるため好ましい。

【0015】

前記第1の窒化ガリウム系化合物半導体は例えばサファイアのような異種基板上に直接成長させるのであれば、格子定数や熱膨張係数の違いから転位密度は多くなる。そのため、下地層であるバッファー層を介することにより基板上に直接に窒化ガリウム系化合物半導体層を形成するよりも結晶性をより向上させることができる。具体的には、InxAlyGa1−x−yN(0≦X<1、0≦Y<1、0≦X+Y<1)で示すことができ、700℃以下の低温成長で形成する。この下地層のみを介して成長させた窒化ガリウム系化合物半導体は単位面積あたりの貫通転位が108〜1010個/cm2となる。そのため、下地層の上にSiリッチ層とSiプアー層とを成長させることにより、より結晶性の良好な窒化物半導体基板を形成することができる。

【0016】

さらに、第1の窒化ガリウム系化合物半導体層と前記第2の窒化ガリウム系化合物半導体層の成長速度は略同じ速度とすることができる。第1の工程において、第1の窒化ガリウム系化合物半導体層の島を成長させ、第2の工程において、第2の窒化ガリウム系化合物半導体層の形成によって島同士の合体を促進させることもできる。また、前記窒化ガリウム系化合物半導体基板の気相成長法としてはハロゲン輸送法による気相成長法、有機金属気相成長法、分子線エピタキシー法等がある。ハロゲン輸送法による気相成長法は成長速度が速いため、厚膜成長させることができ好ましい。また、薄膜で低欠陥化を実現するには横方向成長を制御しやすい有機金属気相成長法、分子線エピタキシー法などの他の気相成長法を用いても良い。

【0017】

また、窒化ガリウム系化合物半導体基 板の製造方法において、基板には、サファイア、炭化珪素、スピネル、又はシリコン等が挙げられる。これらは、窒化ガリウム系化合物半導体をエピタキシャル成長させることができ、また成長温度に対して耐熱性を有するものである。さらに、窒化ガリウム系化合物半導体層を積層後、研削や電磁波照射等による基板の剥離除去を可能とし、これにより窒化ガリウム系化合物半導体からなる単体基板を形成することができる。本発明においては、第1の窒化ガリウム系化合物半導体層をSiリッチ層とするため、基板除去面をn型窒化物半導体層とすることができる。そのため、貫通転位を低減した結晶性のよい窒化物単体基板において、電極を対極形成した窒化ガリウム系化合物半導体レーザ、または発光ダイオードを提供することができる。

【0018】

【発明の実施の形態】

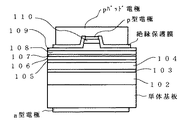

本発明の実施形態に係る窒化ガリウム系化合物半導体基板は、図1に示すように、Siドーピング濃度が1×1019/cm3以上である第1の窒化ガリウム系化合物半導体層3と、該第1の窒化ガリウム系化合物半導体層上に積層されたノンドープ、又はSiドーピング濃度が1×1019/cm3以下である第2の窒化ガリウム系化合物半導体層4と、を備える窒化ガリウム系化合物半導体基板である。

【0019】

前記Si原料にはシラン系化合物を用い、これらのシラン系化合物はSiH4、Si2H6、SiHCl3、SiH2Cl2、SiH3Cl、SiCl4から成る群から選ばれる少なくとも1つである。

【0020】

前記第1の窒化ガリウム系化合物半導体、及び第2の窒化ガリウム系化合物半導体は一般式をInxAlyGa1−x−yN(0≦X<1、0≦Y<1、0≦X+Y<1)とする。

【0021】

効果1

本実施形態における発明は、Siドープを窒化ガリウム系化合物半導体の成長と同時に行うものであり、2段階成長することで表面を平坦化し広範囲に低欠陥領域を有する窒化ガリウム系化合物半導体基板を作製することができる。このような平坦化ができるのは、結晶の自然な横方向成長する作用によるものである。また、本実施形態に示す窒化ガリウム系化合物半導体基板において、転位の低減方法としては、ファセットを埋め込まずに転位を低減させるのではなく、ファセットを埋め込みながら成長させ、転位を低減させるものである。以上より、表面研磨等による平坦化をする必要もなく、効率よく窒化ガリウム系化合物半導体基板を形成することができる。

【0022】

効果2

本発明は、基板を除去することで、低抵抗のn型単体基板を形成することができる。これは、転位の低減過程において、窒化ガリウム系化合物半導体層内に連続的にSiをドーピングするため、低抵抗のn型半導体層を形成することができるためである。このため、対極に電極を形成した構造とすることができ、チップ面積の節減に有利である。また、サファイア基板等異種基板がないため、チップの分離にダイシング工程が必要でなくなりコストの低減にもつながる。また、窒化ガリウム系化合物半導体から成る単体基板は劈開性を有し、半導体レーザを形成する場合には、劈開面を共振器ミラーとすることができ好ましい。また、基板を除去することにより、放熱性も向上するため長寿命化が期待できる。

【0023】

以下に、本発明の一実施形態における窒化ガリウム系化合物半導体基板の製造工程を示すが、これに限定されるものでない。

【0024】

本発明において、基板とは窒化物半導体層をエピタキシャル成長させることができる単結晶基板であればよく、基板の大きさや厚さ等は特に限定されない。この基板の具体例としては、C面、R面、及びA面のいずれかを主面とし、好ましくはC軸配向の窒化物半導体層を成長させるサファイア、スピネル、炭化珪素(6H、4H、3C)、シリコン、ZnS、ZnO、SiO2、GaAs、GaP、ダイヤモンド、NdGaO3、その他に窒化物半導体等が挙げられる。窒化ガリウム系化合物半導体層を積層後、サファイア等の基板を除去してもよい。これらの基板は表面が平坦なものを使用するが、窒化ガリウム系化合物半導体層をエピタキシャル成長することができれば、特に限定しない。例えば基板の裏面にエッチング加工等をすることにより細かい荒れを形成する。この荒れにより基板除去を簡単にすることができる。また、反りを緩和するために基板に凹凸、斜面、階段形状、その他にはエアブリッジ構造を有するものであってもよい。

【0025】

下地層2

前記基板上に800℃以下の低温でバッファー層としてInxAlyGa1−x−yN(0≦X<1、0≦Y<1、0≦X+Y<1)層を介して第1の窒化ガリウム系化合物半導体を成長させる。これは、基板と窒化ガリウム系化合物半導体との格子定数不整合を緩和することで欠陥や割れを抑制するためである。ここで、低温とは700℃以下、好ましくは450℃〜650℃の温度範囲である。この範囲内の温度でバッファー層を成長すれば、微細な核を均一性よく形成することができ好ましい。800℃以上でバッファー層を成長させれば、均一な核生成が阻害され、その後、結晶が多結晶化するため結晶性を低下させてしまう。膜厚は10オングストローム以上0.5μm以下で成長させる。さらに、下地層はバッファー層のみならず、2層構造としてもよい。これは、バッファー層(第1の下地層)上に第2の下地層を950℃以上の高温で成長させることにより、表面が鏡面であり平坦化した下地層とするためである。これより、後工程で成長させる窒化ガリウム系化合物半導体におけるピットの発生が抑制できる。また、この下地層は基板によっては省略することもできる。

【0026】

窒化ガリウム系化合物半導体

次に、前記基板1上に下地層2を形成後、第1の窒化ガリウム系化合物半導体及び第2の窒化ガリウム系化合物半導体を成長させる。この窒化ガリウム系化合物半導体は一般式InxAlyGa1−x−yN(0≦X<1、0≦Y<1、0≦X+Y<1)で表すことができる。但し、これらは互いに異なる組成であってもよい。また、Siの他には、ドーパントとしてOまたはGeやSn及びS等も用いることができ、これらにp型不純物をドープさせた窒化ガリウム系化合物半導体としてもよい。p型不純物はMg、Be、Cr、Mn、Ca、Zn等が挙げられる。

【0027】

また、第1の窒化ガリウム系化合物半導体層の膜厚は5μm以上とする。好ましくは15μm以上とする。これは、第1の窒化ガリウム系化合物半導体層の膜厚が5μm以下であれば、貫通転位を広範囲に屈曲させることができないからである。この膜厚で第1の窒化ガリウム系化合物半導体層を成長させることにより、第1の窒化ガリウム系化合物半導体層を成長後に貫通転位の伸びる方向を屈曲させることができる。次に前記第1の窒化ガリウム系化合物半導体層上に成長させる第2の窒化ガリウム系化合物半導体層を膜厚5μm以上、好ましくは15μm以上成長させれば、第2の窒化ガリウム系化合物半導体層の成長時に貫通転位どうしでループを形成させることで貫通転位を低減させることができる。

【0028】

窒化ガリウム系化合物半導体基板の製造方法として、基板上に下地層を介してハロゲン輸送法による気相エピタキシャル成長(HVPE)法により第1の窒化ガリウム系化合物半導体と、第2の窒化ガリウム系化合物半導体とを成長させる方法を以下に示す。ハライド気相エピタキシャル成長法は、短時間で厚膜を成長させることができるため、窒化物半導体の厚膜成長や、異種基板を剥離した窒化物半導体の単体基板の形成に有効である。

以下に本発明で用いた成長手法、成長工程、及び成長条件を示す。

【0029】

本発明における、1気相成長手段としてIII族元素のハロゲン化物とV族元素を含む化合物(本発明では窒素を含む化合物)とを反応させ、基板上に気相成長を行うハロゲン輸送法による気相成長(halogen-transport vapor phase epitaxy:HVPE)法があげられる。

【0030】

ハロゲンガスとしてはHCl等があり、キャリアガスと共にハロゲンガス管より導入される。このハロゲンガスとGa等の金属が反応することにより3族元素のハロゲン化物を生成させ、さらに、N源供給管より流入したアンモニアガスとが反応することにより窒化ガリウム系化合物半導体を基板上に成長させる。HVPE法において、還元ガス(例えば水素)を含む雰囲気では、反応管全体が抵抗加熱で熱せられているためにドーパントガスであるシラン系ガスは分解して、基板領域に到達する前に分解し、実効的なSiのドーピングは困難である。そのため、ドーパントガスとHClとを同時に導入することにより、シラン系ガスの分解を抑制して効率よくドープが可能である。

【0031】

第1の窒化ガリウム系化合物半導体の成長条件としては、成長速度が5μm/hour以上であればよい。また、第1の窒化ガリウム系化合物半導体、及び第2の窒化ガリウム系化合物半導体は成長速度を同じ速度とすることができる。そのため、成長速度が異なることにより生ずる結晶性の差異により界面に発生する歪みが、緩和できる。ここで、第1の窒化ガリウム系化合物半導体は、好ましくは常圧又は微減圧で成長させる。

【0032】

次に第1の窒化ガリウム系化合物半導体を成長後、この上に第2の窒化ガリウム系化合物半導体を以下の条件で成長させる。

【0033】

第2の窒化ガリウム系化合物半導体は第1の窒化ガリウム系化合物半導体と同温、又はそれ以上の温度で成長させるのが好ましく、基板温度を900℃以上とする。ただし、第1の窒化ガリウム系化合物半導体と第2の窒化ガリウム系化合物半導体との温度差が大きければ成長層界面に残留熱歪みが発生するため温度差が少ない方が好ましい。また、第2の窒化ガリウム系化合物半導体の膜厚としては、最上面が鏡面になれば特に限定されず15μm以上であればよい。そのため、第2の窒化ガリウム系化合物半導体は膜厚を15μm程度の成長が可能な気相成長法であればMOCVD法や他の気相成長法でも行うことができる。さらに、結晶の核密度の均一性や配向特性、及び大きさ、層の厚みの制御にはMOCVD法を用いるのが好ましい。

【0034】

上記の成長方法により得られた窒化ガリウム系化合物半導体基板は、最上面が平坦であり、且つ鏡面となる低欠陥部分を広範囲で有する窒化ガリウム系化合物半導体基板と成る。なお、本発明により得られた窒化ガリウム系化合物半導体基板上に形成する素子は窒化ガリウム系化合物半導体を用いたものであれば発光素子や受光素子、又は電子デバイスでもよい。また、図3には本実施形態における発光素子として同一面上に電極を形成した半導体レーザ素子を示す。図4には電極を対極構造として形成した半導体レーザ素子を示す。

【0035】

以上より得られる窒化ガリウム系化合物半導体基板は貫通転位密度が1×108/cm2以下、より好ましくは1×107/cm2以下である第2の窒化ガリウム系化合物半導体層を有するものとする。

【0036】

【実施例】

以下、本発明における実施例を説明する。

[実施例1]

まず、基板1としてC面を主面とするサファイア基板を用い、MOCVD装置にセットし、温度1050℃で10分間のサーマルクリーニングを行い水分や表面の付着物を除去した。

【0037】

次に、下地層を2層構造で成長させた。まず、温度を510℃にして、キャリアガスに水素、原料ガスにアンモニアとトリメチルガリウムを用い、GaNより成るバッファー層を200オングストロームの膜厚で成長させた。次に、バッファー層上にGaNから成り平坦性を有する層を成長温度1050℃において膜厚3μmで形成した。本実施例では、成長時のキャリアガスとして水素を20.5L/分、原料ガスとしてアンモニアを5L/分、トリメチルガリウムを25cc/分間、流した。

【0038】

基板上に下地層を成長後、第1の窒化ガリウム系化合物半導体、及び第2の窒化ガリウム系化合物半導体を成長させるためにHVPE装置にセットする。

【0039】

まず、Ga源として、Gaメタルをボートに用意し、キャリアガスに窒素、及び/又は水素を用いてハロゲンガスであるHClガスを流すことによりGaClを生成する。キャリアガスに窒素、及び/又は水素を用いてN源であるアンモニアガスを流すことによりGaClとアンモニアガスとを反応させ基板領域にGaNを形成する。また、キャリアガスに窒素、及び/又は水素を用いてSiCl4を流すことでドーピングを行い、SiドープGaNよりなる第1の窒化ガリウム系化合物半導体を基板上に成長させる。基板領域の温度は電気炉で1030℃に設定した。第1の窒化ガリウム系化合物半導体の成長速度を50μm/hourとして、GaCl分圧は1.25×10−3atm、NH3分圧は0.375atmとした。SiCl4分圧は2.87×10−7atmとした。この第1の窒化ガリウム系化合物半導体は膜厚50μmで成長させた。

【0040】

次に、第1の窒化ガリウム系化合物半導体上に、第2の窒化ガリウム系化合物半導体をハロゲン輸送法による気相エピタキシャル成長法装置において成長させた。この時の成長条件としては、SiCl4分圧を1.0×10−8atmとした以外は成長条件を第1の窒化ガリウム系化合物半導体と同様にして、第2の窒化ガリウム系化合物半導体を成長速度50μm/hourで膜厚は100μmで成長させた。

【0041】

以上により得られた第2の窒化ガリウム系化合物半導体基板の表面は平坦かつ鏡面となり、SIMS分析ではSi濃度は第1の窒化ガリウム系化合物半導体層は2×1019/cm2であり、第2の窒化ガリウム系化合物半導体層は2×1018/cm2であった。また、図2に示すようにCL観察によると貫通転位密度は2×107cm−2程度であり、低欠陥である窒化ガリウム系化合物半導体基板を提供することができる。

【0042】

[実施例2]

上記実施例1で得られた窒化ガリウム系化合物半導体基板上に第3の窒化ガリウム系化合物半導体層、第4の窒化ガリウム系化合物半導体層を成長させる。この第3の窒化ガリウム系化合物半導体層は第1の窒化ガリウム系化合物半導体層と成長条件を同じとし、また第4の窒化ガリウム系化合物半導体層は第2の窒化ガリウム系化合物半導体層と成長条件を同様とする。

【0043】

以上より得られた窒化ガリウム系化合物半導体基板は厚膜成長した低転位の基板となるため、異種基板を除去した単体基板とすることができる。

【0044】

[実施例3]

実施例1により得られた窒化ガリウム系化合物半導体基板より、研削によりサファイア基板を除去し、GaNの単体基板とする。この単体基板上にレーザ素子を形成する。

【0045】

(n型コンタクト層102)

まず、GaNの単体基板をMOCVD装置の反応容器にセットしTMG、TMA、アンモニア、不純物ガスとしてシランガスを用い、1050℃でSiドープしたAl0.05Ga0.95Nよりなるn型コンタクト層102を4μmの膜厚で成長させる。

【0046】

(クラック防止層103)

次に、TMG、TMI(トリメチルインジウム)、アンモニアを用い、温度を900℃にしてIn0.07Ga0.93Nよりなるクラック防止層103を0.15μmの膜厚で成長させる。なお、このクラック防止層は省略可能である。

【0047】

(n型クラッド層104)

次に、温度を1050℃にして、原料ガスにTMA、TMG及びアンモニアを用い、アンドープのAl0.05Ga0.95NよりなるA層を25Åの膜厚で成長させ、続いて、TMAを止め、不純物ガスとしてシランガスを用い、Siを5×1018/cm3ドープしたGaNよりなるB層を25Åの膜厚で成長させる。この操作を200回繰り返しA層とB層との積層構造とし、総膜厚1μmの多層膜(超格子構造)よりなるn型クラッド層を成長させる。

【0048】

(n型ガイド層105)

次に、同様の温度で、原料ガスにTMG及びアンモニアを用い、アンドープのGaNよりなるn型ガイド層105を0.15μmの膜厚で成長させる。このn型ガイド層105は、n型不純物をドープしてもよい。

【0049】

(活性層106)

次に、温度を900℃にし、原料ガスにTMI(トリメチルインジウム)、TMG及びアンモニアを用い、不純物ガスとしてシランガスを用い、Siを5×1018/cm3ドープしたIn0.05Ga0.95Nよりなる障壁層を140Åの膜厚、シランガスを止め、アンドープのIn0.13Ga0.87Nよりなる井戸層を40Åの膜厚で、障壁層/井戸層/障壁層/井戸層の順に積層し、最後に障壁層として、TMI、TMG及びアンモニアを用い、アンドープのIn0.05Ga0.95Nを成長させる。活性層106は、総膜厚500Åの多重量子井戸構造(MQW)となる。

【0050】

(p型電子閉じ込め層107)

次に、活性層と同じ温度で、原料ガスにTMA、TMG及びアンモニアを用い、不純物ガスとしてCp2Mg(シクロペンタジエニルマグネシウム)を用い、Mgを1×1019/cm3ドープしたAl0.3Ga0.7Nよりなるp型電子閉じ込め層107を100Åの膜厚で成長させる。

【0051】

(p型ガイド層108)

次に、温度を1050℃にして、原料ガスにTMG及びアンモニアを用い、アンドープのGaNよりなるp型ガイド層108を0.15μmの膜厚で成長させる。このp型ガイド層は、p型不純物をドープしてもよい。

【0052】

(p型クラッド層109)

次に、1050℃でアンドープAl0.05Ga0.95NよりなるA層を25Åの膜厚で成長させ、続いてTMAを止め、Cp2Mgを用いて、MgドープGaNよりなるB層を25Åの膜厚で成長させ、それを90回繰り返して総膜厚0.45μmの超格子層よりなるp型クラッド層109を成長させる。p型クラッド層は、GaNとAlGaNとを積層した超格子構造とする。p型クラッド層109を超格子構造とすることによって、クラッド層全体のAl混晶比を上げることができるので、クラッド層自体の屈折率が小さくなり、さらにバンドギャップエネルギーが大きくなるので、しきい値を低下させる上で非常に有効である。

【0053】

(p型コンタクト層110)

最後に、1050℃で、p型クラッド層109の上に、TMG、アンモニア、Cp2Mgを用い、Mgを1×1020/cm3ドープしたp型GaNよりなるp型コンタクト層110を150Åの膜厚で成長させる。

反応終了後、反応容器内において、ウェハーを窒素雰囲気中、700℃でアニーリングを行い、p型層をさらに低抵抗化する。

【0054】

アニーリング後、窒化物半導体レーザ素子を積層させたGaNから成る単体基板を反応容器から取り出し、最上層のp型コンタクト層の表面にSiO2よりなる保護膜を形成して、RIE(反応性イオンエッチング)を用いてCF4ガスによりエッチングすることにより、ストライプ状の導波路領域としてリッジストライプを形成する。

【0055】

次にリッジストライプ形成後、Zr酸化物(主としてZrO2)よりなる絶縁保護膜を、エッチングにより露出したp型ガイド層108上に0.5μmの膜厚で形成する。

【0056】

p型コンタクト層上にp型電極をNiとAuより形成する。ここで、p型電極の膜厚としてはNiを100Å、Auを1300Åとする。また、p型電極と対極するように裏面となる第1の窒化ガリウム系化合物半導体層にはTiとAlよりn型電極を形成する。Tiは200Å、Alを8000Åの膜厚とする。このp型電極は、リッジ上にストライプ形成されており、同じくストライプ形成されているn型電極とは対極であり平行な方向で形成する。次に、p型電極、n型電極上にそれぞれパッド電極を形成する。p型電極上にはp型パッド電極としてRhO(酸化ロジウム)/Pt/Auを(3000Å−1500Å−6000Å)の膜厚で形成する。また、n型電極上にはn型パッド電極としてNi/Ti/Auを(1000Å−1000Å−8000Å)の膜厚で形成する。

【0057】

電極形成後、n型電極側をスクライブして、リッジストライプに垂直な方向でバー状に劈開し、劈開面にSiO2とTiO2よりなる誘電体多層膜を共振器ミラーとして成膜する。その後、リッジストライプに平行な方向で、バーを切断してレーザチップとする。

【0058】

以上のようにして得られたレーザ素子は、室温においてしきい値2.8kA/cm2、5〜60mWの出力において発振波長405nmの連続発振のレーザ素子が得られる。得られるレーザ素子の素子寿命は、1000〜30000時間を示す。

【0059】

[実施例4]

実施例1により得られた窒化ガリウム系化合物半導体基板より、研削によりサファイア基板を除去し、GaNの単体基板とする。この単体基板上の同一面上にn型電極とp型電極とを形成したレーザ素子を作成する。

【0060】

まず、GaN基板をMOCVD装置の反応容器内にセットし、1050℃で窒化物半導体に、TMG(トリメチルガリウム)、TMA(トリメチルアルミニウム)、アンモニアを用い、Al0.05Ga0.95Nよりなるアンドープn型コンタクト層101を1μmの膜厚で成長させる。この層は、GaNからなる窒化物半導体基板とn型コンタクト層をはじめとする半導体素子との間で、緩衝層としての機能を有する。ただし、このアンドープn型コンタクト層は省略することもできる。

【0061】

次に、アンドープn型コンタクト層を成長後に実施例3と同様の条件でさらにn型コンタクト層102/クラック防止層103/n型クラッド層104/n型ガイド層105/活性層106/p型電子閉じ込め層107/p型ガイド層108/p型クラッド層109/p型コンタクト層110を成長させる。

【0062】

その後、リッジ幅1.7μmでリッジストライプ形成する。次に、n型コンタクト層をエッチングにより露出する。その後、Zr酸化物(主としてZrO2)よりなる絶縁保護膜を、エッチングにより露出したp型ガイド層108上に膜厚を0.5μm以下で形成する。その後、ストライプ形状に露出したp型コンタクト層上にp型電極をNiとAuより形成する。ここで、p型電極の膜厚としてはNi(100Å)、Au(1300Å)とする。また、p型電極を形成した後に前記露出したn型コンタクト層上にn型電極を形成する。このn型電極はTi/Alを膜厚(200Å−8000Å)でp型電極と同一面上に平行に形成する。さらに、p型電極、n型電極上にそれぞれパッド電極を形成する。p型電極上にはp型パッド電極としてRhO(酸化ロジウム)/Pt/Auを(3000Å−1500Å−6000Å)の膜厚で形成する。また、n型電極上にはn型パッド電極としてNi/Ti/Auを(1000Å−1000Å−8000Å)の膜厚で形成する。

【0063】

電極形成後、基板の裏面側をスクライブして、リッジストライプに垂直な方向でバー状に劈開し、劈開面にSiO2とTiO2よりなる誘電体多層膜を共振器ミラーとして成膜する。その後、リッジストライプに平行な方向で、バーを切断してレーザチップとする。

【0064】

以上のようにして得られたレーザ素子は、室温においてしきい値2.8kA/cm2、5〜60mWの出力において発振波長405nmの連続発振のレーザ素子が得られる。得られるレーザ素子の素子寿命は、1000〜30000時間となる。

【0065】

[実施例5]

実施例1により得られたサファイア付きの窒化ガリウム系化合物半導体基板上にレーザ素子を形成する。まず、前記基板上にアンドープn型コンタクト層101を成長させる。基板をMOCVD装置の反応容器内にセットし、1050℃で窒化物半導体に、TMG(トリメチルガリウム)、TMA(トリメチルアルミニウム)、アンモニアを用い、Al0.05Ga0.95Nよりなるアンドープn型コンタクト層101を1μmの膜厚で成長させる。この層は、GaNからなる窒化物半導体基板とn型コンタクト層をはじめとする半導体素子との間で、緩衝層としての機能を有する。

【0066】

次に実施例3と同様の条件で以下の順に素子形成を行う。

アンドープn型コンタクト層を成長させた基板上にn型コンタクト層102/クラック防止層103/n型クラッド層104/n型ガイド層105/活性層106/p型電子閉じ込め層107/p型ガイド層108/p型クラッド層109/p型コンタクト層110の順で成長させる。

【0067】

その後、リッジ幅1.7μmでリッジストライプ形成する。次に、n型コンタクト層をエッチングにより露出する。その後、Zr酸化物(主としてZrO2)よりなる絶縁保護膜を、エッチングにより露出したp型ガイド層108上に膜厚を0.5μm以下で形成する。その後、ストライプ形状に露出したp型コンタクト層上にp型電極をNiとAuより形成する。ここで、p型電極の膜厚としてはNi(100Å)、Au(1300Å)とする。また、p型電極を形成した後に前記露出したn型コンタクト層上にn型電極を形成する。このn型電極はTi/Alを膜厚(200Å−8000Å)でp型電極と同一面上に平行に形成する。さらに、p型電極、n型電極上にそれぞれパッド電極を形成する。p型電極上にはp型パッド電極としてRhO(酸化ロジウム)/Pt/Auを(3000Å−1500Å−6000Å)の膜厚で形成する。また、n型電極上にはn型パッド電極としてNi/Ti/Auを(1000Å−1000Å−8000Å)の膜厚で形成する。

【0068】

電極形成後、基板の裏面側をダイシングして、リッジストライプに垂直な方向でバー状に劈開し、劈開面にSiO2とTiO2よりなる誘電体多層膜を共振器ミラーとして成膜する。その後、リッジストライプに平行な方向で、バーを切断してレーザチップとする。以上より得られたレーザ素子の素子寿命は、500〜10000時間となる。

【0069】

[実施例6]

実施例1により得られたサファイア付きの窒化ガリウム系化合物半導体基板上にレーザ素子を形成する。まず、前記基板上にアンドープn型コンタクト層101を成長させる。基板をMOCVD装置の反応容器内にセットし、1050℃で窒化物半導体に、TMG(トリメチルガリウム)、TMA(トリメチルアルミニウム)、アンモニアを用い、Al0.05Ga0.95Nよりなるアンドープn型コンタクト層101を1μmの膜厚で成長させる。この層は、GaNからなる窒化物半導体基板とn型コンタクト層をはじめとする半導体素子との間で、緩衝層としての機能を有する。

【0070】

前期アンドープn型コンタクト層101を成長させた基板上に、実施例3と同条件でn型コンタクト層102/クラック防止層103/n型クラッド層104/n型ガイド層105/活性層106/p型電子閉じ込め層107/p型ガイド層108/p型クラッド層109/p型コンタクト層110の順で半導体素子を成長させる。

【0071】

次に、研削によりサファイア基板を除去し、さらに、リッジ幅1.7μmでリッジストライプ形成する。次に、n型コンタクト層をエッチングにより露出する。その後、Zr酸化物(主としてZrO2)よりなる絶縁保護膜を、エッチングにより露出したp型ガイド層108上に膜厚を0.5μm以下で形成する。その後、ストライプ形状に露出したp型コンタクト層上にp型電極をNiとAuより形成する。ここで、p型電極の膜厚としてはNi(100Å)、Au(1300Å)とする。また、p型電極を形成した後に前記露出したn型コンタクト層上にn型電極を形成する。このn型電極はTi/Alを膜厚(200Å−8000Å)でp型電極と同一面上に平行に形成する。さらに、p型電極、n型電極上にそれぞれパッド電極を形成する。p型電極上にはp型パッド電極としてRhO(酸化ロジウム)/Pt/Auを(3000Å−1500Å−6000Å)の膜厚で形成する。また、n型電極上にはn型パッド電極としてNi/Ti/Auを(1000Å−1000Å−8000Å)の膜厚で形成する。

【0072】

電極形成後、基板の裏面側をスクライブして、リッジストライプに垂直な方向でバー状に劈開し、劈開面にSiO2とTiO2よりなる誘電体多層膜を共振器ミラーとして成膜する。その後、リッジストライプに平行な方向で、バーを切断してレーザチップとする。以上より得られたレーザ素子の素子寿命は、1000〜30000時間となる。

【0073】

[実施例7]

上記実施例3〜6において、n型電極をTi/Al(200Å−8000Å)、p型電極をNi/Au(100Å−1500Å)、n型パッド電極とp型パッド電極とをNi/Ti/Au(1000Å−1000Å−8000Å)とする以外は同条件でレーザ素子を形成する。ここで得られるレーザ素子の寿命特性は500〜10000時間となる。

【0074】

[実施例8]

C面を主面とし、オリフラ面をA面とするサファイア基板を基板1に用い、基板1上にCVD法によりSiO2よりなる保護膜を0.5μmの膜厚で成膜し、ストライプ状のフォトマスクを形成し、エッチングによりストライプ幅14μm、窓部6μmのSiO2よりなる保護膜を形成する。なお、この保護膜のストライプ方向はサファイアA面に対して垂直な方向とする。

【0075】

次に、MOCVD法により、温度を510℃、キャリアガスに水素、原料ガスにアンモニアとTMG(トリメチルガリウム)とを用い、保護膜の開口部上に窒化ガリウムよりなるバッファー層を200オングストロームの膜厚で成長させる。その後、MOCVD法により、減圧条件で温度を1050℃にして、原料ガスにTMG、アンモニア、シランガス、Cp2Mg(シクロペンタジエニルマグネシウム)を用い、窒化ガリウムよりなる第1の窒化物半導体層を10μmの膜厚で成長させる。この時、第1の窒化物半導体は、SiO2より成る保護膜の開口部を成長起点とし、第1の窒化物半導体層の断面形状がT字形状となるように形成する。

【0076】

次に、ドライエッチングである等方性エッチングにより、温度120℃で、エッチングガスに酸素、CF4を用い、SiO2保護膜を取り除く。さらに、横方向成長させた第1の窒化物半導体の側面および上面より、常圧でMOCVD法により、温度を1050℃にし、原料ガスにTMG、アンモニア、シランガス、Cp2Mg(シクロペンタジエニルマグネシウム)を用い、窒化ガリウムよりなる第2の窒化物半導体層を15μmの膜厚で成長させる。

【0077】

以上より得られた基板上に第1の窒化ガリウム系化合物半導体、及び第2の窒化ガリウム系化合物半導体を成長させるためにHVPE装置にセットする。Ga源として、Gaメタルをボートに用意し、キャリアガスに窒素、及び/又は水素を用いてハロゲンガスであるHClガスを流すことによりGaClを生成する。キャリアガスに窒素、及び/又は水素を用いてN源であるアンモニアガスを流すことによりGaClとアンモニアガスとを反応させ基板領域にGaNを形成する。また、キャリアガスに窒素、及び/又は水素を用いてSiCl4を流すことでドーピングを行い、SiドープGaNよりなる第1の窒化ガリウム系化合物半導体を基板上に成長させる。基板領域の温度は電気炉で1030℃に設定する。第1の窒化ガリウム系化合物半導体の成長速度を50μm/hourとして、GaCl分圧は1.25×10−3atm、NH3分圧は0.375atmとする。SiCl4分圧は2.87×10−7atmとする。この第1の窒化ガリウム系化合物半導体は膜厚50μmで成長させる。

【0078】

次に、第1の窒化ガリウム系化合物半導体上に、第2の窒化ガリウム系化合物半導体をハロゲン輸送法による気相エピタキシャル成長法装置において成長させる。この時の成長条件としては、SiCl4分圧を1.0×10−8atmとした以外は成長条件を第1の窒化ガリウム系化合物半導体と同様にして、第2の窒化ガリウム系化合物半導体を成長速度50μm/hourで膜厚は100μmで成長させる。

【0079】

以上により得られる第2の窒化ガリウム系化合物半導体基板の表面は平坦かつ鏡面となり、貫通転位密度が1×107cm−2以下となる低欠陥な窒化ガリウム系化合物半導体基板を提供することができる。

【0080】

[実施例9]

上記実施例において、第1の窒化ガリウム系化合物半導体の成長速度を50μm/hourとして、第2の窒化ガリウム系化合物半導体を成長速度100μm/hourで成長させる以外は同条件で窒化ガリウム系化合物半導体基板を形成する。以上により得られる第2の窒化ガリウム系化合物半導体基板の表面は平坦かつ鏡面となり、貫通転位密度が1×108cm−2以下となる低欠陥な窒化ガリウム系化合物半導体基板を提供することができる。

【0081】

【発明の効果】

以上より本発明では、保護膜等を用いた横方向成長基板ではなく、基板全面の結晶欠陥を減らした低欠陥基板を提供することができる。そのため、ELO法で得られた基板に比べてデバイス工程を簡略化することができ、量産効率を向上させた窒化ガリウム系化合物半導体基板を提供することが出来る。また、基板を除去することにより窒化物から成る低抵抗の単体基板とすることもできるため、放熱性が向上し窒化物半導体素子の寿命特性をよくすることができる。さらに、対極した電極構造が可能となりチップ面積の節減にも有利となる。

【0082】

【図面の簡単な説明】

【図1】本発明の一実施の形態を示す窒化物半導体の模式断面図である。

【図2】本発明の実施例1におけるCL写真である。

【図3】本発明の一実施の形態における窒化物半導体レーザ素子の模式断面図である。

【図4】本発明の一実施の形態における窒化物半導体レーザ素子の模式断面図である。

【符号の簡単な説明】

1・・・基板

2・・・下地層

3・・・第1の窒化ガリウム系化合物半導体

4・・・第2の窒化ガリウム系化合物半導体

101・・・アンドープn型コンタクト層

102・・・n型コンタクト層

103・・・クラック防止層

104・・・n型クラッド層

105・・・n型ガイド層

106・・・活性層

107・・・p型電子閉じ込め層

108・・・p型ガイド層

109・・・p型クラッド層

110・・・p型コンタクト層[0001]

BACKGROUND OF THE INVENTION

The present invention relates to a gallium nitride compound semiconductor substrate and a method for manufacturing the same, and particularly to a gallium nitride compound semiconductor substrate having n-type conductivity with reduced threading dislocation density.

[0002]

[Prior art]

Gallium nitride compound semiconductors have a light emission wavelength in the short wavelength region around 400 nm, and therefore can be used as light emission light sources from ultraviolet to green. When used as semiconductor laser diodes, they are several in comparison with conventional red laser diodes. It can be used as a playback device or storage device for double the capacity of media. Furthermore, application to electronic devices such as field effect transistors (FETs) is also expected.

[0003]

In order to produce such a gallium nitride compound semiconductor device, a substrate capable of homoepitaxial growth of bulk single crystal gallium nitride or gallium nitride compound semiconductor is desired. Difficult due to high pressure. Therefore, a gallium nitride compound semiconductor is heteroepitaxially grown on a substrate such as sapphire, silicon carbide, or spinel. A gallium nitride compound semiconductor is grown using this nitride semiconductor substrate as a substrate.

[0004]

If the difference in lattice constant between the substrate and the gallium nitride compound semiconductor stacked on the substrate is large, threading dislocations are generated in the gallium nitride compound semiconductor layer stacked on the substrate. If there are many threading dislocations, the leakage current increases, and the life characteristics of the light emitting element such as a semiconductor laser diode are greatly deteriorated. When a gallium nitride compound semiconductor is grown on a substrate such as sapphire, threading dislocations can be reduced through a buffer layer. For example, JP-A-7-202265 and JP-A-7-165498 report a buffer layer made of ZnO. In addition, although there are AlN and GaN buffer layers, the threading dislocation density is 108Piece / cm2-1010Piece / cm2Degree. A semiconductor laser diode or a high-power light emitting diode using a gallium nitride compound semiconductor grown on a substrate through such a buffer layer as an element cannot be expected to be continuously oscillated for a long time.

[0005]

Therefore, an ELO (Epitaxial Lateral Overgrowth) method having an effect of further reducing the threading dislocation density has been reported. This ELO method is a method for reducing dislocations utilizing the lateral growth of a compound semiconductor. For example, a protective film having an opening (window) is formed in, for example, a stripe shape or an island shape on a gallium nitride-based compound semiconductor that is a base layer. Next, a gallium nitride compound semiconductor is grown with the underlying gallium nitride compound semiconductor exposed from the opening of the protective film as a nucleus. A gallium nitride compound semiconductor grown with the underlying layer as a nucleus grows in the vertical direction from the opening and then also grows in the horizontal direction. This lateral growth is continuous growth from the nucleus and grows laterally on the protective film. Thus, threading dislocations grow not only in the vertical direction but also in the horizontal direction, as in the case of gallium nitride compound semiconductors. Therefore, the threading dislocations grown in the lateral direction are concentrated at the junction where the gallium nitride compound semiconductors grown from the adjacent nuclei on the protective film are joined. Therefore, although threading dislocations concentrate on the opening of the protective film and the junction on the protective film, a low dislocation region can be formed on the surface of the lateral growth region excluding these regions.As another method for reducing the threading dislocation density, a first growth layer having a high vertical growth rate and a rough surface is grown, and then the vertical growth rate is lower than that of the first growth layer. Japanese Patent Application Laid-Open No. 2001-168045 discloses a method of growing a growth layer to fill a depression of the first growth layer. Japanese Patent Laid-Open No. 11-1399 discloses a silicon impurity of 10 18 -10 20 cm -3 A method for obtaining an n-type gallium nitride semiconductor substrate by adjusting in the above range is described. Such an n-type gallium nitride semiconductor substrate is formed by repeating a gallium nitride growth process and a polishing process.

[0006]

[Problems to be solved by the invention]

However, the ELO method described above has many steps such as pattern formation of a protective film, and it is difficult to efficiently mass-produce. Further, in the ELO method, an opening is provided in the protective film, and the gallium nitride compound semiconductor is grown using the gallium nitride compound semiconductor exposed from the opening as a nucleus. Therefore, a low dislocation region is obtained in the lateral growth region. However, many dislocations are concentrated on the upper portion of the window, which is the opening, and the junction between the gallium nitride compound semiconductors on the protective film. Therefore, it is difficult to provide a substrate having a uniform low dislocation region on the surface, and a ridge stripe must be selectively formed in the low dislocation region. Therefore, the yield is lowered in the photolithography process for forming the ridge stripe on the warped wafer. In addition, a nitride semiconductor substrate obtained by the ELO method has an insulating heterogeneous substrate, and for example, a nitride semiconductor is formed on a sapphire substrate. For this reason, heat dissipation is poor and continuous oscillation at high output for a long time is difficult. In addition, since the sapphire substrate is insulative, an n-type electrode and a p-type electrode must be formed on the surface, and a step of forming a step after the element is grown is necessary. This is also disadvantageous in reducing the chip area as compared with an element in which an electrode is formed on the counter electrode surface. In addition, since the sapphire substrate is not flaky, a dicing process is required for chip separation, resulting in high costs.

[0007]

An object of the present invention is to obtain a low dislocation region uniformly and over a wide area on the surface of a gallium nitride compound semiconductor substrate. Another object of the present invention is to provide a gallium nitride compound semiconductor substrate with improved mass production efficiency by using an n-type low resistance single substrate from which a different substrate is removed.

[0008]

[Means for Solving the Problems]

The gallium nitride compound semiconductor substrate of the present invention has a Si doping concentration of 1 × 1019/ Cm3The first gallium nitride compound semiconductor layer and the Si concentration lower than that of the first gallium nitride compound semiconductor layer stacked on the first gallium nitride compound semiconductor layer, non-doped, or Si doping concentration is 1 × 1019/ Cm3A second gallium nitride compound semiconductor layer, which is:The first gallium nitride compound semiconductor layer is grown as an island of gallium nitride compound semiconductor, and the second gallium nitride compound semiconductor layer is formed of an island of the gallium nitride compound semiconductor. Growing and adjacent islands are combined to form threading dislocation density of 1 × 10 8 / Cm 2 IsIt is characterized by that.

[0009]

The method for producing a gallium nitride compound semiconductor substrate according to the present invention is a method for producing a gallium nitride compound semiconductor substrate formed by growing a gallium nitride compound semiconductor layer on a substrate by vapor deposition. Si doping concentration is 1 × 1019/ Cm3The first step of forming the first gallium nitride compound semiconductor layer, and the first gallium nitride compound semiconductor layer on the first gallium nitride compound semiconductor layer after the first step. The Si concentration is lower than that, non-doped, or Si doping concentration is 1 × 1019/ Cm3A second step of forming a second gallium nitride compound semiconductor layer,In the first step, the first gallium nitride compound semiconductor layer is an island of gallium nitride compound semiconductor, and in the second step, the second nitridation is performed in the second step. The gallium compound semiconductor layer is formed by growing islands of the gallium nitride compound semiconductor and joining adjacent islands together.It is characterized by that.

[0010]

Thus, the Si doping concentration is 1 × 1019/ Cm3The Si-rich layer as described above, and the Si doping concentration on the Si-rich layer is non-doped, or 1 × 1019/ Cm3If the following Si poor layer is grown, dislocation can be reduced. Here, the Si poor layer includes non-doped Si. The reason why dislocation can be reduced will be described below. In the Si-rich layer, Si acts not only as a donor but also as a contaminant on the growth layer. For this reason, the growth of the site where Si or its compound has a high deposition density is delayed. That is, the gallium nitride compound semiconductor grown on the substrate has an in-plane distribution having a growth rate difference. As a result, nuclei are selectively generated in a portion having a high growth rate on the entire surface, and gallium nitride compound semiconductor islands grow on the surface of the gallium nitride compound semiconductor. Next, in the Si poor layer to be grown, the coalescence of the gallium nitride compound semiconductor islands is promoted. This is because crystal grains having a high growth rate grow so as to cover adjacent crystal grains. Here, the island of the gallium nitride compound semiconductor has threading dislocations extending from the growth interface between the substrate and the gallium nitride compound semiconductor. This threading dislocation not only extends in the vertical direction as the island grows, but also extends perpendicularly to the slope that is the growth surface because the surface of the island has a slope shape. Therefore, the threading dislocations bend and the threading dislocations form a loop in the process of island growth and coalescence between adjacent islands. Therefore, threading dislocations extending in a direction other than the longitudinal direction in the first gallium nitride-based compound semiconductor layer can be reduced by forming a loop in the second gallium nitride-based compound semiconductor layer. Further, the first gallium nitride compound semiconductor layer has a Si doping concentration of 5 × 10 5.19/ Cm3Since the distance between the islands can be formed larger as described above, dislocations can be further reduced when the second gallium nitride compound semiconductor layer is grown. More preferably, the Si doping concentration of the first gallium nitride-based compound semiconductor layer is 1 × 1020/ Cm3That's it. The second gallium nitride compound semiconductor layer has a Si doping concentration of 1 × 10 5.18/ Cm3The mobility can be improved by the following, and more preferably, the Si doping concentration is 1 × 10 6.17/ Cm3The following. Specifically, the first gallium nitride compound semiconductor layer is grown on the gallium nitride compound semiconductor substrate via a buffer layer, and threading dislocations are reduced by the second gallium nitride compound semiconductor layer grown thereon. Let With only a buffer layer, threading dislocations are 1 × 10 per unit area8Piece / cm2~ 1x1010Piece / cm2However, with the above structure, the threading dislocation density on the surface of the second gallium nitride-based compound semiconductor layer can be reduced uniformly.8Piece / cm2Or less, more preferably 1 × 106Piece / cm2It can be as follows.

[0011]

Furthermore, the Si doping concentration is 1 × 10 6 on the second gallium nitride compound semiconductor layer.19/ Cm3The third gallium nitride compound semiconductor layer is stacked on the third gallium nitride compound semiconductor layer., The Si concentration is lower than that of the third gallium nitride compound semiconductor layer,Non-doped or Si doping concentration is 1 × 1019/ Cm3And a fourth gallium nitride compound semiconductor layer which is the following.

[0012]

Thus, if the structure for growing the Si-rich layer and the Si poor layer is repeated twice or more, the threading dislocations form a loop to further reduce the dislocations. In addition, when a thick film is grown by vapor deposition using the halogen transport method, it is possible to form a single substrate consisting only of a gallium nitride compound semiconductor layer from which a dissimilar substrate such as sapphire is removed by grinding or laser irradiation. . Therefore, even a nitride semiconductor substrate grown on an insulator such as a sapphire substrate is removed, and the Si-rich layer is doped with Si at a high concentration to form a low-resistance n-type substrate. Therefore, the electrode can have a counter electrode structure. Here, the step of removing the heterogeneous substrate may be before the growth of the nitride semiconductor element or after the growth of the nitride semiconductor element.

[0013]

In addition, the first and / or second gallium nitride compound semiconductor layer in the gallium nitride compound semiconductor substrate has the general formula InxAlyGa1-xyN (0 ≦ X <1, 0 ≦ Y <1, 0 ≦ X + Y <1). Furthermore, GaN has the effect of reducing pits on the surface after two-stage growth.

[0014]

A silane compound is used as a raw material for Si doping. This silane compound is SiH4, Si2H6, SiHCl3, SiH2Cl2, SiH3Cl, SiCl4Is at least one selected from the group consisting of Use of these raw materials is preferable because Si or a compound thereof can be effectively used as a dopant as well as a contaminant.

[0015]

If the first gallium nitride compound semiconductor is directly grown on a heterogeneous substrate such as sapphire, for example, the dislocation density increases due to the difference in lattice constant and thermal expansion coefficient. Therefore, the crystallinity can be further improved by forming the gallium nitride compound semiconductor layer directly on the substrate through the buffer layer which is the base layer. Specifically, InxAlyGa1-xyN (0.ltoreq.X <1, 0.ltoreq.Y <1, 0.ltoreq.X + Y <1), which is formed by low-temperature growth at 700.degree. C. or lower. The gallium nitride compound semiconductor grown only through this underlayer has 10 threading dislocations per unit area.8-1010Piece / cm2It becomes. Therefore, a nitride semiconductor substrate with better crystallinity can be formed by growing the Si rich layer and the Si poor layer on the base layer.

[0016]

Furthermore, the growth rates of the first gallium nitride compound semiconductor layer and the second gallium nitride compound semiconductor layer can be made substantially the same. In the first step, islands of the first gallium nitride-based compound semiconductor layer can be grown, and in the second step, formation of the second gallium nitride-based compound semiconductor layer can be promoted. Also,Examples of the vapor phase growth method of the gallium nitride compound semiconductor substrate include a vapor phase growth method using a halogen transport method, a metal organic vapor phase growth method, and a molecular beam epitaxy method. The vapor phase growth method based on the halogen transport method is preferable because it can grow a thick film because of its high growth rate. In order to reduce the number of defects in a thin film, another vapor phase growth method such as a metal organic chemical vapor deposition method or a molecular beam epitaxy method in which the lateral growth can be easily controlled may be used.

[0017]

In the method for manufacturing a gallium nitride compound semiconductor substrate, examples of the substrate include sapphire, silicon carbide, spinel, or silicon. These can epitaxially grow a gallium nitride-based compound semiconductor and have heat resistance against the growth temperature. Further, after the gallium nitride compound semiconductor layer is stacked, the substrate can be peeled and removed by grinding, electromagnetic wave irradiation, or the like, whereby a single substrate made of a gallium nitride compound semiconductor can be formed. In the present invention, since the first gallium nitride compound semiconductor layer is an Si-rich layer, the substrate removal surface can be an n-type nitride semiconductor layer. Therefore, it is possible to provide a gallium nitride-based compound semiconductor laser or a light-emitting diode in which electrodes are formed as counter electrodes in a single crystal nitride substrate with reduced threading dislocations and good crystallinity.

[0018]

DETAILED DESCRIPTION OF THE INVENTION

The gallium nitride compound semiconductor substrate according to the embodiment of the present invention is:As shown in FIG.Si doping concentration is 1 × 1019/ Cm3The first gallium nitride

[0019]

Si raw materials are silane compounds, and these silane compounds are SiH.4, Si2H6, SiHCl3, SiH2Cl2, SiH3Cl, SiCl4Is at least one selected from the group consisting of

[0020]

The first gallium nitride compound semiconductor and the second gallium nitride compound semiconductor have the general formula InxAlyGa1-xyN (0 ≦ X <1, 0 ≦ Y <1, 0 ≦ X + Y <1).

[0021]

The invention in the present embodiment is performed simultaneously with the growth of the gallium nitride compound semiconductor by Si doping. By performing the two-step growth, the surface is flattened and a gallium nitride compound semiconductor substrate having a low defect region in a wide range is manufactured. be able to. Such flattening is possible due to the natural lateral growth of the crystal. In the gallium nitride compound semiconductor substrate shown in the present embodiment, as a method for reducing dislocations, dislocations are not reduced without embedding facets, but grown while embedding facets to reduce dislocations. As described above, the gallium nitride compound semiconductor substrate can be formed efficiently without the need for planarization by surface polishing or the like.

[0022]

In the present invention, a low-resistance n-type single substrate can be formed by removing the substrate. This is because, in the process of reducing dislocations, Si is continuously doped in the gallium nitride compound semiconductor layer, so that a low-resistance n-type semiconductor layer can be formed. For this reason, it can be set as the structure which formed the electrode in the counter electrode, and it is advantageous to reduction of a chip area. In addition, since there is no heterogeneous substrate such as a sapphire substrate, a dicing process is not required for chip separation, leading to cost reduction. In addition, a single substrate made of a gallium nitride compound semiconductor has a cleavage property, and when a semiconductor laser is formed, the cleavage plane is preferably a resonator mirror. Further, by removing the substrate, the heat dissipation is improved, so that a long life can be expected.

[0023]

Although the manufacturing process of the gallium nitride-type compound semiconductor substrate in one Embodiment of this invention is shown below, it is not limited to this.

[0024]

In the present invention, the substrate may be a single crystal substrate capable of epitaxially growing a nitride semiconductor layer, and the size and thickness of the substrate are not particularly limited. As a specific example of this substrate, sapphire, spinel, silicon carbide (6H, 4H, 3C) on which a C-plane, R-plane, or A-plane is used as a main surface, and preferably a C-axis oriented nitride semiconductor layer is grown. ), Silicon, ZnS, ZnO, SiO2, GaAs, GaP, diamond, NdGaO3Other examples include nitride semiconductors. After laminating the gallium nitride compound semiconductor layer, the substrate such as sapphire may be removed. These substrates have a flat surface, but are not particularly limited as long as the gallium nitride compound semiconductor layer can be epitaxially grown. For example, fine roughness is formed by etching or the like on the back surface of the substrate. This roughening can simplify the removal of the substrate. Further, in order to alleviate the warpage, the substrate may have an unevenness, a slope, a staircase shape, etc., and an air bridge structure.

[0025]

In as a buffer layer at a low temperature of 800 ° C. or less on the substratexAlyGa1-xyA first gallium nitride compound semiconductor is grown through N (0 ≦ X <1, 0 ≦ Y <1, 0 ≦ X + Y <1) layers. This is because defects and cracks are suppressed by relaxing the lattice constant mismatch between the substrate and the gallium nitride compound semiconductor. Here, the low temperature is a temperature range of 700 ° C. or lower, preferably 450 ° C. to 650 ° C. If the buffer layer is grown at a temperature within this range, fine nuclei can be formed with good uniformity. If the buffer layer is grown at a temperature of 800 ° C. or higher, uniform nucleation is inhibited, and the crystal is then polycrystallized, so that the crystallinity is lowered. The film thickness is grown from 10 angstroms to 0.5 μm. Furthermore, the underlayer may have a two-layer structure as well as the buffer layer. This is because the second underlayer is grown on the buffer layer (first underlayer) at a high temperature of 950 ° C. or higher to form a flattened underlayer with a mirror surface. Accordingly, the generation of pits in the gallium nitride compound semiconductor grown in the subsequent process can be suppressed. This underlayer can be omitted depending on the substrate.

[0026]

Gallium nitride compound semiconductor

Next, after forming the

[0027]

The film thickness of the first gallium nitride compound semiconductor layer is 5 μm or more. Preferably, it is 15 μm or more. This is because threading dislocations cannot be bent over a wide range if the thickness of the first gallium nitride compound semiconductor layer is 5 μm or less. By growing the first gallium nitride compound semiconductor layer with this thickness, the direction in which threading dislocations extend after the first gallium nitride compound semiconductor layer is grown can be bent. Next, if the second gallium nitride compound semiconductor layer grown on the first gallium nitride compound semiconductor layer is grown to a thickness of 5 μm or more, preferably 15 μm or more, the second gallium nitride compound semiconductor layer By forming a loop between threading dislocations during growth, threading dislocations can be reduced.

[0028]

As a method of manufacturing a gallium nitride compound semiconductor substrate, a first gallium nitride compound semiconductor, a second gallium nitride compound semiconductor, and a second gallium nitride compound semiconductor are formed on a substrate by a vapor phase epitaxial growth (HVPE) method using a halogen transport method through an underlayer. The method for growing the is shown below. The halide vapor phase epitaxial growth method can grow a thick film in a short time, and is therefore effective for forming a thick film of a nitride semiconductor or forming a single substrate of a nitride semiconductor from which a different kind of substrate is peeled off.

The growth technique, growth process, and growth conditions used in the present invention are shown below.

[0029]

In the present invention, as a vapor phase growth means in the present invention, a halogen transport method in which a halide of a group III element and a compound containing a group V element (a compound containing nitrogen in the present invention) are reacted to perform vapor phase growth on a substrate. The phase growth (halogen-transport vapor phase epitaxy: HVPE) method is mentioned.

[0030]

The halogen gas includes HCl and the like, and is introduced from the halogen gas pipe together with the carrier gas. The halogen gas reacts with a metal such as Ga to generate a halide of a

[0031]

As a growth condition of the first gallium nitride compound semiconductor, the growth rate may be 5 μm / hour or more. The first gallium nitride compound semiconductor and the second gallium nitride compound semiconductor can have the same growth rate. Therefore, the distortion generated at the interface due to the difference in crystallinity caused by different growth rates can be alleviated. Here, the first gallium nitride compound semiconductor is preferably grown at normal pressure or slightly reduced pressure.

[0032]

Next, after a first gallium nitride compound semiconductor is grown, a second gallium nitride compound semiconductor is grown thereon under the following conditions.

[0033]

The second gallium nitride compound semiconductor is preferably grown at a temperature equal to or higher than that of the first gallium nitride compound semiconductor, and the substrate temperature is set to 900 ° C. or higher. However, if the temperature difference between the first gallium nitride compound semiconductor and the second gallium nitride compound semiconductor is large, it is preferable that the temperature difference is small because residual thermal distortion occurs at the growth layer interface. The thickness of the second gallium nitride compound semiconductor is not particularly limited as long as the uppermost surface is a mirror surface, and may be 15 μm or more. For this reason, the second gallium nitride compound semiconductor can be formed by MOCVD or another vapor deposition method as long as it is a vapor deposition method capable of growing to a thickness of about 15 μm. Furthermore, it is preferable to use the MOCVD method to control the uniformity of crystal nucleus density, orientation characteristics, size, and layer thickness.

[0034]

The gallium nitride compound semiconductor substrate obtained by the above growth method is a gallium nitride compound semiconductor substrate having a flat top surface and a wide range of low-defect portions serving as mirror surfaces. The element formed on the gallium nitride compound semiconductor substrate obtained by the present invention may be a light emitting element, a light receiving element, or an electronic device as long as it uses a gallium nitride compound semiconductor. FIG. 3 shows a semiconductor laser device in which electrodes are formed on the same surface as the light emitting device in the present embodiment. FIG. 4 shows a semiconductor laser device in which electrodes are formed as a counter electrode structure.

[0035]

The gallium nitride compound semiconductor substrate obtained as described above has a threading dislocation density of 1 × 10.8/ Cm2Or less, more preferably 1 × 107/ Cm2It is assumed that the second gallium nitride compound semiconductor layer is as follows.

[0036]

【Example】

Examples of the present invention will be described below.

[Example 1]

First, a sapphire substrate having a C-plane as the main surface was used as the

[0037]

Next, the underlayer was grown in a two-layer structure. First, the temperature was set to 510 ° C., hydrogen was used as the carrier gas, ammonia and trimethyl gallium were used as the source gas, and a buffer layer made of GaN was grown to a thickness of 200 Å. Next, a flat layer made of GaN and having a film thickness of 3 μm was formed on the buffer layer at a growth temperature of 1050 ° C. In this example, hydrogen was supplied at 20.5 L / min as a carrier gas during growth, ammonia was supplied at 5 L / min, and trimethylgallium was supplied at 25 cc / min as a source gas.

[0038]

After the base layer is grown on the substrate, it is set in an HVPE apparatus in order to grow the first gallium nitride compound semiconductor and the second gallium nitride compound semiconductor.

[0039]

First, Ga metal is prepared as a Ga source in a boat, and GaCl is generated by flowing HCl gas, which is a halogen gas, using nitrogen and / or hydrogen as a carrier gas. Nitrogen and / or hydrogen is used as a carrier gas and an ammonia gas as an N source is flowed to react GaCl and ammonia gas to form GaN in the substrate region. In addition, SiCl using nitrogen and / or hydrogen as a carrier gasFourThe first gallium nitride compound semiconductor made of Si-doped GaN is grown on the substrate. The temperature of the substrate region was set to 1030 ° C. with an electric furnace. The growth rate of the first gallium nitride compound semiconductor is 50 μm / hour, and the GaCl partial pressure is 1.25 × 10-3atm, NH3The partial pressure was 0.375 atm. SiCl4Partial pressure is 2.87 × 10-7Atm. The first gallium nitride compound semiconductor was grown to a thickness of 50 μm.

[0040]

Next, a second gallium nitride compound semiconductor was grown on the first gallium nitride compound semiconductor in a vapor phase epitaxial growth apparatus using a halogen transport method. As growth conditions at this time, SiCl4Partial pressure is 1.0 × 10-8A second gallium nitride compound semiconductor was grown at a growth rate of 50 μm / hour and a film thickness of 100 μm under the same growth conditions as those of the first gallium nitride compound semiconductor except that it was set to atm.

[0041]

The surface of the second gallium nitride compound semiconductor substrate obtained as described above is flat and mirror-like, and in SIMS analysis, the Si concentration is 2 × 10 2 for the first gallium nitride compound semiconductor layer.19/ Cm2The second gallium nitride compound semiconductor layer is 2 × 1018/ Cm2Met. Further, as shown in FIG. 2, according to CL observation, the threading dislocation density is 2 × 10.7cm-2Thus, a gallium nitride compound semiconductor substrate having a low defect can be provided.

[0042]

[Example 2]

A third gallium nitride compound semiconductor layer and a fourth gallium nitride compound semiconductor layer are grown on the gallium nitride compound semiconductor substrate obtained in Example 1 above. The third gallium nitride compound semiconductor layer has the same growth conditions as the first gallium nitride compound semiconductor layer, and the fourth gallium nitride compound semiconductor layer has the same growth conditions as the second gallium nitride compound semiconductor layer. The same shall apply.

[0043]

Since the gallium nitride compound semiconductor substrate obtained as described above becomes a low-dislocation substrate with a thick film grown, it can be a single substrate from which a heterogeneous substrate is removed.

[0044]

[Example 3]

The sapphire substrate is removed by grinding from the gallium nitride compound semiconductor substrate obtained in Example 1, and a single substrate of GaN is obtained. A laser element is formed on this single substrate.

[0045]

(N-type contact layer 102)

First, a single substrate of GaN is set in a reaction vessel of a MOCVD apparatus, TMG, TMA, ammonia, silane gas as impurity gas, and Si-doped Al at 1050 ° C.0.05Ga0.95An n-

[0046]

(Crack prevention layer 103)

Next, using TMG, TMI (trimethylindium), and ammonia, the temperature is set to 900 ° C. and In0.07Ga0.93A

[0047]

(N-type cladding layer 104)

Next, the temperature is set to 1050 ° C., TMA, TMG, and ammonia are used as source gases, and undoped Al0.05Ga0.95An A layer made of N is grown to a thickness of 25 mm, then TMA is stopped, silane gas is used as an impurity gas, and Si is 5 × 10 5.18/ Cm3A B layer made of doped GaN is grown to a thickness of 25 mm. This operation is repeated 200 times to obtain a laminated structure of the A layer and the B layer, and an n-type cladding layer made of a multilayer film (superlattice structure) having a total film thickness of 1 μm is grown.

[0048]

(N-type guide layer 105)

Next, at the same temperature, an n-

[0049]

(Active layer 106)

Next, the temperature is set to 900 ° C., TMI (trimethylindium), TMG, and ammonia are used as source gas, silane gas is used as impurity gas, and Si is 5 × 10 5.18/ Cm3Doped In0.05Ga0.95The barrier layer made of N is 140 mm thick, the silane gas is stopped, and undoped In0.13Ga0.87A well layer made of N is stacked in a thickness of 40 mm in the order of barrier layer / well layer / barrier layer / well layer, and finally, TMI, TMG and ammonia are used as the barrier layer, and undoped In0.05Ga0.95Grow N. The

[0050]

(P-type electron confinement layer 107)

Next, at the same temperature as the active layer, TMA, TMG, and ammonia are used as source gases, and Cp is used as an impurity gas.2Mg (cyclopentadienylmagnesium) is used and Mg is 1 × 1019/ Cm3Doped Al0.3Ga0.7A p-type electron confinement layer 107 made of N is grown to a thickness of 100 mm.

[0051]

(P-type guide layer 108)

Next, the temperature is set to 1050 ° C., TMG and ammonia are used as source gases, and a p-type guide layer 108 made of undoped GaN is grown to a thickness of 0.15 μm. This p-type guide layer may be doped with p-type impurities.

[0052]

(P-type cladding layer 109)

Next, undoped Al at 1050 ° C.0.05Ga0.95A layer of N is grown to a thickness of 25 mm, then TMA is stopped, Cp2Using Mg, a B layer made of Mg-doped GaN is grown to a thickness of 25 mm, and this is repeated 90 times to grow a p-

[0053]

(P-type contact layer 110)

Finally, at 1050 ° C., on the p-

After completion of the reaction, the wafer is annealed at 700 ° C. in a nitrogen atmosphere in the reaction vessel to further reduce the resistance of the p-type layer.

[0054]

After annealing, the single substrate made of GaN on which the nitride semiconductor laser elements are stacked is taken out of the reaction vessel, and SiO is deposited on the surface of the uppermost p-type contact layer.2A protective film made of CF and using RIE (reactive ion etching)4Etching with gas forms a ridge stripe as a striped waveguide region.

[0055]

Next, after forming the ridge stripe, Zr oxide (mainly ZrO2Is formed on the p-type guide layer 108 exposed by etching to a thickness of 0.5 μm.

[0056]

A p-type electrode is formed of Ni and Au on the p-type contact layer. Here, the thickness of the p-type electrode is set to 100 mm for Ni and 1300 mm for Au. In addition, an n-type electrode is formed of Ti and Al on the first gallium nitride compound semiconductor layer on the back surface so as to face the p-type electrode. Ti has a thickness of 200 mm and Al has a thickness of 8000 mm. The p-type electrode is formed in stripes on the ridge, and is formed in a direction parallel to and parallel to the n-type electrode similarly formed in stripes. Next, pad electrodes are formed on the p-type electrode and the n-type electrode, respectively. On the p-type electrode, RhO (rhodium oxide) / Pt / Au is formed as a p-type pad electrode with a film thickness of (3000Å-1500Å-6000Å). On the n-type electrode, Ni / Ti / Au is formed as an n-type pad electrode with a film thickness of (1000Å-1000Å-8000Å).

[0057]

After the electrode formation, the n-type electrode side is scribed and cleaved in a bar shape in the direction perpendicular to the ridge stripe, and the cleaved surface is made of SiO.2And TiO2A dielectric multilayer film is formed as a resonator mirror. Thereafter, the bar is cut into a laser chip in a direction parallel to the ridge stripe.

[0058]

The laser element obtained as described above has a threshold value of 2.8 kA / cm at room temperature.2, A continuous oscillation laser element having an oscillation wavelength of 405 nm at an output of 5 to 60 mW can be obtained. The element lifetime of the obtained laser element is 1000 to 30000 hours.

[0059]

[Example 4]

The sapphire substrate is removed by grinding from the gallium nitride compound semiconductor substrate obtained in Example 1, and a single substrate of GaN is obtained. A laser element is formed in which an n-type electrode and a p-type electrode are formed on the same surface of the single substrate.

[0060]

First, a GaN substrate is set in a reaction vessel of a MOCVD apparatus, and TMG (trimethylgallium), TMA (trimethylaluminum), ammonia is used as a nitride semiconductor at 1050 ° C., and Al is used.0.05Ga0.95An undoped n-type contact layer 101 made of N is grown to a thickness of 1 μm. This layer functions as a buffer layer between the nitride semiconductor substrate made of GaN and the semiconductor element including the n-type contact layer. However, this undoped n-type contact layer can be omitted.

[0061]

Next, after growing the undoped n-type contact layer, the n-

[0062]

Thereafter, a ridge stripe is formed with a ridge width of 1.7 μm. Next, the n-type contact layer is exposed by etching. Then, Zr oxide (mainly ZrO2Is formed on the p-type guide layer 108 exposed by etching with a film thickness of 0.5 μm or less. Thereafter, a p-type electrode is formed of Ni and Au on the p-type contact layer exposed in a stripe shape. Here, the film thickness of the p-type electrode is Ni (100 Å) and Au (1300 Å). Further, after forming the p-type electrode, an n-type electrode is formed on the exposed n-type contact layer. This n-type electrode is formed of Ti / Al with a film thickness (200Å-8000Å) in parallel on the same plane as the p-type electrode. Further, pad electrodes are formed on the p-type electrode and the n-type electrode, respectively. On the p-type electrode, RhO (rhodium oxide) / Pt / Au is formed as a p-type pad electrode with a film thickness of (3000Å-1500Å-6000Å). On the n-type electrode, Ni / Ti / Au is formed as an n-type pad electrode with a film thickness of (1000Å-1000Å-8000Å).

[0063]

After electrode formation, the back side of the substrate is scribed and cleaved in a bar shape in the direction perpendicular to the ridge stripe.2And TiO2A dielectric multilayer film is formed as a resonator mirror. Thereafter, the bar is cut into a laser chip in a direction parallel to the ridge stripe.

[0064]

The laser element obtained as described above has a threshold value of 2.8 kA / cm at room temperature.2, A continuous oscillation laser element having an oscillation wavelength of 405 nm at an output of 5 to 60 mW can be obtained. The element lifetime of the obtained laser element is 1000 to 30000 hours.

[0065]

[Example 5]

A laser element is formed on the gallium nitride compound semiconductor substrate with sapphire obtained in Example 1. First, an undoped n-type contact layer 101 is grown on the substrate. The substrate is set in a reaction vessel of an MOCVD apparatus, and TMG (trimethylgallium), TMA (trimethylaluminum), ammonia is used as a nitride semiconductor at 1050 ° C., and Al is used.0.05Ga0.95An undoped n-type contact layer 101 made of N is grown to a thickness of 1 μm. This layer functions as a buffer layer between the nitride semiconductor substrate made of GaN and the semiconductor element including the n-type contact layer.

[0066]

Next, element formation is performed in the following order under the same conditions as in Example 3.

On the substrate on which the undoped n-type contact layer is grown, n-

[0067]

Thereafter, a ridge stripe is formed with a ridge width of 1.7 μm. Next, the n-type contact layer is exposed by etching. Then, Zr oxide (mainly ZrO2Is formed on the p-type guide layer 108 exposed by etching with a film thickness of 0.5 μm or less. Thereafter, a p-type electrode is formed of Ni and Au on the p-type contact layer exposed in a stripe shape. Here, the film thickness of the p-type electrode is Ni (100 Å) and Au (1300 Å). Further, after forming the p-type electrode, an n-type electrode is formed on the exposed n-type contact layer. This n-type electrode is formed of Ti / Al with a film thickness (200Å-8000Å) in parallel on the same plane as the p-type electrode. Further, pad electrodes are formed on the p-type electrode and the n-type electrode, respectively. On the p-type electrode, RhO (rhodium oxide) / Pt / Au is formed as a p-type pad electrode with a film thickness of (3000Å-1500Å-6000Å). On the n-type electrode, Ni / Ti / Au is formed as an n-type pad electrode with a film thickness of (1000Å-1000Å-8000Å).

[0068]

After electrode formation, the back side of the substrate is diced, cleaved in a bar shape in the direction perpendicular to the ridge stripe, and the cleaved surface is SiO.2And TiO2A dielectric multilayer film is formed as a resonator mirror. Thereafter, the bar is cut into a laser chip in a direction parallel to the ridge stripe. The element lifetime of the laser element obtained as described above is 500 to 10,000 hours.

[0069]

[Example 6]

A laser element is formed on the gallium nitride compound semiconductor substrate with sapphire obtained in Example 1. First, an undoped n-type contact layer 101 is grown on the substrate. The substrate is set in a reaction vessel of an MOCVD apparatus, and TMG (trimethylgallium), TMA (trimethylaluminum), ammonia is used as a nitride semiconductor at 1050 ° C., and Al is used.0.05Ga0.95An undoped n-type contact layer 101 made of N is grown to a thickness of 1 μm. This layer functions as a buffer layer between the nitride semiconductor substrate made of GaN and the semiconductor element including the n-type contact layer.

[0070]

An n-

[0071]

Next, the sapphire substrate is removed by grinding, and a ridge stripe is formed with a ridge width of 1.7 μm. Next, the n-type contact layer is exposed by etching. Then, Zr oxide (mainly ZrO2Is formed on the p-type guide layer 108 exposed by etching with a film thickness of 0.5 μm or less. Thereafter, a p-type electrode is formed of Ni and Au on the p-type contact layer exposed in a stripe shape. Here, the film thickness of the p-type electrode is Ni (100 Å) and Au (1300 Å). Further, after forming the p-type electrode, an n-type electrode is formed on the exposed n-type contact layer. This n-type electrode is formed of Ti / Al with a film thickness (200Å-8000Å) in parallel on the same plane as the p-type electrode. Further, pad electrodes are formed on the p-type electrode and the n-type electrode, respectively. On the p-type electrode, RhO (rhodium oxide) / Pt / Au is formed as a p-type pad electrode with a film thickness of (3000Å-1500Å-6000Å). On the n-type electrode, Ni / Ti / Au is formed as an n-type pad electrode with a film thickness of (1000Å-1000Å-8000Å).

[0072]

After electrode formation, the back side of the substrate is scribed and cleaved in a bar shape in the direction perpendicular to the ridge stripe.2And TiO2A dielectric multilayer film is formed as a resonator mirror. Thereafter, the bar is cut into a laser chip in a direction parallel to the ridge stripe. The element lifetime of the laser element obtained as described above is 1000 to 30000 hours.

[0073]

[Example 7]

In Examples 3 to 6, the n-type electrode is Ti / Al (200 (-8000Å), the p-type electrode is Ni / Au (100Å-1500Å), the n-type pad electrode and the p-type pad electrode are Ni / Ti / Au The laser element is formed under the same conditions except that (1000 と す る -1000Å-8000Å). The lifetime characteristic of the laser element obtained here is 500 to 10,000 hours.

[0074]

[Example 8]

A sapphire substrate having a C surface as a main surface and an orientation flat surface as an A surface is used as the

[0075]

Next, by MOCVD, the temperature is 510 ° C., the carrier gas is hydrogen, the source gas is ammonia and TMG (trimethylgallium), and a buffer layer made of gallium nitride is formed on the opening of the protective film to a thickness of 200 Å. Grow in. Thereafter, the temperature is set to 1050 ° C. under a reduced pressure condition by MOCVD, and TMG, ammonia, silane gas, Cp are used as source gases.2Using Mg (cyclopentadienylmagnesium), a first nitride semiconductor layer made of gallium nitride is grown to a thickness of 10 μm. At this time, the first nitride semiconductor is

[0076]

Next, by isotropic etching, which is dry etching, at a temperature of 120 ° C., oxygen and CF are used as an etching gas.4Using SiO2Remove the protective film. Furthermore, from the side and top surfaces of the first nitride semiconductor grown in the lateral direction, the temperature is raised to 1050 ° C. by MOCVD at normal pressure, and TMG, ammonia, silane gas, Cp are used as source gases.2A second nitride semiconductor layer made of gallium nitride is grown to a thickness of 15 μm using Mg (cyclopentadienyl magnesium).

[0077]

In order to grow the first gallium nitride compound semiconductor and the second gallium nitride compound semiconductor on the substrate obtained as described above, they are set in the HVPE apparatus. Ga metal is prepared as a Ga source in a boat and GaCl is generated by flowing HCl gas, which is a halogen gas, using nitrogen and / or hydrogen as a carrier gas. Nitrogen and / or hydrogen is used as a carrier gas and an ammonia gas as an N source is flowed to react GaCl and ammonia gas to form GaN in the substrate region. In addition, SiCl using nitrogen and / or hydrogen as a carrier gasFourThe first gallium nitride compound semiconductor made of Si-doped GaN is grown on the substrate. The temperature of the substrate region is set to 1030 ° C. with an electric furnace. The growth rate of the first gallium nitride compound semiconductor is 50 μm / hour, and the GaCl partial pressure is 1.25 × 10-3atm, NH3The partial pressure is 0.375 atm. SiCl4Partial pressure is 2.87 × 10-7Atm. The first gallium nitride compound semiconductor is grown to a thickness of 50 μm.

[0078]

Next, a second gallium nitride compound semiconductor is grown on the first gallium nitride compound semiconductor in a vapor phase epitaxial growth apparatus using a halogen transport method. As growth conditions at this time, SiCl4Partial pressure is 1.0 × 10-8The second gallium nitride compound semiconductor is grown at a growth rate of 50 μm / hour and a film thickness of 100 μm under the same growth conditions as the first gallium nitride compound semiconductor except that it is atm.

[0079]

The surface of the second gallium nitride compound semiconductor substrate obtained as described above is flat and mirror-like, and the threading dislocation density is 1 × 10.7cm-2A low-defect gallium nitride compound semiconductor substrate can be provided as follows.

[0080]

[Example 9]

In the above embodiment, the growth rate of the first gallium nitride compound semiconductor is 50 μm / hour, and the second gallium nitride compound semiconductor is grown at a growth rate of 100 μm / hour, and the gallium nitride compound semiconductor substrate is used under the same conditions. Form. The surface of the second gallium nitride compound semiconductor substrate obtained as described above is flat and mirror-like, and the threading dislocation density is 1 × 10.8cm-2A low-defect gallium nitride compound semiconductor substrate can be provided as follows.

[0081]

【The invention's effect】

As described above, the present invention can provide a low-defect substrate in which crystal defects on the entire surface of the substrate are reduced, not a laterally grown substrate using a protective film or the like. Therefore, the device process can be simplified as compared with the substrate obtained by the ELO method, and a gallium nitride compound semiconductor substrate with improved mass production efficiency can be provided. Further, by removing the substrate, a single substrate of low resistance made of nitride can be obtained, so that heat dissipation is improved and the life characteristics of the nitride semiconductor device can be improved. Furthermore, a counter electrode structure is possible, which is advantageous for reducing the chip area.

[0082]

[Brief description of the drawings]

FIG. 1 is a schematic cross-sectional view of a nitride semiconductor showing an embodiment of the present invention.

FIG. 2 is a CL photograph in Example 1 of the present invention.

FIG. 3 is a schematic cross-sectional view of a nitride semiconductor laser device according to an embodiment of the present invention.

FIG. 4 is a schematic cross-sectional view of a nitride semiconductor laser device according to an embodiment of the present invention.

[Brief description of symbols]

1 ... Board

2 ... Underlayer

3... First gallium nitride compound semiconductor

4. Second gallium nitride compound semiconductor

101: Undoped n-type contact layer

102: n-type contact layer

103 ... Crack prevention layer

104 ... n-type cladding layer

105 ... n-type guide layer

106 ... Active layer

107 ... p-type electron confinement layer

108 ... p-type guide layer

109 ... p-type cladding layer

110 ... p-type contact layer

Claims (10)

基板上にSiのドーピング濃度が1×1019/cm3以上である第1の窒化ガリウム系化合物半導体層を形成する第1の工程と、

第1の工程後、該第1の窒化ガリウム系化合物半導体層上に、該第1の窒化ガリウム系化合物半導体層よりもSi濃度が小さく、ノンドープ、又はSiのドーピング濃度が1×1019/cm3以下である第2の窒化ガリウム系化合物半導体層を形成する第2の工程とを備え、

前記第1の工程において、前記第1の窒化ガリウム系化合物半導体層は、窒化ガリウム系化合物半導体の島であって、

前記第2の工程において、前記第2の窒化ガリウム系化合物半導体層は、前記窒化ガリウム系化合物半導体の島が成長し隣接する島同士が合体して形成されることを特徴とする窒化ガリウム系化合物半導体基板の製造方法。In a method of manufacturing a gallium nitride compound semiconductor substrate formed by growing a gallium nitride compound semiconductor layer on a substrate by a vapor deposition method,

Forming a first gallium nitride compound semiconductor layer having a Si doping concentration of 1 × 10 19 / cm 3 or more on a substrate;

After the first step, the Si concentration is lower than that of the first gallium nitride compound semiconductor layer on the first gallium nitride compound semiconductor layer, and the doping concentration of non-doped or Si is 1 × 10 19 / cm. A second step of forming a second gallium nitride compound semiconductor layer that is 3 or less ,

In the first step, the first gallium nitride compound semiconductor layer is an island of gallium nitride compound semiconductor,

In the second step, the second gallium nitride compound semiconductor layer is formed by growing islands of the gallium nitride compound semiconductor and combining adjacent islands with each other . A method for manufacturing a semiconductor substrate.

該第1の窒化ガリウム系化合物半導体層上に積層された、該第1の窒化ガリウム系化合物半導体層よりもSi濃度が小さく、ノンドープ、又はSiドーピング濃度が1×1019/cm3以下である第2の窒化ガリウム系化合物半導体層と、を備え、

前記第1の窒化ガリウム系化合物半導体層は、窒化ガリウム系化合物半導体の島として成長されたものであって、

前記第2の窒化ガリウム系化合物半導体層は、前記窒化ガリウム系化合物半導体の島が成長し隣接する島同士が合体して形成されたものであり、貫通転位密度が1×108/cm2以下であることを特徴とする窒化ガリウム系化合物半導体基板。A first gallium nitride compound semiconductor layer having a Si doping concentration of 1 × 10 19 / cm 3 or more;

The Si concentration is lower than that of the first gallium nitride compound semiconductor layer stacked on the first gallium nitride compound semiconductor layer, and the non-doped or Si doping concentration is 1 × 10 19 / cm 3 or less. A second gallium nitride compound semiconductor layer,

The first gallium nitride compound semiconductor layer is grown as an island of a gallium nitride compound semiconductor,

The second gallium nitride compound semiconductor layer is formed by growing islands of the gallium nitride compound semiconductor and combining adjacent islands with a threading dislocation density of 1 × 10 8 / cm 2 or less. A gallium nitride-based compound semiconductor substrate, wherein:

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001203956A JP4734786B2 (en) | 2001-07-04 | 2001-07-04 | Gallium nitride compound semiconductor substrate and manufacturing method thereof |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001203956A JP4734786B2 (en) | 2001-07-04 | 2001-07-04 | Gallium nitride compound semiconductor substrate and manufacturing method thereof |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003017420A JP2003017420A (en) | 2003-01-17 |

| JP2003017420A5 JP2003017420A5 (en) | 2008-08-21 |

| JP4734786B2 true JP4734786B2 (en) | 2011-07-27 |

Family

ID=19040506

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001203956A Expired - Fee Related JP4734786B2 (en) | 2001-07-04 | 2001-07-04 | Gallium nitride compound semiconductor substrate and manufacturing method thereof |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4734786B2 (en) |

Families Citing this family (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI252599B (en) * | 2004-04-27 | 2006-04-01 | Showa Denko Kk | N-type group III nitride semiconductor layered structure |

| TWI427828B (en) * | 2004-07-30 | 2014-02-21 | Sumitomo Chemical Co | Nitride compound semiconductor and process for producing the same |

| JP2006114886A (en) | 2004-09-14 | 2006-04-27 | Showa Denko Kk | N-type group iii nitride semiconductor lamination structure |

| DE102004050806A1 (en) * | 2004-10-16 | 2006-11-16 | Azzurro Semiconductors Ag | Process for the preparation of (Al, Ga) N single crystals |

| US7646027B2 (en) * | 2005-05-06 | 2010-01-12 | Showa Denko K.K. | Group III nitride semiconductor stacked structure |

| JP2006313771A (en) * | 2005-05-06 | 2006-11-16 | Showa Denko Kk | Epitaxial substrate for group iii nitride semiconductor element |

| JP2009126723A (en) * | 2007-11-20 | 2009-06-11 | Sumitomo Electric Ind Ltd | Growing method of group iii nitride semiconductor crystal, fabrication method of group iii nitride semiconductor crystal substrate, and group iii nitride semiconductor crystal substrate |

| JP5018423B2 (en) | 2007-11-20 | 2012-09-05 | 住友電気工業株式会社 | Group III nitride semiconductor crystal substrate and semiconductor device |

| JP5045388B2 (en) | 2007-11-20 | 2012-10-10 | 住友電気工業株式会社 | Group III nitride semiconductor crystal growth method and group III nitride semiconductor crystal substrate manufacturing method |

| KR101137911B1 (en) * | 2007-12-18 | 2012-05-03 | 삼성코닝정밀소재 주식회사 | Fabricating method for gallium nitride wafer |

| JP5287406B2 (en) | 2009-03-24 | 2013-09-11 | 豊田合成株式会社 | Method for producing group III nitride semiconductor |

| JP6005346B2 (en) * | 2011-08-12 | 2016-10-12 | シャープ株式会社 | Nitride semiconductor light emitting device and manufacturing method thereof |

| JP5117609B1 (en) | 2011-10-11 | 2013-01-16 | 株式会社東芝 | Nitride semiconductor wafer, nitride semiconductor device, and method for growing nitride semiconductor crystal |

| JP5705179B2 (en) * | 2012-08-15 | 2015-04-22 | 株式会社東芝 | Nitride semiconductor wafer, nitride semiconductor device, and method for growing nitride semiconductor crystal |

| JP5768027B2 (en) | 2012-09-20 | 2015-08-26 | 株式会社東芝 | Method for forming nitride semiconductor layer |

| JP5837642B2 (en) * | 2014-04-11 | 2015-12-24 | 株式会社東芝 | Semiconductor device and nitride semiconductor wafer |

| JP6376600B2 (en) * | 2015-03-20 | 2018-08-22 | 株式会社タムラ製作所 | Method for manufacturing crystal laminated structure |

| EP3576132A1 (en) * | 2018-05-28 | 2019-12-04 | IMEC vzw | A iii-n semiconductor structure and a method for forming a iii-n semiconductor structure |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002170776A (en) * | 2000-12-04 | 2002-06-14 | Inst Of Physical & Chemical Res | Low-dislocation buffer, its method of manufacture and device provided therewith |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|