JP4442181B2 - 半導体装置およびその製造方法 - Google Patents

半導体装置およびその製造方法 Download PDFInfo

- Publication number

- JP4442181B2 JP4442181B2 JP2003347797A JP2003347797A JP4442181B2 JP 4442181 B2 JP4442181 B2 JP 4442181B2 JP 2003347797 A JP2003347797 A JP 2003347797A JP 2003347797 A JP2003347797 A JP 2003347797A JP 4442181 B2 JP4442181 B2 JP 4442181B2

- Authority

- JP

- Japan

- Prior art keywords

- rewiring

- layer

- connection

- thin film

- circuit element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 239000004065 semiconductor Substances 0.000 title claims description 154

- 238000004519 manufacturing process Methods 0.000 title claims description 30

- 239000010410 layer Substances 0.000 claims description 208

- 239000010408 film Substances 0.000 claims description 149

- 239000010409 thin film Substances 0.000 claims description 94

- 239000000758 substrate Substances 0.000 claims description 46

- 239000000463 material Substances 0.000 claims description 30

- 238000000034 method Methods 0.000 claims description 24

- 229910000679 solder Inorganic materials 0.000 claims description 16

- 238000007789 sealing Methods 0.000 claims description 11

- 230000001939 inductive effect Effects 0.000 claims description 5

- 239000011229 interlayer Substances 0.000 claims 1

- 239000010953 base metal Substances 0.000 description 36

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 18

- 229910052710 silicon Inorganic materials 0.000 description 18

- 239000010703 silicon Substances 0.000 description 18

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 15

- 239000010949 copper Substances 0.000 description 15

- 229910052802 copper Inorganic materials 0.000 description 15

- 238000007747 plating Methods 0.000 description 15

- 229920005989 resin Polymers 0.000 description 15

- 239000011347 resin Substances 0.000 description 15

- 230000001681 protective effect Effects 0.000 description 13

- 239000012790 adhesive layer Substances 0.000 description 12

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 10

- 239000000945 filler Substances 0.000 description 8

- 229920001187 thermosetting polymer Polymers 0.000 description 8

- 230000015572 biosynthetic process Effects 0.000 description 7

- 239000003822 epoxy resin Substances 0.000 description 7

- 230000001965 increasing effect Effects 0.000 description 7

- 239000011810 insulating material Substances 0.000 description 7

- 229920000647 polyepoxide Polymers 0.000 description 7

- 229920001721 polyimide Polymers 0.000 description 6

- 239000003365 glass fiber Substances 0.000 description 5

- 239000009719 polyimide resin Substances 0.000 description 5

- 238000009713 electroplating Methods 0.000 description 4

- 238000010438 heat treatment Methods 0.000 description 4

- 238000003825 pressing Methods 0.000 description 4

- 239000000377 silicon dioxide Substances 0.000 description 4

- 239000004593 Epoxy Substances 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- 239000000835 fiber Substances 0.000 description 3

- 239000011159 matrix material Substances 0.000 description 3

- 239000012779 reinforcing material Substances 0.000 description 3

- 238000007650 screen-printing Methods 0.000 description 3

- 238000004528 spin coating Methods 0.000 description 3

- 238000004544 sputter deposition Methods 0.000 description 3

- 229910052782 aluminium Inorganic materials 0.000 description 2

- 229920006231 aramid fiber Polymers 0.000 description 2

- 239000000919 ceramic Substances 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 229920001955 polyphenylene ether Polymers 0.000 description 2

- 229910052814 silicon oxide Inorganic materials 0.000 description 2

- JYEUMXHLPRZUAT-UHFFFAOYSA-N 1,2,3-triazine Chemical compound C1=CN=NN=C1 JYEUMXHLPRZUAT-UHFFFAOYSA-N 0.000 description 1

- XQUPVDVFXZDTLT-UHFFFAOYSA-N 1-[4-[[4-(2,5-dioxopyrrol-1-yl)phenyl]methyl]phenyl]pyrrole-2,5-dione Chemical compound O=C1C=CC(=O)N1C(C=C1)=CC=C1CC1=CC=C(N2C(C=CC2=O)=O)C=C1 XQUPVDVFXZDTLT-UHFFFAOYSA-N 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- 238000007607 die coating method Methods 0.000 description 1

- 238000007772 electroless plating Methods 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 229920003192 poly(bis maleimide) Polymers 0.000 description 1

- 229920005992 thermoplastic resin Polymers 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L24/19—Manufacturing methods of high density interconnect preforms

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/12105—Bump connectors formed on an encapsulation of the semiconductor or solid-state body, e.g. bumps on chip-scale packages

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L2224/19—Manufacturing methods of high density interconnect preforms

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73267—Layer and HDI connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/91—Methods for connecting semiconductor or solid state bodies including different methods provided for in two or more of groups H01L2224/80 - H01L2224/90

- H01L2224/92—Specific sequence of method steps

- H01L2224/922—Connecting different surfaces of the semiconductor or solid-state body with connectors of different types

- H01L2224/9222—Sequential connecting processes

- H01L2224/92242—Sequential connecting processes the first connecting process involving a layer connector

- H01L2224/92244—Sequential connecting processes the first connecting process involving a layer connector the second connecting process involving a build-up interconnect

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/1901—Structure

- H01L2924/1904—Component type

- H01L2924/19042—Component type being an inductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/191—Disposition

- H01L2924/19101—Disposition of discrete passive components

- H01L2924/19102—Disposition of discrete passive components in a stacked assembly with the semiconductor or solid state device

- H01L2924/19104—Disposition of discrete passive components in a stacked assembly with the semiconductor or solid state device on the semiconductor or solid-state device, i.e. passive-on-chip

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Semiconductor Integrated Circuits (AREA)

Description

請求項2に記載の発明は、請求項1に記載の発明において、前記薄膜回路素子は前記再配線と同一の平面上に設けられ、前記接続配線は前記上層再配線と同一の平面上に設けられていることを特徴とするものである。

請求項3に記載の発明は、請求項1に記載の発明において、前記薄膜回路素子は前記上層再配線と同一の平面上に設けられ、前記接続配線は前記再配線と同一の平面上に設けられていることを特徴とするものである。

請求項4に記載の発明は、請求項1に記載の発明において、前記薄膜回路素子は、渦巻き状の形状を備える誘導素子であることを特徴とするものである。

請求項5に記載の発明は、請求項1に記載の発明において、前記上層絶縁膜上に、前記上層再配線の前記外部接続用の接続パッド部を除く部分を覆う最上層絶縁膜を有することを特徴とするものである。

請求項6に記載の発明は、請求項5に記載の発明において、前記上層再配線の接続パッド部上に半田ボールが設けられていることを特徴とするものである。

請求項7に記載の発明は、ベース板と、前記ベース板上に設けられ、且つ、複数の接続パッドを有する半導体基板および該半導体基板上に前記接続パッドに電気的に接続されて設けられた再配線を有する半導体構成体と、前記半導体構成体の周囲における前記ベース板上に設けられた絶縁層と、前記半導体構成体および前記絶縁層上に設けられた複数層の上層絶縁膜と、前記各上層絶縁膜上に層間で互いに接続され、且つ、前記半導体構成体の再配線の接続パッド部に接続されて設けられ、外部接続用の接続パッド部を備える複数層の上層再配線と、2つの端部を有し、前記複数層の上層再配線のうちの1層と同一の平面上に設けられ、一端部が前記接続パッドに電気的に接続された薄膜回路素子と、前記複数層の上層再配線のうちの他の1層と同一の平面上に設けられ、前記薄膜回路素子の他端部および前記接続パッドに電気的に接続された接続配線とを備えていることを特徴とする半導体装置。

請求項8に記載の発明は、請求項7に記載の発明において、前記接続配線は、前記複数層の上層絶縁膜における前記薄膜回路素子が設けられた層より上層の絶縁膜上に設けられていることを特徴とするものである。

請求項9に記載の発明は、請求項7に記載の発明において、前記接続配線は、前記複数層の上層絶縁膜における前記薄膜回路素子が設けられた層より下層の絶縁膜上に設けられていることを特徴とするものである。

請求項10に記載の発明は、請求項7に記載の発明において、前記薄膜回路素子は、渦巻き状の形状を備える誘導素子であることを特徴とするものである。

請求項11に記載の発明は、請求項7に記載の発明において、前記上層絶縁膜上に、前記上層再配線の前記外部接続用の接続パッド部を除く部分を覆う最上層絶縁膜を有することを特徴とするものである。

請求項12に記載の発明は、請求項5または11に記載の発明において、前記上層再配線の前記外部接続用の接続パッド部上に半田ボールが設けられていることを特徴とするものである。

請求項13に記載の発明は、請求項1または7に記載の発明において、前記半導体構成体は、前記再配線に接続された柱状電極と、前記柱状電極の上端面を除き、少なくとも前記半導体基板の上面を覆う封止膜と、を有するものであることを特徴とするものである。

請求項14に記載の発明は、ベース板と、前記ベース板上に設けられ、且つ、複数の接続パッドを有する半導体基板および該半導体基板上に前記接続パッドに電気的に接続されて設けられた再配線を有する半導体構成体と、前記半導体構成体の周囲における前記ベース板上に設けられた少なくとも1層の絶縁層と、前記半導体構成体および前記絶縁層上に設けられた上層絶縁膜と、前記上層絶縁膜の何れかの層上に前記半導体構成体の再配線の接続パッド部に電気的に接続されて設けられ、外部接続用の接続パッド部を備える少なくとも1層の上層再配線と、2つの端部を有し、前記再配線と前記上層再配線の何れかの層とのうちの一方と同一の平面上に設けられ、一端部が前記接続パッドに電気的に接続された薄膜回路素子と、前記再配線と前記上層再配線の何れかの層の他方と同一の平面上に設けられ、前記薄膜回路素子の他端部および前記接続パッドに電気的に接続された接続配線とを備えた半導体装置の製造方法において、前記再配線と前記上層再配線の何れかの層の一方と前記薄膜回路素子とを同一の材料によって同時に形成し、前記再配線と前記上層再配線の何れかの層の他方と前記接続配線とを同一の材料によって同時に形成することを特徴とするものである。

請求項15に記載の発明は、請求項14に記載の発明において、前記再配線と前記薄膜回路素子とを同一の平面上に形成し、前記上層再配線と前記接続配線とを同一の平面上に形成することを特徴とするものである。

請求項16に記載の発明は、請求項14に記載の発明において、前記上層再配線と前記薄膜回路素子とを同一の平面上に形成し、前記再配線と前記接続配線とを同一の平面上に形成することを特徴とするものである。

請求項17に記載の発明は、ベース板と、前記ベース板上に設けられ、且つ、複数の接続パッドを有する半導体基板および該半導体基板上に前記接続パッドに電気的に接続されて設けられた再配線を有する半導体構成体と、前記半導体構成体の周囲における前記ベース板上に設けられた絶縁層と、前記半導体構成体および前記絶縁層上に設けられた複数層の上層絶縁膜と、前記各上層絶縁膜上に層間で互いに接続され、且つ、前記半導体構成体の再配線の接続パッド部に接続されて設けられ、外部接続用の接続パッド部を備える複数層の上層再配線と、2つの端部を有し、前記複数層の上層再配線のうちの1層と同一の平面上に設けられ、一端部が前記接続パッドに電気的に接続された薄膜回路素子と、前記複数層の上層再配線のうちの他の1層と同一の平面上に設けられ、前記薄膜回路素子の他端部および前記接続パッドに電気的に接続された接続配線とを備えた半導体装置の製造方法において、前記複数層の上層再配線のうちの1層と前記薄膜回路素子とを同一の材料によって同時に形成し、前記複数層の上層再配線のうちの他の1層と前記接続配線とを同一の材料によって同時に形成することを特徴とするものである。

請求項18に記載の発明は、請求項17に記載の発明において、前記接続配線を、前記複数層の上層絶縁膜における前記薄膜回路素子が設けられた層より上層の絶縁膜上に形成することを特徴とするものである。

請求項19に記載の発明は、請求項17に記載の発明において、前記接続配線を、前記複数層の上層絶縁膜における前記薄膜回路素子が設けられた層より下層の絶縁膜上に形成することを特徴とするものである。

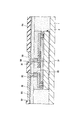

図1はこの発明の第1実施形態としての半導体装置の一部の平面図を示し、図2は図1のII−II線に沿う断面図を示し、図3は図1のIII−III線に沿う断面図を示す。この半導体装置は平面方形状のベース板1を備えている。ベース板1は、ガラス繊維、アラミド繊維、液晶繊維等にエポキシ系樹脂、ポリイミド系樹脂、BT(ビスマレイミド・トリアジン)樹脂、PPE(ポリフェニレンエーテル)等を含浸させたもの、シリコン、ガラス、セラミックス、樹脂単体等の絶縁材料、あるいは、銅やアルミニウム等の金属材料からなっている。

図18はこの発明の第2実施形態としての半導体装置の図2同様の断面図を示し、図19は同半導体装置の図3同様の断面図を示す。この半導体装置において、図2および図3に示す場合と大きく異なる点は、上層絶縁膜25の上面に薄膜コイル素子18を設けた点である。

上記第1実施形態では、図2および図3に示すように、上層絶縁膜25上に上層再配線28を1層だけ形成した場合について説明したが、これに限らず、2層以上としてもよく、例えば、図20および図21に示すこの発明の第3実施形態のように、2層としてもよい。この場合、図20は図2同様の断面図を示し、図21は図3同様の断面図を示す。

図22はこの発明の第4実施形態としての半導体装置の図20同様の断面図を示し、図23は同半導体装置の図21同様の断面図を示す。この半導体装置において、図20および図21に示す場合と大きく異なる点は、第2の上層絶縁膜70の上面に薄膜コイル素子66を設けた点である。

なお、上記各実施形態において、半導体構成体2は、外部接続用電極として、再配線14の接続パッド部上に設けられた柱状電極20を有するものとしたが、これに限定されるものではない。例えば、半導体構成体2は、外部接続用電極としての接続パッド部を有する再配線14のみを有するものであってもよい。また、ベース板1は、1枚の部材に限らず、絶縁膜および配線が交互に積層された多層印刷回路板としてもよい。

2 半導体構成体

3 接着層

4 シリコン基板

5、6 接続パッド

7 絶縁膜

9 保護膜

14 再配線

15 第1の接続配線

16 第2の接続配線

18 薄膜コイル素子

20、21、22 柱状電極

23 封止膜

24 絶縁層

25 上層絶縁膜

28 上層再配線

29 第3の接続配線

33 オーバーコート膜

35 半田ボール

Claims (19)

- ベース板と、

前記ベース板上に設けられ、且つ、複数の接続パッドを有する半導体基板および該半導体基板上に前記接続パッドに電気的に接続されて設けられた再配線を有する半導体構成体と、

前記半導体構成体の周囲における前記ベース板上に設けられた絶縁層と、

前記半導体構成体および前記絶縁層上に設けられた少なくとも1層の上層絶縁膜と、

前記上層絶縁膜の何れかの層上に前記半導体構成体の再配線の接続パッド部に電気的に接続されて設けられ、外部接続用の接続パッド部を備える少なくとも1層の上層再配線と、

2つの端部を有し、前記再配線と前記上層再配線の何れかの層の一方と同一の平面上に設けられ、一端部が前記接続パッドに電気的に接続された薄膜回路素子と、

前記再配線と前記上層再配線の何れかの層の他方と同一の平面上に設けられ、前記薄膜回路素子の他端部および前記接続パッドに電気的に接続された接続配線と、

を備えていることを特徴とする半導体装置。 - 請求項1に記載の発明において、前記薄膜回路素子は前記再配線と同一の平面上に設けられ、前記接続配線は前記上層再配線と同一の平面上に設けられていることを特徴とする半導体装置。

- 請求項1に記載の発明において、前記薄膜回路素子は前記上層再配線と同一の平面上に設けられ、前記接続配線は前記再配線と同一の平面上に設けられていることを特徴とする半導体装置。

- 請求項1に記載の発明において、前記薄膜回路素子は、渦巻き状の形状を備える誘導素子であることを特徴とする半導体装置。

- 請求項1に記載の発明において、前記上層絶縁膜上に、前記上層再配線の前記外部接続用の接続パッド部を除く部分を覆う最上層絶縁膜を有することを特徴とする半導体装置。

- 請求項5に記載の発明において、前記外部接続用の接続パッド部上に半田ボールが設けられていることを特徴とする半導体装置。

- ベース板と、

前記ベース板上に設けられ、且つ、複数の接続パッドを有する半導体基板および該半導体基板上に前記接続パッドに電気的に接続されて設けられた再配線を有する半導体構成体と、

前記半導体構成体の周囲における前記ベース板上に設けられた絶縁層と、

前記半導体構成体および前記絶縁層上に設けられた複数層の上層絶縁膜と、

前記各上層絶縁膜上に層間で互いに接続され、且つ、前記半導体構成体の再配線の接続パッド部に接続されて設けられ、外部接続用の接続パッド部を備える複数層の上層再配線と、

2つの端部を有し、前記複数層の上層再配線のうちの1層と同一の平面上に設けられ、一端部が前記接続パッドに電気的に接続された薄膜回路素子と、

前記複数層の上層再配線のうちの他の1層と同一の平面上に設けられ、前記薄膜回路素子の他端部および前記接続パッドに電気的に接続された接続配線と、

を備えていることを特徴とする半導体装置。 - 請求項7に記載の発明において、前記接続配線は、前記複数層の上層絶縁膜における前記薄膜回路素子が設けられた層より上層の絶縁膜上に設けられていることを特徴とする半導体装置。

- 請求項7に記載の発明において、前記接続配線は、前記複数層の上層絶縁膜における前記薄膜回路素子が設けられた層より下層の絶縁膜上に設けられていることを特徴とする半導体装置。

- 請求項7に記載の発明において、前記薄膜回路素子は、渦巻き状の形状を備える誘導素子であることを特徴とする半導体装置。

- 請求項7に記載の発明において、前記上層絶縁膜上に、前記上層再配線の前記外部接続用の接続パッド部を除く部分を覆う最上層絶縁膜を有することを特徴とする半導体装置。

- 請求項5または11に記載の発明において、前記上層再配線の前記外部接続用の接続パッド部上に半田ボールが設けられていることを特徴とする半導体装置。

- 請求項1または7に記載の発明において、前記半導体構成体は、前記再配線に接続された柱状電極と、該柱状電極の上端面を除き、少なくとも前記半導体基板の上面を覆う封止膜と、を有するものであることを特徴とする半導体装置。

- ベース板と、前記ベース板上に設けられ、且つ、複数の接続パッドを有する半導体基板および該半導体基板上に前記接続パッドに電気的に接続されて設けられた再配線を有する半導体構成体と、前記半導体構成体の周囲における前記ベース板上に設けられた少なくとも1層の絶縁層と、前記半導体構成体および前記絶縁層上に設けられた上層絶縁膜と、前記上層絶縁膜の何れかの層上に前記半導体構成体の再配線の接続パッド部に電気的に接続されて設けられ、外部接続用の接続パッド部を備える少なくとも1層の上層再配線と、2つの端部を有し、前記再配線と前記上層再配線の何れかの層とのうちの一方と同一の平面上に設けられ、一端部が前記接続パッドに電気的に接続された薄膜回路素子と、前記再配線と前記上層再配線の何れかの層の他方と同一の平面上に設けられ、前記薄膜回路素子の他端部および前記接続パッドに電気的に接続された接続配線とを備えた半導体装置の製造方法において、

前記再配線と前記上層再配線の何れかの層の一方と前記薄膜回路素子とを同一の材料によって同時に形成し、

前記再配線と前記上層再配線の何れかの層の他方と前記接続配線とを同一の材料によって同時に形成することを特徴とする半導体装置の製造方法。 - 請求項14に記載の発明において、前記再配線と前記薄膜回路素子とを同一の平面上に形成し、前記上層再配線と前記接続配線とを同一の平面上に形成することを特徴とする半導体装置の製造方法。

- 請求項14に記載の発明において、前記上層再配線と前記薄膜回路素子とを同一の平面上に形成し、前記再配線と前記接続配線とを同一の平面上に形成することを特徴とする半導体装置の製造方法。

- ベース板と、前記ベース板上に設けられ、且つ、複数の接続パッドを有する半導体基板および該半導体基板上に前記接続パッドに電気的に接続されて設けられた再配線を有する半導体構成体と、前記半導体構成体の周囲における前記ベース板上に設けられた絶縁層と、前記半導体構成体および前記絶縁層上に設けられた複数層の上層絶縁膜と、前記各上層絶縁膜上に層間で互いに接続され、且つ、前記半導体構成体の再配線の接続パッド部に接続されて設けられ、外部接続用の接続パッド部を備える複数層の上層再配線と、2つの端部を有し、前記複数層の上層再配線のうちの1層と同一の平面上に設けられ、一端部が前記接続パッドに電気的に接続された薄膜回路素子と、前記複数層の上層再配線のうちの他の1層と同一の平面上に設けられ、前記薄膜回路素子の他端部および前記接続パッドに電気的に接続された接続配線とを備えた半導体装置の製造方法において、

前記複数層の上層再配線のうちの1層と前記薄膜回路素子とを同一の材料によって同時に形成し、

前記複数層の上層再配線のうちの他の1層と前記接続配線とを同一の材料によって同時に形成することを特徴とする半導体装置の製造方法。 - 請求項17に記載の発明において、前記接続配線を、前記複数層の上層絶縁膜における前記薄膜回路素子が設けられた層より上層の絶縁膜上に形成することを特徴とする半導体装置の製造方法。

- 請求項17に記載の発明において、前記接続配線を、前記複数層の上層絶縁膜における前記薄膜回路素子が設けられた層より下層の絶縁膜上に形成することを特徴とする半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003347797A JP4442181B2 (ja) | 2003-10-07 | 2003-10-07 | 半導体装置およびその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003347797A JP4442181B2 (ja) | 2003-10-07 | 2003-10-07 | 半導体装置およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005116714A JP2005116714A (ja) | 2005-04-28 |

| JP4442181B2 true JP4442181B2 (ja) | 2010-03-31 |

Family

ID=34540199

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003347797A Expired - Lifetime JP4442181B2 (ja) | 2003-10-07 | 2003-10-07 | 半導体装置およびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4442181B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7468545B2 (en) * | 2005-05-06 | 2008-12-23 | Megica Corporation | Post passivation structure for a semiconductor device and packaging process for same |

| JP4731984B2 (ja) * | 2005-05-10 | 2011-07-27 | 株式会社フジクラ | 半導体装置およびその製造方法 |

| US7582556B2 (en) | 2005-06-24 | 2009-09-01 | Megica Corporation | Circuitry component and method for forming the same |

| JP2008210933A (ja) * | 2007-02-26 | 2008-09-11 | Casio Comput Co Ltd | 半導体装置 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3177954B2 (ja) * | 1997-11-20 | 2001-06-18 | 日本電気株式会社 | 半導体装置およびその製造方法 |

| JPH11233678A (ja) * | 1998-02-16 | 1999-08-27 | Sumitomo Metal Electronics Devices Inc | Icパッケージの製造方法 |

| JP2002016173A (ja) * | 2000-06-30 | 2002-01-18 | Mitsubishi Electric Corp | 半導体装置 |

| JP3938759B2 (ja) * | 2002-05-31 | 2007-06-27 | 富士通株式会社 | 半導体装置及び半導体装置の製造方法 |

| JP4010236B2 (ja) * | 2002-12-04 | 2007-11-21 | ソニー株式会社 | 半導体装置および半導体装置の製造方法 |

-

2003

- 2003-10-07 JP JP2003347797A patent/JP4442181B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005116714A (ja) | 2005-04-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3945483B2 (ja) | 半導体装置の製造方法 | |

| KR100595891B1 (ko) | 반도체장치 | |

| JP4012496B2 (ja) | 半導体装置 | |

| US7550833B2 (en) | Semiconductor device having a second semiconductor construction mounted on a first semiconductor construction and a manufacturing method thereof | |

| JP3925809B2 (ja) | 半導体装置およびその製造方法 | |

| JP4851794B2 (ja) | 半導体装置 | |

| TW200527647A (en) | A semiconductor device and its fabrication method | |

| JP4285707B2 (ja) | 半導体装置 | |

| JP4379693B2 (ja) | 半導体装置およびその製造方法 | |

| JP3925503B2 (ja) | 半導体装置 | |

| JP4438389B2 (ja) | 半導体装置の製造方法 | |

| JP4513302B2 (ja) | 半導体装置 | |

| JP4316624B2 (ja) | 半導体装置 | |

| JP4442181B2 (ja) | 半導体装置およびその製造方法 | |

| JP2009246404A (ja) | 半導体装置の製造方法 | |

| JP4316622B2 (ja) | 半導体装置の製造方法 | |

| JP4316623B2 (ja) | 半導体装置の製造方法 | |

| JP4321758B2 (ja) | 半導体装置 | |

| JP5880036B2 (ja) | 電子部品内蔵基板及びその製造方法と積層型電子部品内蔵基板 | |

| JP5097006B2 (ja) | プリント配線基板及びその製造方法 | |

| JP4461801B2 (ja) | 半導体装置およびその製造方法 | |

| JP2004221418A (ja) | 半導体装置およびその製造方法 | |

| JP4209341B2 (ja) | 半導体装置およびその製造方法 | |

| JP4561079B2 (ja) | 半導体装置の製造方法 | |

| JP3955059B2 (ja) | 半導体装置およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20060209 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20060404 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061005 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20080519 |

|

| TRDD | Decision of grant or rejection written | ||

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20091203 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20091222 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100104 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4442181 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130122 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130122 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130122 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130122 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140122 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |