JP3710081B2 - Plasma processing equipment - Google Patents

Plasma processing equipment Download PDFInfo

- Publication number

- JP3710081B2 JP3710081B2 JP34080698A JP34080698A JP3710081B2 JP 3710081 B2 JP3710081 B2 JP 3710081B2 JP 34080698 A JP34080698 A JP 34080698A JP 34080698 A JP34080698 A JP 34080698A JP 3710081 B2 JP3710081 B2 JP 3710081B2

- Authority

- JP

- Japan

- Prior art keywords

- chamber

- processing apparatus

- susceptor

- plasma processing

- plasma

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Chemical Vapour Deposition (AREA)

- Drying Of Semiconductors (AREA)

- Plasma Technology (AREA)

Description

【0001】

【産業上の利用分野】

本発明はプラズマ処理装置に係る。

【0002】

【従来の技術】

従来、プラズマ処理装置としては図12に示すものが知られている。

【0003】

従来のプラズマ処理装置は、高周波電源1とプラズマ励起電極4との間に整合回路が介在している。整合回路はこれら高周波電源1とプラズマ励起電極4との間のインピーダンスの整合を得るための回路である。

【0004】

高周波電源1からの高周波電力は整合回路を通して給電板3によりプラズマ励起電極4へ供給される。

【0005】

これら整合回路および給電板3は導電体からなるハウジング21により形成されるマッチングボックス2内に収納されている。

【0006】

プラズマ励起電極(カソード電極)4の下には、多数の孔7が形成されているシャワープレート5が設けられており、プラズマ励起電極4とシャワープレート5とで空間6が形成されている。この空間6にはガス導入管17が設けられている。ガス導入管17から導入されたガスは、シャワープレート5の孔7を介してチャンバ壁10により形成されたチャンバ室60内に供給される。なお、9はチャンバ壁10とプラズマ励起電極(カソード電極)4とを絶縁する絶縁体である。また、排気系の図示は省略してある。

【0007】

一方、チャンバ室60内には基板16を載置しプラズマ励起電極ともなるウエハサセプタ(サセプタ電極)8が設けられておりその周囲にはサセプタシールド12が設けられている。ウエハサセプタ8及びサセプタシールド12はベーローズ11により上下動可能となっており、プラズマ励起電極4,8間の距離の調整ができる。

【0008】

ウエハサセプタ8には、マッチングボックス14内に収納された整合回路を介して第2の高周波電源15が接続されている。

なお、チャンバとサセプタシールド12とは直流的に同電位となっている。

【0009】

図14に他の従来のプラズマ処理装置を示す。

図12に示すプラズマ処理装置はいわゆる二周波励起タイプのプラズマ処理装置であったが、図14に示すプラズマ処理装置は一周波励起タイプのプラズマ処理装置である。すなわち、カソード電極4にのみ高周波電力を供給しており、サセプタ電極8は接地されている。図12で示される高周波電源15とマッチングボックス14がない。また、サセプタ電極8とチャンバ壁10とは直流的に同電位となっている。

【0010】

図15に他の従来のプラズマ処理装置を示す。

図15に示すプラズマ処理装置ではシャワープレートは使用されておらず、プラズマ励起電極であるカソード電極4とウエハサセプタ8とが直接対向している。カソード電極4の裏面周囲にはシールド20が設けられている。他の点は図12に示すプラズマ処理装置と同様の構成を有している。

【0011】

また、図16に他の従来のプラズマ処理装置を示す。

図15に示すプラズマ処理装置はいわゆる二周波励起タイプのプラズマ処理装置であったが、図16に示すプラズマ処理装置は一周波励起タイプのプラズマ処理装置である。すなわち、カソード電極4にのみ高周波電力を供給しており、サセプタ電極8は接地されている。図15で示される高周波電源15とマッチングボックス14がない。また、サセプタ電極8とチャンバ壁10とは直流的に同電位となっている。

【0012】

しかし、従来のプラズマ処理装置を詳細に調べたところ、電力消費効率(高周波電源1からプラズマ励起電極4に投入した電力に対してプラズマ中で消費された電力の割合)は必ずしも良好ではなく、特に高周波電源から供給される周波数が高くなるほど電力消費効率の低下が顕著である。また、基板サイズが大きくなるほどその低下が顕著であることも本発明者は見いだした。

【0013】

また、図12、図14、図15、図16に示す従来のプラズマ処理装置では、サセプタインピーダンス(サセプタ−チャンバ間のインピーダンス)の値が高く、また、高周波電源1,15から供給する高周波の周波数が高くなるにつれそのインピーダンスはより一層大きくなる。すなわち、これらインピーダンスには周波数依存性が存在する。そのため、高周波電源1から供給する高周波の周波数が高くなるにつれて、サセプタインピーダンスと直列な関係にあるプラズマを流れる高周波電流が小さくなり電力消費効率の低下が顕著となる。

【0014】

なお、電力消費効率は、次のようにして調査した。

(1)プラズマ処理装置のチャンバ壁を集中定数回路からなる等価回路に置き換える。

(2)インピーダンスアナライザを用いてチャンバの構成部品のインピーダンスを測定する事によりそれぞれの回路の定数を決定する。

(3)放電中のチャンバ全体のインピーダンスが入力側にダミーロード50Ωを付けたマッチングボックスのインピーダンスと複素共役の関係にあることを利用し、放電中のチャンバ全体のインピーダンスを知る。

(4)プラズマ空間を抵抗Rと容量Cとの直列回路とみなし、それぞれの定数を(2)、(3)で得られた値から算出する。

(5)以上の方法で得られた放電中のチャンバの等価回路モデルに基づいて、回路計算を実施し、電力消費効率を導出する。

【0015】

このように、従来のプラズマ処理装置においては電力消費効率が低いため成膜速度が遅く、また、たとえば絶縁膜の成膜の場合にあってはより絶縁耐圧の高い絶縁膜の形成が困難であるという問題点を有している。

【0016】

本発明者は、電力消費効率が低い原因を鋭意探求した。その結果、電力消費効率が低い原因は次に述べることにあるとの知見を得た。

【0017】

すなわち、まず、図12に示す従来のプラズマ処理装置のサセプタ電極8側で説明すると、図12のサセプタ電極8部近傍を拡大した図13の矢印に示すように、高周波電力は、高周波電源1から同軸ケーブル、整合回路、給電板3、プラズマ励起電極(カソード電極)4に供給される。一方、高周波電流の経路を考えた場合、電流はこれらを介してプラズマ空間(チャンバ室60)を経由した後、さらにもう一方の電極(サセプタ電極)8、シールド12の垂直部、ベローズ11、チャンバ壁10の底部10b、チャンバ壁10の側壁10aを通る。その後、マッチングボックス2のハウジングを通り、高周波電源1のアースに戻る。

【0018】

図14に示すプラズマ処理装置においても、高周波電源1からの高周波電力は、高周波電源1から同軸ケーブル、整合回路、給電板3を介してカソード電極4に供給される。一方、高周波電流の経路を考えた場合、電流はこれらを介してプラズマ空間を経由した後、さらにもう一方の電極(サセプタ電極)8、シャフト13、チャンバ壁10の底部10b、チャンバ壁10の側壁10sを通る。その後、マッチングボックス2のハウジングを通り、高周波電源1のアースに戻る。

【0019】

しかるに、図12、図14に示す従来のプラズマ処理装置においては、サセプタ電極8のシャフト13(あるいはシールド12の垂直部)とチャンバ側壁10aとは平行であるため、往路の電流と復路の電流とがシールド12の垂直部とチャンバ側壁10sとで平行になってしまい相互インダクタンスの増大をもたらしてしまう。その結果、電力消費効率の低下をもたらし、ひいては、成膜速度の低下あるいは膜質の低下をまねいてしまうというものである。特にかかる相互インダクタンスの影響は、基板16が大型になるほど、ひいては給電板3とマッチングボックス2のハウジングとの距離が大きくなるほど大であり、基板が80〜100cmになると顕著にあらわれる。

【0020】

なお、かかる課題を含む知見は本発明者が初めて見いだしたものである。

【0021】

【課題を解決するための手段】

本発明のプラズマ処理装置は、プラズマ処理を行うチャンバ室内に、プラズマ励起用電力が供給されるプラズマ励起電極と、該プラズマ励起電極に対向し、前記チャンバ室のチャンバ壁と直流的に同電位であるサセプタ電極とを備え、該サセプタ電極は、前記プラズマ励起用電力による高周波電流がプラズマ空間を経由した後流入する電極であり、前記チャンバ壁と前記サセプタ電極とを交流的に短絡していることを特徴とする。

【0022】

ここで、前記チャンバ壁と、前記サセプタ電極とを導通されていることが好ましい。

【0023】

また、前記サセプタ電極と前記チャンバ壁と短絡させている点は、前記チャンバ側壁から水平方向に500mm未満の範囲にあることが好ましい。さらに、前記サセプタ電極と前記チャンバ壁とを前記チャンバ側で短絡させている点が前記チャンバ側壁から水平方向に500mm未満の範囲にあることが好ましい。さらにまた、前記チャンバ壁と前記サセプタ電極とを複数の点で短絡させていることが好ましい。

【0024】

ここで、前記チャンバ壁と前記サセプタ電極とを短絡させる短絡点が前記電極の中心に対して略点対称であることが好ましい。また、前記チャンバ壁と前記サセプタ電極とを短絡させる短絡点が前記シールド中心に対して略点対称であることが好ましい。

【0025】

さらに、本発明のプラズマ処理装置は、プラズマ処理を行うチャンバ室内に、プラズマ励起用電力が供給されるプラズマ励起電極と、該プラズマ励起電極と対向して設けられ、前記プラズマ励起用電力による高周波電流がプラズマ空間を経由した後流入するサセプタ電極と、該サセプタ電極の周囲に設けられた、前記チャンバ室のチャンバ壁と直流的に同電位のサセプタシールドと、を備え、前記チャンバ壁と前記サセプタシールドとを交流的に短絡していることを特徴とする。

【0026】

ここで前記チャンバ壁と前記サセプタシールドとを導通させていることが好ましく。さらに前記サセプタシールドと前記チャンバ壁とを短絡させていることが好ましい。

また、本発明において前記チャンバ側の点は、前記チャンバ室の側壁から水平方向に500mm未満の範囲にあることが好ましく、前記サセプタシールドと前記チャンバ壁とを短絡させているそれぞれの点が前記チャンバ室の側壁から水平方向に500mm未満の範囲にあることが好ましい。

さらにまた、本発明において前記チャンバ壁と前記サセプタシールドとを複数の点で短絡させていることが好ましく、前記チャンバ壁と前記サセプタシールドとを短絡させる短絡点が前記サセプタ電極の中心に対して略点対称であることが好ましい。

【0027】

【発明の実施の形態】

(プラズマ処理装置の第1の実施の形態)

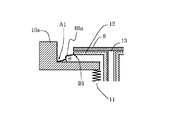

図1に、本発明のプラズマ処理装置の第1の実施の形態を示す。このプラズマ処理装置は、チャンバ壁10と、チャンバと直流的に同電位である電極のシールド12との間を金属プレート80a,80bにより交流的に短絡している。

【0028】

図2にウエハサセプタ電極8側の詳細を示す。

本例では、チャンバ壁10とシールド12との交流的な短絡は2箇所で行っている。この短絡は弾力性を有しバネ体である金属プレート80a,80bをその一端をチャンバ壁10の底部10bに短絡点B1,B2において接続し、他端をシールド12に短絡点A1,A2において接続することにより行っている。短絡点B1,B2は、シールド12の最外周近傍に配置してあり、チャンバ壁10の側壁10sとの距離をできるだけ小さくしている。すなわち、チャンバ壁10の側壁10sから最近接点あるいはその近傍に短絡点B1,B2を設定することが好ましい。

【0029】

金属プレートの材質としては真空中での放出ガス量が少ないなどの観点からインコネル625(商品名)を用いることが好ましく、本例では、20mm×40cm×0.3mmの寸法の金属プレートを用いた。

【0030】

なお、本例では板形状のものを用いたが、メッシュ状のものを用いることも好ましい。メッシュの形状としては図3(a)に示す亀の子状や格子状のものが好ましい。このメッシュ状金属プレートはサセプタシールド12の周縁に沿わせて円筒状配置することが好ましい。図3(b)は図1のIII−III断面図であり、金属プレート80a,80bに代えて図3(a)に示す亀の子状メッシュの金属プレートを配置した図である。金属プレートがメッシュ状であるためチャンバ室内の真空排気が金属プレートのため妨げられることがなく、また、高周波電流の流れを均一にすることができる。また、弾力性に富みベローズの上下動に追従しやすい。

【0031】

なお、本例ではシールド12における短絡点A1,A2は短絡点B1,B2のほぼ直上に設定してある。

【0032】

本例のプラズマ処理装置においては、高周波電力は、高周波電源1から同軸ケーブル、整合回路、給電板3、プラズマ励起電極(カソード電極)4に供給される。この点は従来のプラズマ処理装置と同様である。一方、高周波電流の経路を考えた場合、電流はこれらを介してプラズマ空間(チャンバ室60)を経由した後、さらにもう一方の電極(サセプタ電極)8、シールド12の水平部、金属プレート80a,80b、チャンバ壁10の底部10b、チャンバ壁10の側壁10aを通る。その後、マッチングボックス2のハウジングを通り、高周波電源1のアースに戻る。

【0033】

従来のプラズマ処理装置においては、高周波電流はシールド12の垂直部を通っていた。基板16のサイズが大きくなるとシールド12とチャンバ側壁との間の距離が必然的に大きくなる。シールド12とチャンバ側壁10sとをそれぞれ流れる高周波電流同士により生じる相互インダクタンスはその間の距離が大きくなると大きくなり電力消費効率は低下するため、従来のプラズマ処理装置では大きなサイズの基板に対しては電力消費効率は低くならざるを得なかった。

【0034】

しかるに、本例に係るプラズマ処理装置では、高周波電流は、シールド12の垂直部よりもチャンバ側壁10sに近い金属プレート80a,80bを通るため相互インダクタンスの発生を著しく低減させ電力消費効率を著しく高めることができる。

【0035】

図1に示す装置と図12に示す装置を用いて窒化ケイ素からなる絶縁膜を成膜し、その際の電力消費効率を測定したところ、図1に示す装置の場合は、図12に示す装置の場合に比べ電力消費効率は2倍であった。

【0036】

また、サセプタインピーダンスの測定を行った。その結果を図4に示す。(a)が図12に示すプラズマ処理装置の場合であり(従来例)、(b)が図1に示すプラズマ処理装置の場合である。

【0037】

図4からわかるように本例に係るプラズマ処理装置ではサセプタインピーダンスは従来例に係るプラズマ処理装置より極めて小さくまた、周波数依存性が少ない。

【0038】

(プラズマ処理装置の第2の実施の形態)

図5に第2の実施の形態に係るプラズマ処理装置を示す。

本例は、図14に示すプラズマ処理装置、すなわち、一周波励起タイプのプラズマ処理装置に金属プレート80a,80bを設けた例である。

【0039】

すなわち、チャンバ壁10と、チャンバと直流的に同電位である電極(サセプタ電極8との間を金属プレート80a,80bにより交流的に短絡している。

他の点は第1の実施の形態と同様である。

【0040】

(プラズマ処理装置の第3の実施の形態)

本例では、金属プレートを設ける位置の影響を調べた。

【0041】

すなわち、図1に示す装置において、チャンバ壁10における金属プレートの短絡点B1,B2は、シールド12における金属プレートの短絡点A1,A2の真下とし、短絡点からチャンバ側壁10aまでの距離xを変化させ相互インダクタンスの大きさを調査した。

【0042】

その結果を図6に示す。

図6からわかるように、距離xが500mmを境としてインダクタンスは減少し始め、350mm近辺から減少率が大きくなり、200mm近辺から減少率はより急激に大きくなる。

【0043】

従って、短絡点の位置はチャンバ側壁から500mm未満とすることが好ましく、350mm未満とすることがより好ましく、200mm未満とすることがさらに好ましい。最も好ましいのは、チャンバ側壁10aから最短距離にある点あるいはその近傍である。

【0044】

(プラズマ処理装置の第4の実施の形態)

本例では金属プレートの配置数の影響を調べた。

【0045】

すなわち、金属プレートの配置数を変え、インダクタンスの大きさを測定した。なお、金属プレートはシールドの中心に関して略点対称に配置した。

その結果を図7に示す。

【0046】

図7に示すように、金属プレートを配置することによりインダクタンスは減少し始めるが4個配置した場合も8個配置した場合も減少率はほぼ同じである。すなわち、4個あたりから飽和し始める。従って、4個設けることが好ましい。また方形の電極を用いた際には高周波電流が流れる経路も均一化し、プラスマ処理効果が方形電極中央に配置された被処理物に対して均一に施されることを考慮すれば、金属プレートを4個または8個設けることが好ましい。

【0047】

(プラズマ処理装置の第5の実施の形態)

図8に第5の実施の形態を示す。

【0048】

本例は、金属プレート80aを斜めに配置した例である。すなわち、金属プレート80aの一端はシールド12におけるチャンバ側壁に最も近い点B1で短絡せしめ、金属プレート80aの他端はB1の真下ではなく、チャンバ側壁よりの点A1で短絡せしめることにより金属プレートは斜めに配置している。なお、金属プレート80aを斜めに配置する場合における傾斜角度θは45°未満が相互インダクタンスの発生を抑制する上から好ましい。

【0049】

本第5の実施の形態では第1の実施の形態の場合よりさらに電力消費効率は高まった。

【0050】

(プラズマ処理装置の第6の実施の形態)

図9にさらに第6の実施の形態を示す。

【0051】

本例は、金属プレート80aをチャンバ側壁10aに対して略垂直に、すなわち、サセプタ電極8にほぼ水平に配置した。

本例では第5の実施の形態の場合よりさらに電力消費効率は高まった。

【0052】

(プラズマ処理装置の第7の実施の形態)

図10に第7の実施の形態を示す。

【0053】

本例は、図15に示す従来のプラズマ処理装置において、金属プレートを設けた例である。

【0054】

他の点は第1の実施の形態と同様である。

本例に係るプラズマ処理装置も図15に示す従来のプラズマ処理装置より電力消費効率、成膜速度、絶縁耐圧は優れていた。

【0055】

(プラズマ処理装置の第8の実施の形態)

図11に第8の実施の形態を示す。

【0056】

本例は、図16に示す従来のプラズマ処理装置において、金属プレートを設けた例である。

他の点は第1の実施の形態と同様である。

【0057】

本例に係るプラズマ処理装置も図16に示す従来のプラズマ処理装置より電力消費効率、成膜速度、絶縁耐圧は優れていた。

【0058】

上記した発明においてはインピーダンスを小さくすることにより従来より電力消費効率を向上させることが可能となった。

【0059】

しかし、それでもまだ希望する電力消費効率は達成されていない。

本発明者はその原因を探求したところ、その原因は、高周波電源1が有するインピーダンス、マッチング回路が有するインピーダンスではないかとの着想を得た。

【0060】

すなわち、従来は、基板サイズも80cmより小さく、また、プラズマ密度も高くなく、使用する周波数も13.56MHzであるため、高周波電源が有するインピーダンス、マッチング回路が有するインピーダンスは電力消費効率に影響を与えることはなかった。しかるに高いプラズマ密度が達成可能となり、基板サイズも大きくなり、また、使用する周波数も13.56MHzを超える状況にあっては高周波電源が有するインピーダンス、現在マッチング回路が有するインピーダンスが電力消費効率に与える影響を無視できないのではないかとの着想を得たのである。なお、従来においては高周波電源の抵抗値は50Ωである。

【0061】

かかる着想に基づき試験を行ったところ、13.56MHzを超える周波数を用いる場合には、高周波電源が有する抵抗値を50Ω未満、マッチング回路が有する抵抗値を50Ω未満とすると電力消費効率が向上することを見いだした。なお、10Ω以下がより好ましい。

【0062】

フィックスチャ(検体)は、半導体、LCD、MRヘッドなどの製造に用いられるプラズマ装置のインピーダンスの測定装置並びにその測定方法に用いられる。

フィクスチャについての従来の技術は次の通りである。

【0063】

成膜工程、エッチング工程には、高周波電源を用いてグロー放電させて生成されたプラズマを利用したプラズマ装置が用いられている。このような工程では、装置に寄生するインピーダンスが原因で、投入した電力のうち、プラズマ空間で有効に消費される実効的な電力の比率が小さくなり、成膜速度や膜耐圧に影響を及ぼし、生産性や膜質の低下を招いていた。これを改善するためには、装置に寄生するインピーダンスを定量的に把握する必要があった。

【0064】

このような測定には、同軸形状のプローブを有するインピーダンスアナライザ、もしくは、ネットワークアナライザが用いられる。しかし、プローブ形状の制約から、測定対象物の大きさに、あるいは、測定可能な2点間の距離に、それぞれ制限があった。

【0065】

従来、この問題に対処する方法としては、プローブのアース側に測定対象物の大きさや測定する2点間の距離に見合った長さの導線をプローブのアース側にフィクスチャとして取り付け、これの残留インピーダンスを補正して用いる方法が、最も簡易な方法として挙げられる。

【0066】

しかし、上記従来のフィクスチャには、次のような問題がある。

(1)測定対象を電流が非対称に流れるため、測定対象の部分的なインピーダンスしか測定されず、正確なインピーダンスを知ることができない。

(2)フィクスチャとして取り付けたアース線のインピーダンスで電流が制限を受けるため、低インピーダンスの測定を正確に行えない。

【0067】

測定対象の大きさ、あるいは、測定する2点間の距離に制約を与えることなく、かつ、測定対象に均一に電流を流すことができ、測定対象のインピーダンスを測定するのに影響を及ぼさない残留インピーダンスの値に設計可能な専用フィクスチャ並びにその測定方法を提供することを目的として本発明者は、新規なインピーダンス測定具を考えた。

【0068】

(インピーダンス測定具の第1の実施の形態)

本発明に係るインピーダンス測定具の第1の実施の形態を、図17に基づき説明する。このフィクスチャは、それぞれのインピーダンスが一致する複数本の導線101a〜101hの一端をプローブ取付具104に接続してなることを特徴とする。

【0069】

プローブ取付具104は、例えば50mm×10mm×0.5mmの銅板を、締め付け部106とリング部とができるように成形する。リング部はプローブ105の外側にはめ込み可能な径とする。

【0070】

このプローブ取付部104に導線101a〜101hの一端をハンダ付けなどにより電気的に接続する。

【0071】

導線101a〜101hの他端には、測定対象(被測定物)との着脱用の端子(圧着端子)102a〜102hが取り付けられている。

【0072】

このフィクスチャを使用するに際してはプローブ取付具104のリング状部104をプローブ105にはめ込み、締め付け部106で締め付けを行う。一方各導線101a〜101hは略点対称となるように圧着端子102a〜102hにおいて測定対象に、図21に示すようにねじ114により着脱自在にねじ止めする。このプローブ105は、図23示すように、導線110上に絶縁被覆112を設け、この絶縁被覆112上に外周導体111を被覆してなるものである。このプローブ105は同軸ケーブルを通して図示を省略したインピーダンス測定装置に接続している。

【0073】

導体101a〜101hは、例えばアルミニウム、銅、銀、金により構成すればよく、または、銀、金を50μm以上メッキして構成してもよい。

【0074】

フィクスチャをこのように配置した後測定対象のインピーダンスを測定した。その結果を図19に示す。図19(a)は従来例の結果を示し、図19(b)は本例の結果を示す。なお、図19(a)の従来例の測定は、図23に示したプローブ105を用いて実施した。

【0075】

インピーダンスZはωL−1/ωCで表されるわけであり、ある周波数f0において1/ωCを表す双曲線とωLを表す直線との変曲点があり、その点においては位相が変化する。しかるに、従来例の結果を示す図19(a)においてはかかる点が明確には表れていない。それに対して本例の結果を示す図19(b)においては双曲線と直線並びに変曲点が周波数f0において明確に表れており、インピーダンスが正確に測定されたことがわかる。

【0076】

なお、導線101a〜101hのインピーダンスで電流が制限を受けるのを少なくするとの配慮から、導線101a〜101hには比抵抗の小さい銅を用いることが好ましい。導線を用いることで、測定対象との間の寄生容量も小さくできるという利点を持つ。

【0077】

次に本実施の形態に記載のインピーダンス測定具を用いて、図1に示したプラズマ処理装置の給電板3からプラズマ励起電極(カソード電極)4、プラズマ空間60、サセプタ電極8、シールド12の水平部、金属プレート80a、80b、チャンバ壁10の底部10b、チャンバ壁の側壁部10a、ハウジング21に至る経路のインピーダンスを測定する方法を図21を用いて説明する。

【0078】

まずプラズマ処理装置の高周波電源1とマッチングボックス2をプラズマ処理装置から取り外す。インピーダンス測定具のプローブ105の導線110をマッチングボックス2と給電板3とを接続する導線113に接続する。次いでインピーダンス測定具のフィクスチャの導線101a〜101hに接続する圧着端子102a〜102hをプラズマ処理装置のハウジング21に給電板3を中心とする略点対称となるようにネジ114によってネジ止めする。インピーダンス測定具をこのように配置した後、測定信号をインピーダンス測定具の導線110に供給し、前記プラズマ処理装置の給電板3からプラズマ空間60を経てハウジング21に至る経路のインピーダンスを測定する。

【0079】

0S、0Ω、50Ωでそれぞれ校正済みの測定プローブにこのフィクスチャを取り付けて用いることになるが、このフィクスチャの残留インピーダンスの影響はオープン、および、ショートの補正を実施することで解決可能である。なお、フィクスチャを取り付けたプローブに対して上記校正を施しても図20に示すように同様の効果が得られる。

【0080】

(インピーダンス測定具の第2の実施の形態)

本発明に係るインピーダンス測定具の第2の実施の形態を図18に示す。このインピーダンス測定具は、測定対象が大きい場合に使用するもので、複数の導線101a〜101hの間を、さらに別の短絡用導線108で短絡している。

【0081】

このインピーダンス測定具によれば、測定電流の経路が増えることから上記検体のインピーダンスを減少させることが可能となる。その結果、被測定物を含めた測定系全体のインピーダンスに占める被測定物のインピーダンスの割合が高くなり、より高精度のインピーダンス測定が可能となる。

【0082】

(インピーダンス測定具の第3の実施の形態)

図22に、本発明のインピーダンス測定具に係る第3の実施の形態を示す。本実施の形態では、上述の第1の実施の形態における複数本の導線101a〜101hの一端を、プローブ取付具を介さないで直接プローブ105の外周導体111に半田端子部121で半田付けして接続していることが前記第1の実施の形態と異なり、他の部分は前記第1の実施の形態と同様である。本実施の形態においても上記本発明のインピーダンス測定具に係る第1の実施の形態と同様の効果が得られた。

【0083】

【発明の効果】

本発明によれば、電力消費効率を高くすることができ、成膜速度が従来より速くかつ、より良質の膜の形成が可能となる。また、サセプタインピーダンスを小さくかつ周波数依存性を少なくすることができる。

【図面の簡単な説明】

【図1】 プラズマ処理装置の第1の実施の形態に係るプラズマ処理装置の断面図である。

【図2】 図1のサセプタ電極近傍の拡大図である。

【図3】 (a)はメッシュ状金属プレートの部分側面図、(b)はその平面図である。

【図4】 プラズマ処理装置の第1の実施の形態および従来例にかかる測定結果を示すグラフである。

【図5】 プラズマ処理装置の第2の実施の形態に係るプラズマ処理装置の断面図である。

【図6】 金属プレートとチャンバ壁との距離と相互インダクタンスとの関係を示すグラフである。

【図7】 金属プレートの配置数の影響を示すグラフである。

【図8】 プラズマ処理装置の第5の実施の形態に係るプラズマ処理装置の一部を示す断面図である。

【図9】 プラズマ処理装置の第6の実施の形態に係るプラズマ処理装置の一部を示す断面図である。

【図10】 プラズマ処理装置の第7の実施の形態に係るプラズマ処理装置を示す断面図である。

【図11】 プラズマ処理装置の第8の実施の形態に係るプラズマ処理装置を示す断面図である。

【図12】 従来例に係るプラズマ処理装置の断面図である。

【図13】 図12に示したサセプタ電極及びその周辺部の部分拡大図である。

【図14】 他の従来例に係るプラズマ処理装置の断面図である。

【図15】 他の従来例に係るプラズマ処理装置の断面図である。

【図16】 他の従来例に係るプラズマ処理装置の断面図である。

【図17】 本発明のインピーダンス測定具に係る第1の実施の形態を示す図である。

【図18】 本発明のインピーダンス測定具に係る第2の実施の形態を示す図である。

【図19】 図17に示したインピーダンス測定具を用いて測定を行った結果を示すグラフである。

【図20】 図17に示したインピーダンス測定具を用いて測定を行った結果を示すグラフである。

【図21】 図17に示したインピーダンス測定具を用いて図1に示したプラズマ処理装置のインピーダンスを測定する方法を示す図である。

【図22】 本発明のインピーダンス測定具に係る第3の実施の形態を示す斜視図である。

【図23】 図17、図18、および図22に示したインピーダンス測定具に用いたプローブを示す斜視図である。

【符号の説明】

1 高周波電源、

2 マッチングボックス、

3 給電板、

4 プラズマ励起電極(カソード電極)、

5 シャワープレート、

6 空間、

7 孔、

8 プラズマ励起電極(ウエハサセプタ、サセプタ電極)、

9 絶縁体、

10 チャンバ壁、

10a チャンバ側壁、

10b チャンバ壁底部、

10s チャンバ側壁、

10u チャンバ上部、

11 ベローズ、

12 サセプタシールド、

13 シャフト、

14 マッチングボックス、

15 高周波電源、

16 基板、

17 ガス導入管、

21 ハウジング、

20 シールド、

60 チャンバ室、

80a,80b 金属プレート、

101a〜101h 導線、

102a〜102h 圧着端子、

104 プローブ取付具、

105 プローブ、

106 締め付け部、

111 外周導体、

112 絶縁被膜、

114 ねじ、

121 短絡点、

A1,A2 短絡点、

B1,B2 短絡点。[0001]

[Industrial application fields]

The present invention relates to a plasma processing apparatus.

[0002]

[Prior art]

Conventionally, a plasma processing apparatus shown in FIG. 12 is known.

[0003]

In the conventional plasma processing apparatus, a matching circuit is interposed between the high

[0004]

The high frequency power from the high

[0005]

These matching circuit and

[0006]

Below the plasma excitation electrode (cathode electrode) 4, a

[0007]

On the other hand, a wafer susceptor (susceptor electrode) 8 on which a

[0008]

A second high

The chamber and the

[0009]

FIG. 14 shows another conventional plasma processing apparatus.

Although the plasma processing apparatus shown in FIG. 12 is a so-called dual frequency excitation type plasma processing apparatus, the plasma processing apparatus shown in FIG. 14 is a single frequency excitation type plasma processing apparatus. That is, high-frequency power is supplied only to the

[0010]

FIG. 15 shows another conventional plasma processing apparatus.

In the plasma processing apparatus shown in FIG. 15, no shower plate is used, and the

[0011]

FIG. 16 shows another conventional plasma processing apparatus.

The plasma processing apparatus shown in FIG. 15 is a so-called dual frequency excitation type plasma processing apparatus, but the plasma processing apparatus shown in FIG. 16 is a single frequency excitation type plasma processing apparatus. That is, high-frequency power is supplied only to the

[0012]

However, when the conventional plasma processing apparatus is examined in detail, the power consumption efficiency (the ratio of the power consumed in the plasma to the power input from the high

[0013]

In the conventional plasma processing apparatus shown in FIGS. 12, 14, 15, and 16, the susceptor impedance (impedance between the susceptor and the chamber) is high, and the frequency of the high frequency supplied from the high

[0014]

The power consumption efficiency was investigated as follows.

(1) Replace the chamber wall of the plasma processing apparatus with an equivalent circuit composed of a lumped constant circuit.

(2) Determine the constants of each circuit by measuring the impedance of the components of the chamber using an impedance analyzer.

(3) Using the fact that the impedance of the entire chamber during discharge is in a complex conjugate relationship with the impedance of the matching box with a dummy load of 50Ω on the input side, the impedance of the entire chamber during discharge is known.

(4) The plasma space is regarded as a series circuit of a resistor R and a capacitor C, and the respective constants are calculated from the values obtained in (2) and (3).

(5) Based on the equivalent circuit model of the chamber during discharge obtained by the above method, circuit calculation is performed to derive power consumption efficiency.

[0015]

As described above, in the conventional plasma processing apparatus, the film formation rate is slow because the power consumption efficiency is low, and it is difficult to form an insulating film having a higher withstand voltage in the case of forming an insulating film, for example. Has the problem.

[0016]

The inventor has eagerly searched for the cause of low power consumption efficiency. As a result, we obtained the knowledge that the cause of low power consumption efficiency is the following.

[0017]

That is, first, on the

[0018]

Also in the plasma processing apparatus shown in FIG. 14, the high frequency power from the high

[0019]

However, in the conventional plasma processing apparatus shown in FIGS. 12 and 14, the

[0020]

In addition, knowledge including this subject was found for the first time by the present inventors.

[0021]

[Means for Solving the Problems]

The plasma processing apparatus of the present invention has a plasma excitation electrode to which power for plasma excitation is supplied in a chamber chamber for performing plasma processing , and is opposed to the plasma excitation electrode and has the same DC potential as the chamber wall of the chamber chamber. A susceptor electrode , and the susceptor electrode is an electrode into which a high-frequency current generated by the plasma excitation power flows after passing through a plasma space, and the chamber wall and the susceptor electrode are short-circuited in an alternating manner. It is characterized by.

[0022]

Here, it is preferable that the chamber wall and the susceptor electrode are electrically connected .

[0023]

Moreover, it is preferable that the point which short-circuits the said susceptor electrode and the said chamber wall exists in the range below 500 mm in the horizontal direction from the said chamber side wall. Furthermore, it is preferable that the point where the susceptor electrode and the chamber wall are short-circuited on the chamber side is in a range of less than 500 mm in the horizontal direction from the chamber side wall. Furthermore, it is preferable that the chamber wall and the susceptor electrode are short-circuited at a plurality of points.

[0024]

Here, it is preferable that a short-circuit point that short-circuits the chamber wall and the susceptor electrode is substantially point-symmetric with respect to the center of the electrode. Further, it is preferable that a short-circuit point for short-circuiting the chamber wall and the susceptor electrode is substantially point symmetric with respect to the shield center .

[0025]

Furthermore, the plasma processing apparatus of the present invention is provided with a plasma excitation electrode to which power for plasma excitation is supplied and a high-frequency current generated by the plasma excitation power in a chamber chamber for performing plasma processing. A susceptor electrode that flows after passing through the plasma space, and a susceptor shield that is provided around the susceptor electrode and that has the same potential as the chamber wall of the chamber chamber, and the chamber wall and the susceptor shield Are short-circuited in an alternating manner.

[0026]

Here, it is preferable that the chamber wall and the susceptor shield are electrically connected. Furthermore, it is preferable that the susceptor shield and the chamber wall are short-circuited.

In the present invention, the point on the chamber side is preferably within a range of less than 500 mm in the horizontal direction from the side wall of the chamber chamber, and each point where the susceptor shield and the chamber wall are short-circuited. It is preferable that the distance is less than 500 mm in the horizontal direction from the side wall of the chamber.

Furthermore, in the present invention, it is preferable that the chamber wall and the susceptor shield are short-circuited at a plurality of points, and the short-circuit point that short-circuits the chamber wall and the susceptor shield is substantially the center of the susceptor electrode. It is preferably point-symmetric.

[0027]

DETAILED DESCRIPTION OF THE INVENTION

(First embodiment of plasma processing apparatus)

FIG. 1 shows a first embodiment of a plasma processing apparatus of the present invention. In this plasma processing apparatus, the

[0028]

FIG. 2 shows details of the

In this example, AC short-circuit between the

[0029]

Inconel 625 (trade name) is preferably used as the material of the metal plate from the viewpoint that the amount of gas released in vacuum is small. In this example, a metal plate having dimensions of 20 mm × 40 cm × 0.3 mm was used. .

[0030]

In addition, although the plate-shaped thing was used in this example, it is also preferable to use a mesh-shaped thing. The shape of the mesh is preferably a turtle shape or a lattice shape shown in FIG. The mesh metal plate is preferably arranged in a cylindrical shape along the periphery of the

[0031]

In this example, the short-circuit points A1 and A2 in the

[0032]

In the plasma processing apparatus of this example, high frequency power is supplied from a high

[0033]

In the conventional plasma processing apparatus, the high-frequency current has passed through the vertical portion of the

[0034]

However, in the plasma processing apparatus according to the present example, the high-frequency current passes through the

[0035]

An insulating film made of silicon nitride is formed using the apparatus shown in FIG. 1 and the apparatus shown in FIG. 12, and the power consumption efficiency at that time is measured. In the case of the apparatus shown in FIG. 1, the apparatus shown in FIG. Compared with the case of, the power consumption efficiency was double.

[0036]

In addition, susceptor impedance was measured. The result is shown in FIG. (A) is the case of the plasma processing apparatus shown in FIG. 12 (conventional example), and (b) is the case of the plasma processing apparatus shown in FIG.

[0037]

As can be seen from FIG. 4, in the plasma processing apparatus according to this example, the susceptor impedance is much smaller than that of the plasma processing apparatus according to the conventional example, and the frequency dependency is small.

[0038]

(Second Embodiment of Plasma Processing Apparatus)

FIG. 5 shows a plasma processing apparatus according to the second embodiment.

This example is an example in which

[0039]

In other words, the

The other points are the same as in the first embodiment.

[0040]

(Third embodiment of plasma processing apparatus)

In this example, the influence of the position where the metal plate is provided was examined.

[0041]

That is, in the apparatus shown in FIG. 1, the short-circuit points B1 and B2 of the metal plate in the

[0042]

The result is shown in FIG.

As can be seen from FIG. 6, the inductance starts decreasing when the distance x is 500 mm, the decreasing rate increases from around 350 mm, and the decreasing rate increases more rapidly from around 200 mm.

[0043]

Accordingly, the position of the short-circuit point is preferably less than 500 mm from the chamber side wall, more preferably less than 350 mm, and even more preferably less than 200 mm. Most preferred is the point at or near the shortest distance from the

[0044]

(Fourth embodiment of plasma processing apparatus)

In this example, the influence of the number of metal plates arranged was examined.

[0045]

That is, the number of metal plates was changed and the magnitude of the inductance was measured. The metal plate was arranged approximately point-symmetrically with respect to the center of the shield.

The result is shown in FIG.

[0046]

As shown in FIG. 7, the inductance starts to decrease by arranging the metal plate, but the reduction rate is almost the same when four or eight are arranged. That is, saturation starts from around four. Therefore, it is preferable to provide four. In addition, when a square electrode is used, the path through which the high-frequency current flows is made uniform, and considering that the plasma treatment effect is uniformly applied to the workpiece placed in the center of the square electrode, the metal plate is It is preferable to provide four or eight.

[0047]

(Fifth embodiment of plasma processing apparatus)

FIG. 8 shows a fifth embodiment.

[0048]

In this example, the

[0049]

In the fifth embodiment, the power consumption efficiency is further increased as compared with the case of the first embodiment.

[0050]

(Sixth embodiment of plasma processing apparatus)

FIG. 9 further shows a sixth embodiment.

[0051]

In this example, the

In this example, the power consumption efficiency is further increased than in the case of the fifth embodiment.

[0052]

(Seventh embodiment of plasma processing apparatus)

FIG. 10 shows a seventh embodiment.

[0053]

This example is an example in which a metal plate is provided in the conventional plasma processing apparatus shown in FIG.

[0054]

The other points are the same as in the first embodiment.

The plasma processing apparatus according to this example was also superior in power consumption efficiency, film formation rate, and withstand voltage than the conventional plasma processing apparatus shown in FIG.

[0055]

(Eighth embodiment of plasma processing apparatus)

FIG. 11 shows an eighth embodiment.

[0056]

This example is an example in which a metal plate is provided in the conventional plasma processing apparatus shown in FIG.

The other points are the same as in the first embodiment.

[0057]

The plasma processing apparatus according to this example was also superior in power consumption efficiency, film formation rate, and withstand voltage than the conventional plasma processing apparatus shown in FIG.

[0058]

In the above-described invention, it has become possible to improve the power consumption efficiency as compared with the prior art by reducing the impedance.

[0059]

However, the desired power consumption efficiency is still not achieved.

The inventor searched for the cause, and obtained the idea that the cause might be the impedance of the high-

[0060]

That is, conventionally, since the substrate size is smaller than 80 cm, the plasma density is not high, and the frequency used is 13.56 MHz, the impedance of the high frequency power supply and the impedance of the matching circuit affect the power consumption efficiency. It never happened. However, a high plasma density can be achieved, the substrate size is increased, and the impedance of the high-frequency power source and the impedance of the current matching circuit have an effect on the power consumption efficiency when the frequency used exceeds 13.56 MHz. I got the idea that I couldn't ignore it. Conventionally, the resistance value of the high-frequency power source is 50Ω.

[0061]

A test was conducted based on such an idea. When a frequency exceeding 13.56 MHz is used, the power consumption efficiency is improved when the resistance value of the high-frequency power source is less than 50Ω and the resistance value of the matching circuit is less than 50Ω. I found. Note that 10Ω or less is more preferable.

[0062]

The fixture (specimen) is used in an impedance measuring device and a measuring method of a plasma device used for manufacturing semiconductors, LCDs, MR heads, and the like.

The conventional technique for the fixture is as follows.

[0063]

In the film forming process and the etching process, a plasma apparatus using plasma generated by glow discharge using a high-frequency power source is used. In such a process, due to the parasitic impedance of the device, the ratio of the effective power that is effectively consumed in the plasma space out of the input power is reduced, which affects the film formation speed and film breakdown voltage, Productivity and film quality were reduced. In order to improve this, it was necessary to quantitatively grasp the impedance parasitic on the device.

[0064]

For such measurement, an impedance analyzer having a coaxial probe or a network analyzer is used. However, due to restrictions on the probe shape, there are limitations on the size of the measurement object or the distance between two measurable points.

[0065]

Conventionally, as a method of dealing with this problem, a lead wire having a length corresponding to the size of the object to be measured and the distance between two points to be measured is attached as a fixture to the earth side of the probe as a fixture. A method of correcting and using the impedance is the simplest method.

[0066]

However, the conventional fixture has the following problems.

(1) Since the current flows through the measurement object asymmetrically, only a partial impedance of the measurement object is measured, and an accurate impedance cannot be known.

(2) Since the current is limited by the impedance of the ground wire attached as a fixture, low impedance measurement cannot be performed accurately.

[0067]

Residue that does not affect the measurement of the impedance of the measurement object without restricting the size of the measurement object or the distance between the two points to be measured, and allowing the current to flow uniformly through the measurement object For the purpose of providing a dedicated fixture that can be designed to an impedance value and a measuring method thereof, the present inventor has considered a novel impedance measuring tool.

[0068]

(First Embodiment of Impedance Measuring Tool)

A first embodiment of the impedance measuring tool according to the present invention will be described with reference to FIG. This fixture is characterized in that one end of a plurality of conducting

[0069]

The

[0070]

One end of the conducting

[0071]

Terminals (crimp terminals) 102a to 102h for attaching to and detaching from the measurement target (object to be measured) are attached to the other ends of the conducting

[0072]

When using this fixture, the ring-shaped

[0073]

The

[0074]

After arranging the fixture in this way, the impedance of the object to be measured was measured. The result is shown in FIG. FIG. 19A shows the result of the conventional example, and FIG. 19B shows the result of this example. Note that the measurement of the conventional example of FIG. 19A was performed using the

[0075]

The impedance Z is represented by ωL−1 / ωC, and there is an inflection point between a hyperbola representing 1 / ωC and a straight line representing ωL at a certain frequency f 0 , and the phase changes at that point. However, this point is not clearly shown in FIG. 19A showing the result of the conventional example. On the other hand, in FIG. 19B showing the result of this example, the hyperbola, the straight line, and the inflection point clearly appear at the frequency f 0 , indicating that the impedance was accurately measured.

[0076]

In addition, it is preferable to use copper with a small specific resistance for the conducting

[0077]

Next, using the impedance measuring instrument described in this embodiment, the plasma excitation electrode (cathode electrode) 4, the

[0078]

First, the high

[0079]

This fixture is attached to a measurement probe calibrated at 0S, 0Ω, and 50Ω, respectively. The effect of the residual impedance of this fixture can be solved by correcting for open and short. . Note that the same effect can be obtained as shown in FIG. 20 even if the calibration is applied to the probe to which the fixture is attached.

[0080]

(Second Embodiment of Impedance Measuring Tool)

FIG. 18 shows a second embodiment of the impedance measuring instrument according to the present invention. This impedance measuring tool is used when a measurement target is large, and a plurality of conducting

[0081]

According to this impedance measuring instrument, the impedance of the specimen can be reduced because the path of the measurement current increases. As a result, the ratio of the impedance of the object to be measured occupying the impedance of the entire measurement system including the object to be measured becomes high, and impedance measurement with higher accuracy is possible.

[0082]

(Third Embodiment of Impedance Measuring Tool)

FIG. 22 shows a third embodiment according to the impedance measuring instrument of the present invention. In the present embodiment, one end of the plurality of

[0083]

【The invention's effect】

According to the present invention, it is possible to increase the power consumption efficiency, to form a film with a higher quality and a higher quality film than before. Further, the susceptor impedance can be reduced and the frequency dependency can be reduced.

[Brief description of the drawings]

FIG. 1 is a cross-sectional view of a plasma processing apparatus according to a first embodiment of the plasma processing apparatus.

FIG. 2 is an enlarged view of the vicinity of a susceptor electrode in FIG.

3A is a partial side view of a mesh-like metal plate, and FIG. 3B is a plan view thereof.

FIG. 4 is a graph showing measurement results according to the first embodiment and a conventional example of a plasma processing apparatus.

FIG. 5 is a cross-sectional view of a plasma processing apparatus according to a second embodiment of the plasma processing apparatus.

FIG. 6 is a graph showing the relationship between the distance between the metal plate and the chamber wall and the mutual inductance.

FIG. 7 is a graph showing the influence of the number of metal plates arranged.

FIG. 8 is a cross-sectional view showing a part of a plasma processing apparatus according to a fifth embodiment of the plasma processing apparatus.

FIG. 9 is a cross-sectional view showing a part of a plasma processing apparatus according to a sixth embodiment of the plasma processing apparatus.

FIG. 10 is a cross-sectional view showing a plasma processing apparatus according to a seventh embodiment of the plasma processing apparatus.

FIG. 11 is a cross-sectional view showing a plasma processing apparatus according to an eighth embodiment of the plasma processing apparatus.

FIG. 12 is a cross-sectional view of a plasma processing apparatus according to a conventional example.

13 is a partially enlarged view of the susceptor electrode shown in FIG. 12 and its peripheral portion.

FIG. 14 is a cross-sectional view of a plasma processing apparatus according to another conventional example.

FIG. 15 is a cross-sectional view of a plasma processing apparatus according to another conventional example.

FIG. 16 is a cross-sectional view of a plasma processing apparatus according to another conventional example.

FIG. 17 is a diagram showing a first embodiment according to the impedance measuring instrument of the present invention.

FIG. 18 is a diagram showing a second embodiment according to the impedance measuring instrument of the present invention.

FIG. 19 is a graph showing the results of measurement using the impedance measuring tool shown in FIG.

20 is a graph showing the results of measurement using the impedance measuring tool shown in FIG.

21 is a diagram showing a method of measuring the impedance of the plasma processing apparatus shown in FIG. 1 using the impedance measuring tool shown in FIG.

FIG. 22 is a perspective view showing a third embodiment of the impedance measuring instrument of the present invention.

23 is a perspective view showing a probe used in the impedance measuring instrument shown in FIGS. 17, 18 and 22. FIG.

[Explanation of symbols]

1 high frequency power supply,

2 matching boxes,

3 Power supply plate,

4 Plasma excitation electrode (cathode electrode),

5 shower plate,

6 space,

7 holes,

8 Plasma excitation electrode (wafer susceptor, susceptor electrode),

9 Insulator,

10 chamber walls,

10a chamber sidewall,

10b chamber wall bottom,

10s chamber sidewall,

10u upper chamber,

11 Bellows,

12 Susceptor shield,

13 shaft,

14 Matching box,

15 high frequency power supply,

16 substrates,

17 Gas introduction pipe,

21 housing,

20 Shield,

60 chamber chamber,

80a, 80b metal plate,

101a to 101h conducting wire,

102a to 102h crimp terminal,

104 probe fixture,

105 probes,

106 Tightening part,

111 outer conductor,

112 insulation coating,

114 screws,

121 short-circuit point,

A1, A2 short circuit point,

B1, B2 Short circuit point.

Claims (12)

該プラズマ励起電極に対向し、前記チャンバ室のチャンバ壁と直流的に同電位であるサセプタ電極とを備え、

該サセプタ電極は、前記プラズマ励起用電力による高周波電流がプラズマ空間を経由した後流入する電極であり、

前記チャンバ壁と前記サセプタ電極とを交流的に短絡していることを特徴とするプラズマ処理装置。A plasma excitation electrode to which power for plasma excitation is supplied into a chamber for performing plasma treatment;

A susceptor electrode facing the plasma excitation electrode and having the same DC potential as the chamber wall of the chamber chamber;

The susceptor electrode is an electrode into which a high-frequency current generated by the plasma excitation power flows after passing through the plasma space;

A plasma processing apparatus, wherein the chamber wall and the susceptor electrode are short-circuited in an alternating manner.

該プラズマ励起電極と対向して設けられ、前記プラズマ励起用電力による高周波電流がプラズマ空間を経由した後流入するサセプタ電極と、

該サセプタ電極の周囲に設けられた、前記チャンバ室のチャンバ壁と直流的に同電位のサセプタシールドと、を備え、

前記チャンバ壁と前記サセプタシールドとを交流的に短絡していることを特徴とするプラズマ処理装置。A plasma excitation electrode to which power for plasma excitation is supplied into a chamber for performing plasma treatment;

A susceptor electrode provided facing the plasma excitation electrode and into which a high-frequency current generated by the plasma excitation power flows after passing through the plasma space;

A susceptor shield provided around the susceptor electrode and having the same potential as that of the chamber wall of the chamber chamber;

The plasma processing apparatus, wherein the chamber wall and the susceptor shield are short-circuited in an alternating manner.

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP34080698A JP3710081B2 (en) | 1997-11-30 | 1998-11-30 | Plasma processing equipment |

| US09/442,539 US6349670B1 (en) | 1998-11-30 | 1999-11-18 | Plasma treatment equipment |

| DE69924767T DE69924767T2 (en) | 1998-11-30 | 1999-11-25 | Plasma processing device and tool for impedance measurement |

| EP03023423A EP1406292B1 (en) | 1998-11-30 | 1999-11-25 | Plasma treatment equipment and impedance measurement tool |

| DE69927780T DE69927780T2 (en) | 1998-11-30 | 1999-11-25 | Plasma processing device and tool for impedance measurement |

| EP99309434A EP1030345B1 (en) | 1998-11-30 | 1999-11-25 | Plasma treatment equipment and impedance measurement tool |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP9-345852 | 1997-11-30 | ||

| JP34585297 | 1997-11-30 | ||

| JP34080698A JP3710081B2 (en) | 1997-11-30 | 1998-11-30 | Plasma processing equipment |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001280772A Division JP3705582B2 (en) | 1997-11-30 | 2001-09-14 | Impedance measuring tool |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH11251094A JPH11251094A (en) | 1999-09-17 |

| JP3710081B2 true JP3710081B2 (en) | 2005-10-26 |

Family

ID=26576802

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP34080698A Expired - Fee Related JP3710081B2 (en) | 1997-11-30 | 1998-11-30 | Plasma processing equipment |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3710081B2 (en) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4531185B2 (en) * | 2000-03-03 | 2010-08-25 | 株式会社アルバック | Vacuum processing equipment |

| US6857387B1 (en) * | 2000-05-03 | 2005-02-22 | Applied Materials, Inc. | Multiple frequency plasma chamber with grounding capacitor at cathode |

| US6364958B1 (en) * | 2000-05-24 | 2002-04-02 | Applied Materials, Inc. | Plasma assisted semiconductor substrate processing chamber having a plurality of ground path bridges |

| JP4672861B2 (en) * | 2000-12-15 | 2011-04-20 | 東京エレクトロン株式会社 | Plasma processing equipment |

| US7084832B2 (en) * | 2001-10-09 | 2006-08-01 | Plasma Control Systems, Llc | Plasma production device and method and RF driver circuit with adjustable duty cycle |

| JP4312063B2 (en) | 2004-01-21 | 2009-08-12 | 日本エー・エス・エム株式会社 | Thin film manufacturing apparatus and method |

| US20060027327A1 (en) * | 2004-07-12 | 2006-02-09 | Applied Materials, Inc. | Apparatus and methods for a low inductance plasma chamber |

| US7534301B2 (en) * | 2004-09-21 | 2009-05-19 | Applied Materials, Inc. | RF grounding of cathode in process chamber |

| JP2006236867A (en) * | 2005-02-25 | 2006-09-07 | Ngk Insulators Ltd | Plasma treatment member |

| JP2007096354A (en) * | 2007-01-09 | 2007-04-12 | Tokyo Electron Ltd | Plasma processing apparatus |

| JP4887202B2 (en) * | 2007-04-17 | 2012-02-29 | 東京エレクトロン株式会社 | Plasma processing apparatus and high-frequency current short circuit |

| JP5782226B2 (en) | 2010-03-24 | 2015-09-24 | 東京エレクトロン株式会社 | Substrate processing equipment |

| JP5375763B2 (en) * | 2010-07-27 | 2013-12-25 | 三菱電機株式会社 | Plasma device and semiconductor thin film manufacturing method using the same |

| JP5335875B2 (en) * | 2011-10-03 | 2013-11-06 | 東京エレクトロン株式会社 | Plasma processing equipment |

| US12080522B2 (en) | 2020-04-22 | 2024-09-03 | Applied Materials, Inc. | Preclean chamber upper shield with showerhead |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04247878A (en) * | 1990-07-31 | 1992-09-03 | Applied Materials Inc | Vhf/uhf reacting device |

| JP3090562B2 (en) * | 1993-05-24 | 2000-09-25 | 東京エレクトロン株式会社 | Plasma processing equipment |

| JP3238082B2 (en) * | 1996-05-16 | 2001-12-10 | シャープ株式会社 | Electronic device manufacturing equipment |

-

1998

- 1998-11-30 JP JP34080698A patent/JP3710081B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JPH11251094A (en) | 1999-09-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3710081B2 (en) | Plasma processing equipment | |

| EP1406292B1 (en) | Plasma treatment equipment and impedance measurement tool | |

| TWI239794B (en) | Plasma processing apparatus and method | |

| JP4270872B2 (en) | System and method for monitoring impedance | |

| US6771481B2 (en) | Plasma processing apparatus for processing semiconductor wafer using plasma | |

| US6708123B2 (en) | Voltage current sensor with high matching directivity | |

| JP4681718B2 (en) | Capacitive probe for in-situ measurement of DC bias voltage of wafer | |

| JP4728405B2 (en) | Surface treatment equipment | |

| KR20020030257A (en) | Plasma processing apparatus | |

| TW550385B (en) | Capacitively coupled RF voltage probe | |

| JP2000031072A (en) | Plasma monitoring method and semiconductor fabrication system | |

| JP3292531B2 (en) | High frequency excitation plasma measurement device | |

| JP3705582B2 (en) | Impedance measuring tool | |

| JP4255686B2 (en) | Plasma processing apparatus, driving method thereof, and plasma processing method | |

| JP2003224112A (en) | Plasma treatment device and plasma treatment method | |

| TW200308015A (en) | Method and apparatus for routing harmonics in a plasma to ground within a plasma enhanced semiconductor wafer processing chamber | |

| JP4030766B2 (en) | Plasma processing equipment | |

| US6452408B1 (en) | Impedance measurement tool | |

| KR20120049510A (en) | Plasma diagnose device with auxiliary double probes | |

| US10586688B2 (en) | Inductive current sensor on printed circuit board | |

| JP2893391B2 (en) | Plasma parameter measurement device | |

| JP3396879B2 (en) | Plasma processing device, matching box and power supply | |

| JP2004296612A (en) | Plasma impedance detecting device | |

| JPH05312833A (en) | Probe card | |

| JPWO2021142378A5 (en) |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040602 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040802 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050803 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050805 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090819 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090819 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100819 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110819 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110819 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120819 Year of fee payment: 7 |

|

| LAPS | Cancellation because of no payment of annual fees |