JP3605086B2 - Field effect transistor - Google Patents

Field effect transistor Download PDFInfo

- Publication number

- JP3605086B2 JP3605086B2 JP2002097049A JP2002097049A JP3605086B2 JP 3605086 B2 JP3605086 B2 JP 3605086B2 JP 2002097049 A JP2002097049 A JP 2002097049A JP 2002097049 A JP2002097049 A JP 2002097049A JP 3605086 B2 JP3605086 B2 JP 3605086B2

- Authority

- JP

- Japan

- Prior art keywords

- effect transistor

- field effect

- region

- gate

- field

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000005669 field effect Effects 0.000 title claims description 65

- 239000004065 semiconductor Substances 0.000 claims description 5

- 239000000203 mixture Substances 0.000 claims description 2

- 238000000034 method Methods 0.000 description 29

- 229910052710 silicon Inorganic materials 0.000 description 22

- 239000010703 silicon Substances 0.000 description 22

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 21

- 238000004519 manufacturing process Methods 0.000 description 19

- 239000000758 substrate Substances 0.000 description 14

- 230000000694 effects Effects 0.000 description 9

- 239000012535 impurity Substances 0.000 description 9

- 230000003647 oxidation Effects 0.000 description 9

- 238000007254 oxidation reaction Methods 0.000 description 9

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 9

- 238000005530 etching Methods 0.000 description 8

- 238000005229 chemical vapour deposition Methods 0.000 description 4

- 238000001312 dry etching Methods 0.000 description 4

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 3

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 3

- 229910004298 SiO 2 Inorganic materials 0.000 description 3

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 3

- 229910052796 boron Inorganic materials 0.000 description 3

- 238000000151 deposition Methods 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 238000005468 ion implantation Methods 0.000 description 3

- 150000002500 ions Chemical class 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- 239000011574 phosphorus Substances 0.000 description 3

- 238000004088 simulation Methods 0.000 description 3

- 230000008021 deposition Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 150000003376 silicon Chemical class 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 238000004381 surface treatment Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/785—Field effect transistors with field effect produced by an insulated gate having a channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1203—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body the substrate comprising an insulating body on a semiconductor body, e.g. SOI

- H01L27/1211—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body the substrate comprising an insulating body on a semiconductor body, e.g. SOI combined with field-effect transistors with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Ceramic Engineering (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Thin Film Transistor (AREA)

Description

【0001】

【発明の属する技術分野】

本発明は、電界効果トランジスタに関する。

【0002】

【従来の技術】

現在、超高速MOSFET(Metal Oxide Semiconductor Field Effect Transistor)は、ゲート長(Lg)に代表される素子の寸法を縮小することにより、その性能を向上させてきている。

【0003】

しかしながらゲート長が極端に短くなると、ゲートを閉状態にした場合でもソース領域及びドレイン領域間の電位差により電荷が漏れてしまうというショートチャネル効果が発生してしまう。この結果、電界効果トランジスタにおいてスイッチング動作が出来なくなるという問題が生じる。

【0004】

このショートチャネル効果を抑制するために、チャネル面の両側からゲート電圧を印加するダブルゲート構造の電界効果トランジスタが提案されている。

【0005】

このダブルゲート構造の電界効果トランジスタは、極めて狭い面間隔に配置されたゲート電極でチャネル面を挟むため、チャネル領域に十分な電圧を印加できるのでゲート閉状態においても電荷の漏れを抑制する。

【0006】

しかしながら、ダブルゲート構造の電界効果トランジスタは、ゲート間隔を極めて狭く配置するために、チャネル領域の厚さも小さくなるので、ゲート開状態において流れる電流量が少なくなり駆動力が小さいという問題がある。

【0007】

【発明が解決しようとする課題】

上述したように、従来のダブルゲート構造の電界効果トランジスタでは、ショートチャネル効果を抑制はするものの駆動力が小さいという問題があった。

【0008】

本発明は、このような問題点に鑑みてなされたもので、ショートチャネル効果を抑制しかつ駆動力を向上させることのできる電界効果トランジスタを提供することを目的とする。

【0009】

【課題を解決するための手段】

上記目的を達成するために、本発明は、ソース領域及びドレイン領域を有し、そのソース領域及びドレイン領域間に、相対する主面を有する基体と、

前記主面に設けられた一対のゲート電極と具備し、

前記一対のゲート電極の間隔が、前記ソース領域側において前記ドレイン領域側よりも大きいことを特徴とする電界効果トランジスタを提供する。

【0010】

このとき前記基体が半導体により形成されていることが好ましい。

【0011】

また、前記一対のゲート電極の間隔が、前記ソース領域側から前記ドレイン領域側に次第に小さくなっていることが好ましい。

【0012】

また、前記ソース領域を外側に、前記ドレイン領域を内側に位置するように前記電界効果トランジスタを複数個環状に配置することが好ましい。

【0013】

また、前記複数個の電界効果トランジスタは、p型及びn型が混在しており、p型の方がn型よりも多いことが好ましい。

【0014】

また、中心部にドレイン電極を具備し、前記複数個の電界効果トランジスタのドレイン領域が前記ドレイン電極の周りに配置されていることが好ましい。

【0015】

【発明の実施の形態】

以下、図面を用いて、本発明の実施形態について詳細に説明する。なお、本発明は、以下の実施形態に限定されるものではなく、種々選択して用いることができる。

【0016】

(実施形態1)

図1は、本発明の実施形態1に関わる電界効果トランジスタの斜視図である。

【0017】

図1に示すように、シリコン基板1上に楔形に成形された基体2が形成されている。この基体2は、シリコン等の半導体により形成されている。また、基体2中にはチャネル領域が形成されている。

【0018】

基体2は、対向する一対のチャネル面を具備し、このチャネル面上にそれぞれ一対のゲート電極3及び4が形成されている。チャネル面上とゲート電極3及び4間には、それぞれゲート絶縁膜(図示せず)が形成されている。

【0019】

基体2を挟むように、離間してソース領域5及びドレイン領域6が形成されている。ソース領域5及びドレイン領域6は、チャネル領域が延在している方向でチャネル領域を挟む位置に形成されている。また、ソース領域5及びドレイン領域6は、シリコン等の半導体により形成され、不純物ドープされている。

【0020】

基体2は、シリコン基板1に対して突出して形成された壁状の凸部であり、その形状はソース領域5側の幅が、ドレイン領域6側の幅よりも広い楔形となっている。すなわち一対のゲート電極3及び4の間隔は、ソース領域5側の間隔W1のほうがドレイン領域6側の間隔W2よりも大きい。また、一対のゲート電極3及び4の間隔は、ソース領域5側からドレイン領域6側に次第に小さくなっている。

【0021】

基体2の具体的な寸法は、ソース領域5に接する部分の幅を10nm、ドレイン領域6に接する部分の幅を6nmとしている。これらの幅は、一対のゲート電極3及び4のソース領域5側の間隔W1及びドレイン領域6側の間隔W2から、図示しないゲート絶縁膜の膜厚を引いたものとほぼ一致する。また、基体2の高さLwは20nmである。また、チャネル領域の長さ、ここではソース領域5と接する部分からドレイン領域6と接する部分の距離Lgは、30nmである。

【0022】

ソース領域5及びドレイン領域6の幅は、それぞれチャネル領域と接する部分の幅と同じでよい。ただしドレイン領域6の幅は、抵抗を下げるために広くしてもよい。

【0023】

次に、ゲート電極の間隔がソース領域からドレイン領域まで、次第に狭くなっている電界効果トランジスタと、ゲート電極の間隔が一定の電界効果トランジスタについて、ゲート電圧とドレイン電流の関係をシミュレーションによって求めた結果を示す。

【0024】

図2に示すように、(1)ソース領域(不純物濃度1×1020cm−3)、チャネル領域(不純物濃度1×1015cm−3)及びドレイン領域(不純物濃度1×1020cm−3)の幅が全て5nmであるダブルゲート構造の電界効果トランジスタ及び(2)ソース領域(不純物濃度1×1020cm−3)側のチャネル領域(不純物濃度1×1015cm−3)の幅が3.34nm、ドレイン領域(不純物濃度1×1020cm−3)側のチャネル領域の幅が1.67nmであるダブルゲート構造の電界効果トランジスタについて、シミュレーションした。ゲート長は共に20nmである。

【0025】

図3は、ゲート電圧とドレイン電流の関係を示す特性図である。

【0026】

図3に示すように、(2)に示すソース側が広い構造では、0.2V以下のゲート電圧の低い領域でドレイン電流が、(1)に示す通常の構造のものよりも少ない特性が得られている。すなわち、電界効果トランジスタの閉状におけるショートチャンネル効果が抑制されていることが分かる。

【0027】

また、(2)に示すソース側が広い構造では、0.4V以上のゲート電圧の高い領域では、(1)に示す通常の構造と同様にドレイン電流量が高くなっていることが分かる。これは駆動力が向上できることを示唆している。

【0028】

このように、本実施形態による構造は、ゲート閉状で、ショートチャネル効果を抑制し、かつゲート開状で駆動電流量を十分に確保できるということがいえる。

【0029】

なお、比較として(1)のチャネル幅を、(2)程度に狭くした場合は、ゲート閉状で、ショートチャネル効果を抑制することは可能であるが、駆動電流は(2)に比較して、非常に低いものであると予想される。

【0030】

次に、本実施形態に関する電界効果トランジスタの製造方法について、図4乃至図10を用いて説明する。

【0031】

本実施形態に関する電界効果トランジスタは、例えば、埋め込み酸化膜上に、SOI(Silicon On Insulater)層が積層された基板を用いて、基板表面に熱酸化膜のマスクを形成し、ドライエッチング法にて楔形の突起を作成する。次に、ドライエッチングによりダメージを受けた突起の表面を回復させるために、高温で熱酸化を施す。

【0032】

この高温熱酸化の過程で、突起は、その大きさが小さくなる。その後、表面の酸化膜マスクを除去し、表面処理を施した後にゲート加工及びソース領域及びドレイン領域の加工をして電界効果トランジスタが完成する。

【0033】

今回例としてあげる製造方法は2種類である。ひとつはゲート加工を施してから、ソース領域及びドレイン領域の加工を行うものである。他方は先にソース領域及びドレイン領域の加工を施し、その後にゲート加工を行うものである。

【0034】

先ず、ゲート加工を先に行う製造方法の例を説明する。

【0035】

ここでは厚さ100nmの埋め込み酸化膜上に、厚さ100nmのSOI層が積層された基板を用いる。埋め込み酸化膜の膜厚は、プロセス上からの大きな制約は無い。ただし、埋め込み酸化膜上のシリコン層などを、埋め込み酸化膜とのエッチング速度の差を利用して、選択エッチングする工程が用いられるため、埋め込み酸化膜の厚さが数nm以下ではプロセスに注意が必要となる。

【0036】

SOI層の厚さは、最終的に形成される突起の高さ以上の値が要求される。突起の高さはチャンネル領域の高さLw(図1)を決定する値となるため、50nm以上は必要となる。最大値については、素子設計上からは制約は少ないが、突起の高さ或いは底面に対する高さの比(アスペクト比)が大きいとプロセスが難しくなるため、1μm以下が望ましい。

【0037】

先ず、図4に示すように、シリコン基板10、埋め込み酸化膜11及びSOI層12の積層構造を有するSOI基板を準備する。

【0038】

図4中、(a)は、上面図、(b)はAA断面図、(c)はBB断面図である。以下図5乃至図10について同じである。

【0039】

図4に示すように、SOI基板のSOI層12上にSiN層13を形成し、長さ2μm、幅20nm〜40nmのレジストパターン14を形成する。

【0040】

次に、図5に示すように、レジストパターン14(図4)をマスクとして、エッチングすることで、楔型のSiNマスク13を形成する。次に、SiNマスク13をマスクとして、エッチングすることで楔形のシリコン突起12を形成する。このとき、埋め込み酸化膜11が露出する。

【0041】

シリコン突起部は、後にチャネル領域及び、これを挟むようにソース領域及びドレイン領域が形成される。シリコン突起12の側面が(010)面或いは(100)面を向いていることが望ましい。また、(110)面或いはそれと等価の面でもよい。これらの面を有することで、電荷の移動度を大きくすることができる。

【0042】

次に、図6に示すように、SiNマスク13を残したまま、熱酸化処理を行う。こうすることでドライエッチングのダメージ層を除去することができる。このときSiNマスク13で覆われた上面は酸化が進まないが、カバーの無い側面は酸化され、シリコン突起12の幅が狭くなる。シリコン突起12の側面を5nm酸化した場合、その幅は片面で5nm、両面で10nm薄くなり、10nm〜30nmの楔形となる。

【0043】

次に、SiNマスク13を除去し、シリコン突起12を露出させ、前処理をした後、シリコン突起12の表面を熱酸化する。このときの酸化膜の厚さは4nmである。その結果、シリコン突起12の幅は8nm〜28nmとなる。

【0044】

次に、図7に示すように、全面に厚さ200nmの多結晶シリコン15を堆積する。このときの多結晶シリコン15には高濃度の燐を添加する。燐の添加は多結晶シリコン15をCVD法等により、堆積時に同時に不純物添加する方法でも、イオン注入により導入する方法でもいずれでも良い。図中16は、シリコン酸化膜である。

【0045】

次に、図8に示すように、多結晶シリコン15をゲート加工する。このとき、ゲート加工でマスクに用いたレジストを利用し、シリコン突起12のエクステンションイオン注入もできる。

【0046】

次に、図9に示すように、側壁加工を行うことで側壁絶縁膜17を形成する。ここではCVD法でSiO2層を堆積後、選択エッチングで側壁のみSiO2を残して側壁絶縁膜17とした。このとき多結晶シリコン層15と、シリコン突起12の高さが異なるため、選択エッチングの条件を多結晶シリコン15の側面にのみ酸化物が残る用に設定すれば、シリコン突起12側壁のSiO2は完全除去される。その結果ゲートのみ側壁が残り、フィン側面及び上面は歪Si層が露出する。

【0047】

次に、図10に示すように、ソース領域18及びドレイン領域19をシリコンの選択成長で形成する。ここではシリコン結晶が露出したシリコン突起12上にのみ新たなシリコン層が成長する。このときホウ素を添加した選択成長を行うことによりソース領域18及びドレイン領域19の不純物添加ができる。最後にゲート電極、ソース電極、ドレイン電極を形成して電界効果トランジスタが完成する。

【0048】

(実施形態2)

次に、本発明の実施形態2に関わる電界効果トランジスタについて説明する。本実施形態では、複数のチャネル領域を連結してひとつの電界効果トランジスタを形成する例を示す。

【0049】

図11は、楔形のチャネル領域となる基体が3個並べて形成された電界効果トランジスタの斜視図である。

【0050】

図11に示すように、ソース領域及びドレイン領域をそれぞれ配線で共通に接続され、ゲート電極に共通のゲート電圧が印加されるようになっている。このように複数のチャネル領域を形成して共有させることで、より駆動電流量を稼ぐことができる。

【0051】

図12は、本実施形態の変形例に関わる電界効果トランジスタの上面図である。ここではドレイン端を中心にチャネル領域を環状に配置している。中心部にはドレイン電極が配置されている。各チャネル領域のダブルゲートはそれぞれゲート配線によって共通のゲート電圧が印加されるようになっている。また、ソース領域も配線によって共通化されている。

【0052】

このように楔形の基体をドレイン領域が中心側になるように環状に配置することによって素子面積を小さくする上で有効である。

【0053】

また、電界効果トランジスタは、通常正孔の移動度が電子の移動より低くいために、p型電界効果トランジスタの駆動力がn型電界効果トランジスタの駆動力より低い。

【0054】

したがって図13に示すような環状に配置した電界効果トランジスタにおいて、n型電界効果トランジスタとp型電界効果トランジスタの数を調整することにより実効的なチャンネル幅を制御するようにすればよい。こうすることで駆動力の差の補正が可能となる。具体的には、p型電界効果トランジスタの数pをn型電界効果トランジスタの数nよりも多くすればよい。

【0055】

次に、本実施形態の電界効果トランジスタの製造方法について、図13乃至図19を用いて説明する。図では、2つの基体を具備する電界効果トランジスタの製造方法について示している。

【0056】

先ず、図14に示すように、埋め込み酸化膜11上にSiGeからなるSOI層12が形成されたSOI基板を準備する。ここではSOI層12の厚さを200nmである。

【0057】

図14中、(a)は、上面図、(b)はAA断面図、(c)はBB断面図である。以下図15乃至図20について同じである。

【0058】

図14に示すように、SOI基板のSOI層12上に酸化膜20を厚さ10nmCVD法により堆積し、この酸化膜20上にSiN膜21を厚さ10nm堆積する。次に、ソース領域及びドレイン領域となる部分にSiN膜21が残るようにエッチングをし、酸化膜20を露出させる。さらに、チャネル領域となる基体に酸化膜20が残るようにエッチングしてSOI層12を露出させる。

【0059】

このときチャネル領域となる基体を覆う酸化膜20の幅は240nm〜260nmとした。

【0060】

次に、図15に示すように、酸化膜20及びSiN膜21をマスクとして、ドライエッチングすることによって、チャネル領域の基体22を形成する。これによりソース領域23及びドレイン領域24の間にチャネル領域の基体22が形成される。このときチャネル領域の基体22の側面が(010)面となるよう、マスクを設計する。

【0061】

次に、図16に示すように、熱酸化を施すことによって、酸化膜25を形成する。このとき表面をSiN膜21で覆われたソース領域23及びドレイン領域24は酸化されないが、SiN膜21で覆われていないチャネル領域の基体22の表面は酸化される。

【0062】

すなわちチャネル領域の基体22は、上部はCVD酸化膜25で覆われ、側面は熱酸化膜26で覆われる。この熱酸化によりチャネル領域の基体22をおよそ100nm酸化する。その結果チャネル領域の基体22は、高さ100nm、幅20nm〜40nmとなる。

【0063】

ここでチャネル領域の基体22の上面には予め薄い酸化膜20が形成されていたため、側面の酸化の速度が、酸化開始時にわずかに速い。

【0064】

次に、図17に示すように、ソース領域23及びドレイン領域24を覆うSiN膜を除去した後に、燐のイオン注入をする。このときソース領域23及びドレイン領域24にはイオンは注入されるが、チャネル領域の基体22は熱酸化で形成された厚い酸化膜で覆われているため、イオンは注入されない。

【0065】

次に、図18に示すように、ソース領域23及びドレイン領域24上、チャネル領域の突起基体上の酸化膜を除去し、SiGe表面を露出させたのち、このSiGe層の表面を厚さ3nm熱酸化する。

【0066】

次に、チャネル領域の基体22の隙間を埋め込むようにCVD法により多結晶シリコン25を堆積する。ここで多結晶シリコン25にはホウ素を添加する。これはCVD法による堆積時に同時にホウ素を添加する方法でも、後からイオン注入により導入方法でも良い。

【0067】

次に、図20に示すように、ゲートの幅で多結晶シリコン25を残し、周囲を除去して、ソース領域23及びドレイン領域24、ゲート多結晶部にそれぞれ電極を形成して電界効果トランジスタが出来上がる。

【0068】

【発明の効果】

ゲート閉状のショートチャンネル効果の抑制をしながら、ゲート開状の駆動力を向上させることができる。

【図面の簡単な説明】

【図1】本発明の実施形態1に関わる電界効果トランジスタの斜視図。

【図2】(1)従来のダブルゲート構造の電界効果トランジスタ及び(2)本発明のダブルゲート構造の電界効果トランジスタについて、シミュレーションするための寸法を示した図。

【図3】ゲート電圧とドレイン電流の関係を示す特性図。

【図4】本発明の実施形態1に関わる電界効果トランジスタの製造方法を説明する各主要工程の断面図。

【図5】本発明の実施形態1に関わる電界効果トランジスタの製造方法を説明する各主要工程の断面図。

【図6】本発明の実施形態1に関わる電界効果トランジスタの製造方法を説明する各主要工程の断面図。

【図7】本発明の実施形態1に関わる電界効果トランジスタの製造方法を説明する各主要工程の断面図。

【図8】本発明の実施形態1に関わる電界効果トランジスタの製造方法を説明する各主要工程の断面図。

【図9】本発明の実施形態1に関わる電界効果トランジスタの製造方法を説明する各主要工程の断面図。

【図10】本発明の実施形態1に関わる電界効果トランジスタの製造方法を説明する各主要工程の断面図。

【図11】本発明の実施形態2に関わる電界効果トランジスタの斜視図。

【図12】本発明の実施形態2に関わる電界効果トランジスタの変形例。

【図13】本発明の実施形態2に関わる電界効果トランジスタの変形例。

【図14】本発明の実施形態2に関わる電界効果トランジスタの製造方法を説明する各主要工程の断面図。

【図15】本発明の実施形態2に関わる電界効果トランジスタの製造方法を説明する各主要工程の断面図。

【図16】本発明の実施形態2に関わる電界効果トランジスタの製造方法を説明する各主要工程の断面図。

【図17】本発明の実施形態2に関わる電界効果トランジスタの製造方法を説明する各主要工程の断面図。

【図18】本発明の実施形態2に関わる電界効果トランジスタの製造方法を説明する各主要工程の断面図。

【図19】本発明の実施形態2に関わる電界効果トランジスタの製造方法を説明する各主要工程の断面図。

【図20】本発明の実施形態2に関わる電界効果トランジスタの製造方法を説明する各主要工程の断面図。

【符号の説明】

1・・・基板

2・・・チャネル領域の基体

3・・・ゲート電極

4・・・ゲート電極

5・・・ソース領域

6・・・ドレイン領域[0001]

TECHNICAL FIELD OF THE INVENTION

The present invention relates to a field effect transistor.

[0002]

[Prior art]

Currently, the performance of ultra-high-speed MOSFETs (Metal Oxide Semiconductor Field Effect Transistors) has been improved by reducing the size of devices represented by the gate length (Lg).

[0003]

However, when the gate length is extremely short, even when the gate is closed, a short channel effect occurs in which electric charges leak due to a potential difference between the source region and the drain region. As a result, there is a problem that the switching operation cannot be performed in the field effect transistor.

[0004]

In order to suppress the short channel effect, a field effect transistor having a double gate structure in which a gate voltage is applied from both sides of a channel surface has been proposed.

[0005]

In the field effect transistor having the double gate structure, since the channel surface is sandwiched between the gate electrodes arranged at extremely small plane intervals, a sufficient voltage can be applied to the channel region, so that the leakage of electric charges is suppressed even in the gate closed state.

[0006]

However, the field effect transistor having the double gate structure has a problem that the amount of current flowing in the gate open state is small and the driving force is small since the thickness of the channel region is also small because the gate interval is extremely narrow.

[0007]

[Problems to be solved by the invention]

As described above, the conventional double-gate field-effect transistor has a problem that the short-channel effect is suppressed but the driving force is small.

[0008]

The present invention has been made in view of such a problem, and an object of the present invention is to provide a field effect transistor capable of suppressing a short channel effect and improving a driving force.

[0009]

[Means for Solving the Problems]

In order to achieve the above object, the present invention has a source region and a drain region, and between the source region and the drain region, a base having an opposing main surface,

A pair of gate electrodes provided on the main surface,

A distance between the pair of gate electrodes is larger on the source region side than on the drain region side.

[0010]

At this time, it is preferable that the base is formed of a semiconductor.

[0011]

Further, it is preferable that an interval between the pair of gate electrodes is gradually reduced from the source region side to the drain region side.

[0012]

In addition, it is preferable that a plurality of the field effect transistors are arranged in a ring shape such that the source region is located outside and the drain region is located inside .

[0013]

Further, the plurality of field effect transistors include a mixture of p-type and n-type, and it is preferable that p-type is more than n-type.

[0014]

Further, it is preferable that a drain electrode is provided at a central portion, and drain regions of the plurality of field effect transistors are arranged around the drain electrode.

[0015]

BEST MODE FOR CARRYING OUT THE INVENTION

Hereinafter, embodiments of the present invention will be described in detail with reference to the drawings. Note that the present invention is not limited to the following embodiments, and various selections can be made.

[0016]

(Embodiment 1)

FIG. 1 is a perspective view of a field-effect transistor according to

[0017]

As shown in FIG. 1, a wedge-

[0018]

The

[0019]

A

[0020]

The

[0021]

The specific dimensions of the

[0022]

The width of the

[0023]

Next, the relationship between the gate voltage and the drain current was obtained by simulation for a field-effect transistor in which the distance between the gate electrodes is gradually reduced from the source region to the drain region, and for a field-effect transistor in which the distance between the gate electrodes is constant. Is shown.

[0024]

As shown in FIG. 2, (1) a source region (impurity concentration of 1 × 10 20 cm −3 ), a channel region (impurity concentration of 1 × 10 15 cm −3 ), and a drain region (impurity concentration of 1 × 10 20 cm −3). ) Is 5 nm in width, and the width of the channel region (

[0025]

FIG. 3 is a characteristic diagram showing a relationship between a gate voltage and a drain current.

[0026]

As shown in FIG. 3, in the structure having a wide source side shown in (2), a characteristic in which the drain current is smaller in the region having a low gate voltage of 0.2 V or less than that of the normal structure shown in (1) is obtained. ing. That is, it is understood that the short channel effect in the closed state of the field effect transistor is suppressed.

[0027]

Also, in the structure having a wide source side shown in (2), the drain current amount is high in the region where the gate voltage is higher than 0.4 V as in the normal structure shown in (1). This suggests that the driving force can be improved.

[0028]

Thus, it can be said that the structure according to the present embodiment can suppress the short channel effect when the gate is closed, and sufficiently secure the drive current amount when the gate is open.

[0029]

As a comparison, when the channel width of (1) is reduced to about (2), the gate is closed and the short channel effect can be suppressed, but the driving current is smaller than that of (2). Expected to be very low.

[0030]

Next, a method for manufacturing the field-effect transistor according to the present embodiment will be described with reference to FIGS.

[0031]

The field-effect transistor according to the present embodiment uses, for example, a substrate in which an SOI (Silicon On Insulator) layer is laminated on a buried oxide film, forms a thermal oxide film mask on the substrate surface, and performs dry etching. Create a wedge-shaped projection. Next, thermal oxidation is performed at a high temperature to recover the surface of the projection damaged by the dry etching.

[0032]

In the course of this high-temperature thermal oxidation, the size of the protrusion becomes smaller. Thereafter, the oxide film mask on the surface is removed, and after the surface treatment is performed, the gate processing and the processing of the source region and the drain region are performed to complete the field effect transistor.

[0033]

There are two types of manufacturing methods given as examples this time. One is to perform gate processing and then process the source and drain regions. The other is to process the source region and the drain region first, and then perform the gate process.

[0034]

First, an example of a manufacturing method in which gate processing is performed first will be described.

[0035]

Here, a substrate in which a 100-nm-thick SOI layer is stacked over a 100-nm-thick buried oxide film is used. The thickness of the buried oxide film is not significantly restricted from the process. However, since a process of selectively etching the silicon layer on the buried oxide film using the difference in etching rate from the buried oxide film is used, if the thickness of the buried oxide film is several nm or less, attention must be paid to the process. Required.

[0036]

The thickness of the SOI layer is required to be greater than the height of the finally formed protrusion. Since the height of the projection is a value that determines the height Lw (FIG. 1) of the channel region, 50 nm or more is required. Although there is little restriction on the maximum value in terms of element design, the process is difficult if the height of the projection or the height ratio to the bottom surface (aspect ratio) is large, so that the maximum value is preferably 1 μm or less.

[0037]

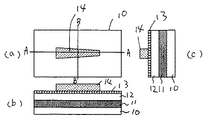

First, as shown in FIG. 4, an SOI substrate having a laminated structure of a

[0038]

4, (a) is a top view, (b) is an AA sectional view, and (c) is a BB sectional view. The same applies to FIGS. 5 to 10 below.

[0039]

As shown in FIG. 4, an

[0040]

Next, as shown in FIG. 5, the wedge-shaped

[0041]

In the silicon projection, a channel region and a source region and a drain region are formed later so as to sandwich the channel region. It is desirable that the side surface of the

[0042]

Next, as shown in FIG. 6, a thermal oxidation process is performed with the

[0043]

Next, the

[0044]

Next, as shown in FIG. 7,

[0045]

Next, as shown in FIG. 8, the gate of the

[0046]

Next, as shown in FIG. 9, a

[0047]

Next, as shown in FIG. 10, a

[0048]

(Embodiment 2)

Next, a field effect transistor according to

[0049]

FIG. 11 is a perspective view of a field-effect transistor in which three bases serving as wedge-shaped channel regions are formed side by side.

[0050]

As shown in FIG. 11, a source region and a drain region are commonly connected by wiring, and a common gate voltage is applied to a gate electrode. By forming and sharing a plurality of channel regions in this manner, the amount of drive current can be further increased.

[0051]

FIG. 12 is a top view of a field-effect transistor according to a modification of the present embodiment. Here, the channel region is arranged annularly around the drain end. A drain electrode is arranged at the center. A common gate voltage is applied to the double gate of each channel region by a gate wiring. The source region is also shared by the wiring.

[0052]

By arranging the wedge-shaped bases in a ring shape such that the drain region is on the center side, it is effective in reducing the element area.

[0053]

In a field-effect transistor, the driving force of a p-type field-effect transistor is lower than that of an n-type field-effect transistor because the mobility of holes is usually lower than that of electrons.

[0054]

Therefore, in a ring-shaped field effect transistor as shown in FIG. 13, the effective channel width may be controlled by adjusting the number of n-type field effect transistors and p-type field effect transistors. This makes it possible to correct the difference in driving force. Specifically, the number p of the p-type field effect transistors may be larger than the number n of the n-type field effect transistors.

[0055]

Next, a method for manufacturing the field-effect transistor of this embodiment will be described with reference to FIGS. The figure shows a method for manufacturing a field effect transistor having two substrates.

[0056]

First, as shown in FIG. 14, an SOI substrate having an

[0057]

14, (a) is a top view, (b) is an AA cross-sectional view, and (c) is a BB cross-sectional view. The same applies to FIGS. 15 to 20 below.

[0058]

As shown in FIG. 14, an

[0059]

At this time, the width of the

[0060]

Next, as shown in FIG. 15, the

[0061]

Next, as shown in FIG. 16, an

[0062]

That is, the base 22 in the channel region is covered with the

[0063]

Here, since the

[0064]

Next, as shown in FIG. 17, after removing the SiN film covering the

[0065]

Next, as shown in FIG. 18, after removing the oxide film on the

[0066]

Next,

[0067]

Next, as shown in FIG. 20, the

[0068]

【The invention's effect】

It is possible to improve the gate open driving force while suppressing the gate closed short channel effect.

[Brief description of the drawings]

FIG. 1 is a perspective view of a field-effect transistor according to a first embodiment of the present invention.

FIG. 2 is a diagram showing dimensions for simulation of (1) a conventional double-gate field effect transistor and (2) a double-gate field effect transistor of the present invention.

FIG. 3 is a characteristic diagram showing a relationship between a gate voltage and a drain current.

FIG. 4 is a sectional view of each main step for explaining the method for manufacturing the field-effect transistor according to the first embodiment of the present invention.

FIG. 5 is a sectional view of each main step for explaining the method for manufacturing the field-effect transistor according to the first embodiment of the present invention.

FIG. 6 is a sectional view of each main step for explaining the method for manufacturing the field-effect transistor according to the first embodiment of the present invention.

FIG. 7 is a sectional view of each main step for explaining the method for manufacturing the field-effect transistor according to the first embodiment of the present invention.

FIG. 8 is a sectional view of each main step for explaining the method for manufacturing the field effect transistor according to the first embodiment of the present invention.

FIG. 9 is a cross-sectional view of each main step for explaining the method for manufacturing the field-effect transistor according to the first embodiment of the present invention.

FIG. 10 is a sectional view of each main step for explaining the method for manufacturing the field-effect transistor according to the first embodiment of the present invention.

FIG. 11 is a perspective view of a field-effect transistor according to a second embodiment of the present invention.

FIG. 12 is a modified example of the field-effect transistor according to the second embodiment of the present invention.

FIG. 13 is a modification example of the field-effect transistor according to the second embodiment of the present invention.

FIG. 14 is a sectional view of each main step for explaining a method for manufacturing a field-effect transistor according to the second embodiment of the present invention.

FIG. 15 is a sectional view of each main step for explaining a method for manufacturing a field-effect transistor according to the second embodiment of the present invention.

FIG. 16 is a sectional view of each main step for explaining the method for manufacturing the field-effect transistor according to the second embodiment of the present invention.

FIG. 17 is a cross-sectional view of each main step for explaining the method for manufacturing the field-effect transistor according to the second embodiment of the present invention.

FIG. 18 is a sectional view of each main step for explaining a method for manufacturing a field-effect transistor according to the second embodiment of the present invention.

FIG. 19 is a sectional view of each main step for explaining the method for manufacturing the field effect transistor according to the second embodiment of the present invention.

FIG. 20 is a sectional view of each main step for explaining the method for manufacturing the field effect transistor according to the second embodiment of the present invention.

[Explanation of symbols]

DESCRIPTION OF

Claims (6)

前記主面に設けられた一対のゲート電極と具備し、

前記一対のゲート電極の間隔が、前記ソース領域側において前記ドレイン領域側よりも大きいことを特徴とする電界効果トランジスタ。A base having a source region and a drain region, and having a main surface facing each other between the source region and the drain region;

A pair of gate electrodes provided on the main surface,

A field effect transistor wherein a distance between the pair of gate electrodes is larger on the source region side than on the drain region side.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002097049A JP3605086B2 (en) | 2002-03-29 | 2002-03-29 | Field effect transistor |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002097049A JP3605086B2 (en) | 2002-03-29 | 2002-03-29 | Field effect transistor |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2003298063A JP2003298063A (en) | 2003-10-17 |

| JP3605086B2 true JP3605086B2 (en) | 2004-12-22 |

Family

ID=29387593

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002097049A Expired - Fee Related JP3605086B2 (en) | 2002-03-29 | 2002-03-29 | Field effect transistor |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3605086B2 (en) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6794718B2 (en) * | 2002-12-19 | 2004-09-21 | International Business Machines Corporation | High mobility crystalline planes in double-gate CMOS technology |

| WO2004090992A1 (en) * | 2003-04-09 | 2004-10-21 | Nec Corporation | Vertical misfet semiconductor device having high mobility silicon channel |

| KR100526889B1 (en) * | 2004-02-10 | 2005-11-09 | 삼성전자주식회사 | Fin field effect transistor structure |

| US7115920B2 (en) * | 2004-04-12 | 2006-10-03 | International Business Machines Corporation | FinFET transistor and circuit |

| JP5017795B2 (en) * | 2005-04-13 | 2012-09-05 | 日本電気株式会社 | Method for manufacturing field effect transistor |

| US7348642B2 (en) | 2005-08-03 | 2008-03-25 | International Business Machines Corporation | Fin-type field effect transistor |

| WO2011065210A1 (en) * | 2009-11-28 | 2011-06-03 | Semiconductor Energy Laboratory Co., Ltd. | Stacked oxide material, semiconductor device, and method for manufacturing the semiconductor device |

| EP3161872B1 (en) * | 2014-06-27 | 2023-09-06 | Tahoe Research, Ltd. | Multi-gate transistor with variably sized fin |

| US10134893B2 (en) * | 2017-02-22 | 2018-11-20 | International Business Machines Corporation | Fabrication of a vertical field effect transistor device with a modified vertical fin geometry |

| US11476350B2 (en) | 2017-07-12 | 2022-10-18 | Sony Semiconductor Solutions Corporation | Transistor and electronic device |

-

2002

- 2002-03-29 JP JP2002097049A patent/JP3605086B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2003298063A (en) | 2003-10-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3782021B2 (en) | Semiconductor device, semiconductor device manufacturing method, and semiconductor substrate manufacturing method | |

| TWI404145B (en) | Method for fabricating strained silicon-on-insulator structures and strained silicon-on-insulator structures formed thereby | |

| JP3543946B2 (en) | Field effect transistor and method of manufacturing the same | |

| JP4058751B2 (en) | Method for manufacturing field effect transistor | |

| JP3462301B2 (en) | Semiconductor device and manufacturing method thereof | |

| JPH1197693A (en) | Semiconductor device and manufacture thereof | |

| KR20050094576A (en) | Three dimensional cmos field effect transistor and method of fabricating the same | |

| JPH04102317A (en) | Manufacture of semiconductor device | |

| JPH02166762A (en) | Compact cmos device and | |

| JP3605086B2 (en) | Field effect transistor | |

| JP2000196090A (en) | Double-gate soi device and manufacture thereof | |

| JP2733909B2 (en) | Thin film transistor and method of manufacturing the same | |

| JP2008085357A (en) | Manufacturing method of fet | |

| JPH077773B2 (en) | Method for manufacturing semiconductor device | |

| JP2571004B2 (en) | Thin film transistor | |

| JP2827882B2 (en) | Method for manufacturing semiconductor device | |

| JP3420301B2 (en) | Method for manufacturing thin film transistor | |

| JPH113993A (en) | Semiconductor device and its manufacture | |

| JPH01283956A (en) | Semiconductor device and preparation thereof | |

| JPH10335660A (en) | Semiconductor device and manufacture thereof | |

| KR100263475B1 (en) | Semiconductor device and method for fabricating the same | |

| JPH0923013A (en) | Semiconductor element and its preparation | |

| JPH06177376A (en) | Manufacture of mos field-effect semiconductor device | |

| JP2519541B2 (en) | Semiconductor device | |

| JP2004063918A (en) | Lateral mos transistor |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20040426 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040511 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040628 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20040629 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20040928 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20040930 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20081008 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20081008 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091008 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101008 Year of fee payment: 6 |

|

| LAPS | Cancellation because of no payment of annual fees |