JP2008205399A - 半導体集積回路の設計方法 - Google Patents

半導体集積回路の設計方法 Download PDFInfo

- Publication number

- JP2008205399A JP2008205399A JP2007042743A JP2007042743A JP2008205399A JP 2008205399 A JP2008205399 A JP 2008205399A JP 2007042743 A JP2007042743 A JP 2007042743A JP 2007042743 A JP2007042743 A JP 2007042743A JP 2008205399 A JP2008205399 A JP 2008205399A

- Authority

- JP

- Japan

- Prior art keywords

- cell

- power supply

- semiconductor chip

- wiring

- integrated circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Semiconductor Integrated Circuits (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

Abstract

【課題】レイアウト設計において、電源強化を図りつつ、半導体チップのサイズの最適化、および設計時間の短縮化が図れるようにした半導体集積回路の設計方法の提供。

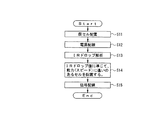

【解決手段】この発明は、半導体集積回路のレイアウト設計に係るものである。まず、半導体チップ上にセルを配置したのち、そのセルに対する電源配線を行う(S1、S2)。次に、電源配線上に生じる電圧降下を測定し、その測定結果に基づいてIRドロップ解析を行う(S3)。さらに、そのIRドロップの解析結果に基づき、半導体チップ上にすでに配置されているセルの配置位置を変更する(S4、S5)。その終了後に、半導体チップ上のセル間の信号配線を行う(S6)。

【選択図】図1

【解決手段】この発明は、半導体集積回路のレイアウト設計に係るものである。まず、半導体チップ上にセルを配置したのち、そのセルに対する電源配線を行う(S1、S2)。次に、電源配線上に生じる電圧降下を測定し、その測定結果に基づいてIRドロップ解析を行う(S3)。さらに、そのIRドロップの解析結果に基づき、半導体チップ上にすでに配置されているセルの配置位置を変更する(S4、S5)。その終了後に、半導体チップ上のセル間の信号配線を行う(S6)。

【選択図】図1

Description

本発明は、半導体集積回路(LSI)の設計方法に関するものである。

近年、半導体集積回路は、プロセスの微細化や低消費電力化に伴い動作電源電圧が下がってきており、また配線抵抗の増加も相まって、配線パターンによる電圧降下が問題になってきている。

すなわち、半導体集積回路に外部から供給される電圧は、その内部集積回路の動作による電力消費や電源配線抵抗によって、内部集積回路の中心部では電圧レベルが下がってしまうので、その低下を防止するために電源を強化する必要がある。

すなわち、半導体集積回路に外部から供給される電圧は、その内部集積回路の動作による電力消費や電源配線抵抗によって、内部集積回路の中心部では電圧レベルが下がってしまうので、その低下を防止するために電源を強化する必要がある。

この電源の強化のために、従来のレイアウト設計では、例えば半導体チップ上にセルを自動配置したのちに、自動配線を行い、この後にIRドロップを測定して電源の補強を図るようにしている。

また、内部集積回路内において、電源配線の本数を増やしたり、あるいは自動配置配線の終了後に電源補強をすることが難しいので、初期の電源配線の本数を多めにしておくなどの対策が採用されている。

また、内部集積回路内において、電源配線の本数を増やしたり、あるいは自動配置配線の終了後に電源補強をすることが難しいので、初期の電源配線の本数を多めにしておくなどの対策が採用されている。

さらに、半導体集積回路の電源の強化のために、以下の特許文献1や特許文献2に記載の発明が知られている。

特許文献1には、各給電線エリアに配置された基本回路セルの種類および個数に基づいて各給電線エリアに流れる電流量を算出し、その電流量に基づいて枝電源配線の配線幅を決定するようにした発明が開示されている。

特許文献1には、各給電線エリアに配置された基本回路セルの種類および個数に基づいて各給電線エリアに流れる電流量を算出し、その電流量に基づいて枝電源配線の配線幅を決定するようにした発明が開示されている。

特許文献2には、自動配置配線後に、機能セルの動作周波数と、実際の機能セルの出力容量から消費電流を算出し、各セル列ごとに各機能セルの電圧降下値を基準にして、電源の配線幅およびセル列の幅を最適にする発明が開示されている。

特開平8−23029号公報

特開2000−20576号公報

しかし、上記の従来技術には、以下のような不具合がある。

(1)電源補強を実施するためのスペースがない場合には、配置配線をやり直す必要があった。

(2)内部集積回路内の電源配線の本数を増やす場合には、電源配線として使用する領域にセルを配置することができないので、半導体チップのサイズが大きくなってしまう。

(3)電源配線の本数を多めにしておく場合には、半導体チップのサイズが大きくなる上に、余った分の本数は、自動的に削除することができず、その削除のために無駄な時間が発生してしまう。

(1)電源補強を実施するためのスペースがない場合には、配置配線をやり直す必要があった。

(2)内部集積回路内の電源配線の本数を増やす場合には、電源配線として使用する領域にセルを配置することができないので、半導体チップのサイズが大きくなってしまう。

(3)電源配線の本数を多めにしておく場合には、半導体チップのサイズが大きくなる上に、余った分の本数は、自動的に削除することができず、その削除のために無駄な時間が発生してしまう。

(4)特許文献1の発明では、各給電エリア内において電源配線の幅を最適化できるが、電源配線の幅が太くなる給電エリアでは、その面積を大きくしなければならない事態が発生し、その結果、半導体チップのサイズが大きくなってしまう。

(5)特許文献2の発明では、電源の配線幅やセル列の幅を最適にできるが、電源の配線幅が太くなる場合には、その結果、半導体チップのサイズが大きくなってしまう。

そこで、本発明の目的は、上記の点に鑑み、レイアウト設計において、電源強化を図りつつ、半導体チップのサイズの最適化、および設計時間の短縮化が図れるようにした半導体集積回路の設計方法を提供することにある。

(5)特許文献2の発明では、電源の配線幅やセル列の幅を最適にできるが、電源の配線幅が太くなる場合には、その結果、半導体チップのサイズが大きくなってしまう。

そこで、本発明の目的は、上記の点に鑑み、レイアウト設計において、電源強化を図りつつ、半導体チップのサイズの最適化、および設計時間の短縮化が図れるようにした半導体集積回路の設計方法を提供することにある。

上記の課題を解決し本発明の目的を達成するために、各発明は、以下のような構成からなる。

第1の発明は、半導体集積回路の設計方法であって、半導体チップ上にセルを配置したのち、そのセルに対する電源配線を行う第1ステップと、前記電源配線上に生じる電圧降下を測定し、その測定結果に基づいてIRドロップ解析を行う第2ステップと、前記IRドロップの解析結果に基づき、前記半導体チップ上にすでに配置されているセルの配置位置を変更する第3ステップと、この第3ステップの終了後に、前記半導体チップ上のセル間の信号配線を行う第4ステップと、からなる。

第1の発明は、半導体集積回路の設計方法であって、半導体チップ上にセルを配置したのち、そのセルに対する電源配線を行う第1ステップと、前記電源配線上に生じる電圧降下を測定し、その測定結果に基づいてIRドロップ解析を行う第2ステップと、前記IRドロップの解析結果に基づき、前記半導体チップ上にすでに配置されているセルの配置位置を変更する第3ステップと、この第3ステップの終了後に、前記半導体チップ上のセル間の信号配線を行う第4ステップと、からなる。

第2の発明は、第1の発明において、前記第2ステップでは、前記電圧降下の測定値に応じて前記半導体チップ上の領域を分割し、前記第3ステップでは、前記分割された領域のうちの任意の領域の使用効率を求め、この求めた使用効率に基づいて前記領域内におけるセルの配置の疎密を変更するために、前記領域にすでに配置されているセルの配置位置を変更する。

第3の発明は、半導体集積回路の設計方法であって、半導体チップ上に所定の能力のセルを配置したのち、そのセルに対する電源配線を行う第1ステップと、前記電源配線上に生じる電圧降下を測定し、その測定結果に基づいてIRドロップ解析を行う第2ステップと、前記IRドロップの解析結果に基づき、前記半導体チップ上にすでに配置されているセルを、その能力の異なるセルに変更する第3ステップと、この第3ステップの終了後に、前記半導体チップ上のセル間の信号配線を行う第4ステップと、からなる。

第4の発明は、第3の発明において、前記第2ステップでは、前記電圧降下の測定値に応じて前記半導体チップ上の領域を分割し、前記第3ステップでは、前記分割された領域のうち、電圧降下の大きな領域はすでに配置されているセルをそれよりも能力の大きセルに変更し、電圧降下の小さな領域はすでに配置されているセルをそれよりも能力の小さなセルに変更する。

第5の発明は、半導体集積回路の設計方法であって、半導体チップ上にセルを配置したのち、そのセルに対する電源配線を行う第1ステップと、前記電源配線上に生じる電圧降下を測定し、その測定結果に基づいてIRドロップ解析を行う第2ステップと、前記IRドロップの解析結果に基づき、前記半導体チップ上にすでに配線されている電源配線の配線密度を変更する第3ステップと、この第3ステップの終了後に、前記半導体チップ上に仮に配置されているセル間の信号配線を行う第4ステップと、からなる。

第6の発明は、第5の発明において、前記第2ステップでは、前記電圧降下の測定値に応じて前記半導体チップ上の領域を分割し、前記第3ステップでは、前記分割された領域のうち、電圧降下の大きな領域はすでに配線されている電源配線をそれよりも配線密度が低くなるように変更し、電圧降下の小さな領域はすでに配線されている電源配線をそれよりも配線密度が高くなるように変更する。

このような本発明によれば、レイアウト設計において、電源強化を図りつつ、半導体チップのサイズの最適化、および設計時間の短縮化が図れる。

このような本発明によれば、レイアウト設計において、電源強化を図りつつ、半導体チップのサイズの最適化、および設計時間の短縮化が図れる。

以下、本発明の実施形態について、図面を参照して説明する。

(第1実施形態)

本発明の半導体集積回路の設計方法の第1実施形態について、図1〜図3を参照して説明する。

この第1実施形態に係る設計方法は、半導体集積回路のレイアウト設計に係るものであり、コンピュータの支援に基づく自動配置配線システムを利用して、図1に示す手順で行うようにしたものである。

(第1実施形態)

本発明の半導体集積回路の設計方法の第1実施形態について、図1〜図3を参照して説明する。

この第1実施形態に係る設計方法は、半導体集積回路のレイアウト設計に係るものであり、コンピュータの支援に基づく自動配置配線システムを利用して、図1に示す手順で行うようにしたものである。

まず、半導体チップ上に、コンピュータに登録されているセルを仮に(一時的に)配置する(ステップS1)。これにより、半導体チップ上の所望の各位置に、複数のセルがそれぞれ配置される。

次に、その複数のセルに対してそれぞれ電源配線が行われる(ステップS2)。これにより、複数の各セルは、所定の電源配線とそれぞれ接続される。

さらに、半導体チップ上に配線された電源配線上に生じる電圧降下(IRドロップ)を測定し、この測定結果に基づいてIRドロップ解析を行う(ステップS3)。このIRドロップ解析の一例を示すと、コンピュータの表示画面には、図2に示すような図が表示される。

次に、その複数のセルに対してそれぞれ電源配線が行われる(ステップS2)。これにより、複数の各セルは、所定の電源配線とそれぞれ接続される。

さらに、半導体チップ上に配線された電源配線上に生じる電圧降下(IRドロップ)を測定し、この測定結果に基づいてIRドロップ解析を行う(ステップS3)。このIRドロップ解析の一例を示すと、コンピュータの表示画面には、図2に示すような図が表示される。

図2は、半導体チップ上におけるIRドロップの大小の分布を等高線で表現し、半導体チップを領域A〜Gに分割したものである。領域AがIRドロップが最大で、領域B、領域C、領域D、領域E、領域Fの順でIRドロップが下がっていき、領域GがIRドロップが最小である。

次に、IRドロップ値に応じて分割された領域A〜Gのうち任意の領域について、セルの使用効率を計算し(ステップS4)、この計算結果をコンピュータの表示画面に表示する。ここで、使用効率を任意の領域について求めるのは、領域によっては後述のセルの配置位置の変更ができない領域があるからである。この任意の領域については、設計者が表示画面などを参照して指定する。

上記のように計算したセルの使用効率の一例を示すと、図3に示すようになる。領域A〜Gにおける使用効率、図3に示すように、20〜50%になる。

なお、上記のセルの使用効率は、次の(1)式により求める。

次に、IRドロップ値に応じて分割された領域A〜Gのうち任意の領域について、セルの使用効率を計算し(ステップS4)、この計算結果をコンピュータの表示画面に表示する。ここで、使用効率を任意の領域について求めるのは、領域によっては後述のセルの配置位置の変更ができない領域があるからである。この任意の領域については、設計者が表示画面などを参照して指定する。

上記のように計算したセルの使用効率の一例を示すと、図3に示すようになる。領域A〜Gにおける使用効率、図3に示すように、20〜50%になる。

なお、上記のセルの使用効率は、次の(1)式により求める。

セルの使用効率=(領域内に配置されたセルの合計)/(領域内に配置可能なベーシックセルの全個数)・・・(1)

図3によれば、IRドロップの大きな領域ほど、セルの使用効率が小さな値になっていることがわかる。

次に、IRドロップ値に応じてセルの配置の疎密を変更するために、すでに配置されているセルの配置位置を変更(修正)する(ステップS5)。すなわち、IRドロップ値の大きな領域(セルの使用効率が低い領域)は、セルの使用効率が相対的に高くなり、IRドロップ値の小さな領域(セルの使用効率が高い領域)は、セルの使用効率が相対的に低くなるように、セルの配置替えを行う。

次に、IRドロップ値に応じてセルの配置の疎密を変更するために、すでに配置されているセルの配置位置を変更(修正)する(ステップS5)。すなわち、IRドロップ値の大きな領域(セルの使用効率が低い領域)は、セルの使用効率が相対的に高くなり、IRドロップ値の小さな領域(セルの使用効率が高い領域)は、セルの使用効率が相対的に低くなるように、セルの配置替えを行う。

このようなセルの配置替えによって、領域にかかわらず、IRドロップ値をほぼ一律(均一)にすることができ、電源の強化を図ることができる。

次に、セルの配置替えが終了したら、そのセル間の配線(信号配線)を行う(ステップS6)。これにより、複数のセルは、信号配線によって所定の接続が行われる。

以上説明した第1実施形態によれば、半導体集積回路のレイアウト設計の際に、電源補強を図りつつ、設計時間の短縮化を図ることができる。

次に、セルの配置替えが終了したら、そのセル間の配線(信号配線)を行う(ステップS6)。これにより、複数のセルは、信号配線によって所定の接続が行われる。

以上説明した第1実施形態によれば、半導体集積回路のレイアウト設計の際に、電源補強を図りつつ、設計時間の短縮化を図ることができる。

また、第1実施形態によれば、半導体チップ上のどこにおいてもIRドロップ値をほぼ一律にすることができるので、遅延ライブラリの精度が向上する。すなわち、歩留りの向上、信号のタイミングの合わせ込みを過剰に実施することがなく、しかも半導体チップの大きさの最適化が図れる。

さらに、第1実施形態によれば、電源配線の本数を予め多く配線しておく必要がないので、チップサイズを最適化することができるとともに、配線効率が向上してタイミング解析の際の収束性が向上する。

さらに、第1実施形態によれば、電源配線の本数を予め多く配線しておく必要がないので、チップサイズを最適化することができるとともに、配線効率が向上してタイミング解析の際の収束性が向上する。

(第2実施形態)

本発明の半導体集積回路の設計方法の第2実施形態について、図4を参照しながら説明する。

この第2実施形態は、第1実施形態において、セルの配置を変更した場合に、この変更に伴って配置配線ができない場合があり、これに対処するようにしたものである。

したがって、この第2実施形態は、図4に示すように、ステップS1〜S6までの各処理は、第1実施形態のステップS1〜S6までの各処理と同様であり、ステップS7、S8の処理を追加したものである。

本発明の半導体集積回路の設計方法の第2実施形態について、図4を参照しながら説明する。

この第2実施形態は、第1実施形態において、セルの配置を変更した場合に、この変更に伴って配置配線ができない場合があり、これに対処するようにしたものである。

したがって、この第2実施形態は、図4に示すように、ステップS1〜S6までの各処理は、第1実施形態のステップS1〜S6までの各処理と同様であり、ステップS7、S8の処理を追加したものである。

この第2実施形態では、ステップS6においてセル間の信号配線を行うが、このときに、信号配線をすることができずに、配線層の増加が必要か否かがコンピュータにより判断される(ステップS7)。この判断の結果、信号配線が終了して配線層の増加が必要でない場合には、その処理を終了する。

一方、信号配線をすることができずに、配線層の増加が必要な場合にはステップS8に進む。ステップS8では、配線層を増加し、その配線層を用いて必要な配線を行って、処理を終了する。

以上説明した第2実施形態によれば、第1実施形態と同様の作用効果を実現することができる。

一方、信号配線をすることができずに、配線層の増加が必要な場合にはステップS8に進む。ステップS8では、配線層を増加し、その配線層を用いて必要な配線を行って、処理を終了する。

以上説明した第2実施形態によれば、第1実施形態と同様の作用効果を実現することができる。

(第3実施形態)

本発明の半導体集積回路の設計方法の第3実施形態について、図5を参照しながら説明する。

この第3実施形態に係る設計方法は、半導体集積回路のレイアウト設計に係るものであり、コンピュータの支援に基づく自動配置配線システムを利用して、図5に示す手順で行うようにしたものである。

まず、半導体チップ上に、コンピュータに登録されているセルを仮に(一時的に)配置する(ステップS11)。これにより、半導体チップ上の所望の各位置に、複数のセルがそれぞれ配置される。

本発明の半導体集積回路の設計方法の第3実施形態について、図5を参照しながら説明する。

この第3実施形態に係る設計方法は、半導体集積回路のレイアウト設計に係るものであり、コンピュータの支援に基づく自動配置配線システムを利用して、図5に示す手順で行うようにしたものである。

まず、半導体チップ上に、コンピュータに登録されているセルを仮に(一時的に)配置する(ステップS11)。これにより、半導体チップ上の所望の各位置に、複数のセルがそれぞれ配置される。

ここで、仮に配置される複数のセルは、その論理回路(論理機能)ごとに、その能力が異なるものが複数個ずつ予め用意されている。すなわち、各セルは、その機能が同じであって、例えば駆動速度(駆動能力)が大、中、および小と異なるものが、3つずつ用意されている。そして、上記の複数のセルの配置の際には、各セルはそのうちの駆動速度が中のものが配置されるものとする。

次に、その複数のセルに対してそれぞれ電源配線が行われる(ステップS12)。これにより、複数の各セルは、所定の電源配線とそれぞれ接続される。

さらに、上記の配線の終了した電源配線上に生じる電圧降下を測定し、この測定結果に基づいてIRドロップ解析を行う(ステップS13)。このIRドロップ解析の一例を示すと、図2に示すようになる。これにより、半導体チップは、IRドロップに応じて複数に分割される。

さらに、上記の配線の終了した電源配線上に生じる電圧降下を測定し、この測定結果に基づいてIRドロップ解析を行う(ステップS13)。このIRドロップ解析の一例を示すと、図2に示すようになる。これにより、半導体チップは、IRドロップに応じて複数に分割される。

次に、IRドロップ値に応じて、前記IRドロップの解析結果に基づき、前記半導体チップ上にすでに配置されているセルを、その能力の異なるセルに変更する(ステップS14)。すなわち、上記の分割された領域のうち、電圧降下の大きな領域はすでに配置されているセルをそれよりも駆動速度の大きセルに変更し(置き換え)、電圧降下の小さな領域はすでに配置されているセルをそれよりも駆動速度の小さなセルに変更する。

このようなセルの配置替えによって、IRドロップ値の差異にかかわらず、セルの駆動速度を一律にすることができる。これは、電源強化したことと、等価になる。

次に、セルの配置替えが終了したら、そのセル間の配線(信号配線)を行う(ステップS15)。これにより、複数のセルは、信号配線によって所定の接続が行われる。

このようなセルの配置替えによって、IRドロップ値の差異にかかわらず、セルの駆動速度を一律にすることができる。これは、電源強化したことと、等価になる。

次に、セルの配置替えが終了したら、そのセル間の配線(信号配線)を行う(ステップS15)。これにより、複数のセルは、信号配線によって所定の接続が行われる。

以上説明した第3実施形態によれば、半導体集積回路のレイアウト設計の際に、電源補強を図りつつ、設計時間の短縮化を図ることができる。

また、第3実施形態によれば、半導体チップ上のどこ配置されるセルであっても駆動速度を一律にすることができるので、遅延ライブラリの精度が向上する。すなわち、歩留りの向上、タイミングの合わせ込みを過剰に実施することがなく、しかも半導体チップの大きさの最適化が図れる。

さらに、第3実施形態によれば、電源配線の本数を予め多く配線しておく必要がないので、チップサイズを最適化することができるとともに、配線効率が向上してタイミング解析の際の収束性が向上する。

また、第3実施形態によれば、半導体チップ上のどこ配置されるセルであっても駆動速度を一律にすることができるので、遅延ライブラリの精度が向上する。すなわち、歩留りの向上、タイミングの合わせ込みを過剰に実施することがなく、しかも半導体チップの大きさの最適化が図れる。

さらに、第3実施形態によれば、電源配線の本数を予め多く配線しておく必要がないので、チップサイズを最適化することができるとともに、配線効率が向上してタイミング解析の際の収束性が向上する。

(第4実施形態)

本発明の半導体集積回路の設計方法の第4実施形態について、図6〜図9を参照して説明する。

この第4実施形態に係る設計方法は、半導体集積回路のレイアウト設計に係るものであり、コンピュータの支援に基づく自動配置配線システムを利用して、図6に示す手順で行うようにしたものである。

まず、半導体チップ上に、コンピュータに登録されているセルを仮に(一時的に)配置する(ステップS21)。これにより、半導体チップ上の所望の各位置に、複数のセルがそれぞれ配置される。

本発明の半導体集積回路の設計方法の第4実施形態について、図6〜図9を参照して説明する。

この第4実施形態に係る設計方法は、半導体集積回路のレイアウト設計に係るものであり、コンピュータの支援に基づく自動配置配線システムを利用して、図6に示す手順で行うようにしたものである。

まず、半導体チップ上に、コンピュータに登録されているセルを仮に(一時的に)配置する(ステップS21)。これにより、半導体チップ上の所望の各位置に、複数のセルがそれぞれ配置される。

次に、その複数のセルに対してそれぞれ電源配線が行われる(ステップS22)。これにより、複数の各セルは、所定の電源配線とそれぞれ接続される。ここで、半導体チップ上における、セルと電源配線の配置例を示すと、図7に示すようになる。

図7において、縦横方向に配置されるのが電源配線であり、このうち横方向に配置される細めの電源配線11が例えばメタル第1層に配置され、縦方向に配置される太めの電源配線12が例えばメタル第1層に配置される。

図7において、縦横方向に配置されるのが電源配線であり、このうち横方向に配置される細めの電源配線11が例えばメタル第1層に配置され、縦方向に配置される太めの電源配線12が例えばメタル第1層に配置される。

電源配線11、12のうち、斜線部で示すものは、その交点でスルーホールにより接続され、電源電圧VDD用に使用される。また、斜線部以外で示すものは、その交点でスルーホールにより接続され、電源電圧VSS用に使用される。さらに、図7において、方形状のブロックはセル13を表している。

次に、半導体チップ上に配線された電源配線上に生じる電圧降下(IRドロップ)を測定し、この測定結果に基づいてIRドロップ解析を行う(ステップS23)。このIRドロップ解析の一例を示すと、図8に示すようになる。これにより、半導体チップは、IRドロップの大きさに応じて領域A〜Cに分割される。

次に、半導体チップ上に配線された電源配線上に生じる電圧降下(IRドロップ)を測定し、この測定結果に基づいてIRドロップ解析を行う(ステップS23)。このIRドロップ解析の一例を示すと、図8に示すようになる。これにより、半導体チップは、IRドロップの大きさに応じて領域A〜Cに分割される。

次に、IRドロップ値に応じて、半導体チップ上にすでに配線されている電源配線の配線密度を変更し、電源配線の再実施(再配置)を行う(ステップS24)。

すなわち、分割された領域A〜Cのうち、IRドロップ(電圧降下)の大きな領域A内では、すでに配線されている電源配線を、それよりも配線密度が低くなるように変更をする。具体的には、領域A内では、電源配線の配置間隔を広くし(電源配線の本数を減らすことに相当)、または電源配線それ自体の幅を狭くする。

すなわち、分割された領域A〜Cのうち、IRドロップ(電圧降下)の大きな領域A内では、すでに配線されている電源配線を、それよりも配線密度が低くなるように変更をする。具体的には、領域A内では、電源配線の配置間隔を広くし(電源配線の本数を減らすことに相当)、または電源配線それ自体の幅を狭くする。

一方、IRドロップの小さな領域Cは、すでに配線されている電源配線をそれよりも配線密度が高くなるように変更する。具体的には、領域Cでは、電源配線の配置間隔を狭くし(電源配線の本数を増やすことに相当)、または電源配線それ自体の幅を広くする。

このような考え方で再実施した電源配線の一例を、図9に示す。この例は、図8のIRドロップに対応して作成したものであり、半導体チップのうち、IRドロップが小さい外周部側ほど電源配線の密度が高く、IRドロップが大きな中心部側ほど電源配線の密度が疎になっている。そして、電源配線の疎密の調整は、電源配線の幅は一定とし、その配置間隔を調整することにより実現している。

このような考え方で再実施した電源配線の一例を、図9に示す。この例は、図8のIRドロップに対応して作成したものであり、半導体チップのうち、IRドロップが小さい外周部側ほど電源配線の密度が高く、IRドロップが大きな中心部側ほど電源配線の密度が疎になっている。そして、電源配線の疎密の調整は、電源配線の幅は一定とし、その配置間隔を調整することにより実現している。

ここで、図9において、電源配線は、横方向に配置される電源配線が例えばメタル第1層に配置され、縦方向に配置される電源配線が例えばメタル第1層に配置されている。

このような電源配線の変更によって、領域にかかわらず、IRドロップ値をほぼ一律(均一)にすることができ、電源の強化を図ることができる。

次に、電源配線の変更が終了したら、その変更に伴ってセルの配置の修正を行い、それが終了すると、セル間の配線(信号配線)を行う(ステップS25)。これにより、複数のセルは、信号配線によって所定の接続が行われる。

このような電源配線の変更によって、領域にかかわらず、IRドロップ値をほぼ一律(均一)にすることができ、電源の強化を図ることができる。

次に、電源配線の変更が終了したら、その変更に伴ってセルの配置の修正を行い、それが終了すると、セル間の配線(信号配線)を行う(ステップS25)。これにより、複数のセルは、信号配線によって所定の接続が行われる。

以上説明した第4実施形態によれば、半導体集積回路のレイアウト設計の際に、電源補強を図りつつ、設計時間の短縮化を図ることができる。

また、第4実施形態によれば、半導体チップ上のどこにおいてもIRドロップ値をほぼ一律にすることができるので、遅延ライブラリの精度が向上する。すなわち、歩留りの向上、タイミングの合わせ込みを過剰に実施することがなく、しかも半導体チップの大きさの最適化が図れる。

さらに、第4実施形態によれば、電源配線の本数を予め多く配線しておく必要がないので、チップサイズを最適化することができるとともに、配線効率が向上してタイミング解析の際の収束性が向上する。

また、第4実施形態によれば、半導体チップ上のどこにおいてもIRドロップ値をほぼ一律にすることができるので、遅延ライブラリの精度が向上する。すなわち、歩留りの向上、タイミングの合わせ込みを過剰に実施することがなく、しかも半導体チップの大きさの最適化が図れる。

さらに、第4実施形態によれば、電源配線の本数を予め多く配線しておく必要がないので、チップサイズを最適化することができるとともに、配線効率が向上してタイミング解析の際の収束性が向上する。

11、12・・・電源配線、13・・・セル

Claims (6)

- 半導体集積回路の設計方法であって、

半導体チップ上にセルを配置したのち、そのセルに対する電源配線を行う第1ステップと、

前記電源配線上に生じる電圧降下を測定し、その測定結果に基づいてIRドロップ解析を行う第2ステップと、

前記IRドロップの解析結果に基づき、前記半導体チップ上にすでに配置されているセルの配置位置を変更する第3ステップと、

この第3ステップの終了後に、前記半導体チップ上のセル間の信号配線を行う第4ステップと、

からなることを特徴とする半導体集積回路の設計方法。 - 前記第2ステップでは、前記電圧降下の測定値に応じて前記半導体チップ上の領域を分割し、

前記第3ステップでは、前記分割された領域のうちの任意の領域の使用効率を求め、この求めた使用効率に基づいて前記領域内におけるセルの配置の疎密を変更するために、前記領域にすでに配置されているセルの配置位置を変更することを特徴とする請求項1に記載の半導体集積回路の設計方法。 - 半導体集積回路の設計方法であって、

半導体チップ上に所定の能力のセルを配置したのち、そのセルに対する電源配線を行う第1ステップと、

前記電源配線上に生じる電圧降下を測定し、その測定結果に基づいてIRドロップ解析を行う第2ステップと、

前記IRドロップの解析結果に基づき、前記半導体チップ上にすでに配置されているセルを、その能力の異なるセルに変更する第3ステップと、

この第3ステップの終了後に、前記半導体チップ上のセル間の信号配線を行う第4ステップと、

からなることを特徴とする半導体集積回路の設計方法。 - 前記第2ステップでは、前記電圧降下の測定値に応じて前記半導体チップ上の領域を分割し、

前記第3ステップでは、前記分割された領域のうち、電圧降下の大きな領域はすでに配置されているセルをそれよりも能力の大きセルに変更し、電圧降下の小さな領域はすでに配置されているセルをそれよりも能力の小さなセルに変更することを特徴とする請求項3に記載の半導体集積回路の設計方法。 - 半導体集積回路の設計方法であって、

半導体チップ上にセルを配置したのち、そのセルに対する電源配線を行う第1ステップと、

前記電源配線上に生じる電圧降下を測定し、その測定結果に基づいてIRドロップ解析を行う第2ステップと、

前記IRドロップの解析結果に基づき、前記半導体チップ上にすでに配線されている電源配線の配線密度を変更する第3ステップと、

この第3ステップの終了後に、前記半導体チップ上に仮に配置されているセル間の信号配線を行う第4ステップと、

からなることを特徴とする半導体集積回路の設計方法。 - 前記第2ステップでは、前記電圧降下の測定値に応じて前記半導体チップ上の領域を分割し、

前記第3ステップでは、前記分割された領域のうち、電圧降下の大きな領域はすでに配線されている電源配線をそれよりも配線密度が低くなるように変更し、電圧降下の小さな領域はすでに配線されている電源配線をそれよりも配線密度が高くなるように変更することを特徴とする請求項5に記載の半導体集積回路の設計方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007042743A JP2008205399A (ja) | 2007-02-22 | 2007-02-22 | 半導体集積回路の設計方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007042743A JP2008205399A (ja) | 2007-02-22 | 2007-02-22 | 半導体集積回路の設計方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2008205399A true JP2008205399A (ja) | 2008-09-04 |

Family

ID=39782534

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007042743A Pending JP2008205399A (ja) | 2007-02-22 | 2007-02-22 | 半導体集積回路の設計方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2008205399A (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011258952A (ja) * | 2010-06-09 | 2011-12-22 | Lsi Corp | パワーグリッド最適化 |

| JP2022000902A (ja) * | 2016-11-18 | 2022-01-04 | クゥアルコム・インコーポレイテッドQualcomm Incorporated | 集積回路のための適応的多階層電力分配グリッド |

-

2007

- 2007-02-22 JP JP2007042743A patent/JP2008205399A/ja active Pending

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011258952A (ja) * | 2010-06-09 | 2011-12-22 | Lsi Corp | パワーグリッド最適化 |

| JP2022000902A (ja) * | 2016-11-18 | 2022-01-04 | クゥアルコム・インコーポレイテッドQualcomm Incorporated | 集積回路のための適応的多階層電力分配グリッド |

| JP7261273B2 (ja) | 2016-11-18 | 2023-04-19 | クゥアルコム・インコーポレイテッド | 集積回路のための適応的多階層電力分配グリッド |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7503026B2 (en) | Cell, standard cell, standard cell library, a placement method using standard cell, and a semiconductor integrated circuit | |

| US8219965B2 (en) | Layout design method of semiconductor integrated circuit including regenerating a cell layout to set first and second distances and generating library data | |

| US7795943B2 (en) | Integrated circuit device and layout design method therefor | |

| JP4860123B2 (ja) | デカップリング容量の配置方法 | |

| JP2002334933A (ja) | タップ・セルを有する集積回路及び集積回路にタップ・セルを配置するための方法 | |

| US7612599B2 (en) | Semiconductor device | |

| US7650584B2 (en) | Application specific semiconductor integrated circuit and its manufacturing method thereof | |

| JP2011034291A (ja) | 半導体集積回路の設計方法、設計プログラム、設計支援装置、及び半導体集積回路 | |

| JP3971033B2 (ja) | レイアウトデータ作成方法、レイアウトデータ作成装置、及び、記録媒体 | |

| JP2001306641A (ja) | 半導体集積回路の自動配置配線方法 | |

| JP2007234777A (ja) | 半導体集積回路装置およびその設計方法 | |

| JP2008205399A (ja) | 半導体集積回路の設計方法 | |

| JP2009199467A (ja) | 集積回路の設計支援装置、集積回路の設計支援方法、集積回路の設計支援プログラム、及びこのプログラムが記録された記録媒体 | |

| US20100138803A1 (en) | Apparatus and method of supporting design of semiconductor integrated circuit | |

| JP2006155182A (ja) | 半導体集積回路の設計方法および設計プログラム | |

| JP2006261458A (ja) | クロックツリー安定化装置、および半導体装置 | |

| JP2007088151A (ja) | 半導体集積回路の電源配線方法 | |

| JP2007103579A (ja) | 半導体集積回路装置、並びに半導体集積回路装置における電源及びグランド配線レイアウト方法 | |

| JP2001308190A (ja) | 半導体集積回路のレイアウト方法 | |

| JP2000020576A (ja) | 電源最適化自動配置配線方法及びその方法を用いた電源最適化自動配置配線装置 | |

| US8726221B2 (en) | Topology density aware flow (TDAF) | |

| JP2001203272A (ja) | 半導体集積回路のレイアウト設計方法 | |

| JP4523290B2 (ja) | セルレイアウト、半導体集積回路装置、半導体集積回路の設計方法並びに半導体集積回路の半導体製造方法 | |

| JP2011107950A (ja) | 半導体集積回路の設計方法および半導体集積回路設計支援装置 | |

| JP2004055873A (ja) | 半導体集積回路装置およびその設計方法 |