JP2008066562A - 半導体装置およびその製造方法 - Google Patents

半導体装置およびその製造方法 Download PDFInfo

- Publication number

- JP2008066562A JP2008066562A JP2006243844A JP2006243844A JP2008066562A JP 2008066562 A JP2008066562 A JP 2008066562A JP 2006243844 A JP2006243844 A JP 2006243844A JP 2006243844 A JP2006243844 A JP 2006243844A JP 2008066562 A JP2008066562 A JP 2008066562A

- Authority

- JP

- Japan

- Prior art keywords

- film

- gate electrode

- gate

- gate electrodes

- columnar

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Abandoned

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 75

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 54

- 239000000758 substrate Substances 0.000 claims abstract description 36

- 239000004020 conductor Substances 0.000 claims description 4

- 239000011810 insulating material Substances 0.000 claims 1

- 229910052751 metal Inorganic materials 0.000 abstract description 10

- 239000002184 metal Substances 0.000 abstract description 10

- 230000003071 parasitic effect Effects 0.000 abstract description 10

- 239000012212 insulator Substances 0.000 abstract description 3

- 239000010408 film Substances 0.000 description 210

- 238000000034 method Methods 0.000 description 43

- 239000011229 interlayer Substances 0.000 description 32

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 23

- 229910052710 silicon Inorganic materials 0.000 description 23

- 239000010703 silicon Substances 0.000 description 23

- 239000013039 cover film Substances 0.000 description 17

- 229910021334 nickel silicide Inorganic materials 0.000 description 17

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 17

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 15

- 239000010410 layer Substances 0.000 description 13

- 229910052581 Si3N4 Inorganic materials 0.000 description 11

- 238000001459 lithography Methods 0.000 description 11

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 11

- 239000012535 impurity Substances 0.000 description 10

- 238000005530 etching Methods 0.000 description 9

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 8

- 238000002955 isolation Methods 0.000 description 8

- 229910052814 silicon oxide Inorganic materials 0.000 description 8

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 7

- 238000001312 dry etching Methods 0.000 description 7

- 230000003647 oxidation Effects 0.000 description 7

- 238000007254 oxidation reaction Methods 0.000 description 7

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 6

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 5

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 5

- 229910052785 arsenic Inorganic materials 0.000 description 5

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 5

- 229910052796 boron Inorganic materials 0.000 description 5

- 238000005468 ion implantation Methods 0.000 description 5

- 150000002500 ions Chemical class 0.000 description 5

- 229910052698 phosphorus Inorganic materials 0.000 description 5

- 239000011574 phosphorus Substances 0.000 description 5

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 4

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 4

- 230000015572 biosynthetic process Effects 0.000 description 4

- 230000000694 effects Effects 0.000 description 3

- 230000001590 oxidative effect Effects 0.000 description 3

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 2

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 2

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 2

- 239000013078 crystal Substances 0.000 description 2

- 238000000227 grinding Methods 0.000 description 2

- 229910000449 hafnium oxide Inorganic materials 0.000 description 2

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- PEUPIGGLJVUNEU-UHFFFAOYSA-N nickel silicon Chemical compound [Si].[Ni] PEUPIGGLJVUNEU-UHFFFAOYSA-N 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 230000000149 penetrating effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42384—Gate electrodes for field effect devices for field-effect transistors with insulated gate for thin film field effect transistors, e.g. characterised by the thickness or the shape of the insulator or the dimensions, the shape or the lay-out of the conductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

- H01L29/41725—Source or drain electrodes for field effect devices

- H01L29/41791—Source or drain electrodes for field effect devices for transistors with a horizontal current flow in a vertical sidewall, e.g. FinFET, MuGFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66787—Unipolar field-effect transistors with an insulated gate, i.e. MISFET with a gate at the side of the channel

- H01L29/66795—Unipolar field-effect transistors with an insulated gate, i.e. MISFET with a gate at the side of the channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/785—Field effect transistors with field effect produced by an insulated gate having a channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Thin Film Transistor (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Abstract

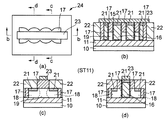

【解決手段】半導体装置25は、半導体基板10上に一定間隔で列状に形成された多数のMOSFET用の複数の柱状ゲート電極16と、複数の柱状ゲート電極16のうちの隣接する2つの柱状ゲート電極間の一部分に形成されるMOSFETのチャネルに相当する半導体領域19と、を備える。この半導体装置の製造方法は、半導体基板を含む基層10〜12の表面に複数の穴14を列状に形成し、これら列状の複数の穴14に半導体を埋め込んで柱状ゲート電極16を列状に複数形成し、ゲート電極16の少なくとも一部を露出させて半導体基板10,11の表面に複数の柱状ゲート電極16を露出させ、隣接する2つの前記柱ゲート電極の離隔する距離の半分の長さよりも厚い絶縁物からなるゲート側壁膜17を成膜し、列状で複数の柱状ゲート電極16の上端を平坦面としてから金属膜により橋絡して第2ゲート電極23を形成し、ゲート電極を製造する。

【選択図】図1

Description

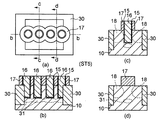

本願発明者は熟考の末に、従来技術のようなFIN形状を有するSOI領域に対してゲート合わせしてパターニングするのではなく、寄生抵抗の問題のないソース・ドレイン領域をセルフアライン(自己整合的)に形成することができる半導体装置とその製造方法の技術を見出すことができた。図1(a)〜(d)は、第1実施形態に係る半導体装置の構造を示すものであり、図1(a)は平面図であり、図1(a)におけるb−b線断面は図1(b)に、c−c線断面は図1(c)に、d−d線断面は図1(d)にそれぞれ示されている。

第2実施形態は、シリコン基板を用いて半導体装置を製造する方法を示している。第1工程ST1において、図10(a)(b)に示すように、まず、半導体基板10に素子分離領域30を形成する。

第3実施形態は、第1ないし第3工程ST1〜ST3までは第2実施形態と同じであるので、図10(a)〜(f)に関連する重複説明を省略して、図16ないし図19を用いて第4工程ST4から説明する。

以下、第4実施形態において、既知のダマシンゲートプロセスを用いた半導体装置の製造方法を説明する。まず、第1工程ST1において、図20(a)(b)に示すように、第1実施形態と同様にして、半導体基板10、BOX酸化膜11、厚み100nm程度のSOI(Silicon on Insulator)領域12からなるSOI基板を用いて、図示のような直径20nm程度で、穴と穴の間隔が25nm程度の複数の穴14を例えばSOI領域12を貫通するように形成する。第1実施形態で用いたカバー膜13はなくても良い。

本発明の実施形態の特徴は、平面で捉えたときのゲート電極16の断面形状が、円、楕円、四角形を含む柱状であることと、隣接する柱状のゲート電極16間をゲート側壁膜17で埋め込むことによって自己整合的にダブルゲート構造のチャネル領域を形成することとの2点である。第1ないし第4実施形態においては、ピラードゲート電極の形状を全て円柱状であるものとして説明したが、本発明の実施形態はこれに限定されず、ピラードゲート電極の形状は柱状でありさえすればいかなる形状であっても良い。このピラードゲートの形状の種々の変形例を第5実施形態として説明する、第5実施形態においては、図28(a)〜(f)に示すように、第2のゲート電極23が省略された状態での層間膜22と柱状ゲート電極16の平面形状をゲート側壁膜17と共に例示している。

11 BOX酸化膜

12 SOI領域

16 柱状ゲート電極

17 ゲート側壁

18 ソース・ドレイン領域

19 チャネル領域

23 第2ゲート電極

25 半導体装置

Claims (5)

- 半導体基板上に離隔して列状に形成された多数のMOSFET用の複数の柱状ゲート電極と、前記複数の柱状ゲート電極のうちの隣接する2つの柱状ゲート電極間の一部分に形成されて前記MOSFETのチャネルに相当する半導体領域と、を備えることを特徴とする半導体装置。

- 前記複数の柱状ゲート電極の間隙側壁の一部に形成されると共に、その厚さが隣接する2つの前記柱状ゲート電極の間隙幅の半分の長さよりも厚いゲート側壁膜をさらに備えることを特徴とする請求項1に記載の半導体装置。

- 前記半導体基板は、バルク基板およびSOI基板の何れか一方を含むことを特徴とする請求項1に記載の半導体装置。

- 半導体基板を含む基層の表面に複数の穴を列状に形成し、

列状に形成された前記複数の穴に第1の導電体を埋め込んで柱状ゲート電極を列状に複数形成し、

前記ゲート電極の少なくとも側面の一部を露出させて前記半導体基板の表面に複数の前記柱状ゲート電極を露出させ、

隣接する2つの前記柱ゲート電極の離隔する距離の半分の長さよりも厚い絶縁物からなるゲート側壁膜を成膜し、

複数の前記柱状ゲート電極の上端を平坦面とした後に列状に形成された前記柱状ゲート電極の上端面を橋絡するように第2の導電体により第2ゲート電極を形成し、

ゲート電極を製造することを特徴とする半導体装置の製造方法。 - 前記基層は、所定の厚さを有する半導体よりなるバルク基板および前記半導体基板の表面に絶縁膜を介して形成された半導体層を有するSOI基板の何れか一方を含むことを特徴とする請求項4に記載の半導体装置の製造方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006243844A JP2008066562A (ja) | 2006-09-08 | 2006-09-08 | 半導体装置およびその製造方法 |

| US11/898,020 US7642162B2 (en) | 2006-09-08 | 2007-09-07 | Semiconductor device and method of manufacturing the same |

| US12/591,643 US7902603B2 (en) | 2006-09-08 | 2009-11-25 | Semiconductor device and method of manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006243844A JP2008066562A (ja) | 2006-09-08 | 2006-09-08 | 半導体装置およびその製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2008066562A true JP2008066562A (ja) | 2008-03-21 |

Family

ID=39168695

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006243844A Abandoned JP2008066562A (ja) | 2006-09-08 | 2006-09-08 | 半導体装置およびその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US7642162B2 (ja) |

| JP (1) | JP2008066562A (ja) |

Cited By (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101247019B1 (ko) * | 2009-08-11 | 2013-03-26 | 유니산티스 일렉트로닉스 싱가포르 프라이빗 리미티드 | 반도체 장치 및 그 제조 방법 |

| US8441066B2 (en) | 2009-09-16 | 2013-05-14 | Unisantis Electronics Singapore Pte Ltd. | Semiconductor device |

| US8633535B2 (en) | 2010-06-09 | 2014-01-21 | Kabushiki Kaisha Toshiba | Nonvolatile semiconductor memory |

| US8642426B2 (en) | 2009-03-25 | 2014-02-04 | Unisantis Electronics Singapore Pte Ltd. | Semiconductor device and production method therefor |

| US8772881B2 (en) | 2009-06-05 | 2014-07-08 | Unisantis Electronics Singapore Pte Ltd. | Semiconductor device |

| KR20150020172A (ko) * | 2012-04-13 | 2015-02-25 | 샌디스크 테크놀로지스, 인코포레이티드 | 박막 트랜지스터 |

| KR20170074340A (ko) * | 2015-12-22 | 2017-06-30 | 에스케이하이닉스 주식회사 | 반도체장치 및 그 제조 방법 |

| KR101916463B1 (ko) | 2012-06-29 | 2018-11-07 | 에스케이하이닉스 주식회사 | 반도체 소자의 안티퓨즈 및 그 제조 방법 |

| KR20200014442A (ko) * | 2017-06-29 | 2020-02-10 | 마이크론 테크놀로지, 인크 | 절연 재료 및 메모리 셀의 수직 교번하는 티어를 포함하는 메모리 어레이 및 트랜지스터 및 커패시터를 개별적으로 포함하는 메모리 셀을 포함하는 메모리 어레이를 형성하는 방법 |

Families Citing this family (45)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5329835B2 (ja) * | 2008-04-10 | 2013-10-30 | 株式会社東芝 | 半導体装置の製造方法 |

| US8106459B2 (en) | 2008-05-06 | 2012-01-31 | Taiwan Semiconductor Manufacturing Company, Ltd. | FinFETs having dielectric punch-through stoppers |

| US8048723B2 (en) | 2008-12-05 | 2011-11-01 | Taiwan Semiconductor Manufacturing Company, Ltd. | Germanium FinFETs having dielectric punch-through stoppers |

| US7964487B2 (en) * | 2008-06-04 | 2011-06-21 | International Business Machines Corporation | Carrier mobility enhanced channel devices and method of manufacture |

| DE102008030853B4 (de) * | 2008-06-30 | 2014-04-30 | Globalfoundries Dresden Module One Limited Liability Company & Co. Kg | Dreidimensionaler Transistor mit einer Doppelkanal-Konfiguration |

| WO2010032174A1 (en) * | 2008-09-16 | 2010-03-25 | Nxp B.V. | Fin field effect transistor (finfet) |

| US8263462B2 (en) | 2008-12-31 | 2012-09-11 | Taiwan Semiconductor Manufacturing Company, Ltd. | Dielectric punch-through stoppers for forming FinFETs having dual fin heights |

| US8293616B2 (en) * | 2009-02-24 | 2012-10-23 | Taiwan Semiconductor Manufacturing Company, Ltd. | Methods of fabrication of semiconductor devices with low capacitance |

| JP4577592B2 (ja) | 2009-04-20 | 2010-11-10 | 日本ユニサンティスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| CN102034865B (zh) * | 2009-09-30 | 2012-07-04 | 中国科学院微电子研究所 | 半导体器件及其制造方法 |

| CN102117828B (zh) * | 2009-12-30 | 2013-02-06 | 中国科学院微电子研究所 | 半导体器件及其制造方法 |

| JP2011204745A (ja) * | 2010-03-24 | 2011-10-13 | Toshiba Corp | 半導体装置及びその製造方法 |

| US8431995B2 (en) * | 2010-05-13 | 2013-04-30 | International Business Machines Corporation | Methodology for fabricating isotropically recessed drain regions of CMOS transistors |

| US8716798B2 (en) | 2010-05-13 | 2014-05-06 | International Business Machines Corporation | Methodology for fabricating isotropically recessed source and drain regions of CMOS transistors |

| US20120168819A1 (en) * | 2011-01-03 | 2012-07-05 | Fabio Alessio Marino | Semiconductor pillar power MOS |

| US9401436B2 (en) | 2011-05-05 | 2016-07-26 | Qualcomm Incorporated | Multiple control transcap variable capacitor |

| US8557666B2 (en) * | 2011-09-13 | 2013-10-15 | GlobalFoundries, Inc. | Methods for fabricating integrated circuits |

| US10438836B2 (en) | 2011-11-09 | 2019-10-08 | Unisantis Electronics Singapore Pte. Ltd. | Method for manufacturing a semiconductor device |

| US8759178B2 (en) | 2011-11-09 | 2014-06-24 | Unisantis Electronics Singapore Pte. Ltd. | Method for manufacturing semiconductor device and semiconductor device |

| US8735232B2 (en) | 2011-11-29 | 2014-05-27 | GlobalFoundries, Inc. | Methods for forming semiconductor devices |

| US9012981B2 (en) | 2012-05-17 | 2015-04-21 | Unisantis Electronics Singapore Pte. Ltd. | Semiconductor device |

| US8829601B2 (en) | 2012-05-17 | 2014-09-09 | Unisantis Electronics Singapore Pte. Ltd. | Semiconductor device |

| US9166043B2 (en) | 2012-05-17 | 2015-10-20 | Unisantis Electronics Singapore Pte. Ltd. | Semiconductor device |

| US8877578B2 (en) | 2012-05-18 | 2014-11-04 | Unisantis Electronics Singapore Pte. Ltd. | Method for producing semiconductor device and semiconductor device |

| US8697511B2 (en) | 2012-05-18 | 2014-04-15 | Unisantis Electronics Singapore Pte. Ltd. | Method for producing semiconductor device and semiconductor device |

| JP2014007305A (ja) * | 2012-06-25 | 2014-01-16 | Toshiba Corp | 半導体記憶装置及びその製造方法 |

| US8941177B2 (en) | 2012-06-27 | 2015-01-27 | International Business Machines Corporation | Semiconductor devices having different gate oxide thicknesses |

| US8629420B1 (en) * | 2012-07-03 | 2014-01-14 | Intel Mobile Communications GmbH | Drain extended MOS device for bulk FinFET technology |

| US8932918B2 (en) * | 2012-08-29 | 2015-01-13 | International Business Machines Corporation | FinFET with self-aligned punchthrough stopper |

| CN103928333B (zh) * | 2013-01-15 | 2019-03-12 | 中国科学院微电子研究所 | 半导体器件及其制造方法 |

| US9165933B2 (en) | 2013-03-07 | 2015-10-20 | Sandisk 3D Llc | Vertical bit line TFT decoder for high voltage operation |

| US8900934B2 (en) | 2013-04-18 | 2014-12-02 | International Business Machines Corporation | FinFET devices containing merged epitaxial Fin-containing contact regions |

| CN104112748B (zh) * | 2013-04-19 | 2016-12-28 | 中国科学院微电子研究所 | 存储器件及其制造方法和存取方法 |

| CN104124159B (zh) * | 2013-04-23 | 2017-11-03 | 中国科学院微电子研究所 | 半导体器件制造方法 |

| JP5670603B1 (ja) * | 2013-04-26 | 2015-02-18 | ユニサンティス エレクトロニクス シンガポール プライベート リミテッドUnisantis Electronics Singapore Pte Ltd. | 半導体装置の製造方法及び半導体装置 |

| US8980713B2 (en) * | 2013-05-31 | 2015-03-17 | Sony Corporation | Method for fabricating a metal high-k gate stack for a buried recessed access device |

| CN104425601B (zh) * | 2013-08-30 | 2018-02-16 | 中国科学院微电子研究所 | 半导体器件及其制造方法 |

| US9240420B2 (en) | 2013-09-06 | 2016-01-19 | Sandisk Technologies Inc. | 3D non-volatile storage with wide band gap transistor decoder |

| US9337195B2 (en) * | 2013-12-18 | 2016-05-10 | Taiwan Semiconductor Manufacturing Company, Ltd. | Semiconductor devices and methods of manufacture thereof |

| US9691763B2 (en) | 2013-12-27 | 2017-06-27 | International Business Machines Corporation | Multi-gate FinFET semiconductor device with flexible design width |

| US9190466B2 (en) | 2013-12-27 | 2015-11-17 | International Business Machines Corporation | Independent gate vertical FinFET structure |

| US9312360B2 (en) * | 2014-05-01 | 2016-04-12 | International Business Machines Corporation | FinFET with epitaxial source and drain regions and dielectric isolated channel region |

| US9679965B1 (en) * | 2015-12-07 | 2017-06-13 | Samsung Electronics Co., Ltd. | Semiconductor device having a gate all around structure and a method for fabricating the same |

| US9859389B1 (en) | 2016-06-27 | 2018-01-02 | International Business Machines Corporation | Sidewall protective layer for contact formation |

| CN114496761B (zh) * | 2022-04-06 | 2022-06-17 | 泰科天润半导体科技(北京)有限公司 | 一种圆形栅纵向mosfet功率器件的制造方法 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001298194A (ja) * | 2000-04-14 | 2001-10-26 | Nec Corp | 電界効果型トランジスタ及びその製造方法 |

| JP2003086795A (ja) * | 2001-09-11 | 2003-03-20 | Sharp Corp | 半導体装置およびその製造方法と集積回路と半導体システム |

| JP2003101013A (ja) * | 2001-09-26 | 2003-04-04 | Sharp Corp | 半導体装置およびその製造方法および集積回路および半導体システム |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3338434B2 (ja) | 1994-02-28 | 2002-10-28 | 株式会社半導体エネルギー研究所 | 薄膜トランジスタの作製方法 |

| JP2002118255A (ja) | 2000-07-31 | 2002-04-19 | Toshiba Corp | 半導体装置およびその製造方法 |

| KR100458288B1 (ko) | 2002-01-30 | 2004-11-26 | 한국과학기술원 | 이중-게이트 FinFET 소자 및 그 제조방법 |

| JP3651802B2 (ja) | 2002-09-12 | 2005-05-25 | 株式会社東芝 | 半導体装置の製造方法 |

| JP4197607B2 (ja) | 2002-11-06 | 2008-12-17 | 株式会社東芝 | 絶縁ゲート型電界効果トランジスタを含む半導体装置の製造方法 |

| US7199419B2 (en) * | 2004-12-13 | 2007-04-03 | Micron Technology, Inc. | Memory structure for reduced floating body effect |

| KR100660881B1 (ko) * | 2005-10-12 | 2006-12-26 | 삼성전자주식회사 | 수직 채널 트랜지스터를 구비한 반도체 소자 및 그 제조방법 |

| JP2007165461A (ja) * | 2005-12-12 | 2007-06-28 | Elpida Memory Inc | 半導体装置及びその製造方法 |

| KR100720258B1 (ko) * | 2006-01-23 | 2007-05-23 | 주식회사 하이닉스반도체 | 반도체 소자의 형성 방법 |

| JP5122762B2 (ja) * | 2006-03-07 | 2013-01-16 | 株式会社東芝 | 電力用半導体素子、その製造方法及びその駆動方法 |

| JP4256411B2 (ja) * | 2006-08-18 | 2009-04-22 | 株式会社東芝 | 強誘電体記憶装置の製造方法 |

-

2006

- 2006-09-08 JP JP2006243844A patent/JP2008066562A/ja not_active Abandoned

-

2007

- 2007-09-07 US US11/898,020 patent/US7642162B2/en active Active

-

2009

- 2009-11-25 US US12/591,643 patent/US7902603B2/en active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001298194A (ja) * | 2000-04-14 | 2001-10-26 | Nec Corp | 電界効果型トランジスタ及びその製造方法 |

| JP2003086795A (ja) * | 2001-09-11 | 2003-03-20 | Sharp Corp | 半導体装置およびその製造方法と集積回路と半導体システム |

| JP2003101013A (ja) * | 2001-09-26 | 2003-04-04 | Sharp Corp | 半導体装置およびその製造方法および集積回路および半導体システム |

Cited By (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8642426B2 (en) | 2009-03-25 | 2014-02-04 | Unisantis Electronics Singapore Pte Ltd. | Semiconductor device and production method therefor |

| US8772881B2 (en) | 2009-06-05 | 2014-07-08 | Unisantis Electronics Singapore Pte Ltd. | Semiconductor device |

| US9484268B2 (en) | 2009-08-11 | 2016-11-01 | Unisantis Electronics Singapore Pte Ltd. | Semiconductor device and production method |

| US8558317B2 (en) | 2009-08-11 | 2013-10-15 | Unisantis Electronics Singapore Pte Ltd. | Semiconductor device and production method |

| KR101247019B1 (ko) * | 2009-08-11 | 2013-03-26 | 유니산티스 일렉트로닉스 싱가포르 프라이빗 리미티드 | 반도체 장치 및 그 제조 방법 |

| US9059309B2 (en) | 2009-08-11 | 2015-06-16 | Unisantis Electronics Singapore Pte Ltd. | Semiconductor device and production method |

| US8441066B2 (en) | 2009-09-16 | 2013-05-14 | Unisantis Electronics Singapore Pte Ltd. | Semiconductor device |

| US8633535B2 (en) | 2010-06-09 | 2014-01-21 | Kabushiki Kaisha Toshiba | Nonvolatile semiconductor memory |

| KR20150020172A (ko) * | 2012-04-13 | 2015-02-25 | 샌디스크 테크놀로지스, 인코포레이티드 | 박막 트랜지스터 |

| KR101961982B1 (ko) * | 2012-04-13 | 2019-07-17 | 샌디스크 테크놀로지스 엘엘씨 | 박막 트랜지스터 |

| KR101916463B1 (ko) | 2012-06-29 | 2018-11-07 | 에스케이하이닉스 주식회사 | 반도체 소자의 안티퓨즈 및 그 제조 방법 |

| KR20170074340A (ko) * | 2015-12-22 | 2017-06-30 | 에스케이하이닉스 주식회사 | 반도체장치 및 그 제조 방법 |

| KR102410927B1 (ko) * | 2015-12-22 | 2022-06-21 | 에스케이하이닉스 주식회사 | 반도체장치 및 그 제조 방법 |

| KR20200014442A (ko) * | 2017-06-29 | 2020-02-10 | 마이크론 테크놀로지, 인크 | 절연 재료 및 메모리 셀의 수직 교번하는 티어를 포함하는 메모리 어레이 및 트랜지스터 및 커패시터를 개별적으로 포함하는 메모리 셀을 포함하는 메모리 어레이를 형성하는 방법 |

| KR102401865B1 (ko) * | 2017-06-29 | 2022-05-25 | 마이크론 테크놀로지, 인크 | 절연 재료 및 메모리 셀의 수직 교번하는 티어를 포함하는 메모리 어레이 및 트랜지스터 및 커패시터를 개별적으로 포함하는 메모리 셀을 포함하는 메모리 어레이를 형성하는 방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| US7902603B2 (en) | 2011-03-08 |

| US20100072550A1 (en) | 2010-03-25 |

| US20080061370A1 (en) | 2008-03-13 |

| US7642162B2 (en) | 2010-01-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2008066562A (ja) | 半導体装置およびその製造方法 | |

| KR100625177B1 (ko) | 멀티-브리지 채널형 모오스 트랜지스터의 제조 방법 | |

| TWI590451B (zh) | 鰭式場效電晶體結構及其形成方法 | |

| US7663166B2 (en) | Wire-type semiconductor devices and methods of fabricating the same | |

| US8921191B2 (en) | Integrated circuits including FINFET devices with lower contact resistance and reduced parasitic capacitance and methods for fabricating the same | |

| JP4825526B2 (ja) | Fin型チャネルトランジスタおよびその製造方法 | |

| JP4796329B2 (ja) | マルチ−ブリッジチャンネル型mosトランジスタの製造方法 | |

| US8536653B2 (en) | Metal oxide semiconductor transistor | |

| US8541286B2 (en) | Methods for fabricating integrated circuits | |

| KR20160099447A (ko) | 랩어라운드 실리사이드를 구비한 finfet 및 그 형성 방법 | |

| JP2011071235A (ja) | 半導体装置及びその製造方法 | |

| KR100769418B1 (ko) | 반도체장치 및 그 제조방법 | |

| KR20080035659A (ko) | 스트레스형 mos 디바이스 제조방법 | |

| JP2013065672A (ja) | 半導体装置および半導体装置の製造方法 | |

| US6940129B2 (en) | Double gate MOS transistors | |

| JP2012160749A (ja) | 電界効果トランジスタを備える半導体素子及びその製造方法 | |

| JP2014107302A (ja) | 半導体装置 | |

| JP2007005568A (ja) | 半導体装置 | |

| JP2005333136A (ja) | 電界効果トランジスタを備える半導体素子及びその製造方法 | |

| US8669162B2 (en) | Semiconductor device and method of manufacturing the same | |

| JP2008103579A (ja) | 半導体装置及びその製造方法 | |

| JP2009055027A (ja) | Mosトランジスタの製造方法、および、これにより製造されたmosトランジスタ | |

| KR101674179B1 (ko) | 전계 효과 트랜지스터를 포함하는 반도체 소자 및 그 형성 방법 | |

| JP2006269975A (ja) | 半導体装置及びその製造方法 | |

| US20130292779A1 (en) | Semiconductor device and semiconductor device production process |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090209 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110819 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110823 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111024 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120228 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120423 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120706 |

|

| A762 | Written abandonment of application |

Free format text: JAPANESE INTERMEDIATE CODE: A762 Effective date: 20120713 |