JP2006147880A - Method and device for bonding semiconductor with solder bump - Google Patents

Method and device for bonding semiconductor with solder bump Download PDFInfo

- Publication number

- JP2006147880A JP2006147880A JP2004336479A JP2004336479A JP2006147880A JP 2006147880 A JP2006147880 A JP 2006147880A JP 2004336479 A JP2004336479 A JP 2004336479A JP 2004336479 A JP2004336479 A JP 2004336479A JP 2006147880 A JP2006147880 A JP 2006147880A

- Authority

- JP

- Japan

- Prior art keywords

- chip

- solder bumps

- semiconductor

- substrate

- solder

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/8319—Arrangement of the layer connectors prior to mounting

- H01L2224/83192—Arrangement of the layer connectors prior to mounting wherein the layer connectors are disposed only on another item or body to be connected to the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/013—Alloys

- H01L2924/0132—Binary Alloys

- H01L2924/01322—Eutectic Alloys, i.e. obtained by a liquid transforming into two solid phases

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/095—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00 with a principal constituent of the material being a combination of two or more materials provided in the groups H01L2924/013 - H01L2924/0715

- H01L2924/097—Glass-ceramics, e.g. devitrified glass

- H01L2924/09701—Low temperature co-fired ceramic [LTCC]

Landscapes

- Wire Bonding (AREA)

Abstract

Description

本発明は半田バンプ付き半導体の接合方法および半田バンプ付き半導体接合装置に関す

るものである。

The present invention relates to a method for joining semiconductors with solder bumps and a semiconductor joining device with solder bumps.

近年、半導体デバイスの軽薄短小化や高機能化が進んでおり、それに伴った高密度実装

要求に応えていくために半田バンプ付き半導体(以下チップという)を直接フェイスダウ

ンにて、基板上に実装するフリップチップボンディングが開発されている。これは、チッ

プ側にある半田と基板側にある基板電極を使って、裏返したチップ(フリップチップ)を

基板上に位置合わせした後、半田を溶融させ接合を行なうものである。

In recent years, semiconductor devices have become lighter, thinner, smaller, and more advanced, and semiconductors with solder bumps (hereinafter referred to as chips) are mounted directly on the board in order to meet the high-density mounting requirements. Flip chip bonding has been developed. In this method, after turning over the chip (flip chip) on the substrate using the solder on the chip side and the substrate electrode on the substrate side, the solder is melted and bonded.

図2は従来技術によるフリップチップ工法において、チップの半田バンプ部及び基板電極上にフラックスが供給された状態の断面図である。従来、チップ1をフリップチップ工法にて基板2に接合する場合、予め半田バンプ3表面および/または基板電極4側にフラックス5を転写あるいは供給し、フラックス5の有する粘着性を利用してチップ1の搭載後の仮固定を行う。リフロー方式の加熱では、チップ1を基板2に搭載後リフロー炉(不図示)に投入して半田バンプ3を溶融し、半田バンプ3と基板電極4を接合し、その後、冷却して半田バンプ3を固化することで接合が終了する工程を辿っている。

FIG. 2 is a cross-sectional view showing a state in which flux is supplied onto a solder bump portion of a chip and a substrate electrode in a conventional flip chip method. Conventionally, when the

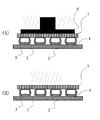

図3は従来技術によるフリップチップ工法において、ボンディングヘッドにより吸着したチップの半田バンプと基板電極の位置を合わせて搭載し、所定の加熱及び加重で押し付け半田溶融を行なった状態の断面図(A)と、ボンディングヘッドにより吸着したチップを半田バンプと基板電極の位置を合わせて搭載し、所定の加重で押し付けた後、リフローによる加熱で半田溶融を行なった状態の断面図(B)である。図(A)のフリップチップ工法では、ボンディングヘッド6により吸着したチップ1の半田バンプ3と基板2に形成された基板電極4の位置合わせをして搭載し、そのまま所定の加重でチップ1を基板2に押し付け、ボンディングヘッド6により加熱して半田バンプ3を溶融し、半田バンプ3と基板電極4を接合し、半田バンプが固まるのを待ってボンディングヘッド6を外す工程を辿っている。

FIG. 3 is a cross-sectional view (A) of the state in which the solder bumps of the chip adsorbed by the bonding head and the substrate electrodes are mounted in the conventional flip-chip method, and the solder is melted by pressing with predetermined heating and load. FIG. 4B is a cross-sectional view (B) of a state where the chip adsorbed by the bonding head is mounted with the position of the solder bump and the substrate electrode aligned, pressed with a predetermined load, and then solder melted by reflow heating. In the flip chip method of FIG. 1A, the

フラックスの主な作用は、前述の粘着性によるチップ搭載後の仮固定と、半田が溶融し接合する際に、半田や非半田接合面の酸化膜を除去するとともに、前記半田や非半田接合面の表面を覆って再酸化を防止することにあり、半田溶融させる際には必要不可欠なものとなっている。 The main effect of the flux is to temporarily fix the chip after mounting due to the above-mentioned adhesiveness and to remove the oxide film on the solder or non-solder joint surface when the solder is melted and joined, and the solder or non-solder joint surface. It is indispensable when the solder is melted to prevent reoxidation.

しかしながらフラックスには腐食性があるため、接合後は除去しなければならず、洗浄工程を必要としている。図4は従来のフリップチップ工法において洗浄工程によりフラックスを除去した後の状態の断面図である。また、フラックス除去後は、チップ1と基板2の間に樹脂を充填するのが一般的である。図5は、チップと基板との間に熱硬化性樹脂を充填した状態の断面図であるが、チップ1と基板2との接合強度を補強し、製品の信頼性を向上させる為、接合後のチップ1と基板2の間に熱硬化性樹脂7などのアンダーフィル樹脂の充填が必須条件となっていた。熱硬化性樹脂7はディスペンサー8等で供給するが、フラックス5の残渣により樹脂の注入が阻害され充填が困難になるといった問題がある。さらに、フラックス残渣は接合後に注入する熱硬化性樹脂7との密着性が悪い為、剥離を起こすことがあり、製造された製品の信頼性を低下させる要因となっている。

However, since the flux is corrosive, it must be removed after joining, which requires a cleaning process. FIG. 4 is a cross-sectional view showing a state after the flux is removed by a cleaning process in the conventional flip chip method. Also, after removing the flux, it is common to fill the resin between the

前記問題があるためフラックス5を完全に除去する為の洗浄工程が必要となっている。フリップチップ実装のフラックス洗浄を行なう場合、チップ1と基板2間は50μm程度であり、非常に狭ギャップ間の洗浄を行なうことになり、完全に除去するためには長時間の洗浄を行なう必要があり、コストアップの要因となっている。

Due to the above problems, a cleaning process for completely removing the

前述の加熱方式は、リフロー方式だと全体加熱のため半田溶融までに時間がかかってしまい、ボンディングヘッド加熱による接合方法だと局部加熱により半田溶融までに至る時間は短く出来るものの、溶融後の半田が冷却し凝固するまでボンディングヘッドをチップから離せないため、長時間の接合タクトが必要となりコストアップの要因となっている。 In the above heating method, it takes time to melt the solder due to the entire reflow method, and the bonding method by heating the bonding head can shorten the time until the solder melts due to local heating, but the solder after melting Since the bonding head cannot be separated from the chip until it cools and solidifies, a long tact time is required, which increases costs.

このような問題を解決する為、フラックスレスにてフリップチップ実装を行なう方法として、フラックス作用を有する熱硬化性樹脂を使用し、リフローによる接合工法もあるが、リフロー時の高温により熱硬化性樹脂中の水分及び樹脂中に巻き込まれた空気が急激に膨張してクラックを起こしたり、リフロー炉に入った時点では、熱硬化性樹脂が硬化しておらず液状である為、チップ保持力が弱く、リフロー炉内の熱風によりチップ位置がずれるなどの問題がある。(例えば特許文献1参照) In order to solve such problems, a fluxless flip chip mounting method uses a thermosetting resin having a flux action, and there is also a reflow bonding method, but the thermosetting resin due to the high temperature during reflow. Moisture inside and air entrained in the resin suddenly expands to cause cracks, or when entering the reflow furnace, the thermosetting resin is not cured and is liquid, so the chip holding power is weak There is a problem that the tip position shifts due to hot air in the reflow furnace. (For example, see Patent Document 1)

リフロー方式及びボンディングヘッド加熱方式による長時間の接合タクトによるコストアップ問題。チップをフリップチップ工法にて実装する際に使用するフラックスによる腐食あるいは製品の信頼性低下の問題。チップと基板の接合後の、狭ギャップ間のフラックス洗浄工程を行なう場合の長時間の洗浄時間を行なうことによるコストアップ問題。洗浄後のフラックス残渣による熱硬化性樹脂の注入阻害。フラックス残渣と熱硬化性樹脂との密着性による信頼性の低下問題。本発明は、接合タクトの問題、フラックス使用による問題、熱硬化性樹脂の注入に関する問題、信頼性の低下問題を解決することを目的としている。 Cost increase due to long tact time due to reflow method and bonding head heating method. Corrosion due to the flux used when mounting the chip by the flip-chip method or deterioration of product reliability. Cost increase problem due to long cleaning time when performing flux cleaning process between narrow gap after bonding chip and substrate. Inhibition of thermosetting resin injection due to flux residue after cleaning. Reliability degradation due to adhesion between flux residue and thermosetting resin. An object of the present invention is to solve the problem of joining tact, the problem due to the use of flux, the problem related to the injection of thermosetting resin, and the problem of lowering reliability.

請求項1に記載のチップ接合方法の発明は、少なくとも、熱硬化性樹脂を予め基板に供給する工程と、該熱硬化性樹脂上にチップを供給する工程と、非接触の熱源による局部加熱で前記チップを加熱して半田バンプを溶融させ基板上の電極と接合を行なう工程を有することを特徴とするチップ接合方法である。

The invention of the chip bonding method according to

請求項2に記載のチップ接合方法の発明は、請求項1において、熱硬化性樹脂を硬化させる工程を有することを特徴とする請求項1記載のチップ接合方法である。

An invention of a chip bonding method according to

請求項3に記載のチップ接合装置の発明は、少なくとも、チップが供給された基板を位置決め載置する手段と、前記基板の半導体載置部を局部的に加熱する非接触加熱手段と、該加熱手段を制御する手段を有することを特徴とするチップ接合装置である。

The invention of a chip bonding apparatus according to

請求項4に記載のチップ接合装置の発明は、請求項3において、熱硬化性樹脂を供給する手段と、チップを供給する手段を有することを特徴とするチップ接合装置である。 According to a fourth aspect of the present invention, there is provided a chip bonding apparatus according to the third aspect, further comprising means for supplying a thermosetting resin and means for supplying a chip.

請求項5に記載のチップ接合装置の発明は、請求項4において、チップの供給を行なう前に、半田バンプと基板電極の位置を合わせるための位置合わせ認識機能と、チップを供給した際に、半田バンプと基板電極間に介在している熱硬化性樹脂を押し出す為の搭載加重を制御する手段を有することを特徴とするチップ接合装置である。

The invention of a chip bonding apparatus according to

請求項6に記載のチップ接合装置の発明は、請求項3〜5のいずれか1項に記載において、少なくとも、熱硬化性樹脂を供給する手段と、半田バンプ付き半導体を供給する手段と半導体載置部を局部的に加熱する手段を同一搬送系上で次工程への流動を連続に行なう手段を有することを特徴とする半田バンプ付き半導体接合装置である。 According to a sixth aspect of the present invention, there is provided the chip bonding apparatus according to any one of the third to fifth aspects, wherein at least the means for supplying the thermosetting resin, the means for supplying the semiconductor with solder bumps, and the semiconductor mounting are provided. A semiconductor bonding apparatus with solder bumps, characterized in that means for locally heating the mounting portion has means for continuously flowing to the next process on the same transport system.

請求項1の発明のチップ接合方法によると、予め基板に供給された熱硬化性樹脂の粘着性により搭載されたチップに、非接触の熱源にてチップを局部的に加熱するので、短時間で半田溶融点まで温度が上昇し溶融・接合が行なわれ、非接触の局部加熱なので、半田が冷却し凝固するまでの待機時間がきわめて短くなる。従来のリフロー方式及びボンディングヘッド方式による接合時間に比べ、短時間接合が可能となり長時間の接合タクトによるコストアップ問題を解決することが出来る。また、フラックス洗浄工程を省くことが出来、工程を簡略化することが出来る為、洗浄工程を行なうことによるコストアップ問題を解決することが出来る。さらに、ノンフラックスにて半田溶融接合が行なわれることで、フラックスによる腐食あるいは剥離等による製品の信頼性低下の問題を解決することが出来る。予め熱可塑性樹脂を供給するので、従来技術の課題であったフラックス残渣による熱硬化性樹脂の注入阻害はあり得なくなる。

According to the chip bonding method of the invention of

請求項2の発明のチップ接合方法によると、溶融接合時で半硬化状態であった熱硬化性樹脂を接合後に硬化させることにより、熱硬化性樹脂が本硬化され製品の信頼性向上を行なうことが出来る。

According to the chip bonding method of the invention of

請求項3の発明のチップ接合装置は、予め基板に供給された熱硬化性樹脂の粘着性により搭載されたチップに、非接触の熱源にてチップを局部的に加熱する手段を有するので、短時間で半田溶融点まで温度が上昇し溶融・接合が行なわれる。非接触の局部加熱なので、半田が冷却し凝固するまでの待機時間がきわめて短くなる。従来のリフロー方式及びボンディングヘッド方式による接合時間に比べ、短時間接合が可能となり長時間の接合タクトが必要な装置と比べ接合装置の生産能力が向上できる。また従来後工程で必要であったフラックス洗浄工程を省くことが出来、工程を簡略化することが出来る為、洗浄工程を行なうことによるコストアップ問題を解決することが出来る。さらに、ノンフラックスにて半田溶融接合が行なえるので、フラックスによる腐食あるいは剥離等による製品の信頼性低下の問題を解決することが出来る。局部的な加熱なので、高温により熱硬化性樹脂中の水分及び樹脂中に巻き込まれた空気が急激に膨張してクラックを起こしたり、リフロー炉内の熱風によりチップ位置がずれるなどの問題が発生しない等々の特徴を有する。

Since the chip bonding apparatus of the invention of

請求項4の発明のチップ接合装置によると、さらに熱硬化性樹脂を供給する手段とチップを供給する手段を有することにより、基板上に供給されたチップが次工程である半田溶融工程に流動するまでの移動距離や移動時間が短縮される為、製品移動間での外部衝撃によるチップ位置のずれや樹脂の長時間放置による吸湿などの不具合がなくなる。また、熱硬化性樹脂供給とチップ供給及び半田溶融接合とを同一装置で行なうことが可能になり、人員削減が可能となる。 According to the chip bonding apparatus of the fourth aspect of the present invention, the chip supplied on the substrate flows to the solder melting process which is the next process by further including means for supplying the thermosetting resin and means for supplying the chip. Therefore, there are no problems such as chip position shift due to external impact between product movements and moisture absorption due to leaving the resin for a long time. In addition, it is possible to perform thermosetting resin supply, chip supply, and solder fusion bonding with the same apparatus, thereby reducing personnel.

請求項5の発明のチップ接合装置によると、さらにチップの半田バンプ部と基板電極位置を合わせる為の位置認識機能を有することにより、常に正確な位置にチップ供給を行なうことが可能となる。また、搭載加重制御機能を有することにより、常に適正な加重にて搭載を行なうことが出来、過加重によるチップ破壊や加重不足によりバンプと基板電極間の樹脂を押し出すことが出来ず、それらが接触出来ないことによる未接合問題を防ぐことが出来る。 According to the chip bonding apparatus of the fifth aspect of the present invention, it is possible to always supply the chip at an accurate position by further having a position recognition function for aligning the solder bump portion of the chip and the substrate electrode position. Also, by having a mounting weight control function, mounting can always be performed with an appropriate weight, and the resin between the bump and the substrate electrode cannot be pushed out due to chip breakage due to overloading or insufficient weighting. It is possible to prevent the unbonded problem caused by the failure.

請求項6の発明のチップ接合装置によると、さらに熱硬化性樹脂の供給手段とチップ供給手段とチップへの非接触による局部的加熱手段を同一搬送系にて行なえる機能を有することにより、各工程が同一搬送系上で行なわれ、次工程への流動が連続となることにより、熱硬化性樹脂の供給手段とチップ供給手段とチップへの非接触による局部加熱手段を一人の作業者にて行なうことが可能となり、人員削減及び作業効率の向上が可能となる。

According to the chip joining apparatus of the invention of

少なくとも、熱硬化性樹脂を予め基板に供給する工程と、チップを供給する工程と、非接触の熱源にて局部加熱を行い、半田を溶融させ接合を行なう工程を有することを特徴とするチップ接合方法である。 Chip joining, comprising: a step of supplying a thermosetting resin to a substrate in advance; a step of supplying a chip; and a step of locally heating with a non-contact heat source to melt and bond the solder Is the method.

図1は本発明に係わる基板とチップを重ね合わせた上面図(A)と側面図(B)である(A)においては重ね合わせた部分にある基板電極、半田バンプ部を透視して記載してあり、(B)においては基板とチップを離して記載してある。チップ1には12の半田バンプ3が形成され、基板2には半田バンプ3に対応する12の基板電極4が形成されている。

FIG. 1A is a top view (A) and a side view (B) in which a substrate and a chip according to the present invention are overlaid, and (A) is a perspective view of substrate electrodes and solder bumps in the overlaid portion. In (B), the substrate is separated from the chip. Twelve

図6は基板上に熱硬化性樹脂のチップ接合装置を供給した状態の模式図である。熱硬化性樹脂(例えばエポキシ系樹脂)7の供給位置としては半田バンプ3が接触する基板電極4部が全て覆われるように行なうことが望ましく、供給手段としてはディスペンサ8や転写等の汎用手段でよく、供給量としては、チップ1を搭載した際に、チップ1の側面にチップ1の厚さの半分程度にまでフィレットが出来る程度の量が良い。熱硬化性エポキシ樹脂7中に巻き込まれた空気が急激に膨張してクラックを起こしたり、熱硬化性エポキシ樹脂7による浮力でチップ1の位置がズレてしまうことのないよう配慮することは言うまでもない。

FIG. 6 is a schematic view of a state in which a thermosetting resin chip bonding apparatus is supplied onto a substrate. It is desirable that the thermosetting resin (for example, epoxy resin) 7 is supplied so that the

使用する熱硬化性エポキシ樹脂7の樹脂物性値については、チップ1を搭載した際に、位置ズレを起こさないように、またチップ1付近のみの局部加熱を行なった際に、照射熱により熱硬化性エポキシ樹脂7が飛散するのを抑える為に、ある程度の粘度(10Pa.s程度)をもった樹脂が望ましい。また、加熱した際に熱硬化性エポキシ樹脂のゲル化が始まり半田バンプ3より先に硬化してしまうと、チップ1が傾き接続することが出来なくなる恐れがある為、ゲルタイム(150℃時)が100sec〜120secのものが望ましい。

Regarding the resin physical properties of the thermosetting

図7は、熱硬化性エポキシ樹脂を供給した基板上に、ボンディングヘッドにより吸着したチップを半田バンプと基板電極の位置を合わせて搭載し、所定の加重で押し付けた状態の断面図である。この際のボンディング加重は半田バンプ3と基板電極4の間に介在している熱硬化性エポキシ樹脂7を押し出すように、40〜50gf/バンプ程度の加重をかけることが望ましい。

FIG. 7 is a cross-sectional view of a state where a chip adsorbed by a bonding head is mounted on a substrate supplied with a thermosetting epoxy resin with the positions of solder bumps and substrate electrodes aligned and pressed with a predetermined load. The bonding weight at this time is preferably about 40 to 50 gf / bump so as to extrude the thermosetting

図8は、非接触の熱源(例えばハロゲンランプ・キセノンランプ・レーザー光線等)にて搭載されたチップをスポット加熱し、半田溶融させて接合を行なった状態を示す模式図である。この時の照射時間は熱硬化性エポキシ樹脂7の硬化が始まらないようになるべく短くするのが望ましく(好ましくは2sec以内程度)、照射時間内に半田バンプ3の溶融が可能となるような温度に達するように非接触熱源のパワーを調整することが必要である。

FIG. 8 is a schematic view showing a state in which a chip mounted with a non-contact heat source (for example, a halogen lamp, a xenon lamp, a laser beam, etc.) is spot-heated and soldered to be joined. It is desirable that the irradiation time at this time be as short as possible so that curing of the thermosetting

図9は所定の硬化条件にて熱硬化性エポキシ樹脂の硬化を行なった状態の断面図である。使用熱硬化性エポキシ樹脂のメーカー推奨条件にてポストキュアを行い、樹脂硬化を行なう。 FIG. 9 is a cross-sectional view of a state where the thermosetting epoxy resin is cured under predetermined curing conditions. Post cure under the conditions recommended by the manufacturer of the thermosetting epoxy resin used to cure the resin.

本実施例では、基板材料に外形5×5mmで厚み0.5mm程度のガラエポを使用したが、使用する基板材料は、外形2×2mm以上程度で半田バンプが接合される基板電極などが形成されているセラミックやFPCまたはガラスや樹脂基板であれば同様に接合を行なうことが可能である。また、チップに2×2mm程度の小チップを使用したが、チップサイズの大小による局部加熱の対応は、非接触の局部加熱源の高さを調整し、焦点範囲を調整することにより所望の局部過熱を得ることができる。尚、焦点範囲を広げると加熱温度も下がる為、非接触熱源のパワーを上げる必要がある。チップが小さくなった場合は、非接触の熱源の最小焦点範囲に限界があるため、2×2mmよりチップサイズが小さくなる場合は、照射されるチップ上にチップサイズと同程度の穴の空いた金属製のマスクなどを設置し、マスク穴により強制的に焦点範囲を小さくし、照射を行なう必要がある。使用する半田バンプの種類に関しては、共晶半田や鉛フリー半田等、溶融温度の異なるものでも接合が可能であり、その際の加熱温度は、各半田バンプの所定の溶融可能温度に10〜20℃程度プラスした温度を照射し溶融接合を行なえば良い。非接触の熱源にハロゲンランプを使用したが、キセノンランプやレーザー光線など非接触で急加熱が可能な熱源であれば本発明のチップ接合方法やチップ接合装置に適用できる。 In this embodiment, a glass epoxy having an outer shape of 5 × 5 mm and a thickness of about 0.5 mm is used as the substrate material. However, the substrate material to be used is formed with substrate electrodes and the like to which solder bumps are joined with an outer shape of about 2 × 2 mm or more. Any ceramic, FPC, glass, or resin substrate can be similarly bonded. In addition, a small chip of about 2 × 2 mm was used for the chip, but local heating due to the size of the chip can be achieved by adjusting the height of the non-contact local heating source and adjusting the focal range. Overheating can be obtained. Note that if the focal range is expanded, the heating temperature also decreases, so the power of the non-contact heat source must be increased. When the chip becomes smaller, there is a limit to the minimum focal range of the non-contact heat source. Therefore, when the chip size is smaller than 2 × 2 mm, a hole of the same size as the chip size is formed on the irradiated chip. It is necessary to install a metal mask or the like, forcibly reduce the focal range by the mask hole, and perform irradiation. As for the type of solder bump to be used, even those having different melting temperatures, such as eutectic solder and lead-free solder, can be joined. The heating temperature at that time is 10 to 20 at a predetermined melting temperature of each solder bump. What is necessary is just to perform melt bonding by irradiating a temperature plus about ℃. Although a halogen lamp is used as a non-contact heat source, any heat source capable of rapid heating without contact, such as a xenon lamp or a laser beam, can be applied to the chip bonding method and the chip bonding apparatus of the present invention.

図10は本発明によるチップ接合装置の模式図である。チップ接合装置は、少なくとも、基板2上に熱硬化性エポキシ樹脂7の供給を行なうユニット(A)と基板2上にチップ1供給を行なうユニット(B)さらに供給されているチップ1上に非接触にて局部加熱を行なうユニット(C)にて構成されており、各工程を同一搬送系10(例えばベルトコンベア)にて行なえるような機構となっている。ユニット(A)の熱硬化性エポキシ樹脂7供給部は、ディスペンサーにて行なえるようになっており、半田バンプ3が接触する基板電極4部が全て覆われるように供給を行なう。ユニット(B)のチップ供給部は、半田バンプ3と基板電極4との位置合わせ認識機能と加重制御機能を持ち合せた機構11となっており、所定のチップ位置及び搭載加重にて供給を行なう。ユニット(C)部の非接触の局部加熱部は、加熱量を制御できる機構と焦点調整を行なう為の高さ調整機構12を持ち合せており、熱量及び加熱範囲の制御を行い、供給済みのチップ1上に局部加熱を行なう。尚、各ユニットは同一搬送系10上にて行なわれ、全工程を同時進行及び次工程への自動流動が行なえるような構造となっている。

FIG. 10 is a schematic view of a chip bonding apparatus according to the present invention. The chip bonding apparatus includes at least a unit (A) for supplying the thermosetting

1 チップ

2 基板

3 半田バンプ

4 基板電極

5 フラックス

6 ボンディングヘッド

7 熱硬化性(エポキシ)樹脂

8 ディスペンサ

9 非接触の熱源

10 搬送系

11 位置合わせ認識機能と加重制御機能を持ち合せた機構

12 高さ調整機構

DESCRIPTION OF

Claims (6)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004336479A JP2006147880A (en) | 2004-11-19 | 2004-11-19 | Method and device for bonding semiconductor with solder bump |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004336479A JP2006147880A (en) | 2004-11-19 | 2004-11-19 | Method and device for bonding semiconductor with solder bump |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2006147880A true JP2006147880A (en) | 2006-06-08 |

Family

ID=36627209

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004336479A Pending JP2006147880A (en) | 2004-11-19 | 2004-11-19 | Method and device for bonding semiconductor with solder bump |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2006147880A (en) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009203292A (en) * | 2008-02-26 | 2009-09-10 | Panasonic Electric Works Co Ltd | Liquid epoxy resin composition, sealed semiconductor device and sealing method |

| JP2011029350A (en) * | 2009-07-24 | 2011-02-10 | Sumitomo Bakelite Co Ltd | Method for manufacturing electronic component, and electronic component |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02197373A (en) * | 1989-01-26 | 1990-08-03 | Fuji Electric Co Ltd | Method for soldering ic chip |

| JPH02249247A (en) * | 1989-03-23 | 1990-10-05 | Casio Comput Co Ltd | Bonding of integrated circuit chip |

| JP2001148403A (en) * | 1999-11-18 | 2001-05-29 | Seiko Epson Corp | Method and apparatus for packaging semiconductor chip |

| JP2006140295A (en) * | 2004-11-11 | 2006-06-01 | Sony Corp | Manufacturing method for semiconductor device |

-

2004

- 2004-11-19 JP JP2004336479A patent/JP2006147880A/en active Pending

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02197373A (en) * | 1989-01-26 | 1990-08-03 | Fuji Electric Co Ltd | Method for soldering ic chip |

| JPH02249247A (en) * | 1989-03-23 | 1990-10-05 | Casio Comput Co Ltd | Bonding of integrated circuit chip |

| JP2001148403A (en) * | 1999-11-18 | 2001-05-29 | Seiko Epson Corp | Method and apparatus for packaging semiconductor chip |

| JP2006140295A (en) * | 2004-11-11 | 2006-06-01 | Sony Corp | Manufacturing method for semiconductor device |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009203292A (en) * | 2008-02-26 | 2009-09-10 | Panasonic Electric Works Co Ltd | Liquid epoxy resin composition, sealed semiconductor device and sealing method |

| JP2011029350A (en) * | 2009-07-24 | 2011-02-10 | Sumitomo Bakelite Co Ltd | Method for manufacturing electronic component, and electronic component |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI514487B (en) | Thermal compression bonding of semiconductor chips | |

| KR100555395B1 (en) | Flip chip interconnection using no-clean flux | |

| JPH03166739A (en) | Method for soldering | |

| US20110095423A1 (en) | Semiconductor device mounted structure and its manufacturing method | |

| JP6057224B2 (en) | Component mounting structure | |

| JPWO2004107432A1 (en) | Electronic component mounting method, removal method and apparatus | |

| CN104221480A (en) | Electronic component mounting method and electronic component mounting line | |

| WO2005081602A1 (en) | Electronic component mounting method, and circuit board and circuit board unit used therein | |

| JP4810393B2 (en) | Optical module manufacturing method and manufacturing apparatus | |

| JP2006147880A (en) | Method and device for bonding semiconductor with solder bump | |

| JP2014143316A (en) | Resin sealing method of flip chip component | |

| JP2007142232A (en) | Method for packaging electronic component with bump | |

| JP5853135B2 (en) | Electrode joining method and circuit member joining line | |

| JP4200273B2 (en) | Mounting board manufacturing method | |

| TWI453845B (en) | Method for manufacturing semiconductor device | |

| US20060065696A1 (en) | System and method for forming solder joints | |

| JP4260712B2 (en) | Electronic component mounting method and apparatus | |

| JP6037300B2 (en) | Circuit member joint structure | |

| JP2010140924A (en) | Electronic component mounting structure, and electronic component mounting method | |

| JP4785486B2 (en) | Electronic device manufacturing method and manufacturing apparatus | |

| JPH11121921A (en) | Method and device for soldering electronic components | |

| JPH1154559A (en) | Device and method for bonding work with bump | |

| JP2003008196A (en) | Method and machine for mounting electronic component | |

| JP2011044530A (en) | Solder joint method and solder joint device | |

| JP2006012943A (en) | Electronic device and method of manufacturing the same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070926 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090929 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091002 |

|

| A521 | Written amendment |

Effective date: 20091127 Free format text: JAPANESE INTERMEDIATE CODE: A523 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20100810 |